半导体中的电子状态习题

半导体物理问答题

半导体物理问答题 -CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN第一篇 习题 半导体中的电子状态1-1、什么叫本征激发温度越高,本征激发的载流子越多,为什么试定性说明之。

1-2、试定性说明Ge 、Si 的禁带宽度具有负温度系数的原因。

1-3、试指出空穴的主要特征。

1-4、简述Ge 、Si 和GaAS 的能带结构的主要特征。

1-5、某一维晶体的电子能带为[])sin(3.0)cos(1.01)(0ka ka E k E --=其中E 0=3eV ,晶格常数a=5х10-11m 。

求:(1) 能带宽度;(2) 能带底和能带顶的有效质量。

第一篇 题解 半导体中的电子状态1-1、解:在一定温度下,价带电子获得足够的能量(≥E g )被激发到导带成为导电电子的过程就是本征激发。

其结果是在半导体中出现成对的电子-空穴对。

如果温度升高,则禁带宽度变窄,跃迁所需的能量变小,将会有更多的电子被激发到导带中。

1-2、解:电子的共有化运动导致孤立原子的能级形成能带,即允带和禁带。

温度升高,则电子的共有化运动加剧,导致允带进一步分裂、变宽;允带变宽,则导致允带与允带之间的禁带相对变窄。

反之,温度降低,将导致禁带变宽。

因此,Ge 、Si 的禁带宽度具有负温度系数。

1-3、解: 空穴是未被电子占据的空量子态,被用来描述半满带中的大量电子的集体运动状态,是准粒子。

主要特征如下:A 、荷正电:+q ;B 、空穴浓度表示为p (电子浓度表示为n );C 、E P =-E nD 、m P *=-m n *。

1-4、解:(1) Ge 、Si:a )Eg (Si :0K) = 1.21eV ;Eg (Ge :0K) = 1.170eV ;b )间接能隙结构c )禁带宽度E g 随温度增加而减小;(2) GaAs :a )E g (300K )= 1.428eV , Eg (0K) = 1.522eV ;b )直接能隙结构;c )Eg 负温度系数特性: dE g /dT = -3.95×10-4eV/K ;1-5、解:(1) 由题意得:[][])sin(3)cos(1.0)cos(3)sin(1.002220ka ka E a k d dE ka ka aE dk dE+=-=eVE E E E a kd dE a k E a kd dE a k a k a k ka tg dk dE oooo 1384.1min max ,01028.2)4349.198sin 34349.198(cos 1.0,4349.198,01028.2)4349.18sin 34349.18(cos 1.0,4349.184349.198,4349.1831,04002222400222121=-=∆<⨯-=+==>⨯=+====∴==--则能带宽度对应能带极大值。

半导体习题

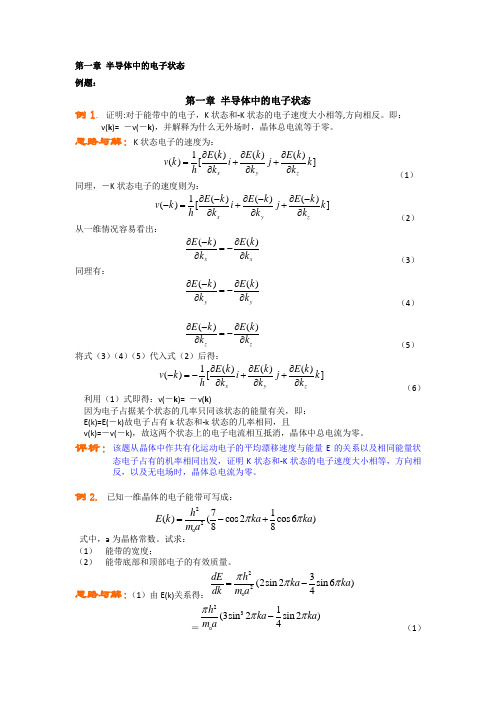

第一章 半导体中的电子状态 例题:第一章 半导体中的电子状态例1. 证明:对于能带中的电子,K 状态和-K 状态的电子速度大小相等,方向相反。

即:v(k )= -v(-k ),并解释为什么无外场时,晶体总电流等于零。

思路与解:K 状态电子的速度为:1()()()()[]x y zE k E k E k v k i j k h k k k ∂∂∂=++∂∂∂ (1)同理,-K 状态电子的速度则为:1()()()()[]x y zE k E k E k v k i j k h k k k ∂-∂-∂--=++∂∂∂ (2)从一维情况容易看出:()()x x E k E k k k ∂-∂=-∂∂ (3)同理有:()()yy E k E k k k ∂-∂=-∂∂ (4)()()zz E k E k k k ∂-∂=-∂∂ (5) 将式(3)(4)(5)代入式(2)后得:1()()()()[]x y zE k E k E k v k i j k h k k k ∂∂∂-=-++∂∂∂ (6)利用(1)式即得:v(-k )= -v(k )因为电子占据某个状态的几率只同该状态的能量有关,即: E(k)=E(-k)故电子占有k 状态和-k 状态的几率相同,且v(k)=-v(-k),故这两个状态上的电子电流相互抵消,晶体中总电流为零。

评析:该题从晶体中作共有化运动电子的平均漂移速度与能量E 的关系以及相同能量状态电子占有的机率相同出发,证明K 状态和-K 状态的电子速度大小相等,方向相反,以及无电场时,晶体总电流为零。

例2. 已知一维晶体的电子能带可写成:2271()(cos 2cos6)88h E k ka ka m a ππ=-+式中,a 为晶格常数。

试求:(1) 能带的宽度;(2) 能带底部和顶部电子的有效质量。

思路与解:(1)由E(k)关系得:223(2sin 2sin 6)4dE h ka ka dk m a πππ=-=231(3sin 2sin 2)4h ka ka m a πππ- (1)222221(18sin 2cos 2cos 2)2d E h ka ka ka dk m ππππ=- (2)令 0dE dk = 得:21sin 212ka π= 1211cos 2()12ka π∴=±当cos 2ka π=2)得:222211(180121221212d E h dk m mπ=⨯=>对应E(k)的极小值。

半导体物理课后习题

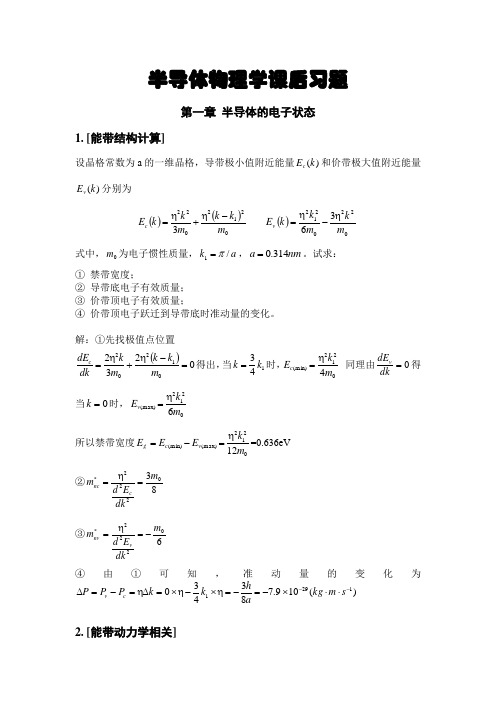

半导体物理学课后习题第一章 半导体的电子状态1. [能带结构计算]设晶格常数为a 的一维晶格,导带极小值附近能量)(k E c 和价带极大值附近能量)(k E v 分别为()()02120223m k k m k k E c -+= ()022021236m k m k k E v -= 式中,0m 为电子惯性质量,a k /1π=,nm a 314.0=。

试求: ① 禁带宽度;② 导带底电子有效质量; ③ 价带顶电子有效质量;④ 价带顶电子跃迁到导带底时准动量的变化。

解:①先找极值点位置()023201202=-+=m k k m k dk dE c 得出,当143k k =时,0212(min)4m k E c =同理由0=dk dE v 得当0=k 时,0212(max)6m k E v = 所以禁带宽度0212(max)(min)12m k E E E v c g =-==0.636eV ②830222*m dk E d m c nc== ③60222*m dk E d m v nv-==④由①可知,准动量的变化为)(109.7834301291--⋅⋅⨯-=-=⨯-⨯=∆=-=∆s m kg ahk k P P P c v2. [能带动力学相关]晶格常数为0.25nm 的一维晶格,当外加102V/m ,107V/m 的电场时,试分别计算电子能带底运动到能带顶所需要的时间。

解:设晶格常数为a ,则电子从能带底到能带顶过程中准动量的变化为ak π=∆,因为dt dk qE f==,所以qEdt dk =所以所需要的时间为:E =∙∆=∆=∆qa qE k dtdk k t π,当m V /102=E 时,s t 81028.8-⨯=∆ 当m V /107=E 时,s t 131028.8-⨯=∆第二章 半导体中杂质和缺陷能级1. [半导体、杂质概念]实际半导体与理想半导体的主要区别是什么? 解:杂质和缺陷的存在是实际半导体和理想半导体的主要区别。

04-第一章-半导体中的电子状态

锗和硅的能带结构

Si : m 0.98m0 , m 0.19 m0

* l * t

Ge : ml* 1.64 m0 , mt* 0.082 m0

h2 2 2 2 E1, 2 (k ) Ev Ak 2 B 2k 4 C 2 (k x2k y ky k z k z2k x2 2m0

h2 E3 ( k ) E v Ak 2 2m0

Si : m 0.49 m0 , m 0.16m0

* hh * lh

* * Ge : mhh 0.28m0 , mlh 0.044 m0

直接能隙

E

间接能隙

E 声子

导带

导带底 W 价带顶

E g

价带

g

0

0.9 0.8

Unstrained

Strained

0.9 0.8 0.7 0.6 0.5 0.4 1.0

0.7 0.6 0.5 0.4 0.0

0.2

0.4

0.6

0.8

Ge组份

能带偏移与应变关系

习题:书P35 习题1,习题2

k

hk (photon) hk c hq E g W

kc

0

k

* III-V族化合物半导体

Eg Al Ga In

P 2.40 2.26 1.33

As 2.13 1.43 0.35

Sb 1.62 0.72 0.18

* * GaAs : me 0.068 m0 , meh 1.2m0 * * GaAs : mhh 0.45m0 , mlh 0.082 m0

* 合金半导体 GaAlAs

半导体物理知识点及重点习题总结

半导体物理知识点及重点习题总结基本概念题:第⼀章半导体电⼦状态1.1 半导体通常是指导电能⼒介于导体和绝缘体之间的材料,其导带在绝对零度时全空,价带全满,禁带宽度较绝缘体的⼩许多。

1.2能带晶体中,电⼦的能量是不连续的,在某些能量区间能级分布是准连续的,在某些区间没有能及分布。

这些区间在能级图中表现为带状,称之为能带。

1.3导带与价带1.4有效质量有效质量是在描述晶体中载流⼦运动时引进的物理量。

它概括了周期性势场对载流⼦运动的影响,从⽽使外场⼒与加速度的关系具有⽜顿定律的形式。

其⼤⼩由晶体⾃⾝的E-k 关系决定。

1.5本征半导体既⽆杂质有⽆缺陷的理想半导体材料。

1.6空⽳空⽳是为处理价带电⼦导电问题⽽引进的概念。

设想价带中的每个空电⼦状态带有⼀个正的基本电荷,并赋予其与电⼦符号相反、⼤⼩相等的有效质量,这样就引进了⼀个假想的粒⼦,称其为空⽳。

它引起的假想电流正好等于价带中的电⼦电流。

1.7空⽳是如何引⼊的,其导电的实质是什么?答:空⽳是为处理价带电⼦导电问题⽽引进的概念。

设想价带中的每个空电⼦状态带有⼀个正的基本电荷,并赋予其与电⼦符号相反、⼤⼩相等的有效质量,这样就引进了⼀个假想的粒⼦,称其为空⽳。

这样引⼊的空⽳,其产⽣的电流正好等于能带中其它电⼦的电流。

所以空⽳导电的实质是能带中其它电⼦的导电作⽤,⽽事实上这种粒⼦是不存在的。

1.8 半导体的回旋共振现象是怎样发⽣的(以n型半导体为例)答案:⾸先将半导体置于匀强磁场中。

⼀般n型半导体中⼤多数导带电⼦位于导带底附近,对于特定的能⾕⽽⾔,这些电⼦的有效质量相近,所以⽆论这些电⼦的热运动速度如何,它们在磁场作⽤下做回旋运动的频率近似相等。

当⽤电磁波辐照该半导体时,如若频率与电⼦的回旋运动频率相等,则半导体对电磁波的吸收⾮常显著,通过调节电磁波的频率可观测到共振吸收峰。

这就是回旋共振的机理。

1.9 简要说明回旋共振现象是如何发⽣的。

半导体样品置于均匀恒定磁场,晶体中电⼦在磁场作⽤下运动运动轨迹为螺旋线,圆周半径为r ,回旋频率为当晶体受到电磁波辐射时,在频率为时便观测到共振吸收现象。

半导体物理与器件习题答案

半导体物理与器件习题答案【篇一:半导体物理与器件课后习题2】图3.35所示色e-k关系曲线表示了两种可能的价带。

说明其中哪一种对应的空穴有效质量较大。

为什么?解:图中b曲线对应的空穴有效质量较大空穴的有效质量: m*p?1 21de?222?dk?图中曲线a的弯曲程度大于曲线bd2e 故 22dkd2e?22dkba?m*p?a??m*p?b?3.16 图3.37所示为两种不同半导体材料导带中电子的e-k关系抛物线,试确定两种电子的有效质量(以自由电子质量为单位)。

解:e-k关系曲线k=0附近的图形 ?k2近似于抛物线故有:e?ec? *2mn由图可知 ec?0①对于a曲线1??1.055?10?0.1????2k210-10??*?31? ?4.97?10kg?0.55me 有mn(a)?-192e0.07?1.06?10 ?-342?2②对于b曲线有1??1.055?10??0.1?-10?22?k10?32m*??4.97?10kg?0.055men (b)?-192e0.7?1.06?10 ?-342?23.20 硅的能带图3.23b所示导带的最小能量出现在[100]方向上。

最小值附近一维方向上的能量可以近似为s(k?k0) e?e0?e1co?其中k0是最小能量的k值。

是确定k?k0时的粒子的有效质量。

解:导带能量最小值附近一维方向上的能量e?e0?e1cos?(k?k0) d2e ?22??2e1cos?(k?k0) dkd2e当k?k0时 cos?(k?k0)?1;22??2e1dk 11d2e?*?222又mn?dk?2?k?k0时粒子的有效质量为:m?2?e1 *n3.24 试确定t=300k时gaas中ev和ev-kt之间的总量子态数量。

h3?3*2pev?e当t=300k时 gaas中ev和ev?kt之间总量子态数量:h3h36.6262?10?3432?1.38?103?23?30032?3.28?10?7cm?33.37 某种材料t=300k时的费米能级为6.25ev。

半导体物理习题答案完整版

半导体物理习题答案 HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】第一章半导体中的电子状态例1.证明:对于能带中的电子,K状态和-K状态的电子速度大小相等,方向相反。

即:v(k)= -v(-k),并解释为什么无外场时,晶体总电流等于零。

解:K状态电子的速度为:(1)同理,-K状态电子的速度则为:(2)从一维情况容易看出:(3)同理有:(4)(5)将式(3)(4)(5)代入式(2)后得:(6)利用(1)式即得:v(-k)= -v(k)因为电子占据某个状态的几率只同该状态的能量有关,即:E(k)=E(-k)故电子占有k状态和-k状态的几率相同,且v(k)=-v(-k)故这两个状态上的电子电流相互抵消,晶体中总电流为零。

例2.已知一维晶体的电子能带可写成:式中,a为晶格常数。

试求:(2)能带底部和顶部电子的有效质量。

解:(1)由E(k)关系(1)(2)令得:当时,代入(2)得:对应E(k)的极小值。

当时,代入(2)得:对应E(k)的极大值。

根据上述结果,求得和即可求得能带宽度。

故:能带宽度(3)能带底部和顶部电子的有效质量:习题与思考题:1 什么叫本征激发温度越高,本征激发的载流子越多,为什么试定性说明之。

2 试定性说明Ge、Si的禁带宽度具有负温度系数的原因。

3 试指出空穴的主要特征。

4 简述Ge、Si和GaAs的能带结构的主要特征。

5 某一维晶体的电子能带为其中E0=3eV,晶格常数a=5×10-11m。

求:(2)能带底和能带顶的有效质量。

6原子中的电子和晶体中电子受势场作用情况以及运动情况有何不同原子中内层电子和外层电子参与共有化运动有何不同7晶体体积的大小对能级和能带有什么影响?8描述半导体中电子运动为什么要引入“有效质量”的概念?用电子的惯性质量描述能带中电子运动有何局限性?9 一般来说,对应于高能级的能带较宽,而禁带较窄,是否如此为什么10有效质量对能带的宽度有什么影响?有人说:“有效质量愈大,能量密度也愈大,因而能带愈窄。

半导体物理习题及答案

复习思考题与自测题第一章1.原子中的电子和晶体中电子受势场作用情况以及运动情况有何不同,原子中内层电子和外层电子参与共有化运动有何不同。

答:原子中的电子是在原子核与电子库伦相互作用势的束缚作用下以电子云的形式存在,没有一个固定的轨道;而晶体中的电子是在整个晶体内运动的共有化电子,在晶体周期性势场中运动。

当原子互相靠近结成固体时,各个原子的内层电子仍然组成围绕各原子核的封闭壳层,和孤立原子一样;然而,外层价电子那么参与原子间的相互作用,应该把它们看成是属于整个固体的一种新的运动状态。

组成晶体原子的外层电子共有化运动较强,其行为与自由电子相似,称为准自由电子,而内层电子共有化运动较弱,其行为与孤立原子的电子相似。

2.描述半导体中电子运动为什么要引入"有效质量"的概念,用电子的惯性质量描述能带中电子运动有何局限性。

答:引进有效质量的意义在于它概括了半导体内部势场的作用,使得在解决半导体中电子在外力作用下的运动规律时,可以不涉及半导体内部势场的作用。

惯性质量描述的是真空中的自由电子质量,而不能描述能带中不自由电子的运动,通常在晶体周期性势场作用下的电子惯性运动,成为有效质量3.一般来说, 对应于高能级的能带较宽,而禁带较窄,是否如此,为什么?答:不是,能级的宽窄取决于能带的疏密程度,能级越高能带越密,也就是越窄;而禁带的宽窄取决于掺杂的浓度,掺杂浓度高,禁带就会变窄,掺杂浓度低,禁带就比较宽。

4.有效质量对能带的宽度有什么影响,有人说:"有效质量愈大,能量密度也愈大,因而能带愈窄.是否如此,为什么?答:有效质量与能量函数对于K的二次微商成反比,对宽窄不同的各个能带,1〔k〕随k的变化情况不同,能带越窄,二次微商越小,有效质量越大,内层电子的能带窄,有效质量大;外层电子的能带宽,有效质量小。

5.简述有效质量与能带构造的关系;答:能带越窄,有效质量越大,能带越宽,有效质量越小。

半导体物理习题答案

第1章 半导体中的电子状态1. 设晶格常数为a 的一维晶格,导带极小值附近能量()c E k 和价带极大值附近能量()v E k 分别为2222100()()3c h k k h k E k m m -=+,22221003()6v h k h k E k m m =-0m 为电子惯性质量,112k a =, 0.314a =nm 。

试求:1) 禁带宽度;2) 导带底电子有效质量; 3) 价带顶电子有效质量;4) 价带顶电子跃迁到导带底时准动量的变化。

解:1) 禁带宽度g E ,根据22100()2()202c dE k h k k h k dk m m -=+=,可求出对应导带能量极小值min E 的k 值:min 134k k =, 由题目中()c E k 式可得:min 12min 3104()4c k k k h E E k k m ====; 根据20()60v dE k h k dk m =-=,可以看出,对应价带能量极大值max E 的k 值为:k max = 0;可得max 221max 00()6v k k h k E E k m ====,所以2221min max 2001248g h k h E E E m m a=-== 2) 导带底电子有效质量m n由于2222200022833c d E h h h dk m m m =+=,所以202238nc m h md E dk== 3) 价带顶电子有效质量vn m由于22206v d E h dk m =-,所以20226v nv m h m d E dk ==- 4) 准动量的改变量min max 133()48hh k h k k hk a∆=-==2. 晶格常数为 nm 的一维晶格,当外加102V/m 、107V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:设电场强度为E ,电子受到的力f 为dkf hqE dt==(E 取绝对值),可得h dt dk qE =, 所以12012ta h h t dt dk qE qE a===⎰⎰,代入数据得: 34619106.62108.310()1.6102(2.510)t s E E----⨯⨯==⨯⨯⨯⨯⨯ 当E = 102V/m 时,88.310t s -=⨯;当E = 107V/m 时,138.310t s -=⨯。

半导体物理部分考试习题答案

第一章 半导体中的电子状态1. 设晶格常数为a 的一维晶格,导带极小值附近能量E c (k )和价带极大值附近能量E v (k )分别为:E c (k)=0223m k h +022)1(m k k h −和E v (k)= 0226m k h -0223m k h ; m 0为电子惯性质量,k 1=1/2a ;a =0.314nm 。

试求: ①禁带宽度; ②导带底电子有效质量; ③价带顶电子有效质量; ④价带顶电子跃迁到导带底时准动量的变化。

[解] ①禁带宽度Eg 根据dk k dEc )(=0232m k h +012)(2m k k h −=0;可求出对应导带能量极小值E min 的k 值: k min =143k , 由题中E C 式可得:E min =E C (K)|k=k min =2104k m h ;由题中E V 式可看出,对应价带能量极大值Emax 的k 值为:k max =0;并且E min =E V (k)|k=k max =02126m k h ;∴Eg=E min -E max =021212m k h =20248a m h =112828227106.1)1014.3(101.948)1062.6(−−−−×××××××=0.64eV②导带底电子有效质量m n 0202022382322m h m h m h dkE d C =+=;∴ m n=022283/m dk E d h C= ③价带顶电子有效质量m ’ 02226m h dk E d V −=,∴0222'61/m dk E d h m Vn−== ④准动量的改变量 h △k=h (k min -k max )= a h k h 83431=3. 如果n 型半导体导带峰值在[110]轴上及相应对称方向上,回旋共振实验结果应如何?[解] 根据立方对称性,应有下列12个方向上的旋转椭球面:[][][]110,101,011,110,⎡⎤⎣⎦ 101,011;⎡⎤⎡⎤⎣⎦⎣⎦ [110],101,011,110,⎡⎤⎡⎤⎡⎤⎣⎦⎣⎦⎣⎦ 101,011;⎡⎤⎡⎤⎣⎦⎣⎦ 则由解析几何定理得, B 与3k 的夹角余弦cos θ为:cos θ= 式中, 123B b i b j b k =++. 对不同方向的旋转椭球面取不同的一组123(,,)k k k .(1) 若B 沿[111]方向,则cos θ可以取两组数. 对[][]110,110,101,101,⎡⎤⎡⎤⎣⎦⎣⎦[]011,011⎡⎤⎣⎦方向的旋转椭球得: cos θ=对110,110,101,101,011,011⎡⎤⎡⎤⎡⎤⎡⎤⎡⎤⎡⎤⎣⎦⎣⎦⎣⎦⎣⎦⎣⎦⎣⎦方向的旋转椭球得:cos θ∴当cos θ=时: 22cos 3θ= 21sin 3θ= n t m m =∵ *n t m m ∴= 当cos 0θ=时; 2cos 0θ= 2sin 1θ= 同理得: *n m = 由*c n qB m ω=可知,当B 沿(111)方向时应有两个共振吸收峰. (2) 若B 沿(110)方向,则cos θ可以取三组数. 对[]110,110⎡⎤⎣⎦ 方向旋转椭球, cos 1θ= 对110,110⎡⎤⎡⎤⎣⎦⎣⎦ 方向旋转椭球, cos 0θ= 对[][]011,011,011,011,101,101,101,101⎡⎤⎡⎤⎡⎤⎡⎤⎡⎤⎡⎤⎣⎦⎣⎦⎣⎦⎣⎦⎣⎦⎣⎦方向的旋转椭球, 1cos 2θ=当cos 1θ=时: 2cos 1θ= 2sin0θ= 得: *n m 当cos 0θ=时:2cos 0θ= 2sin1θ= 得: *n m = 当1cos 2θ=时: 21cos 4θ= 23sin 4θ= 得: *n m 故,应有三个吸收峰. (3)若B 沿[100]方向,则cos θ可以取两组数.对[][]110,110,110,110,101,101,101,101⎡⎤⎡⎤⎡⎤⎡⎤⎡⎤⎡⎤⎣⎦⎣⎦⎣⎦⎣⎦⎣⎦⎣⎦方向上的旋转椭球得: cos θ= 对[]011,011,011,011⎡⎤⎡⎤⎡⎤⎣⎦⎣⎦⎣⎦方向上的旋转椭球得:cos 0θ= 当cos θ=时, 21cos 2θ= 21sin 2θ= 得: *n t m m = 当cos 0θ=时: 2cos 0θ= 2sin 1θ= 得*n m = .(4) B 沿空间任意方向时, cos θ最多可有六个不同值,故可以求六个*nm ,所对应的六个共振吸收峰.第二章 半导体中的杂志和缺陷能级7. 锑化铟的禁带宽度0.18V g E e =,相对介电常数17r ε=,电子的有效质量00.015n m m ∗=,0m 为电子的惯性质量,求ⅰ)施主杂质的电离能,ⅱ)施主的若束缚电子基态轨道半径。

半导体物理参考习题和解答

半导体物理参考习题和解答第一章1.原子中的电子和晶体中电子受势场作用情况以及运动情况有何不同, 原子中内层电子和外层电子参与共有化运动有何不同。

答:原子中的电子是在原子核与电子库伦相互作用势的束缚作用下以电子云的形式存在,没有一个固定的轨道;而晶体中的电子是在整个晶体内运动的共有化电子,在晶体周期性势场中运动。

当原子互相靠近结成固体时,各个原子的内层电子仍然组成围绕各原子核的封闭壳层,和孤立原子一样;然而,外层价电子则参与原子间的相互作用,应该把它们看成是属于整个固体的一种新的运动状态。

组成晶体原子的外层电子共有化运动较强,其行为与自由电子相似,称为准自由电子,而内层电子共有化运动较弱,其行为与孤立原子的电子相似。

2.描述半导体中电子运动为什么要引入"有效质量"的概念, 用电子的惯性质量描述能带中电子运动有何局限性。

答:引进有效质量的意义在于它概括了半导体内部势场的作用,使得在解决半导体中电子在外力作用下的运动规律时,可以不涉及半导体内部势场的作用。

惯性质量描述的是真空中的自由电子质量,而不能描述能带中不自由电子的运动,通常在晶体周期性势场作用下的电子惯性运动,成为有效质量3.一般来说, 对应于高能级的能带较宽,而禁带较窄,是否如此,为什么?答:不是,能级的宽窄取决于能带的疏密程度,能级越高能带越密,也就是越窄;而禁带的宽窄取决于掺杂的浓度,掺杂浓度高,禁带就会变窄,掺杂浓度低,禁带就比较宽。

4.有效质量对能带的宽度有什么影响,有人说:"有效质量愈大,能量密度也愈大,因而能带愈窄.是否如此,为什么?答:有效质量与能量函数对于K的二次微商成反比,对宽窄不同的各个能带,1(k 随k的变化情况不同,能带越窄,二次微商越小,有效质量越大,内层电子的能带窄,有效质量大;外层电子的能带宽,有效质量小。

5.简述有效质量与能带结构的关系;答:能带越窄,有效质量越大,能带越宽,有效质量越小。

半导体物理与器件答案

半导体物理与器件答案半导体物理与器件答案篇一:半导体物理习题及答案复习思索题与自测题第一章1. 原子中的电子和晶体中电子受势场作用状况以及运动状况有何不同, 原子中内层电子和外层电子参加共有化运动有何不同。

答:原子中的电子是在原子核与电子库伦互相作用势的束缚作用下以电子XX的形式存在,没有一个固定的轨道;而晶体中的电子是在整个晶体内运动的共有化电子,在晶体周期性势场中运动。

当原子相互靠近结成固体时,各个原子的内层电子仍旧组成围绕各原子核的封闭壳层,和孤立原子一样;然而,外层价电子则参加原子间的互相作用,应当把它们看成是属于整个固体的一种新的运动状态。

组成晶体原子的外层电子共有化运动较强,其行为与自由电子相像,称为准自由电子,而内层电子共有化运动较弱,其行为与孤立原子的电子相像。

2.描述半导体中电子运动为什么要引入有效质量的概念, 用电子的惯性质量描述能带中电子运动有何局限性。

答:引进有效质量的意义在于它概括了半导体内部势场的作用,使得在解决半导体中电子在外力作用下的运动规律时,可以不涉及半导体内部势场的作用。

惯性质量描述的是真空中的自由电子质量,而不能描述能带中不自由电子的运动,通常在晶体周期性势场作用下的电子惯性运动,成为有效质量3.一般来说, 对应于高能级的能带较宽,而禁带较窄,是否如此,为什么?答:不是,能级的宽窄取决于能带的疏密程度,能级越高能带越密,也就是越窄;而禁带的宽窄取决于掺杂的浓度,掺杂浓度高,禁带就会变窄,掺杂浓度低,禁带就比较宽。

4.有效质量对能带的宽度有什么影响,有人说:有效质量愈大,能量密度也愈大,因此能带愈窄.是否如此,为什么?答:有效质量与能量函数对于K的二次微商成反比,对宽窄不同的各个能带,1〔k〕随k的改变状况不同,能带越窄,二次微商越小,有效质量越大,内层电子的能带窄,有效质量大;外层电子的能带宽,有效质量小。

5.简述有效质量与能带结构的关系;答:能带越窄,有效质量越大,能带越宽,有效质量越小。

半导体物理习题及答案

复习思考题与自测题第一章1.原子中的电子和晶体中电子受势场作用情况以及运动情况有何不同, 原子中内层电子和外层电子参与共有化运动有何不同。

答:原子中的电子是在原子核与电子库伦相互作用势的束缚作用下以电子云的形式存在,没有一个固定的轨道;而晶体中的电子是在整个晶体内运动的共有化电子,在晶体周期性势场中运动。

当原子互相靠近结成固体时,各个原子的内层电子仍然组成围绕各原子核的封闭壳层,和孤立原子一样;然而,外层价电子则参与原子间的相互作用,应该把它们看成是属于整个固体的一种新的运动状态。

组成晶体原子的外层电子共有化运动较强,其行为与自由电子相似,称为准自由电子,而内层电子共有化运动较弱,其行为与孤立原子的电子相似。

2.描述半导体中电子运动为什么要引入"有效质量"的概念, 用电子的惯性质量描述能带中电子运动有何局限性。

答:引进有效质量的意义在于它概括了半导体内部势场的作用,使得在解决半导体中电子在外力作用下的运动规律时,可以不涉及半导体内部势场的作用。

惯性质量描述的是真空中的自由电子质量,而不能描述能带中不自由电子的运动,通常在晶体周期性势场作用下的电子惯性运动,成为有效质量3.一般来说, 对应于高能级的能带较宽,而禁带较窄,是否如此,为什么?答:不是,能级的宽窄取决于能带的疏密程度,能级越高能带越密,也就是越窄;而禁带的宽窄取决于掺杂的浓度,掺杂浓度高,禁带就会变窄,掺杂浓度低,禁带就比较宽。

4.有效质量对能带的宽度有什么影响,有人说:"有效质量愈大,能量密度也愈大,因而能带愈窄.是否如此,为什么?答:有效质量与能量函数对于K的二次微商成反比,对宽窄不同的各个能带,1(k)随k的变化情况不同,能带越窄,二次微商越小,有效质量越大,内层电子的能带窄,有效质量大;外层电子的能带宽,有效质量小。

5.简述有效质量与能带结构的关系;答:能带越窄,有效质量越大,能带越宽,有效质量越小。

半导体物理课后习题答案(1-12章)

∆ ED =

7.06 10− 4 eV

r1,n = ε r (

° m0 1 ) � a 17 = 0.53 600.67 A 0 ∗ mn 0.015

8. 磷化鎵的禁带宽度 Eg = 2.26eV ,相对介电常数 ε r = 11.1 ,空穴的有效质量

m∗p = 0.86m0 , m0 为电子的惯性质量,求ⅰ)受主杂质的电离能,ⅱ)受主所若 束缚的空穴基态轨道半径。 [解]: ∆ E A = 已知, E0 = m m∗p E0 rp = n 2ε r ( ∗0 ) a0 2 , mp m0 ε r

第1章 半导体中的电子状态

1. 设晶格常数为 a 的一维晶格,导带极小值附近能量 Ec(k)和价带极大值附近 能量 Ev(k)分别为: Ec(k)=

h 2 k 2 h 2 (k − k1) 2 h2k 2 3h 2 k 2 + 和 Ev(k)= - ; 3m 0 6m 0 m0 m0

m0 为电子惯性质量,k1=1/2a;a=0.314nm。试求: ①禁带宽度; ②导带底电子有效质量; ③价带顶电子有效质量; ④价带顶电子跃迁到导带底时准动量的变化。 [解] ① 禁带宽度 Eg 根据 值: kmin=

[ 110] , [ 101] , [ 011] , 轾 臌1 10

轾 臌10 1 , 轾 臌0 1 1 ;

,

[1 10], 轾 10 1 , 轾 臌 臌01 1 , 轾 臌110 , 轾 臌101 , 轾 臌0 11 ; 则由解析几何定理得, B 与 k3 的夹角余弦 cos θ 为: cos θ = 式中, B = b1i + b2 j + b3k . 对不同方向的旋转椭球面取不同的一组 (k1 , k2 , k3 ) .

半导体物理课后习题(保密)

解: 须先求出本征载流子浓度ni,即

代入数据得,ni=1.86 ×1013cm-3 根据电中性条件有 p0+ND+=n0+NA-

ni

q( n p )

i

1 i ( n p )

联立 载流子浓度公式

n0p0=ni2

可求解得 n0=3.89 ×1013cm-3, p0=8.89 ×1012cm-3 所以样品的电导率为:

解: 由图3-7查得T=500k时,Si的本征载流子浓度ni=3.5×1014cm-3 联立方程

p0=ni2/n0

解得, ND=3.5×1014cm-3时,n0≈4.3×1014cm-3, p0=2.8×1014cm-3 —— n0,p0差别不显著,杂质导电特性不很明显 ND=1012cm-3时,n0≈ni=3.5×1014cm-3, p0=3.5×1014cm-3,即n0=p0. —— 进入本征 半导体材料在某一温度下所处的区域与杂质浓度相关 或 杂质浓度不同,材料进入同一区域所需要的温度不一样。

m0为电子惯性质量,k1=1/2a; a=0.314nm。试求: (1)禁带宽度; (2)导带底电子有效质量; (3)价带顶电子有效质量; (4)价带顶电子跃迁到导带底时准动量的变化。

练习2-课后习题2

第一章 半导体中的电子状态

2.晶格常数为0.25nm的一维晶格,当外加102V/m和107V/m 的电 场时,试分别计算电子自能带底运动到能带顶所需的时间。

作业-课后习题14

第三章 半导体中载流子的统计分布

计算含有施主杂质浓度ND=9×1015cm-3与受主杂质浓度为1.1×1016cm-3 的硅在室温时的电子和空穴浓度以及费米能级的位置。

半导体习题

补充习题1, 原子中的电子和晶体中电子受势场作用情况及运动情况有何不同?原子中内层电子和外层电子参与共有化运动有何不同?(1)原子中的电子是受到原子核和其他电子的势场的作用下做圆周运动晶体中的电子是在严格周期性排列的原子间做共有化运动(2)外层电子轨道交叠程度大,共有化运动显著内层电子轨道交叠程度小,共有化运动较弱2, 描述半导体中电子运动为什么要引入“有效质量”的概念?用电子的惯用质量m 0描述能带中电子运动有何局限性?有效质量概括了半导体内部势场的作用,使得在解决半导体中电子在外力作用下的运动规律时,可以不涉及半导体内部势场的作用。

3, 以硅的本征激发为例,说明由价带导带构成的半导体能带图的物理意义、价带和导带中能级与硅晶格结构中价键上电子和自由运动电子有何联系?为什么电子从其价键挣脱出来所需的最小能量就是半导体的禁带宽度?4, 若体心立方晶格能带为0()8(cos cos cos )x y z E k E A J ak ak ak πππ=--,求:(1) 体心立方晶格的能带宽度(2) 能带底部和顶部电子的有效质量(3) 画出沿k x 方向(k y =k z =0)E(k x )和v (k x )的曲线5, 杂质能级为什么位于禁带之中?能带图上如何表示中性和电离杂质?杂质电离后在半导体中产生些什么?6, 说明杂质补偿在制作半导体器件中的重大作用。

7, 试解释重掺杂半导体使禁带变窄的原因。

8, 试述硅晶体经过辐照后产生的影响。

9, 说明费米能级E F 的物理意义。

根据E F 位置,如何计算半导体中电子和空穴浓度?如何理解费米能级EF 是掺杂类型和掺杂程度的标志?10, 半导体的电阻温度系数是正的还是负的?为什么?分别说明本征和掺杂(非简并)情况。

11, 半导体中如果同时存在着施主杂质和受主杂质并且杂质全部电离时,说明为什么在室温下其载流子浓度为两者之差,而对迁移率的影响却是两者之和?12, 半导体的平衡状态和非平衡状态有何不同?什么叫非平衡载流子?为什么说非平衡载流子一般是指非平衡少数载流子?。

半导体物理习题

半导体物理习题半导体物理习题:1第一章半导体中的电子状态例题:第一章半导体中的电子状态例1. 证明:对于能带中的电子,K状态和-K状态的电子速度大小相等,方向相反。

即: v(k)= -v(-k),并解释为什么无外场时,晶体总电流等于零。

思路与解:K状态电子的速度为:(1)同理,-K状态电子的速度则为:(2)从一维情况容易看出:(3)同理有:(4)(5)将式(3)(4)(5)代入式(2)后得:(6)利用(1)式即得:v(-k)= -v(k) 因为电子占据某个状态的几率只同该状态的能量有关,即: E(k)=E(-k)故电子占有k状态和-k状态的几率相同,且 v(k)=-v(-k),故这两个状态上的电子电流相互抵消,晶体中总电流为零。

评析:该题从晶体中作共有化运动电子的平均漂移速度与能量E的关系以及相同能量状态电子占有的机率相同出发,证明K状态和-K状态的电子速度大小相等,方向相反,以及无电场时,晶体总电流为零。

例2. 已知一维晶体的电子能带可写成:式中,a为晶格常数。

试求:能带的宽度;能带底部和顶部电子的有效质量。

思路与解:(1)由E(k)关系得:=(1)(2)令得:当时,代入(2)得:对应E(k)的极小值。

当时,代入(2)得:对应E(k)的极大值。

根据上述结果,求得和即可求得能带宽度。

故:能带宽度能带底部和顶部电子的有效质量:评析:本题根据能带宽度为能带顶和能带底的能量之差,即能量最大值和最小值之差。

习题: 1.什么叫本征激发?温度越高,本征激发的载流子越多,为什么?试定性说明之。

2.试定性说明Ge、Si的禁带宽度具有负温度系数的原因。

3.试指出空穴的主要特征。

4.简述Ge、Si和GaAs的能带结构的主要特征。

5.某一维晶体的电子能带为其中E0=3eV,晶格常数a=5×10-11m。

求:能带宽度;能带底和能带顶的有效质量。

半导体物理习题:2第二章半导体中的杂质和缺陷能级例题:第二章半导体中的杂质与缺陷能级例1. 半导体硅单晶的介电常数=11.8,电子和空穴的有效质量各为=0.97,=0.19和=0.16,=0.53,利用类氢模型估计:(1)施主和受主电离能; (2)基态电子轨道半径。

第1章 半导体器件习题及答案

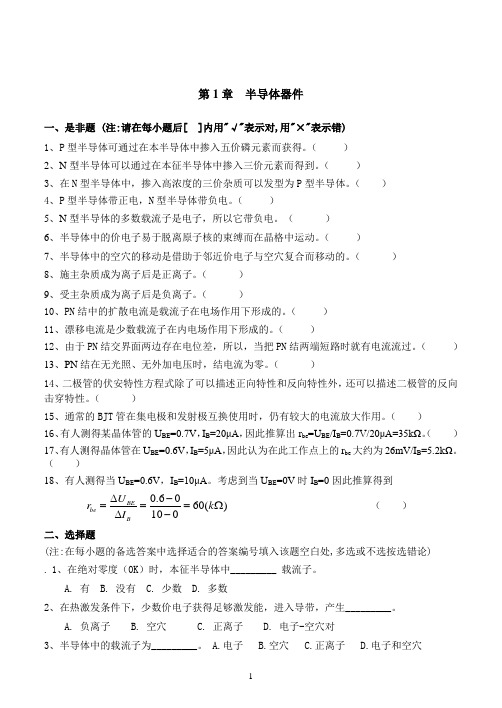

第1章 半导体器件一、是非题 (注:请在每小题后[ ]内用"√"表示对,用"×"表示错) 1、P 型半导体可通过在本半导体中掺入五价磷元素而获得。

( ) 2、N 型半导体可以通过在本征半导体中掺入三价元素而得到。

( ) 3、在N 型半导体中,掺入高浓度的三价杂质可以发型为P 型半导体。

( ) 4、P 型半导体带正电,N 型半导体带负电。

( )5、N 型半导体的多数载流子是电子,所以它带负电。

( )6、半导体中的价电子易于脱离原子核的束缚而在晶格中运动。

( )7、半导体中的空穴的移动是借助于邻近价电子与空穴复合而移动的。

( )8、施主杂质成为离子后是正离子。

( )9、受主杂质成为离子后是负离子。

( )10、PN 结中的扩散电流是载流子在电场作用下形成的。

( ) 11、漂移电流是少数载流子在内电场作用下形成的。

( )12、由于PN 结交界面两边存在电位差,所以,当把PN 结两端短路时就有电流流过。

( ) 13、PN 结在无光照、无外加电压时,结电流为零。

( )14、二极管的伏安特性方程式除了可以描述正向特性和反向特性外,还可以描述二极管的反向击穿特性。

( ) 15、通常的BJT 管在集电极和发射极互换使用时,仍有较大的电流放大作用。

( ) 16、有人测得某晶体管的U BE =0.7V ,I B =20μA ,因此推算出r be =U BE /I B =0.7V/20μA=35kΩ。

( ) 17、有人测得晶体管在U BE =0.6V ,I B =5μA ,因此认为在此工作点上的r be 大约为26mV/I B =5.2kΩ。

( )18、有人测得当U BE =0.6V ,I B =10μA 。

考虑到当U BE =0V 时I B =0因此推算得到0.6060()100BE be B U r k I ∆-===Ω∆- ( )二、选择题(注:在每小题的备选答案中选择适合的答案编号填入该题空白处,多选或不选按选错论) . 1、在绝对零度(0K )时,本征半导体中_________ 载流子。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一篇半导体中的电子状态习题1-1、 什么叫本征激发?温度越高,本征激发的载流子越多,为什么?试定性说明之。

解:在一定温度下,价带电子获得足够的能量(≥E g )被激发到导带成为导电电子的过程就是本征激发。

其结果是在半导体中出现成对的电子-空穴对。

如果温度升高,则禁带宽度变窄,跃迁所需的能量变小,将会有更多的电子被激发到导带中。

1-2、 试定性说明Ge 、Si 的禁带宽度具有负温度系数的原因。

解:电子的共有化运动导致孤立原子的能级形成能带,即允带和禁带。

温度升高,则电子的共有化运动加剧,导致允带进一步分裂、变宽;允带变宽,则导致允带与允带之间的禁带相对变窄。

反之,温度降低,将导致禁带变宽。

因此,Ge 、Si 的禁带宽度具有负温度系数。

1-3、 试指出空穴的主要特征。

解:空穴是未被电子占据的空量子态,被用来描述半满带中的大量电子的集体运动状态,是准粒子。

主要特征如下:A 、荷正电:+q ;B 、空穴浓度表示为p (电子浓度表示为n );C 、E P =-E nD 、m P *=-m n *。

1-4、 简述Ge 、Si 和GaAS 的能带结构的主要特征。

解:(1) Ge 、Si:a )Eg (Si :0K) = 1.21eV ;Eg (Ge :0K) = 1.170eV ;b )间接能隙结构c )禁带宽度E g 随温度增加而减小;(2) GaAs :a )E g (300K )= 1.428eV ,Eg (0K) = 1.522eV ;b )直接能隙结构;c )Eg 负温度系数特性: dE g /dT = -3.95×10-4eV/K ;1-5某一维晶体的电子能带为[])sin(3.0)cos(1.01)(0ka ka E k E --=其中E 0=3eV ,晶格常数a=5х10-11m 。

求:(1)能带宽度;(2)能带底和能带顶的有效质量。

解:(1) 由题意得:[][])sin(3)cos(1.0)cos(3)sin(1.002220ka ka E a k d dE ka ka aE dk dE+=-=eVE E E E a kd dE a k E a kd dE a k a k a k ka tg dk dE ooo o 1384.1min max ,01028.2)4349.198sin 34349.198(cos 1.0,4349.198,01028.2)4349.18sin 34349.18(cos 1.0,4349.184349.198,4349.1831,04002222400222121=-=∆<⨯-=+==>⨯=+====∴==--则能带宽度对应能带极大值。

当对应能带极小值;当)(得令(2)()()()()()()⎪⎪⎪⎩⎪⎪⎪⎨⎧⨯-=⎥⎥⎦⎤⎢⎢⎣⎡⨯⨯-=⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫⎝⎛=⨯=⎥⎥⎦⎤⎢⎢⎣⎡⨯⨯=⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫⎝⎛=----------kg k d dE h m kg k d dE h m k n k n 271234401222*271234401222*10925.110625.61028.2110925.110625.61028.2121带顶带底则答:能带宽度约为1.1384Ev ,能带顶部电子的有效质量约为1.925x10-27kg ,能带底部电子的有效质量约为-1.925x10-27kg 。

第二篇 半导体中的杂质和缺陷能级习题2-1、什么叫浅能级杂质?它们电离后有何特点? 解:浅能级杂质是指其杂质电离能远小于本征半导体的禁带宽度的杂质。

它们电离后将成为带正电(电离施主)或带负电(电离受主)的离子,并同时向导带提供电子或向价带提供空穴。

2-2、什么叫施主?什么叫施主电离?施主电离前后有何特征?试举例说明之,并用能带图表征出n 型半导体。

解:半导体中掺入施主杂质后,施主电离后将成为带正电离子,并同时向导带提供电子,这种杂质就叫施主。

施主电离成为带正电离子(中心)的过程就叫施主电离。

施主电离前不带电,电离后带正电。

例如,在Si 中掺P ,P 为Ⅴ族元素,本征半导体Si为Ⅳ族元素,P掺入Si中后,P的最外层电子有四个与Si的最外层四个电子配对成为共价电子,而P的第五个外层电子将受到热激发挣脱原子实的束缚进入导带成为自由电子。

这个过程就是施主电离。

n型半导体的能带图如图所示:其费米能级位于禁带上方2-3、什么叫受主?什么叫受主电离?受主电离前后有何特征?试举例说明之,并用能带图表征出p型半导体。

解:半导体中掺入受主杂质后,受主电离后将成为带负电的离子,并同时向价带提供空穴,这种杂质就叫受主。

受主电离成为带负电的离子(中心)的过程就叫受主电离。

受主电离前带不带电,电离后带负电。

例如,在Si中掺B,B为Ⅲ族元素,而本征半导体Si为Ⅳ族元素,P掺入B中后,B的最外层三个电子与Si的最外层四个电子配对成为共价电子,而B倾向于接受一个由价带热激发的电子。

这个过程就是受主电离。

p型半导体的能带图如图所示:其费米能级位于禁带下方2-4、掺杂半导体与本征半导体之间有何差异?试举例说明掺杂对半导体的导电性能的影响。

解:在纯净的半导体中掺入杂质后,可以控制半导体的导电特性。

掺杂半导体又分为n型半导体和p型半导体。

例如,在常温情况下,本征Si中的电子浓度和空穴浓度均为1.5╳1010cm-3。

当在Si中掺入1.0╳1016cm-3后,半导体中的电子浓度将变为1.0╳1016cm-3,而空穴浓度将近似为2.25╳104cm-3。

半导体中的多数载流子是电子,而少数载流子是空穴。

2-5、两性杂质和其它杂质有何异同?解:两性杂质是指在半导体中既可作施主又可作受主的杂质。

如Ⅲ-Ⅴ族GaAs 中掺Ⅳ族Si。

如果Si替位Ⅲ族As,则Si为施主;如果Si替位Ⅴ族Ga,则Si 为受主。

所掺入的杂质具体是起施主还是受主与工艺有关。

2-6、深能级杂质和浅能级杂质对半导体有何影响?解:深能级杂质在半导体中起复合中心或陷阱的作用。

浅能级杂质在半导体中起施主或受主的作用。

2-7、何谓杂质补偿?杂质补偿的意义何在?当半导体中既有施主又有受主时,施主和受主将先互相抵消,剩余的杂质最后电离,这就是杂质补偿。

利用杂质补偿效应,可以根据需要改变半导体中某个区域的导电类型,制造各种器件。

第三篇 半导体中载流子的统计分布3-1、对于某n 型半导体,试证明其费米能级在其本征半导体的费米能级之上。

即E Fn >E Fi 。

证明:设n n 为n 型半导体的电子浓度,n i 为本征半导体的电子浓度。

显然n n > n iin i nF F F c c F c c E E Tk E E N Tk E E N >⎪⎪⎭⎫⎝⎛--⋅>⎪⎪⎭⎫ ⎝⎛--⋅则即00exp exp即得证。

3-2、试分别定性定量说明:(1) 在一定的温度下,对本征材料而言,材料的禁带宽度越窄,载流子浓度越高;(2) 对一定的材料,当掺杂浓度一定时,温度越高,载流子浓度越高。

3-2、解:(1) 在一定的温度下,对本征材料而言,材料的禁带宽度越窄,则跃迁所需的能量越小,所以受激发的载流子浓度随着禁带宽度的变窄而增加。

由公式:Tk E v c i g eN N n 02-=也可知道,温度不变而减少本征材料的禁带宽度,上式中的指数项将因此而增加,从而使得载流子浓度因此而增加。

(2)对一定的材料,当掺杂浓度一定时,温度越高,受激发的载流子将因此而增加。

由公式可知,这时两式中的指数项将因此而增加,从而导致载流子浓度增加。

3-3、若两块Si 样品中的电子浓度分别为2.25×1010cm -3和6.8×1016cm -3,试分别求出其中的空穴的浓度和费米能级的相对位置,并判断样品的导电类型。

假如再在其中都掺入浓度为2.25×1016cm -3的受主杂质,这两块样品的导电类型又将怎样?3-3、解:由 200i n p n =得:()()()()⎪⎪⎩⎪⎪⎨⎧⨯≈⨯⨯==⨯=⨯⨯==--3316210022023101021001201103.3108.6105.1100.11025.2105.1cm n n p cm n np ii可见,型半导体本征半导体n p n p n →>→≈02020101又因为 Tk E E v v F eN p 00--=,则⎪⎪⎩⎪⎪⎨⎧+=⎪⎪⎭⎫ ⎝⎛⨯⨯⋅+=⎪⎪⎭⎫ ⎝⎛⋅+=+≈⎪⎪⎭⎫⎝⎛⨯⨯⋅+=⎪⎪⎭⎫ ⎝⎛⋅+=eV E E p N T k E E eV E E p N T k E E v v n v F v v v v F 331.0103.3101.1ln 026.0ln 234.0100.1101.1ln 026.0ln 319020210190101 假如再在其中都掺入浓度为2.25×1016cm -3的受主杂质,那么将出现杂质补偿,第一种半导体补偿后将变为p 型半导体,第二种半导体补偿后将近似为本征半导体。

答:第一种半导体中的空穴的浓度为 1.1x1010cm -3,费米能级在价带上方0.234eV 处;第一种半导体中的空穴的浓度为3.3x103cm -3,费米能级在价带上方0.331eV 处。

掺入浓度为2.25×1016cm -3的受主杂质后,第一种半导体补偿后将变为p 型半导体,第二种半导体补偿后将近似为本征半导体。

3-4、含受主浓度为8.0×106cm -3和施主浓度为7.25×1017cm -3的Si 材料,试求温度分别为300K 和400K 时此材料的载流子浓度和费米能级的相对位置。

⎪⎪⎭⎫⎝⎛--=⎪⎪⎭⎫ ⎝⎛--⋅=Tk E E N p Tk E E N n VF V Fc c 0000exp exp 和3-4、解:由于杂质基本全电离,杂质补偿之后,有效施主浓度 317*1025.7-⨯≈-=cm N N N A D D则300K 时,电子浓度 ()31701025.7300-⨯=≈cm N K n D空穴浓度 ()()()3217210001011.31025.7105.1300-⨯≈⨯⨯==cm n n K p i费米能级为:()eVE E p N T k E E v v v VF 3896.01011.3100.1ln 026.0ln 21900+=⎥⎦⎤⎢⎣⎡⨯⨯⋅+=⎪⎪⎭⎫⎝⎛⋅+=在400K 时,根据电中性条件 *00D N p n +=和 20i p n p n =得到:()()()()()()⎪⎪⎩⎪⎪⎨⎧⨯=⨯⨯==⨯≈⨯+⨯+⨯-=++-=--317821320382132171722*010249.7103795.1100.1103795.12100.141025.71025.724*cmp n n cm n N N p p i i D D费米能级为:()()eV E E p K K K N T k E E v v p v v F 0819.01025.7300400101.1ln 026.0300400300ln 172319230+=⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡⨯⎪⎭⎫ ⎝⎛⨯⨯⋅+=⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡⎪⎭⎫ ⎝⎛⨯⋅+=答:300K 时此材料的电子浓度和空穴浓度分别为7.25 x1017cm -3和3.11x102cm -3,费米能级在价带上方0.3896eV 处;400 K 时此材料的电子浓度和空穴浓度分别近似为为7.248 x1017cm -3和1.3795x108cm -3,费米能级在价带上方0.08196eV 处。