杭电计组实验5-存储器设计实验资料讲解

杭电计组实验-存储器设计实验

杭电计组实验-存储器设计实验————————————————————————————————作者:————————————————————————————————日期:实验报告2018 年 5 月 5 日成绩:姓名阳光男学号16041321 班级16052317专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号5实验名称《实验五存储器设计实验》实验时间2018/5/12实验地点1教211实验设备号个人电脑、Nexys3开发板一、实验程序源代码存储器顶层电路代码:module top_RAM_B(Mem_Addr,C,Mem_Write,Clk,LED);input [7:2]Mem_Addr;//开关的3、4、5、6、7、8位input Mem_Write,Clk;//clk为按键C9,读写使能信号为按键C4,0为读,1为写input [1:0]C;//选择写入数据+读操作时选择显示字节,为开关1、2位output reg [7:0]LED;wire [31:0]M_R_Data;//存在存储器里的32位读出数据reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据RAM_B test_ram (.clka(Clk), //输入时钟信号.wea(Mem_Write), //输入读写信号.addra(Mem_Addr[7:2]), //输入5位地址信号.dina(M_W_Data), //写入32位数据.douta(M_R_Data) //读出32位数据);always@(*)beginLED=0;//初始化M_W_Data=0;//初始化if(!Mem_Write)//读操作begincase(C)2'b00:LED=M_R_Data[7:0];//读出数据的0-7位2'b01:LED=M_R_Data[15:8];//读出数据的8-15位2'b10:LED=M_R_Data[23:16];//读出数据的16-23位2'b11:LED=M_R_Data[31:24];//读出数据的24-31位endcaseendelsebegincase(C)2'b00:M_W_Data=32'h0055_7523;//写入第一个数据2'b01:M_W_Data=32'h1234_5678;//写入第二个数据2'b10:M_W_Data=32'h8765_4321;//写入第三个数据2'b11:M_W_Data=32'hffff_ffff;//写入第四个数据endcaseendendendmodule测试代码:module test;// Inputsreg clka;reg [0:0] wea;reg [5:0] addra;reg [31:0] dina;// Outputswire [31:0] douta;// Instantiate the Unit Under Test (UUT)RAM_B uut (.clka(clka),.wea(wea),.addra(addra),.dina(dina),.douta(douta));initial begin// Initialize Inputsclka = 0;wea = 0;addra = 0;dina = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus hereclka = 1;wea = 0;addra = 6'b000001;dina = 32'h0000_0003;#100;clka = 0;wea = 0;addra = 6'b000001;dina = 32'h0000_0607;#100;clka = 1;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;#100;clka = 0;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;endendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "Clk" LOC = C9;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[2]" LOC = U15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "Mem_Addr[7]" LOC = U8;NET "Mem_Addr[6]" LOC = N8;NET "Mem_Addr[5]" LOC = M8;NET "Mem_Addr[4]" LOC = V9;NET "Mem_Addr[2]" LOC = T10;NET "Mem_Write" LOC = C4;NET "Mem_Addr[3]" LOC = T9;NET "C[1]" LOC = T5;NET "C[0]" LOC = V8;NET "LED[7]" LOC = T11;NET "LED[5]" LOC = N11;NET "LED[6]" LOC = R11;五、思考与探索(1)读操作实验结果记录表存储器地址初始化数据读出数据写入新数据读出数据5’b000000 32’b0000000032’b0000000032'h0055_752332'h0055_7523 5’b000001 32’b0000000132’b0000000132'h0055_752332'h0055_7523 5’b000002 32’b0000000232’b0000000232'h0055_752332'h0055_7523 5’b000003 32’b0000000332’b0000000332'h0055_752332'h0055_7523 5’b000004 32’b0000000432’b0000000432'h0055_752332'h0055_7523 5’b000005 32’b0000000532’b0000000532'h0055_752332'h0055_7523 5’b000006 32’b0000000632’b0000000632'h0055_752332'h0055_7523 5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523 (2)答:这些单元的数据已经被改写了。

杭电计算机组成原理寄存器堆设计实验

杭电计算机组成原理寄存器堆设计实验计算机组成原理是计算机科学与技术的基础课程之一,它涉及到计算机的基本组成部分和原理。

在这门课程中,学生通常需要进行一系列的实验来加深对计算机组成原理的理解和应用。

其中之一是关于寄存器堆的设计实验。

寄存器堆是计算机中重要的组成部分之一,它用于存储、读取和写入数据。

在计算机中,数据通常被存储在寄存器中,然后进行各种操作。

因此,设计一个高效可靠的寄存器堆对于计算机的性能至关重要。

根据实验要求,我们需要设计一个8位的寄存器堆,并实现读取、写入和清零等操作。

以下是针对该实验的设计思路和实施步骤。

首先,我们需要确定寄存器堆的结构。

由于该寄存器堆为8位宽度,我们选择使用一个8x8的存储单元阵列。

每个存储单元都可以存储一个8位的数据。

整个寄存器堆由8个存储单元组成,每个存储单元对应一个地址,即0~7接下来,我们需要设计寄存器堆的读写电路。

对于读操作,我们需要通过地址线来选择要读取的存储单元,并将其输出到数据线。

对于写操作,我们同样需要通过地址线来选择要写入的存储单元,并将数据线上的数据写入该存储单元。

为了实现这些操作,我们需要使用多路选择器和数据解码器。

在设计中,我们还需要考虑到时钟信号的输入,以确保读写操作在时钟的上升沿或下降沿进行。

此外,我们还需要添加清零功能,以便将寄存器堆的值重置为零。

为实现清零功能,我们可以将一个额外的输入线与所有存储单元的清零输入连接。

在实施阶段,我们需要使用Verilog或其他硬件描述语言来实现设计。

在代码中,我们首先声明一个8位宽的存储单元阵列作为寄存器堆的基本组成部分。

然后,我们定义读写电路,包括地址线、数据线、多路选择器和数据解码器。

最后,我们添加时钟信号和清零功能。

在完成设计后,我们可以通过仿真工具进行验证。

通过输入不同的数据和地址,观察输出结果是否符合预期。

如果存在问题,我们可以进行调试并进行必要的修改。

一旦仿真结果正确无误,我们就可以开始进行硬件实验了。

实验五存储器连接(6116的使用)

实验五 存储器连接(6116的使用)【实验名称】存储器连接(6116的使用)。

【实验目的】 掌握存储器译码及读写的方法。

【实验原理】 微处理器通过数据总线、地址总线及控制总线与存储器连接,如下图所示:地址总线为地址信号,用来指明选中的存储单元地址。

数据总线为数据信号,它是微处理器送往存储器的信息或存储器送往微处理器的信息。

它包括指令和数据。

控制总线发出存储器读写信号,以便从ROM 、RAM 中读出指令或数据,或者向RAM 写入数据。

在微机系统中,常用的静态RAM 有6116、6264、62256等。

在本实验中使用的是6116。

6116为2K ╳8位的静态RAM ,其逻辑图如下:其中A 0~10为11根地址线,I/O 0~7为8根数据线,CS 为片选端,OE 为数据输出选通端,WR 为写信号端。

其工作方式见下表:FD-SJ86/88实验板上提供了一片6116用来作存储器读写实验。

在6116的上方三根跳线J57、J58、J59分别用来设置6116的片选端、读信号、写信号的连接状态。

当以短路块分别将J57、J58、J59上面两根针短路时,则6116片选端连接由U39产生的译码信号,其译码范围为0A0000H~0A07FFH,因6116为2K存储器,所以地址0A0000H~0A07FFH和0A0800H~0A0FFFH重叠。

6116的读写信号则分别接到系统总线上的存储器读写信号。

其数据通过74LS245(U38)接到系统的数据总线上。

【实验内容】在FD-SJ86/88实验板上的6116芯片内写入一些数据,然后读出显示在屏幕上以验证正确与否。

【实验连线】① 6264的地址线J8(A0~A10)接总线上的地址线A0~A10。

② J57、J58、J59的下面的两个脚以短路块连接。

【实验程序】DATA SEGMENTMESSAGE DB 'PLEASE ENTER A KEY TO SHOW THE CONTENTS',0DH,0AH,'$'DATA ENDSSTACK SEGMENT STACKSTA DW 50 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATASTART: MOV AX,DATAMOV DS,AXMOV AX,STACKMOV SS,AXMOV SP,TOPMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26MOV DL,40HWRITE: INC DLMOV ES:[BX],DLINC BXCMP DL,5AHJNZ SS1MOV DL,40HSS1: LOOP WRITEMOV DX,OFFSET MESSAGEMOV AH,9INT 21HMOV AH,01HINT 21HMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26READ: MOV DL,ES:[BX]MOV AH,02HINT 21HINC BXLOOP READMOV AH,4CHINT 21HCODE ENDSEND START【思考题】将字符‘0’~‘9’写入存储器,再将其读出,应如何修改程序?。

计组存储器实验实验报告(3篇)

第1篇一、实验目的1. 理解存储器的基本组成和工作原理;2. 掌握存储器的读写操作过程;3. 熟悉存储器芯片的引脚功能及连接方式;4. 了解存储器与CPU的交互过程。

二、实验环境1. 实验设备:TD-CMA计算机组成原理实验箱、计算机;2. 实验软件:无。

三、实验原理1. 存储器由地址线、数据线、控制线、存储单元等组成;2. 地址线用于指定存储单元的位置,数据线用于传输数据,控制线用于控制读写操作;3. 存储器芯片的引脚功能:地址线、数据线、片选线、读线、写线等;4. 存储器与CPU的交互过程:CPU通过地址线访问存储器,通过控制线控制读写操作,通过数据线进行数据传输。

四、实验内容1. 连线:按照实验原理图连接实验箱中的存储器芯片、地址线、数据线、控制线等;2. 写入操作:将数据从输入单元IN输入到地址寄存器AR中,然后通过控制线将数据写入存储器的指定单元;3. 读取操作:通过地址线指定存储单元,通过控制线读取数据,然后通过数据线将数据输出到输出单元OUT;4. 实验步骤:a. 连接实验一(输入、输出实验)的全部连线;b. 按实验逻辑原理图连接两根信号低电平有效信号线;c. 连接A7-A0 8根地址线;d. 连接13-AR正脉冲有效信号线;e. 在输入数据开关上拨一个地址数据(如00000001,即16进制数01H),拨下开关,把地址数据送总线;f. 拨动一下B-AR开关,实现0-1-0”,产生一个正脉冲,把地址数据送地址寄存器AR保存;g. 在输入数据开关上拨一个实验数据(如10000000,即16进制数80H),拨下控制开关,把实验数据送到总线;h. 拨动控制开关,即实现1-0-1”,产生一个负脉冲,把实验数据存入存储器的01H号单元;i. 按表2-11所示的地址数据和实验数据,重复上述步骤。

五、实验结果与分析1. 通过实验,成功实现了存储器的读写操作;2. 观察到地址线、数据线、控制线在读写操作中的协同作用;3. 理解了存储器芯片的引脚功能及连接方式;4. 掌握了存储器与CPU的交互过程。

计算机组成原理5 存储器实验

实验5 存储器实验一、实验目的1.掌握静态存储随机存储器RAM的工作特性2.掌握静态存储随机存储器RAM的读写方法二、实验设备74LS273组件一片,静态存储器MEMORY 6116组件一片(是一个2k×8的静态存储器。

在本实验中只使用8位地址),单脉冲一个,开关若干,灯泡若干三、实验原理本实验所用的静态存储器由一片6116(2K × 8)构成,其数据线接至数据开关,地址线由地址锁存器(74LS373)给出。

因地址寄存器为8位,接入6116的地址A7-A0,而高三位A8-A10接地,所以其实际容量为256字节。

6116有三个控制线:CE(片选线)、OE(读线)、WE(写线)。

当片选CE=0,读信号OE=0时,进行读操作,当片选CE=0,写信号WE=1时,进行写操作。

由于本实验中将OE常接地,这样,当CE=0、WE=0时进行写操作,CE=0、WE=1时进行读操作,写时间与T3脉冲宽度一致。

四、实验步骤1.选择实验设备:根据实验原理图,将所需要的组件从组件列表中拖到实验设计流程栏中。

2. 搭建实验流程:将已选择的组件进行连线, 74LS273的0―7号输入引脚(数据端)、9号引脚(复位端)分别接到开关上,8号引脚接单脉冲信号,11-18号输出引脚接到静态MEMORY的0-7号地址输入引脚。

静态MEMORY的高3位地址输入引脚8―10统一置0,由开关控制,使存储器实际容量为256个字节。

11-13号使能端(CE 、WE、 OE)分别由开关控制,14-21号数据端同时接入开关和灯泡,进行读写操作,开关控制欲写入存储器的数据,灯泡用于从存储器读出数据的显示。

实验流程图如图6所示。

3. 设置相应芯片的控制位.( 273的9号引脚为1,6116的CE=1,WE=1,OE=0.)4. 写入数据:点击运行按钮,74LS273的连接的地址数据开关作为地址输入端可以自己设置,设置完毕后,双击单脉冲信号,将地址数据输入到74LS273里面去。

实验5存储器读写实验讲述

E/M=0 LDAR=1

X2X1X0=011

执行上述流程总线单元应显示11h, 若正确可按上述流程读出01h~05h单元的内容。

2.存储器程序段读写操作

(1)程序段写操作

PC装载写操作流程:

数据来源 I/O

置地址 S7~S0=00

打PC 00→PC

置数据 S7~S0=55

写程序 55→[00]

X2X1X0XP =1000

00h~05h单元依次写入11 22 33 44 55 66

。

置地址 S7~S0=00h I/O=0000h

打地址 00→AR

置数据

S7~S0=11h

写数据 11→[00]

关存储器 写

令MWR=1

X2X1X0XP=1000

LDAR=0 按【单拍】

按钮

LDAR=1 E/M=0

MWR=0 按【单拍】

按钮

Addr地址段定义:0=AR指针 ,1=PC指针

7

MWR

K21(M21)

存储器写使能:0=存储器写, 1=存储器读

8

LDAR

K19(M19)

AR地址寄存器写使能

低电平有 效

9

LDPC

K22(M22)

PC装载与PC+1

低电平有 效

五、实验内容 1.存储器数据段读写操作

(1)数据段写操作

• 按下流程从0址单元开始,向数据段

LDPC=0 MWR=1

按【单拍】按 钮

完成上流程,PC=01,总线单元显示AA,此时每按一次【单拍】按钮,PC+1,总线单 元依次显示23 45 67……等内容。

3.程序与数据存储器的分段读出

• 分段读出流程

存储器实验资料

******实验报告课程名称:计算机组织结构试姓名/学号:实验名称:实验五存储器实验讲解专业:软件工程班级:08 软件1班任课教师:指导教师:陈南南指导教师:实验日期:2010年11 月18 日实验成绩:批阅教师签字:、实验目的练习使用STEP 开关了解地址寄存器(AR)中地址的读入了解STOP 和STEP 开关的状态设置了解向存储器RAM 中存入数据的方法了解从存储器RAM 中读出数据的、实验设备静态存储器:一片6116 (2K*8 )芯片地址锁存器(74LS273)地址灯AD0 -AD7三态门(74LS245)三、实验原理实验所用的半导体静态存储器电路原理如图所示,实验中的静态存储器由一片6116 (2K*8)芯片构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0- AD7与地址线相连,显示地址线状况。

数据开关经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,在时序电路模块中有两个二进制开关“ STOP和“ STEP,将“ STOP开关置为“ RUN状态、“ STEP开关置为“ EXEC状态时,按动微动开关START则TS3端输出连续的方波信号当“ STOP开关置为RUN犬态,“STEP开关置为“ STEP状态时,每按动一次微动开关“ start ”,则TS3输出一个单脉冲,脉冲宽度与连续方式相同。

四、实验内容练习使用STEP开关往地址寄存器(AR)中存入地址设置STOP禾口STEP开关的状态:从数据开关送地址给总线:SW-B=___打开AR,关闭存储器:LDAR二_、CE=_按下Start产生T3脉冲关闭AR,关闭数据开关:LDAR二_、SW-B=往存储器RAM中存入数据1. 设定好要访问的存储器单元地址2. 从数据开关送数给总线:SW-B=3. 选择存储器片选信号:CE=_4. 选择读或写:WE= ___5. 按下Start产生T3脉冲6. 关闭存储器片选信号:CE=_7. 关闭数据开关:SW-B=___ (三)从存储器RAM中读出数据1. 设定好要访问的存储器单元地址2. 选择存储器片选信号:CE=_3. 选择读或写:WE= ___4. 按下Start产生T3脉冲5. 关闭存储器片选信号:CE=五、实验结果总结六、思考题在进行存储器操作(写/读)是不是必须先往地址寄存器(AR)存入所访问的存储器单元地址?T3在本实验中起了哪些作用,如何区分它们?在进行存储器读写操作时,CE和WE信号有没有先后顺序?为什么?。

实验五存储器实验指导PPT教学课件

A

B

C

uA5 uA4 uA3 uA2 uA1 uA0

15

14

13

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

2020/12/10

选择

LDRi LDDR1 LDDR2 LDIR LOAD LDAR

12

11

10

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

选择

RS-B RD-B RI-B 299-B ALU-B PC-B

实验五 存储器实验

2020/12/10

1

三态门

地址寄存器

主存芯片

2020/12/10

2

1)输入数据由8 位数据开关 KD0~KD7提供

2)进入地址寄存器 3)或做为数据进入主存芯片

2020/12/10

究竟进

入哪里, 由SWB、 LDAR等 信号组 合控3制

将外部数据总线EXD0~EXD7用8芯排

2020/12/10

9

实验七 基本模型机的设计与实现

2020/12/10

10

1)设计指令(其中操作码应与译码逻辑配合)

助记符

机器指令操作码

说明

IN

0000 0000 ; “外部开关量输入”KD0~KD7的开关状态→R0

ADD addr 0001 0000 ×××× ××××; R0+[addr]→R0

计算机组成原理存储器实验报告

计算机组成原理存储器实验报告一、实验目的本次实验的目的是通过实际操作,了解存储器的组成和工作原理,掌握存储器的读写操作。

二、实验原理存储器是计算机中的重要组成部分,用于存储程序和数据。

存储器按照存储介质的不同可以分为内存和外存,按照存储方式的不同可以分为随机存储器(RAM)和只读存储器(ROM)等。

本次实验使用的是随机存储器,随机存储器是一种易失性存储器,数据在断电后会丢失。

随机存储器按照存储单元的位数可以分为8位、16位、32位等,按照存储单元的数量可以分为256×8、512×16、1024×32等。

存储器的读写操作是通过地址总线、数据总线和控制总线来完成的。

地址总线用于传输存储单元的地址,数据总线用于传输数据,控制总线用于传输控制信号。

三、实验器材1. 存储器芯片:AT24C022. 单片机:STC89C523. 电源、示波器、万用表等四、实验步骤1. 连接电路将AT24C02存储器芯片和STC89C52单片机按照电路图连接好,接上电源。

2. 编写程序编写程序,实现对AT24C02存储器的读写操作。

程序中需要设置存储器的地址和数据,以及读写操作的控制信号。

3. 烧录程序将编写好的程序烧录到STC89C52单片机中。

4. 运行程序运行程序,观察存储器的读写操作是否正确。

五、实验结果经过实验,我们成功地实现了对AT24C02存储器的读写操作。

在程序中设置了存储器的地址和数据,通过控制信号实现了读写操作。

在读操作中,我们可以看到存储器中的数据被正确地读出;在写操作中,我们可以看到存储器中的数据被正确地写入。

六、实验总结通过本次实验,我们深入了解了存储器的组成和工作原理,掌握了存储器的读写操作。

同时,我们也学会了如何使用单片机来控制存储器的读写操作。

这对于我们深入学习计算机组成原理和嵌入式系统开发都具有重要的意义。

计算机组成原理存储器实验报告

计算机组成原理存储器实验报告

实验名称:计算机组成原理存储器实验

实验目的:通过实验验证存储器的基本原理,掌握存储器的基本操作方法。

实验原理:

计算机系统中的存储器是计算机系统中最基本的组成部分之一,也是最重要的组成部分之一。

存储器主要是用来储存计算机程序和数据的,计算机在执行程序时需要从存储器中读取指令和数据,将结果写回存储器中。

根据存储器的类型,存储器可以分为RAM和ROM两种类型。

RAM(Random Access Memory)是一种随机读写存储器,它能够随机存取任意地址的数据。

RAM又分为静态RAM(SRAM)和动态RAM (DRAM)两种类型。

其中,静态RAM(SRAM)是使用闪存电路实现的,其速度快、性能优异,但成本相对较高;而动态RAM(DRAM)是使用电容储存信息的,价格相对较低,但性能相对较差。

ROM(Read Only Memory)是只读存储器,它不能被随意修改,只能被读取。

ROM主要用来存储程序中需要固化的数据和指令,如BIOS和系统引导程序等。

实验步骤:

1. 打开计算机,将存储器连接到计算机主板上的插槽上。

2. 打开计算机并进入BIOS设置。

3. 在BIOS设置中进行存储器检测。

4. 在操作系统中查看存储器容量。

实验结果:

本次实验中,存储器检测结果显示正常,存储器容量为8GB,符合预期。

实验总结:

本次实验通过了解存储器的基本原理和操作方法,掌握了存储器

的检测和使用方法。

同时也深入了解了计算机系统中存储器的重要性和种类。

对于今后的计算机学习和使用将具有重要的帮助作用。

存储器设计实验报告

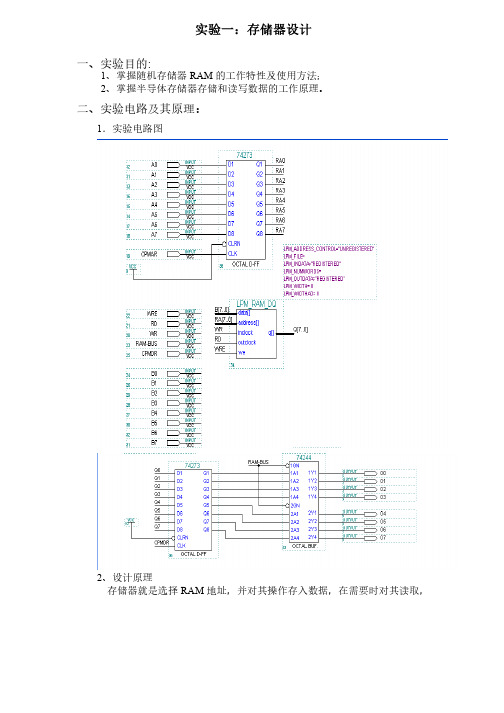

实验一:存储器设计一、实验目的:1、掌握随机存储器RAM 的工作特性及使用方法;的工作特性及使用方法;2、掌握半导体存储器存储和读写数据的工作原理。

、掌握半导体存储器存储和读写数据的工作原理。

二、实验电路及其原理:二、实验电路及其原理:1.实验电路图.实验电路图2、设计原理、设计原理存储器就是选择RAM 地址,并对其操作存入数据,在需要时对其读取,并把数据输出到数据总线。

实验思路大致为:并把数据输出到数据总线。

实验思路大致为: ①第一个74273用来接收数据存放在RAM 里的地址,即A0A0……7。

当CPMAR 有效时数据进入芯片。

有效时数据进入芯片。

②当WE=1,RD=0时,RAM 进行写操作,接收存储在74273里的数传到地址端口,同时接收从B0B0……7输入的数据传到数据端口,把数据写到相应RAM 里。

③当WE=0。

RD=1时,RAM 进行读操作,把对应存储单元的数据传到第二个74273,通过74273传到74244芯片输出。

芯片输出。

三、实验步骤三、实验步骤1、根据实验原理在maxplus 下连接电路图,对其进行编译。

下连接电路图,对其进行编译。

2、根据实验原理设计各个输入端的波形图,对其进行仿真模拟获得输出数据,仿真波形如下图。

仿真波形如下图。

四、仿真图四、仿真图说明:RAM 在WRE=1时才工作,为方便起见WRE 置为1;74244在RAM_BUS=0时工作,为方便起见RAM_BUS 置为0。

因CPMOR 为一个周期变换一次,为了不浪费存储空间,A0为两倍的周期变换,A1为四周期变换,以此类推。

存储的数据从11H 起依次增加。

起依次增加。

五、实验总结五、实验总结通过本次实验熟练掌握MAX+PLUS 软件,并运用该软件设计存储器,了解了存储器的结构设计和工作原理,并在理解的基础上自己设计了一个简单的存储器。

在之后的波形仿真图模拟时,发现自己不能很好控制各个芯片的片选信号,不知道如何使各个芯片在合适的时间工作,在经过仔细分析后,设置了上图的波形图,保证每个存储单元都可以存到数,保证每个存储单元都可以存到数,没有刚开始的浪费现象,没有刚开始的浪费现象,没有刚开始的浪费现象,数据在各个数数据在各个数据线之间的传输也正常,存储器的数据输出为两个周期输出一次(这是因为WR 、RD 为一个周期变换一次,在两个周期后才会读有效)。

计算机组成实验五-存储器读写实验

实验五存储器读写实验一、实验目的1.掌握存储器的工作特性。

2.数学静态存储器的操作过程,验证存储器的读写方法。

二、实验原理存储器是计算机的主要部件,用来保存程序和数据。

从工作方式上分类,存储器可分成易失性和非易失性存储器,易失性存储器中的数据在关电后将不复存在,非易失性储器又可分为动态存储器和静态存储器,动态存储器保存信息的时间只有2ms,工作时需要不断更新,既不断刷新数据;静态存储器只要不断电,信息是不会丢失的。

为简单起见,计算机组成实验用的是容量为2K的镜头存储器6116。

1.静态存储器芯片6116的逻辑功能6116是一种数据宽度为8位(8个二进制位),容量为2048字节的态存储器芯片,封在24引脚的封装中,封装型式如图2-7所示。

6116芯片有8根双向三态数据线D7-D0,所谓三态是指输入状态、输出状态和高阻状态,高阻状态数据线处于一种特殊的“断开”状态;11根地址线A10-A0,指示芯片内部2048个存储单元号;3根控制线片选控制信号,低电平时,芯片可进行读写操作,高电平时,芯片保存信息不能进行读写;为写入控制信号,低电平时,把数据线上的信息存入地址线A10-A0指示的存储单元中;为输出使能控制信号,低电平时,把地址线A10-A0指示的存储单元中的数据读出送到数据线上。

芯片控制信号逻辑功能见表2-9。

图2-7 存储器部件电路图2.存储器实验单元电力路因为在计算机组成原理实验中仅用了256个存储单元,所以6116芯片的三根地址线A11-A8接地也没有多片联用问题,片选信号接地使芯片总是处于被选中状态。

芯片的WE和信号分别连接实验台的存储器写信号和存储器读写信号,存储器实验单元逻辑电路如图2-7所示。

这种简化了控制过程的实验电路可方便实验进行,存储器实验单元电路控制信号逻辑功能见表2-10。

3.存储器实验电路存储器读/写实验需呀三部分电路共同完成:存储器单元(MEM UNIT)、地址寄存器单元(ADDRESS UNIT)和输入、输出单元(INPUT/OUTPUT UNIT)。

杭电计算机组成原理存储器设计实验5

NET "Mem_Addr[4]" LOC = N8;

NET "Mem_Addr[5]" LOC = U8;

NET "Mem_Addr[6]" LOC = V8;

NET "Mem_Addr[7]" LOC = T5;

NET "Mem_Write" LOC = B8;

数据记录和计算

实验仿真结果

结论(结果)

本实验的结果正确,根据自己写的coe文件中存储的数据进行操作,和实验四有很多的相似处,只是进行简单的读写的操作,实验的结果正确.能够根据操作,lED灯显示具体的数据.

试验心得与小结

本实验和实验四比较来说的话,更为简单,利用IP核中储存数据,我们就可以通过其中存储的数据进行操作,代码也是比较的简单,我们直接调用IP核生成的模块的代码,以至于操作也比较的方便.刚开始不熟悉使用IP核,了解了之后就比较简单了,比第四个实验自己写寄存器更简单.

2'b11:LED=M_R_Data[31:24];

endcase

end

else

begin

case(C)

2'b00:M_W_Data=32'h0002_0003;

2'b01:M_W_Data=32'h0002_0603;

2'b10:M_W_Data=32'h1234_5678;

2'b11:M_W_Data=32'hffff_ffff;

.dina(M_W_Data),

.douta(M_R_Data)

);

杭电计组实验-寄存器堆设计实验

杭电计组实验-寄存器堆设计实验————————————————————————————————作者:————————————————————————————————日期:实验报告2018 年 5 月12 日成绩:姓名阳光男学号班级专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号 4 实验名称《实验四寄存器堆设计》实验时间2018/5/12 实验地点1教211 实验设备号个人电脑、Nexys3开发板一、实验程序源代码1.寄存器堆模块代码:module Register_);input [4:0]R_Addr_A;input [4:0]R_Addr_B;input [4:0]W_Addr;input Write_Reg;input [31:0]W_Data;input Clk;input Reset;output [31:0]R_Data_A;output [31:0]R_Data_B;reg [31:0]REG_Files[0:31];reg [5:0]i;initial//仿真过程中的初始化beginfor(i=0;i<=31;i=i+1)REG_Files[i]=0;endassign R_Data_A=REG_Files[R_Addr_A]; assign R_Data_B=REG_Files[R_Addr_B]; always@(posedge Clk or posedge Reset)beginif(Reset)for(i=0;i<=31;i=i+1)REG_Files[i]=0;elseif(Write_Reg&&W_Addr!=0)REG_Files[W_Addr]=W_Data;endendmodule2.顶层电路模块代码:module Top_Register_);input [4:0]Addr;input [1:0]C1;//C1选择32位数据输出哪八位字节input Write_Reg,C2,Clk,Reset;//C2选择读A/B端口的数据output reg [7:0]LED;wire [31:0]R_Data_A,R_Data_B;reg [31:0]W_Data;reg[4:0] A,B;Register_(A,B,Addr,Write_Reg,W_Data,Clk,Reset,R_Data_A,R_Data_B); always@(Addr or Write_Reg or C1 or C2 or R_Data_A or R_Data_B) beginA=0;B=0;LED=0;W_Data=0;if(!Write_Reg)//读操作Write_Reg=0beginif(!C2)beginA=Addr;case(C1)2'b00:LED=R_Data_A[7:0];2'b01:LED=R_Data_A[15:8];2'b10:LED=R_Data_A[23:16];2'b11:LED=R_Data_A[31:24];endcaseendelsebeginB=Addr;case(C1)2'b00:LED=R_Data_B[7:0];2'b01:LED=R_Data_B[15:8];2'b10:LED=R_Data_B[23:16];2'b11:LED=R_Data_B[31:24];endcaseendendelse//写操作begincase(C1)2'b00:W_Data=32'h0000_0003;2'b01:W_Data=32'h0000_0607;2'b10:W_Data=32'hFFFF_FFFF;2'b11:W_Data=32'h1111_1234;endcaseendendendmodule3.测试代码module test;// Inputsreg [4:0] R_Addr_A;reg [4:0] R_Addr_B;reg [4:0] W_Addr;reg Write_Reg;reg [31:0] W_Data;reg Clk;reg Reset;// Outputswire [31:0] R_Data_A;wire [31:0] R_Data_B;// Instantiate the Unit Under Test (UUT) Register_ (.R_Addr_A(R_Addr_A),.R_Addr_B(R_Addr_B),.W_Addr(W_Addr),.Write_Reg(Write_Reg),.W_Data(W_Data),.Clk(Clk),.Reset(Reset),.R_Data_A(R_Data_A),.R_Data_B(R_Data_B));initial begin// Initialize InputsR_Addr_A = 0;R_Addr_B = 0;W_Addr = 0;Write_Reg = 0;W_Data = 0;Clk = 0;Reset = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus here#100;R_Addr_A = 0;R_Addr_B = 0;W_Addr = 5'b00001; Write_Reg = 1;W_Data = 32'h1111_1111; Clk = 1;Reset = 0;#100;R_Addr_A = 0;R_Addr_B = 0;W_Addr = 5'b00001; Write_Reg = 1;W_Data = 32'h1111_1111; Clk = 0;Reset = 0;#100;R_Addr_A = 0;R_Addr_B = 0;W_Addr = 5'b00010; Write_Reg = 1;W_Data = 32'h2222_2222; Clk = 1;Reset = 0;#100;R_Addr_A = 5'b00001;R_Addr_B = 5'b00010;W_Addr = 0;Write_Reg = 0;W_Data = 0;Clk = 0;Reset = 0;#100;R_Addr_A = 5'b00001;R_Addr_B = 5'b00010;W_Addr = 0;Write_Reg = 0;W_Data = 0;Clk = 0;Reset = 1;endendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "Clk" LOC = C9;NET "Reset" LOC = D9;NET "Write_Reg" LOC = T5;NET "C2" LOC = C4;# PlanAhead Generated physical constraintsNET "LED[7]" LOC = T11;NET "LED[6]" LOC = R11;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "LED[2]" LOC = U15;NET "LED[5]" LOC = N11;NET "Addr[0]" LOC = T10;NET "Addr[2]" LOC = V9;NET "Addr[3]" LOC = M8;NET "Addr[4]" LOC = N8;NET "C1[0]" LOC = U8;NET "C1[1]" LOC = V8;NET "Addr[1]" LOC = T9;五、思考与探索(1)实验四实验结果记录表寄存器地址写入数据读出数据$1 32'h0000_0003 32'h0000_0003$2 32'h0000_0607 32'h0000_0607$3 32'hFFFF_FFFF 32'hFFFF_FFFF $4 32'h1111_1234 32'h1111_1234$5 32'h0000_0003 32'h0000_0003$6 32'h0000_0607 32'h0000_0607$7 32'hFFFF_FFFF 32'hFFFF_FFFF $8 32'h1111_1234 32'h1111_1234。

计组实验-存储器实验

计算机组织与体系结构实验课程实验报告

实验名称存储器实验

一、实验目的

1、掌握FPGA中lpm_ROM只读存储器配置方法。

2、用文本编辑器编辑mif文件配置ROM,加载于ROM中;

3、验证FPGA中mega_lpm_ROM的功能。

二、实验所用仪器(或实验环境)

定制的lpm_rom input output

Quartus II(32-bit)仿真软件环境

三、实验基本原理及步骤(或方案设计及理论计算)

原理: ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。

CPU中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。

lpm_ROM有3组信号:地址信号address[ ]、数据信号q[ ]、时钟信号clk。

由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。

在这里,我们通过定制lpm_rom,然后加input端和output端实现电路。

最后通过设置输入端信号,并进行仿真得到结果。

步骤:

1、用图形编辑,绘制电路图。

2、进行波形仿真。

四、实验数据记录(或仿真及软件设计)

五、实验结果分析及回答问题(或测试环境及测试结果)遇到的问题:

1、运行模拟器之前,没有运行生成功能仿真网表

后来生成

得到结果。

杭电计组实验5存储器设计实验

杭州电子科技大学计算机学院

实验报告

实验项目:

课程名称:计算机组成原理与系统结构设计

姓名:学号:同组姓名:学号:实验位置(机号):

实验日期:指导教师:

addr = 6'b000001;

dina = 32'b 111111111111101101111;

#100;

clk = 1;

wea = 0;

addr = 6'b000001;

dina = 32'b 111111111111101101111;

#100;

clk = 0;

wea = 1;

addr = 6'b000001;

dina = 32'b 111111111111101101111;

#100;

clk = 1;

wea = 1;

addr = 6'b000001;

dina = 32'b 111111111111101101111;

end

endmodule

RTL图

二、结果

思考题:

(3)设计实现一个ROM,常规存储器是单端口存储器,每次只接收一个地址,访问一个存储单元,从中读取或写入一个字节或字。

主存储器是信息交换的中心,一方面CPU频繁地与主存交换信息,另一方面外设也较频繁地与主存交换信息,而单端口存储器每次只能接受一个访存者,或是读或是写,这就影响到存储器的整体工作速度。

双端口存储器具有两个彼此独立的读写口,每个读写口都有一套自己的地址寄存器和译码电路,可以并行地独立工作。

两个读写口可以按各自接收的地址同时读出或写入,或一。

实验5存储器读写实验

存储器读写过程

读操作

从存储器中读取数据的过程,通过地址码选中相应的单 元,将数据传输到数据总线。

写操作

将数据写入存储器的过程,同样通过地址码选中相应的 单元,将数据从数据总线传输到相应单元并保存。

03

实验步骤

实验准备

准备实验器材

存储器、数据线、电源适 配器、电脑等。

了解实验原理

熟悉存储器的读写原理和 实验要求。

在实验过程中,我学会了如何使用相关工具进行存储器的读写操作, 提高了实验操作技能。

加深理论知识应用

通过实际操作,我更加深入地理解了存储器相关的理论知识,如地 址码、数据总线、读写时序等。

实验不足与改进建议

01

02

03

实验时间紧张

由于时间安排的原因,我 在实验过程中感到时间比 较紧张,有些操作未能完 全展开。

安全与可靠性研究ቤተ መጻሕፍቲ ባይዱ

存储器的安全性和可靠性 对于数据保护至关重要, 未来可以加强这一领域的 研究。

THANKS

感谢观看

在实际应用中,需要考虑存储器的容量、读写速度和稳定性等因素,以选择合适的存储器芯片。 同时,还需要注意存储器的功耗和散热问题,以确保系统的稳定性和可靠性。

05

实验总结与展望

实验收获与体会

理解存储器工作原理

通过本次实验,我深入理解了存储器的工作原理,包括其基本架 构、读写操作、地址映射等。

掌握实验操作技能

实验5存储器读写实 验

目录

• 实验简介 • 存储器基础知识 • 实验步骤 • 实验结果与分析 • 实验总结与展望

01

实验简介

实验目的

掌握存储器的基本读写原 理。

学会使用存储器进行数据 存储和读取操作。

实验五_存储器设计

实验五存储器设计实验地点:EDA实验室901 实验时间:2014年5月23日实验人员:1240041 冯雅轩1240048 刘洁然实验五存储器设计一、实验目的1、掌握RAM和ROM的Verilog语言描述方法;2、学习用宏模块的方法定制RAM和ROM。

二、实验任务1、设计并实现一个128*16 的单端口的RAM;2、设计并实现一个128*16的ROM;3、设计并实现一个双端口的128*16的RAM4、设计并实现一个16*32的FIFO。

5、设计并实现正弦信号发生器,见“正弦信号发生器实验指南”。

三、实验步骤1 编写Verilog代码2功能仿真进行分析与综合,排除语法上的错误建立波形仿真文件,输入激励生成功能仿真网表进行功能仿真,观察输出结果3选择器件DE2_70开发板的使用者请选择EP2C70F896C64绑定管脚5 下载验证DE2_70开发板的下载:使用USB-Blaster进行下载四、实验内容五、实验思考题1.分析存储器采用三态输出的原因是什么?在第一个实验中,读出数据的改变是在数据地址readaddress或者存储器中存储数据发生变化时。

这是数据改变的条件,设置成三态门更高效,更合理。

2.单端口和双端口的区别是什么?单端口存储器就是:存储器接受数据和输出数据,只能在同一时刻只能执行一项操作,这样一来数据的写和传输就无法同时进行。

双端口存储器是指同一个存储器具有两组相互独立的读写控制线路,由于进行并行的独立操作,是一种高速工作的存储器。

简单说来,就是增加了一个端口,可以同时读数据和写数据,提高了机器运行速度和带宽,可以实现无冲突的读写控制。

3.什么情况下考虑采用双端口存储器?主存的存取速度是影响计算机速度的关键,才用双端口存储器可是明显提高机器的利用率和效率。

如果在对速度要求特别高的情况下,可以考虑采用双端口存储器。

4.FIFO的工作特点是什么?为什么常用于实现程序中的子程序调用、递归等?特点:FIFO(First In First Out)全称是先进先出的存储器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5’b000001 32’b0000000132’b0000000132'h0055_752332'h0055_7523

5’b000002 32’b0000000232’b0000000232'h0055_752332'h0055_7523

实验设备号

个人电脑、Nexys3开发板

一、实验程序源代码

存储器顶层电路代码:

module top_RAM_B(Mem_Addr,C,Mem_Write,Clk,LED);

input [7:2]Mem_Addr;//开关的3、4、5、6、7、8位

input Mem_Write,Clk;//clk为按键C9,读写使能信号为按键C4,0为读,1为写

RAM_B uut (

.clka(clka),

.wea(wea),

.addra(addra),

.dina(dina),

.douta(douta)

);

initial begin

// Initialize Inputs

clka = 0;

wea = 0;

addra = 0;

dina = 0;

// Wait 100 ns for global reset to finish

wea = 1;

addra = 6'b000001;

dina = 32'hFFFF_FFFF;

#100;

clka = 0;

wea = 1;

addra = 6'b000001;

dina = 32'hFFFF_FFFF;

end

endmodule

二、仿真波形

三、电路图

顶层电路模块

顶层电路内部结构:

四、引脚配置(约束文件)

NET "Clk" LOC = C9;

NET "LED[4]" LOC = M11;

NET "LED[3]" LOC = V15;

NET "LED[2]" LOC = U15;

NET "LED[1]" LOC = V16;

NET "LED[0]" LOC = U16;

NET "Mem_Addr[7]" LOC = U8;

杭电计组实验5-存储器设计实验

实验报告

2018年5月5日成绩:

姓名

阳光男

学号

16041321

班级

16052317

专业

计算机科学与技术

课程名称

《计算机组成原理与系统结构试验》

任课老师

张翔老师

指导老师

张翔老师

机位号

默认

实验序号

5

实验名称

《实验五存储器设计实验》

实验时间

2018/5/12

实验地点

1教211

#100;

// Add stimulus here

clka = 1;

wea = 0;

addra = 6'b000001;

dina = 32'h0000_0003;

#100;

clka = 0;

wea = 0;

addra = 6'b000001;

dina = 32'h0000_0607;

#100;

clka = 1;

if(!Mem_Write)//读操作

begin

case(C)

2'b00:LED=M_R_Data[7:0];//读出数据的0-7位

2'b01:LED=M_R_Data[15:8];//读出数据的8-15位

2'b10:LED=M_R_Data[23:16];//读出数据的16-23位

2'b11:LED=M_R_Data[31:24];//读出数据的24-31;读操作时选择显示字节,为开关1、2位

output reg [7:0]LED;

wire [31:0]M_R_Data;//存在存储器里的32位读出数据

reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据

RAM_B test_ram (

.clka(Clk), //输入时钟信号

5’b000003 32’b0000000332’b0000000332'h0055_752332'h0055_7523

5’b000004 32’b0000000432’b0000000432'h0055_752332'h0055_7523

5’b000005 32’b0000000532’b0000000532'h0055_752332'h0055_7523

NET "C[1]" LOC = T5;

NET "C[0]" LOC = V8;

NET "LED[7]" LOC = T11;

NET "LED[5]" LOC = N11;

NET "LED[6]" LOC = R11;

五、思考与探索

(1)读操作实验结果记录表

存储器地址初始化数据读出数据写入新数据读出数据

.wea(Mem_Write), //输入读写信号

.addra(Mem_Addr[7:2]), //输入5位地址信号

.dina(M_W_Data), //写入32位数据

.douta(M_R_Data) //读出32位数据

);

always@(*)

begin

LED=0;//初始化

M_W_Data=0;//初始化

endcase

end

end

endmodule

测试代码:

module test;

// Inputs

reg clka;

reg [0:0] wea;

reg [5:0] addra;

reg [31:0] dina;

// Outputs

wire [31:0] douta;

// Instantiate the Unit Under Test (UUT)

NET "Mem_Addr[6]" LOC = N8;

NET "Mem_Addr[5]" LOC = M8;

NET "Mem_Addr[4]" LOC = V9;

NET "Mem_Addr[2]" LOC = T10;

NET "Mem_Write" LOC = C4;

NET "Mem_Addr[3]" LOC = T9;

endcase

end

else

begin

case(C)

2'b00:M_W_Data=32'h0055_7523;//写入第一个数据

2'b01:M_W_Data=32'h1234_5678;//写入第二个数据

2'b10:M_W_Data=32'h8765_4321;//写入第三个数据

2'b11:M_W_Data=32'hffff_ffff;//写入第四个数据