第章半导体存储器课件

合集下载

《半导体存储器》课件

04

制造设备

用于将掺杂剂引入硅片。

用于在硅片上生长单晶层 。

掺杂设备 外延生长设备

用于切割硅片。

晶圆切割机

制造设备

光刻机

用于将电路图形转移到硅片上。

刻蚀机

用于刻蚀硅片表面。

镀膜与去胶设备

用于在硅片表面形成金属层或介质层,并去 除光刻胶。

测试与封装设备

用于对芯片进行电气性能测试和封装成最终 产品。

分类

根据存储方式,半导体存储器可分为随机存取存储器(RAM)和只读存储器( ROM)。

历史与发展

1 2 3

早期阶段

20世纪50年代,半导体存储器开始出现,以晶 体管为基础。

发展阶段

随着技术的进步,20世纪70年代出现了动态随 机存取存储器(DRAM)和静态随机存取存储器 (SRAM)。

当前状况

现代半导体存储器已经广泛应用于计算机、移动 设备、数据中心等领域。

物联网和边缘计算

在物联网和边缘计算领域应用半导体存储器,实现高 效的数据存储和传输。

CHAPTER

05

案例分析:不同类型半导体存 储器的应用场景

DRAM的应用场景

01

DRAM(动态随机存取存储器)是一种常用的半导体存储器,广泛应 用于计算机和服务器等领域。

02

由于其高速读写性能和低成本,DRAM被用作主内存,为CPU提供快 速的数据存取。

外延生长

在硅片上生长一层或多 层所需材料的单晶层。

掺杂

通过扩散或离子注入等 方法,将掺杂剂引入硅 片。

制造流程

01

光刻

利用光刻胶将电路图形转移到硅片 上。

镀膜与去胶

在硅片表面形成金属层或介质层, 并去除光刻胶。

制造设备

用于将掺杂剂引入硅片。

用于在硅片上生长单晶层 。

掺杂设备 外延生长设备

用于切割硅片。

晶圆切割机

制造设备

光刻机

用于将电路图形转移到硅片上。

刻蚀机

用于刻蚀硅片表面。

镀膜与去胶设备

用于在硅片表面形成金属层或介质层,并去 除光刻胶。

测试与封装设备

用于对芯片进行电气性能测试和封装成最终 产品。

分类

根据存储方式,半导体存储器可分为随机存取存储器(RAM)和只读存储器( ROM)。

历史与发展

1 2 3

早期阶段

20世纪50年代,半导体存储器开始出现,以晶 体管为基础。

发展阶段

随着技术的进步,20世纪70年代出现了动态随 机存取存储器(DRAM)和静态随机存取存储器 (SRAM)。

当前状况

现代半导体存储器已经广泛应用于计算机、移动 设备、数据中心等领域。

物联网和边缘计算

在物联网和边缘计算领域应用半导体存储器,实现高 效的数据存储和传输。

CHAPTER

05

案例分析:不同类型半导体存 储器的应用场景

DRAM的应用场景

01

DRAM(动态随机存取存储器)是一种常用的半导体存储器,广泛应 用于计算机和服务器等领域。

02

由于其高速读写性能和低成本,DRAM被用作主内存,为CPU提供快 速的数据存取。

外延生长

在硅片上生长一层或多 层所需材料的单晶层。

掺杂

通过扩散或离子注入等 方法,将掺杂剂引入硅 片。

制造流程

01

光刻

利用光刻胶将电路图形转移到硅片 上。

镀膜与去胶

在硅片表面形成金属层或介质层, 并去除光刻胶。

半导体存储器

Erasable PROM)

一、静态RAM

(一)六管静态存 储电路

Q7

Q8

图6-2 静态RAM存储单元电路

(二)静态RAM器件的组成

静态RAM器 件可分成三个部 分,分别是存储 单元阵列、地址 译码器和读/写控 制与数据驱动/缓 冲。一个典型的 静态RAM的示意 图如右图所示。

右图是一个1K×1 位的静态RAM器件的组 成框图。该器件总共可 以寻址1024个单元,每 个单元只存储一位数据。

数据(字操作,使用AD0~AD15),也可以只 传送8位数据(字节操作,使用AD0~AD7或 AD8~AD15)。

仅A0为低电平时,CPU使用AD0~AD7, 这是偶地址字节操作;仅为低电平时,CPU使用 AD8~AD15,这是奇地址字节操作。

若和A0同时为低电平时,CPU对AD0~ AD15操作,即从偶地址读写一个字,是字操作; 如果字地址为奇地址,则需要两次访问存储器。 如下表所示

2、Intel 2114是一个容量为1024×4位的静态 RAM ,Intel 2114是一个容量为1024×4位的静 态RAM其引脚和逻辑符号如下图所示。

引脚图

逻辑符号

(四)静态RAM与CPU的连接

进行静态RAM存储器模块与CPU的连接电路 设计时,需要考虑下面几个问题:

1、CPU总线的负载能力 2、时序匹配问题 3、存储器的地址分配和片选问题 4、控制信号的连接

若存储容量较小,可以 将该RAM芯片的单元阵 列直接排成所需要位数

的形式,每一条行选择 线(X选择线)代表一 个字节,每一条列选择 线(Y选择线)代表字 节的一个位,故通常把

行选择线称为字线,而 列选择线称为位线。

(三)静态RAM的例子

1、Intel 6116是CMOS静态RAM芯片,属双列直 插式、24引脚封装。它的存储容量为2K×8位,其 引脚及功能框图如下图所示。

一、静态RAM

(一)六管静态存 储电路

Q7

Q8

图6-2 静态RAM存储单元电路

(二)静态RAM器件的组成

静态RAM器 件可分成三个部 分,分别是存储 单元阵列、地址 译码器和读/写控 制与数据驱动/缓 冲。一个典型的 静态RAM的示意 图如右图所示。

右图是一个1K×1 位的静态RAM器件的组 成框图。该器件总共可 以寻址1024个单元,每 个单元只存储一位数据。

数据(字操作,使用AD0~AD15),也可以只 传送8位数据(字节操作,使用AD0~AD7或 AD8~AD15)。

仅A0为低电平时,CPU使用AD0~AD7, 这是偶地址字节操作;仅为低电平时,CPU使用 AD8~AD15,这是奇地址字节操作。

若和A0同时为低电平时,CPU对AD0~ AD15操作,即从偶地址读写一个字,是字操作; 如果字地址为奇地址,则需要两次访问存储器。 如下表所示

2、Intel 2114是一个容量为1024×4位的静态 RAM ,Intel 2114是一个容量为1024×4位的静 态RAM其引脚和逻辑符号如下图所示。

引脚图

逻辑符号

(四)静态RAM与CPU的连接

进行静态RAM存储器模块与CPU的连接电路 设计时,需要考虑下面几个问题:

1、CPU总线的负载能力 2、时序匹配问题 3、存储器的地址分配和片选问题 4、控制信号的连接

若存储容量较小,可以 将该RAM芯片的单元阵 列直接排成所需要位数

的形式,每一条行选择 线(X选择线)代表一 个字节,每一条列选择 线(Y选择线)代表字 节的一个位,故通常把

行选择线称为字线,而 列选择线称为位线。

(三)静态RAM的例子

1、Intel 6116是CMOS静态RAM芯片,属双列直 插式、24引脚封装。它的存储容量为2K×8位,其 引脚及功能框图如下图所示。

半导体存储器.ppt

数字电子技术

上一页 下一页 回目录 退出

三. 可擦除的可编程ROM

EPROM E2PROM 总体结构与掩模ROM一样,但存储单元不同 EPROM (erasable programmable ROM)

叠栅注入MOS管(stacked-gate injection metal-oxidesemiconductor,SIMOS管)

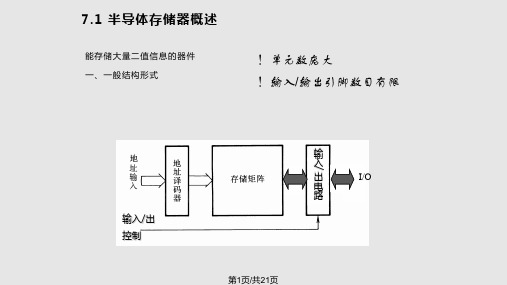

!输入/输出引脚数目有限

输入/出 控制

数字电子技术

输 入

/

出

I/O

电

路

上一页 下一页 回目录 退出

二、分类

1、从存/取功能分: 掩模ROM

①只读存储器

可 编 程ROM 可 擦 除 的 可 编 程EPROM

(Read-Only-Memory)

②随机读/写

静 态RAM 动 态RAM

(Random-Access-Memory)

漏 源 间 形 成 导 电 沟 道 ,沟 道 内 电 子 获 得 动 能 ,

在

受

到G

上

c

所

加

正

电

压

的

电

场

吸引

下

,

部 分 电 子 穿 过SiO2到 达Gf , 形 成 注 入 电 荷

“ 擦 除 ” : 紫 外 线 穿 过EPROM芯 片 上 的 石 英 窗 口

照 射 到 叠 栅 上 , 使Gf 周 围 的 二 氧 化 硅 绝 缘 层产 生 少 量 的 空 穴 和 电 子 对 ,形 成 导 电 通 道 , 从 而 使Gf 上 的电子回到衬底中。

上一页 下一页 回目录 退出

一.固定ROM(掩膜R容量为16×8的ROM

地

(1)存储矩阵:16个字排成矩阵 址

半导体存储技术课件

A.1,15 B. 2,15 C. 1,30 D. 2,30.

(2010年) 15、假定用若干个2k*4位芯片组成 一个8K*8位存储器,则地址0B1FH所在芯片 的最小地址是

A:0000H B:0600H

C: 0700H D:0800H

4.典型存储芯片

4.1 Intel2114 容量: 1K*4位SRAM; 译码方式:A3~A8行译码,

该类芯片一定有一个CLOCK端子。

DDR·SDRAM :习惯称为DDR,部分初学者也常看到DDR

SDRAM,就认为是SDRAM。DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的 意思。DDR内存是在SDRAM内存基础上发展而来的,仍然 沿用SDRAM生产体系,因此对于内存厂商而言,只需对 制造普通SDRAM的设备稍加改进,即可实现DDR内存的生

读“1”:

无流

有流

怎样判断读出的是“1”?

2.2四管动态存储单元

写“1”:

0

+

1

-

读“1”:

1

1

+

-

读“0”:

1

1

+

-

2.3动态与静态单元比对

静态单元:读出时电流为出;

动态单元:写入和读出时电流均为入,读出时三 线均 为高电平。 另外,动态单元内部无需电源(需要预充*)。

如果是单管动态存储单元* (图见书),则是破 坏性读出。

每行被刷新2000/128=15.625。

异步刷新方式:均分方式。每大周 期按刷新行数等分,每等分刷新 一行。

1

2

128

R

R

2ms

2ms/128≌15.5微秒

(2010年) 15、假定用若干个2k*4位芯片组成 一个8K*8位存储器,则地址0B1FH所在芯片 的最小地址是

A:0000H B:0600H

C: 0700H D:0800H

4.典型存储芯片

4.1 Intel2114 容量: 1K*4位SRAM; 译码方式:A3~A8行译码,

该类芯片一定有一个CLOCK端子。

DDR·SDRAM :习惯称为DDR,部分初学者也常看到DDR

SDRAM,就认为是SDRAM。DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的 意思。DDR内存是在SDRAM内存基础上发展而来的,仍然 沿用SDRAM生产体系,因此对于内存厂商而言,只需对 制造普通SDRAM的设备稍加改进,即可实现DDR内存的生

读“1”:

无流

有流

怎样判断读出的是“1”?

2.2四管动态存储单元

写“1”:

0

+

1

-

读“1”:

1

1

+

-

读“0”:

1

1

+

-

2.3动态与静态单元比对

静态单元:读出时电流为出;

动态单元:写入和读出时电流均为入,读出时三 线均 为高电平。 另外,动态单元内部无需电源(需要预充*)。

如果是单管动态存储单元* (图见书),则是破 坏性读出。

每行被刷新2000/128=15.625。

异步刷新方式:均分方式。每大周 期按刷新行数等分,每等分刷新 一行。

1

2

128

R

R

2ms

2ms/128≌15.5微秒

数字逻辑电路半导体存储器资料PPT课件

用SIMOS管构成的存储单元

工作原理: 若G f 上充以负电荷,则 Gc处正常逻辑高电平下不 导通 若G f 上未充负电荷,则 Gc处正常逻辑高电平下导 通

第9页/共21页

“写入”:在叠栅管的D S上同时加上较高电压(25V),

漏源间形成导电沟道,沟道内电子获得动能,

在

受到G

上所加正电压的电场吸引下

第14页/共21页

7.3.1 RAM的基本结构与工作原理 以SRAM为例

第15页/共21页

7.3.2 存储单元

6只N沟道增强型MOS管 组成的静态存储单元

T1 ~ T4组成基本的锁存器,作存储单元

T5 ~ T8是门控管,起模拟开关的作用 T5和T6受控于地址译码器的输出

T7和T8决定存储单元是否与输入输出 电路I/O相连,受控于列地址译码器

第6页/共21页

7.2.2 可编程ROM

可编程ROM(programmable ROM,PROM) 总体结构与掩模ROM一样,但存储单元不同

熔丝由易熔合金制成 出厂时,每个结点上都 有 编程时将不用的熔断 !! 是一次性编程,不能改 写

第7页/共21页

7.2.3 可擦除的可编程ROM

EPROM

为储克 单元服不紫 同 外线擦除的EPRO M擦除慢,操作复杂的缺点 采用FLO TO X(浮栅隧道氧化层MO S管)

Gf与漏区之间有小的隧道区,当场强大到一定程度时, 在漏区和Gf 之间出现导电隧道,电子可以双向通过形成电流, 这种现象称为隧道效应。

第11页/共21页

7.2.4 利用ROM实现组合逻辑函数

第12页/共21页

地址译码器是一个与阵列,它的输出包含了输入地址变量的 全部最小项,每一条字线对应一个最小项; 存储矩阵是一个或阵列,每一位输出数据都是将地址译码器 输出的一些最小项相加。

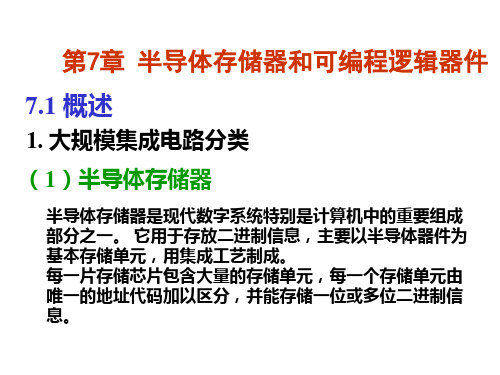

模电课件第七章 半导体存储器和可编程逻辑器件

(2)可编程逻辑器件

(Programmable Logic Device,PLD)

可编程逻辑器件是20世纪70年代后期发展起来的一种功能特殊 的大规模集成电路,它是一种可以由用户定义和设置逻辑功能 的器件。 特点:结构灵活、集成度高、处理速度快、可靠性高

(3)微处理器

微处理器主要指通用的微处理机芯片,它的功能由汇编语言 编写的程序来确定,具有一定的灵活性。但该器件很难与其 他类型的器件直接配合,应用时需要用户设计专门的接口电 路。 微处理器是构成计算机的主要部件。目前除用作CPU外,多 用于实时处理系统。

2. PLD器件的连接表示方法 (1)PLD 器件的连接表示法

固定连接

可编程连接

不连接

(2)门电路表示法

1

A

A

A

1

A

A

A

反向缓冲器

A

&

B

F

C

ABC

&

F

与门

A

≥1

B

F

C

ABC

≥1

F

或门

缓(冲d)器

ABC

(3) 阵列图

1

1

1

& D=BC

& E=AABBCC=0 & F=AABBCC=0

& G=1

1)浮栅注入 MOS 管(FAMOS 管) 存储单元采用两只 MOS管 缺点:集成度低、击穿电压高、速度较慢

2)叠层栅注入 MOS 管(SIMOS 管)

层叠栅存储单元

叠层栅MOS管剖面示意图

控制栅 与字线 相连,控制信息的 读出和写入

浮栅 埋在二氧化硅绝缘层, 处于电“悬浮”状态, 不与外部导通,注入电 荷后可长期保存

《半导体存储器》PPT课件_OK

T3

主

从

1位

图7-2-2 动态CMOS移存单元

当CP=1时,主动态反相器接收信息,从动态反相器保持原存

信息;CP=0时,主动态反相器保持原存信息,从动态反相器随9 主

动态反相器变化。每经过一个CP,数据向右移动一位。

7.2.3 动态移存器和顺序存取存储器

1.动态移存器 动态移存器可用动态CMOS移存单元串接而成,主要用来组 成顺序存取存储器(SAM)。

• ••

CS1

• ••

21

图7-3-6 RAM的位

2.字扩展

适用于位数(字长)够用,但字数不够的情况。 如: 8K×8 → 32K×8 增加地址线。

D0

D7

•••

•••

•••

•••

I/O7···I/O0 VDD

OE 6264Ⅰ 1

GND

CS2

R/W A12 ···A0CS1

I/O7···I/O0 VDD

•••

A2 译

A3

码 X15 器

T0

1,1 位线 16,1

1,16 位线 16,16

I/O电路 G1 1

D

EN

G2

1

I/O

•

EN

T0' T15

T15'

1 EN G3

Y0 (列)

•••

Y15

Y 地址译码器

D G4 &

& G5

A4 A5 A6 A7

图7-3-1 256×1位RAM 示意图

CS

R/W

25

返回

第7章 半导体存储器

• 教学内容 : 半导体存储器的特点、分类及主要技术指标 ; 顺序存取存储器(SAM); 随机存取存储器(RAM) ;

主

从

1位

图7-2-2 动态CMOS移存单元

当CP=1时,主动态反相器接收信息,从动态反相器保持原存

信息;CP=0时,主动态反相器保持原存信息,从动态反相器随9 主

动态反相器变化。每经过一个CP,数据向右移动一位。

7.2.3 动态移存器和顺序存取存储器

1.动态移存器 动态移存器可用动态CMOS移存单元串接而成,主要用来组 成顺序存取存储器(SAM)。

• ••

CS1

• ••

21

图7-3-6 RAM的位

2.字扩展

适用于位数(字长)够用,但字数不够的情况。 如: 8K×8 → 32K×8 增加地址线。

D0

D7

•••

•••

•••

•••

I/O7···I/O0 VDD

OE 6264Ⅰ 1

GND

CS2

R/W A12 ···A0CS1

I/O7···I/O0 VDD

•••

A2 译

A3

码 X15 器

T0

1,1 位线 16,1

1,16 位线 16,16

I/O电路 G1 1

D

EN

G2

1

I/O

•

EN

T0' T15

T15'

1 EN G3

Y0 (列)

•••

Y15

Y 地址译码器

D G4 &

& G5

A4 A5 A6 A7

图7-3-1 256×1位RAM 示意图

CS

R/W

25

返回

第7章 半导体存储器

• 教学内容 : 半导体存储器的特点、分类及主要技术指标 ; 顺序存取存储器(SAM); 随机存取存储器(RAM) ;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7.2 只读存储器 (ROM)

在正常工作时,存储器的数据只能读出,不能写入。

7.2.1 掩膜只读存储器 ——所存储的数据,

在制作过程中使用

存储矩阵

—— 许多存储单元排列构成,每个存储 单存放1位二值代码。

掩膜板固定。

每个或一组存储单元有一个地址码。

地址译码器

一、结构 —— 三部分组成 —— 将地址码译码,形成从存储矩阵中

1 D′3

▽

D3

1 D′2

▽

D2

1 D′1

▽

D1

0 D′0

▽

D0

地址

A1 A0

D00 0 01

10 11

数据

D3 D2 D1

010

101

10 1 0 01 1 1 0

EN

二极管ROM的电路结构图 第章半导体存储器

二、举例

VCC

第 7 章 半导体存储器

ROM中的数据表

地址

数

据

A1 A1

A1 A0

D3 D2 D1

同时在GC上加25V、50ms宽的正脉冲,吸引高速电子穿 过 SIO2 到达 Gf ,形成注入电荷。

擦除:通过照射产生电子-空穴对,提供泄放通道。

第章半导体存储器

第 7 章 半导体存储器

二、电可擦除的可编程ROM(E2 PROM)

浮栅隧道氧化层MOS管 ( FLOTOX )

E2 PROM的存储单元

①掩膜 ROM

1)只读存储器 (ROM)

②可编程 ROM (PROM)

③可擦除的可编程 ROM

1、按存/ 取功能分

(EPROM)

半导体 存储器 分类

① 静态随机存储器 2) 随机存储器 (SRAM)

(RAM) ② 动态随机存储器 (DRAM)

2、按工艺分

1) 双极型 2) M第章O半导S体型存储器

第 7 章 半导体存储器

一、用紫外线擦除的EPROM(UVEPROM)

浮栅雪崩注入MOS管(FAMOS管)

使用FAMOS管的存储单元

写入: 雪崩注入。 擦除:通过照射产生电子-空穴对,提供泄放通道。

第章半导体存储器

第 7 章 半导体存储器

叠栅注入MOS管

GC : 控制栅 Gf : 浮置栅

写入: 雪崩注入,D—S间加高压(20~25V),发生雪崩击穿,

5) 字长 一个字的位数。

6) 地址变量数与字数的关系 n个地址变量, 2n 个字

7) 存储器的寻址范围 地址变量的取值组合范第章围半导。体存储器

第 7 章 半导体存储器

用MOS管构成的存储矩阵

掩膜ROM的特点: 出厂时已经固定,不能更改,非易失性。

第章半导体存储器

第 7 章 半导体存储器

7.2.2 可编程只读存储器 ( PROM ) 用户可写入一次的存储器。 正常工作时只能读不能写。 总体结构与掩膜ROM一样,但存储单元不同。

EN

存入“0”。

二极管ROM的电路结构图 第章半导体存储器

第 7 章 半导体存储器

存储器的一些概念和数量关系

1) 存储器的容量 存储器的容量 = 字数×位数

2) 存储单元数 存储单元数= 字数、位数的乘积结果

3) 字线 对存放每个字的存储单元组进行选择的译码器的输出线。

4) 位线 一个存储单元组中,每一位数据的传输线。

0

D′1

▽

D1

0

D′0

▽

D0

地址

A1 A0

D00 0 01 10

数据

D3 D2 D1

010 101 10 1 0 0

EN

二极管ROM的电路结构图 第章半导体存储器

二、举例

VCC

第 7 章 半导体存储器

ROM中的数据表

A1 1 A0 1

存 储 矩 阵

A1

0

地 址 译

码Hale Waihona Puke A0器0W00 W01 W02 W31 输出缓冲器

地 址

D00 0 0 1 0

A0

译 码

01 101

A0

器

1 0 10 1 0

存 储 矩 阵

W0 W1 W2 W3

输出缓冲器

D′3

▽

D3

D′2

▽

D2

D′1

▽

D1

D′0

▽

D0

1 1 01 1 1 1) 横向理解真0 值表 输入一个地址,读出一个字。 2) 存储矩阵的每个交叉点 是一个“存储单元”,存储单 元中有器件存入“1”,无器件

选择存储单元的选择信号。

输出缓冲器

—— 提高负载能力及控制三态输出。

第章半导体存储器

二、举例

VCC

第 7 章 半导体存储器

ROM中的数据表

A1 0 A0 0

存 储 矩 阵

A1

1

地 址 译

码

A0

器

1

W10 W01 W02 W30 输出缓冲器

0

D′3

▽

D3

1

D′2

▽

D2

0

D′1

▽

D1

1

D′0

▽

D0

地址

熔丝由易熔合金制成; 出厂时每个结点上都有存储单元; 编程时将不用的存储单元熔丝熔断; 是一次性编程,不能改写。

熔丝型PROM的存储单元

第章半导体存储器

第 7 章 半导体存储器

第章P半R导O体M存的储器结构原理图

第 7 章 半导体存储器

7.2.3 可擦除的可编程只读存储器(EPROM) 可反复多次写入的存储器。 正常工作时只能读不能写。 总体结构与掩膜ROM一样,但存储单元不同。

第 7 章 半导体存储器

第 7 章 半导体存储器

7.1 概述 7.2 只读存储器 (ROM) 7.3 随机存储器 (RAM) 7.4 存储器容量的扩展 7.5 用存储器实现组合逻辑函数

第章半导体存储器

返回主目录

第 7 章 半导体存储器

7.1 概 述

半导体存储器 —— 能存储大量二值信息的半导体器件。

列地址译码器:输入列地址码,

输出列选择线。

③ 读写控制电路

片选信号 CS = 0 时:

当读/写控制信号R / W =0时,进

A1 A0

D00 0

数据

D3 D2 D1

010 1

EN

二极管ROM的电路结构图 第章半导体存储器

二、举例

VCC

第 7 章 半导体存储器

ROM中的数据表

A1 0 A0 1

存 储 矩 阵

A1

1

地 址 译

码

A0

器

0

W00 W11 W02 W30 输出缓冲器

1

D′3

▽

D3

0

D′2

▽

D2

1

D′1

▽

D1

1

D′0

▽

D0

地址

A1 A0

D00 0

01

数据

D3 D2 D1

010 101 1

EN

二极管ROM的电路结构图 第章半导体存储器

二、举例

VCC

第 7 章 半导体存储器

ROM中的数据表

A1 1 A0 0

存 储 矩 阵

A1

0

地 址 译

码

A0

器

1

W00 W01 W12 W30 输出缓冲器

0

D′3

▽

D3

1

D′2

▽

D2

第章半导体存储器

第 7 章 半导体存储器

7.3 随机存储器 (RAM)

可随机对任一存储地址的存储单元进行读或写操作。

7.3.1 静态随机存储器(SRAM) 一、 SRAM的结构与工作原理

① 存储矩阵

存储单元按行、列排列。 每个存储单元可写入或读出0或1。

② 地址译码器

行地址译码器:输入行地址码,

输出行选择线。