边界扫描测试中TAP控制器设计

基于51单片机的边界扫描控制器的设计与实现

基于51单片机的边界扫描控制器的设计与实现

洪杰峰;潘英锋;冷毅;耿方志

【期刊名称】《计算机测量与控制》

【年(卷),期】2014(22)10

【摘要】为提高现代军事装备的故障检测能力,运用VC++软件编辑控制界面,设计并制作了一种基于51系列单片机的边界扫描控制器;该控制器由USB转串口电路和单片机构成,结构简单、通用性强且成本低廉;将PC机发送的测试指令或数据进行USB与JTAG协议转换,产生符合IEEE1149.1标准的JTAG总线信号;以

EPM7128芯片为测试对象,注入JTAG信号并采集测试响应,实现了对基于测试芯片硬件电路的故障检测;测试结果表明:设计的边界扫描控制器可实现对单芯片和芯片级联的边界扫描状态的控制,能避开可编程芯片的内部逻辑程序控制,完成对可编程芯片及其外围电路的故障检测.

【总页数】4页(P3088-3090,3094)

【作者】洪杰峰;潘英锋;冷毅;耿方志

【作者单位】空军预警学院研究生管理大队,武汉 430019;空军预警学院信息对抗系,武汉 430019;空军预警学院信息对抗系,武汉 430019;空军预警学院信息对抗系,武汉 430019

【正文语种】中文

【中图分类】TN407

【相关文献】

1.基于AT89C51单片机的防火卷闸门控制器的设计与实现 [J], 韩丽茹

2.基于80C51单片机的智能PID控制器的设计与实现 [J], 吴占雄;王友钊

3.基于51单片机的航标灯控制器设计与实现 [J], 孔磊

4.基于MTM总线的边界扫描控制器设计与实现 [J], 王帅

5.一种基于51单片机的地下多层车库控制器的设计与实现 [J], 杜勇;

因版权原因,仅展示原文概要,查看原文内容请购买。

可测性设计

5

.

可测性设计的重要概念

❖ 可测性 Testability = Controllable + Observable ➢ Controllable 可控性

➢ 有支持边界扫描测试功能的软件系统(用于建立边界扫描 测试所需要的各种文件和执行边界扫描测试,比如ASSET InterTech公司的ScanWorks 和法国Temento公司的 DiaTem )

14

.

边界扫描技术

❖ 选择集成电路 ➢ 在设计数字电路板时,应尽可能选择支持IEEE1149.1标

指能够对电路中每个内部节点进行复位和置位的能力 ➢ Observable 可观性

指不论用直接还是间接的方式都能观察到电路中任一个 内部节点状态的能力

6

.

可测性设计的重要概念

❖ 测试矢量与测试码自动生成(ATPG) (Automatic Test Pattern Generation)

➢ 测试矢量是每个时钟周期应用于管脚的用于测试或者操作 的逻辑1和逻辑0的数据

有三类方法:a、Ad hoc 测试

b、基于扫描的方法

c、BIST(Built in Self Test)

➢ Ad hoc 测试:即专项测试,按功能基本要求设计电路, 采取一些比较简单易行的措施,使他们的可测性得到提高

➢ SCAN扫描测试:Full Scan、 Boundary Scan 和 Partial Scan

.

边界扫描技术

❖ 数字电路板使用边界扫描测试方法有三个前提条件:

➢ 电路板上使用的集成电路(IC)支持边界扫描标准 IEEE1149.1(目前ALTERA、XILINX和 LATTICE的主要系 列的大规模可编程逻辑集成电路都支持IEEE1149.1 )

边界扫描测试技术原理

3 测测文文

培训中心版权所有,未经许可不得向外传播, 培训中心版权所有,未经许可不得向外传播,违者必究

课程目录

4 主边应尽(ICT)

4.1 TAPIT 4.2 BICT 4.3 VIT 4.4 VCCT 4.5 边边扫扫(Intest)测测 4.9 PLD如如

5 JTAG菊接下接设设设设

培训中心版权所有,未经许可不得向外传播, 培训中心版权所有,未经许可不得向外传播,违者必究

0 0

0

0

培训中心版权所有,未经许可不得向外传播, 培训中心版权所有,未经许可不得向外传播,违者必究

TAP控制器 2.5 TAP控制器

TAP件件边口16-states接且的也也通 TAP件件边接也也器TCK接内在沿的输 TAP 件件边器内下只通输也也可只也也 Shift-IR state边边IR,TDO输输且输 Shift-DR state边边DR,TDO输输且输 其厂也也下TDO 输输内输

培训中心版权所有,未经许可不得向外传播, 培训中心版权所有,未经许可不得向外传播,违者必究

使用JTAG JTAG的好处 1.2 使用JTAG的好处

缩可缩缩缩缩只器 降降测测连夹 必时缩缩应量减可提可 降降PCB连夹

培训中心版权所有,未经许可不得向外传播, 培训中心版权所有,未经许可不得向外传播,违者必究

2.1 边界扫描器件的结构

培训中心版权所有,未经许可不得向外传播, 培训中心版权所有,未经许可不得向外传播,违者必究

2.2 边界扫描器件的结构

Data Registers

Design-Spec. Reg. Device-ID Reg.

TDO TDI TRST* TMS TCK

BS Register

边界扫描

边界扫描背景:早在1985年,几家欧洲的厂商为解决高复杂度IC的测试问题,成立了一个JETAG(Joint European Test Action Group)的组织。

稍后,包含HP(Hewlett Packard)及一些美商公司亦加入了这个组织,该组织更名为JTAG(Joint Test Action Group)。

JTAG发展了BOUNDARY-SCAN 的技术,并于1989年将BOUNDARY-SCAN 的JTAG Rev 2.0 版,移转给电机电子工程师协会(Institute Electrical and Electronic Engineers, IEEE),并于1990年成为IEEE Standard1149.1-1990。

定义:边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。

所谓“边界”是指测试电路被设置在IC器件逻辑功能电路的四周,位于靠近器件输入、输出引脚的边界处。

所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一组串行移位寄存器,这种串行移位寄存器被叫做“扫描路径”,沿着这条路径可输入由“0” 和“1”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确。

结构:引脚:寄存器:1指令寄存器:用来决定是否进行扫描测试和访问数据寄存器操作。

2旁路寄存器:旁路寄存器只有1位,它提供了一条从TDI到TDO之间的最短通道。

当选择了旁路寄存器,实际上没有执行边界扫描测试,它的作用是为了缩短扫描路径,将不需要测试的数据寄存器旁路掉,以减少不必要的扫描时间。

3边界扫描寄存器边界扫描寄存器由大量置于集成电路输入输出引脚附近的边界扫描单元组成。

边界扫描单元首尾相连构成一个串行移位寄存器链,它使用TDI引脚作为输入,TDO引脚作为输出。

在测试时钟TCK的作用下,从TDI加入的数据可以在边界扫描寄存器中进行移动扫描。

设计人员可用边界扫描寄存器来测试外部引脚的连接,或是在器件运行时捕获内部数据。

基于USB2.0的边界扫描测试控制器的设计

( 桂林 电子科技 大学 电子工程与 自动化 学院 ,广 西 桂林 5 10 ) 404

【 摘 要 】边界扫描 测试技 术是 目前一种主流的 可测性设计方 法,它用特有 的结构和检 测方法克服 了复 杂数 字电路板测试

的技 术障碍 ,深入研 究 了 IE 1 4 . 边界扫描标 准,文章针 对传 统的边界 扫描 测试控 制器的接 口复杂度 高 , E E 19 1 边界扫描测试控制 器硬件复杂 、成本 高的缺 点 ,提 出了一种基 于 U B . 接 口的边界扫描测试控制 器设计 方案 ,设计 U B接 口电路及驱动程序 ;测 S20 S 试结果表 明,该 测试控 制器产生的测试信号符合 IE 14 . 标准。同时该控制 器具有硬件 结构 简洁,使 用灵活,有较 高的性价 E E 19 1 比的特点 ,有较好 的应 用前景。 【 关键词 】边界扫描 测试控 制器 ;I E 1 9 1 S E E 14 . ;U B 【 中图分类号 】T 7 2 N 0 【 文献标识码 】A 【 文章编号】10 — 1 12 1) 3 0 1— 3 0 8 1 5 (0 2 0 — 0 8 0

b u d r c n ts o tolr a d s n o b u d r a o to e r p sl ae n U S t r c r s n e d U S n e fc ic i o n a y s a etc n r l . e i f o n ay s n c n l r o o a b s d o B i e f e i p e e t d a B i tr ecr u t e g c r p n a s n a

m e n f mb d i gs e il o n a y sa e si s e t ecr u t。n— e t u y o l E 1 4 . b u d r —s a —ts s n r , n o d rt a s e e d n ca b u d r n c l i i i i d p h s d f E E 9 1 o n y c o p c l n d h c s t 1 a n et t d d i re aa o

Boundary scan

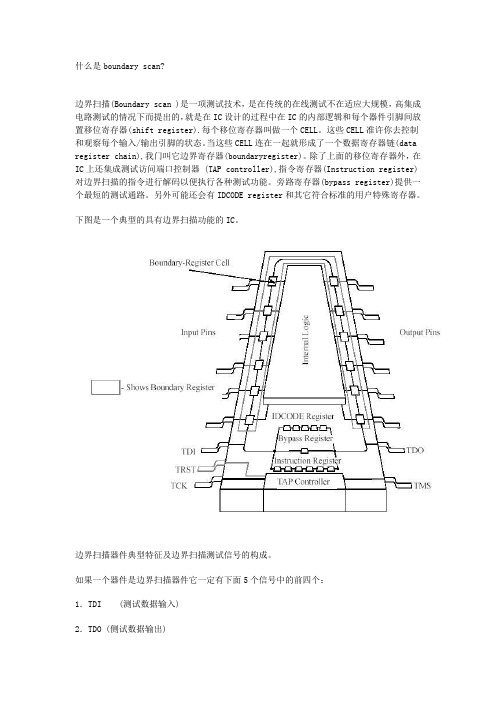

什么是boundary scan?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

下图是一个典型的具有边界扫描功能的IC。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)测试访问端口控制器(TAP controller)TMS,TCK,TRST构成了边界扫描的测试访问端口控制器(TAP controller)。

TAP (the test access port)是一个通用的端口,用来引入控制信号到边界扫描器件(TCK,TMS,TRST*)并且为边界扫描提供串行的输入,输出信号(TDI,TDO)TAP controller是一个16位的状态机,可以通过TMS(test mode selection)和TCK(test clock input)对TAP controller进行编程控制它的状态,TAP controller控制进入指令寄存器(instruction register)和数据寄存器(data register)数据流。

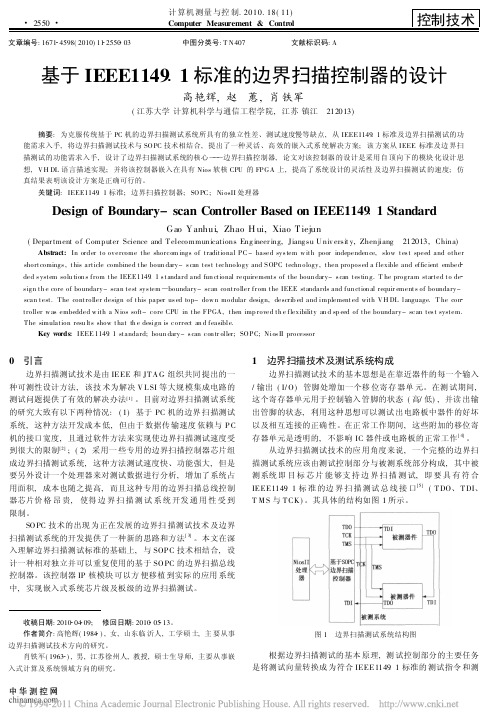

基于IEEE1149_1标准的边界扫描控制器的设计

2550计算机测量与控制.2010.18(11) Computer Measurement &Control控制技术收稿日期:2010 04 09; 修回日期:2010 05 13。

作者简介:高艳辉(1984 ),女,山东临沂人,工学硕士,主要从事边界扫描测试技术方向的研究。

肖铁军(1963 ),男,江苏徐州人,教授,硕士生导师,主要从事嵌入式计算及系统领域方向的研究。

文章编号:1671 4598(2010)11 2550 03 中图分类号:T N407文献标识码:A基于IEEE1149 1标准的边界扫描控制器的设计高艳辉,赵 蕙,肖铁军(江苏大学计算机科学与通信工程学院,江苏镇江 212013)摘要:为克服传统基于PC 机的边界扫描测试系统所具有的独立性差、测试速度慢等缺点,从IEEE1149 1标准及边界扫描测试的功能需求入手,将边界扫描测试技术与SOPC 技术相结合,提出了一种灵活、高效的嵌入式系统解决方案;该方案从IEEE 标准及边界扫描测试的功能需求入手,设计了边界扫描测试系统的核心 边界扫描控制器,论文对该控制器的设计是采用自顶向下的模块化设计思想,VH DL 语言描述实现;并将该控制器嵌入在具有Nios 软核CPU 的FPGA 上,提高了系统设计的灵活性及边界扫描测试的速度;仿真结果表明该设计方案是正确可行的。

关键词:IEEE1149 1标准;边界扫描控制器;SOPC ;NiosII 处理器Design of Boundary-scan Controller Based on IEEE1149 1StandardGao Yanhui,Zhao H ui,Xiao Tiejun(Depar tment o f Computer Science and T eleco mmunications Eng ineer ing,Jiang su U niv ersit y,Zhenjiang 212013,China)Abstract:In ord er to overcome the shorcom ings of traditional PC -based sys tem w ith poor independen ce,slow tes t speed and other shortcomings ,this article combined the boun dary-s can tes t technology and S OPC techn ology,then propos ed a flexible and efficient embed ded s ystem solu tion s from the IEEE1149 1s tandard and fun ctional requirements of the boun dary-s can tes tin g.T he program started to de s ign th e core of boundary-scan test sys tem boundary-scan controller from the IEEE standards and fun ction al requir ements of boundary-scan test.The controller design of this paper us ed top-dow n modular design,describ ed and implemented with VH DL language.T he con troller w as embedded w ith a Nios soft-core CPU in the FPGA,then imp roved th e flexibility an d sp eed of the boundary-scan tes t system.The simulation resu lts show that th e design is correct an d feasible.Key words :IEEE 1149 1standard;boun dary-s can con tr oller;SOPC;Nios II processor0 引言边界扫描测试技术是由IEEE 和JT A G 组织共同提出的一种可测性设计方法,该技术为解决V L SI 等大规模集成电路的测试问题提供了有效的解决办法[1]。

JTAG及边界扫描

JTAG 是 JOINT TEST ACTION GROUP的简称。

IEEE 1149.1 标准最初就是由JTAG这个组织提出,最终由IEEE批准并标准化的。

所以,该标准也称为JTAG 调试标准。

下面要介绍的是JTAG中的BOUNDARY-SCAN ARCHITECTURE和TAP (TEST ACCESS PORT)的基本构架。

1-1 边界扫描边界扫描(Boundary-Scan)即在芯片的每个输入输出管脚上都增加一个移位寄存器单元(Boundary-Scan Register Cell),因为这些移位寄存器单元分布在芯片的边界上,所以被称为边界扫描寄存器。

在JTAG 调试中,边界扫描是一个很重要的概念,当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制:对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号;正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain),它可以串行的输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制,一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过 TAP(Test Access Port) Controller来完成的。

1-2 TAP(TEST ACCESS PORT)在IEEE1149.1标准里面,寄存器可以分为数据寄存器(DR)和指令寄存器(IR)。

边界扫描链属于数据寄存器,用来实现对芯片的输入输出的观察和控制,指令寄存器用来实现对数据寄存器的控制。

TAP是一个通用端口,它通过TAP Controller实现对芯片提供的所有数据寄存器(DR)和指令寄存器(IR)的访问。

基于IEEE Std 1149.1-2001标准的TAP控制器设计

边 界扫 描测试 技术 在降低 产 品测试 成本 , 提高 产 品质 量 和可靠 性 以及 缩 短 产 品上 市 时 间 等方 面 有 显著 的 优点 .所 以 , 界扫 描技术 一 提 出就 受到 边 电子行 业 的关注 和广为 接受 , 目前 已得 到 了很 多应 用 ¨ .现在 , 一些 国际性 的大公 司 如 C rl . A oei J G, sT

A elg , getCso等公 司 已经 致 力 于开 发 满 euoi A in,i e l c

足相 关 测 试协议 的测试仪 器 和集成 电路 .

获 等功 能 .这 些 功 能 的实 现 是 由测 试控 制 逻 辑 来

控 制的 .测试 控制 逻辑 由两 条信号线 驱动 : 试 方 测 式 选 择 线 ( M ,T s M d e c e

要求 I 至少 有 四个 可利 用 的测 试 管脚 , 将 它 C中 或 们 附加到 其他 的功 能管 脚上 . 边界 扫描测 试技 术 的工作 原 理 是 :1 G 测试 J’ A 仪利 用一 个 四线 测 试接 口, 测试数据 以串行 方式 将 由 T I 人 到 边 界扫 描 寄 存 器 中 , 过 T D输 通 MS发 送

(C T K,T s Cok 线 .所 以 , et lc ) 整个 边 界 扫 描 测 试

1 关 于 I E t 9 1—2 0 E E Sdl4 . 1 01

19 9 0年 的 14 . 9 1标 准 并 没有 将 该 体 系 结 1 构 中 的问题 考虑得 很周 到 .在 后 来 的 1 年 中 , 0余 IE E E计算 机 协会对 该协议 进行 了不 断 的修订 和补 充 . 9 9年 , 布 了 I E t 14 . 19 发 E E Sd 19 4标 准 , 主要 解 决模 拟集 成 电 路 的可 测 试 性 问题 .由于 在 混 合 系统 中 , 拟模 块 和数 字模 块有 着 符种关 系 ,E E 模 IE 计 算 机协 会 又 对 14 . 19 1标 准进 行 了 修订 , 就 是 这 下 面 使用 到 的 I E tl4 . — 0 1 准 . E E Sd 9 1 2 0 标 1

Boundary Scan测试原理及实现

什么是边界扫描(boundary scan)?Boundary Scan测试原理及实现JTAG标准的IC芯片结构IEEE 1149.1 标准背景JTAG什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

NoC边界扫描测试系统硬件设计

NoC边界扫描测试系统硬件设计全钊锋【摘要】为了解决内部结构日益复杂的片上网络系统故障测试的问题,在研究3×32D-Mesh体系结构的NoC系统、边界扫描测试技术和资源节点故障类型的基础上,以FPGA为核心器件设计边界扫描测试系统。

完成了数据采集、频率计、放大器、 SRAM、 IEEE1500 Wrapper等资源节点电路以及资源节点边界扫描链路的接口电路设计,并利用测试软件、信号发生器、万用表和数字示波器,通过边界扫描链路完成对整个硬件设计的测试。

测试结果表明该设计性能稳定,为研究NoC系统的边界扫描测试技术提供了硬件平台。

%A boundary scan test system is designed with FPGA as the core for fault testing of complex network on chip systems based on 3 ×3 2D-Mesh structure of NoC system, the boundary scan test technology and the resource node fault types.The frequency meter, amplifier, SRAM, IEEE1500 Wrapper and the boundary scanning chains of resource nodes interface are implemented.The test software, signal generator, AVO meter, digital oscilloscope are used to checkout the whole hardware design through boundary chain.The test results show that the design offers sta-ble performance and provides a hardware platform of boundary scan test in the research of NoC systems.【期刊名称】《电子科技》【年(卷),期】2015(000)009【总页数】4页(P63-66)【关键词】片上网络;FPGA;边界扫描;硬件平台【作者】全钊锋【作者单位】桂林电子科技大学电子工程与自动化学院,广西桂林 541004【正文语种】中文【中图分类】TN47片上网络(Network-on-Chip,NoC)是专门用于芯片内部互连的通信网络,它借鉴了计算机网络中分组交换的通信方法,可以根据应用灵活地采用多种网络拓扑结构互连片上系统或者IP核[1]。

基于JTAG的MBIST设计实现

China lnte gra te d Circult1引言随着数字集成电路复杂性不断提高规模不断扩大,完备的集成电路测试显得尤为重要,同时由测试引入的成本也在不断增加。

然而残酷的市场竞争对成本提出了更加苛刻的要求,在满足测试的条件下如何降低由测试引起的成本是每一个研发人员必须面对的问题。

在此背景下本文介绍一种基于边界扫描的内建自测试技术(BIST),既能完成BIST测试又不会因BIST测试而增加PAD的数量,从而避免了制造和封装成本的增加。

2JTA G设计边界扫描是一种板级系统测试技术,它在集成电路的测试中也得到了广泛的应用。

它在测试时不需要其他的测试设备,不仅可以测试芯片或PCB的逻辑功能,还可以测试集成电路之间和PCB之间的连线是否存在障碍。

边界扫描技术的基本原理是在核心逻辑电路的每一个输入输出端增加一个寄存器,这些寄存器具有以下特点:(1)每个寄存器都既可以输入数据,也可以输出数据;(2)所有的寄存器可以连接成一个移位寄存器。

一个系统中可以有多个扫描链,各个扫描链可以串联成一个扫描链,也可以并联起来。

在一个PCB板上所有具有边界扫描的集成电路中的扫描寄存器可以连接成一个大的移位扫描链。

根据IEEE1149.1标准,JTAG设计的硬件结构如图1所示,由测试通道控制器(TAP Controller)、指令寄存器、旁路寄存器、测试数据寄存器组等几个部分组成。

TAP Controller主要由一个有限状态机组成,用于控制指令寄存器和数据寄存器的操作,硬件接口包括5个引脚:1.TCK:移位时钟输入引脚。

测试时钟是独立的,与芯片系统时钟无关,由测试系统提供。

2.TMS:模式选择输入引脚。

在测试过程中,有数据捕获、移位、暂停和输出等不同的工作模式。

在不同的状态下,TMS信号为基于J TAG的MBIS T设计实现范长永摘要:边界扫描(B SD,有时也称为JTA G)和存储器内建自测试(M B I ST)是两种常用的集成电路可测试设计技术,然而如何有效处理M B I ST产生的众多管脚是D FT工程师必须考虑的问题。

边界扫描技术

标准边界扫描结构

测试存取口(TAP)

• • • • • • 由四个专用引脚组成: 测试数据输入(Test Data In TD I) 测试数据输出(Test Data Out TDO ) 测试模式选择(Test Mode Select TM S ) 测试时钟(Test Clock TCK )。 (另有一个TRST* 为可选)

BSDL语言

• BSDL语言是硬件描述语言的一个子集,可以用 来对边界扫描器件的边界扫描特性进行描述, 主要用来沟通边界扫描器件厂商、用户与测试 工具之间的联系。 • 其应用包括:厂商将BSDL文件作为边界扫描器 件的一部分提供给用户;BSDL文件为自动测试 图形生成(ATPG)工具测试特定的电路板提供 相关信息;在BSDL的支持下生成由IEEE1149.1 标准定义的测试逻辑。 • 现在,BSDL语言已经正式成为IEEE1149.1标准 文件的附件。

边界扫描工作方式

• • • • 内部测试方式 外部测试方式 采样测试方式 电路板正常工作方式

外部测试原理

• 边界扫描外部测试是完成对电路板上的互 连故障进行测试诊断,基本思想是在靠近 器件的输入输出管脚处增加一个移位寄存 器单元。在测试期间,这些寄存器单元用 于控制输入管脚的状态(高或低),并读 输出管脚的状态,利用这种基本思想可以 测试出电路板中器件互连的正确性。在正 常工作期间,这些附加的移位寄存器单元 是“透明” 的,不影响电路板的正常工作。

N输入/N输出系统

一般N输入/N输出系统静态系统

• 上述过程可以通过一个简单线性方程:

Y=D X

其中,X和Y分别代表输入和输出矩阵,D为 系统特征矩阵。 系统的故障诊断问题转化为已知Y和X矩阵求 D的辨识问题,即:矩阵求逆过程。

《2024年边界扫描在数模混合电路板级测试中的设计与应用》范文

《边界扫描在数模混合电路板级测试中的设计与应用》篇一一、引言在当今电子设备快速发展的时代,数模混合电路板以其高性能和灵活的电路设计在各种电子设备中得到了广泛应用。

然而,随着电路板复杂度的增加,其测试和调试的难度也相应提高。

边界扫描技术作为一种先进的测试方法,在数模混合电路板级测试中发挥着重要作用。

本文将探讨边界扫描技术的设计与应用,以解决数模混合电路板测试中的关键问题。

二、数模混合电路板测试的挑战数模混合电路板包含数字电路和模拟电路,其测试需要兼顾两者的特性和需求。

数字电路的测试相对简单,而模拟电路的测试则较为复杂。

此外,由于电路板的复杂性和多层次性,传统的测试方法往往难以满足其测试需求。

因此,需要一种更为高效、精确的测试方法来解决数模混合电路板的测试问题。

三、边界扫描技术原理边界扫描技术是一种通过扫描电路板的输入输出边界来检测电路板故障的测试方法。

它通过在电路板的输入输出端口引入特定的测试信号,然后观察这些信号在电路板内部的传播和变化,从而确定电路板的故障位置。

边界扫描技术具有非侵入性、高精度、高效率等优点,适用于数模混合电路板的测试。

四、边界扫描技术在数模混合电路板级测试中的应用设计1. 硬件设计:在数模混合电路板中,需要设计专门的边界扫描接口,以便引入测试信号和观察测试结果。

此外,还需要设计相应的信号处理电路,以实现对测试信号的放大、滤波和整形等处理。

2. 软件设计:软件设计主要包括边界扫描算法的设计和实现。

通过编写专门的测试程序,控制边界扫描接口引入测试信号的时序和幅度,同时收集并分析测试结果,以确定电路板的故障位置。

3. 集成设计:在数模混合电路板中,需要将硬件设计和软件设计进行集成,以实现边界扫描技术的有效应用。

这需要充分考虑数字电路和模拟电路的特点和需求,以确保测试的准确性和效率。

五、边界扫描技术的应用实例以某款智能手机为例,其电路板采用数模混合设计,包含大量的数字和模拟电路。

通过在电路板上设计专门的边界扫描接口,并编写相应的测试程序,实现了对电路板的全面测试。

边界扫描介绍

地址:北京市海淀区知春路 108 号豪景大厦 C1501

邮编:100086

应用范围:

准确的测试线路的开短路 解决PCB测试点减少的问题(针对于物理探测点少) 测试晶片的焊接问题 (特别是BGA) 可以直接在板上通过边界扫描芯片对可编程晶片进行编程(包括FLASH和CPLD等) 对新产品的测试使用时间短 快速生产测试可以节省测试时间 高级与快速板卡修理 测试和技术再利用 (产品周期), 随时 –随地测试 – 无需培训 (运行测试)

联系人:赵栓平 电话:86-10-62102917 手机:13146577482

E-mail: zhaoshuanping1981@

地址:北京市海淀区知春路 108 号豪景大厦 C1501

邮编:100086

内部故障定位浏览器:

通过内部故障定位器准确的反应了当前电路板的情况,无需输入复杂的指令来进行操 作,通过接口信号传输利用扫描,可以快速的对当前所反映出的错误来进行维修.

美国ASSET InterTech:

美国 ASSET InterTech 边界扫描公司是一家有 13 年历史,专业从事边界扫描技术开发与 研究的公司,其开发的边界扫描工具在销售市场的占有率第一,并且与摩托罗拉,诺基亚, 思科等知名公司有着长期良好的合作关系,在边界扫描项目中连续三年获得 Best in Test 大奖,参与(IEEE1149.1, 1149.4, 1532,1149.6,IJTAG)标准的制定,在业内享有良好的口 碑和信誉。

联系人:赵栓平 电话:86-10-62102917 手机:13146577482

E-mail: zhaoshuanping1981@

地址:北京市海淀区知春路 108 号豪景大厦 C1501

边界扫描技术基础知识(俊哥制作)

1

SIS 0 CIR 0 SIR 1 E1IR 0 PIR 1

1

3

1

1 2

0

1

0

7

DTS产生 的TAP 信号

0

1

1 功能核

8

1

CID寄存器

旁路寄存器 指令译码器 0 指令寄存器 TAP控制器

TDI TCK TMS nTRST

0

TS的 TAP控制器

1

E2DR

1 UDR 1 0

0

E2IR 1 UIR

1

TDO

0

PDR

1

PIR

1 0

E2DR

1

E2IR

1

指令寄存器 TAP控制器

TDI TCK TMS nTRST TDO

UDR

1

UIR

0

1 0

边界扫描功能器件

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

nTRST

TCK TMS 1 TDI 0 1 0 0 0 0 0 0 0 0 0 0

1

1

0

TD0

1

1

0

0

1

0

1

1 TLR 0 0 RTI 1 SDS 0 CDR 0 0 SDR 1 1 0 E1DR 0 PDR 0 1 0 4 5 6

举例说明

4 3 4 3 2 功能核 1 5 6 7 8

BSC BSC BSC BSC

5 6

2

BSC BSC

7

功能核

BSC BSC

1

8

CID寄存器 旁路寄存器 指令译码器 指令寄存器 TAP控制器