边界扫描测试原理与应用

边界扫描测试技术原理

2.6 TAP控制器口线功能和关系1

TCK为低时Test logic的存储单元保持不变,TCK在上升 沿 采样TMS和TDI输入值,在TCK下降沿TDO输出变化 测试指令(test instruction)和测试数据(test data )从 TDI输入线输入到指令寄存器( instruction register )和 各种数据寄存器(various test data registers )

边界扫描测试技术原理

员工培训中心 2005年11月15日

培训中心版权所有,未经许可不得向外传播,违者必究

课程目的

1、了解边界扫描器件的基本结构; 2、了解边界扫描测试技术的原理; 3、了解边界扫描描述语言BSDL的基本格式; 4、了解边界扫描测试技术的主要应用; 5、了解边界扫描JTAG接口的设计规范;

可选的Public Instructions

INTEST, RUNBIST

IC厂商可以自定义Public or Private Instructions, Public Instructions的资料必须公开。

培训中心版权所有,未经许可不得向外传播,违者必究

3.2 JTAG电路指令码

BYPASS: 全1,IC厂商可以再分配几个其它的binary code. EXTEST: 全0,IC厂商可以再分配几个其它的binary code. SAMPLE/PRELOAD, INTEST, RUNBIST, IDCODE, USERCODE: IC厂商自行分配binary code。 未分配的binary code表示BYPASS。

培训中心版权所有,未经许可不得向外传播,违者必究

2.4 控制器的16位状态机

BoundaryScan测试原理及实现

Boundary Scan测试原理及实现什么是边界扫描(boundary scan)?什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器(TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register 和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

在不了解Boundary scan的目的:Boundary scan是一种用于测试数字集成电路的技术,它能找出,开路,短路,和功能不良的数字器件,另外它还能完成一些功能测试。

系统级边界扫描测试系统的设计与实现

试系统 , 并设计了测试系统软件。通过测试验证 , 表明系统工作稳定 , 关键技术通用性强, 能够准确地进行故障诊断和

定位 。

关 键词 :MT B s M- u ;边界扫描测 试 ;测试系统

De i n a m p e e a i n o y t m e e o nd r c n t s y t m sg nd i l m nt to f s s e l v lb u a y s a e ts s e

p e e t h rhtcu e a d d sg ig o y tm e e o n ay s a e ts se rs n ste ac i t r n e inn fs se lv lb u d r c n t s y tm. I lo p ee t h t o f e t as rs n s t e meh d o

0 引 言

边 界扫 描技 术 的应 用 提 高 了 电路

1 1 MTV B s 介 . 1- u 简 I

观察性 , 解决了现代电子技术发展带来 的测试 问题。但是

随着 电路 系统复 杂度 不断 提 高 , 个 系统 甚 至 可 以划 分 为 整 多个 子系 统 时 , 采 用 扩 展 I E 19 11 仅 E E 14. l 边界 扫 描 总 线

Le Ja Hu n n Ya eo g Ch n Ka i i a gKi nXu ln e i

( p rme to e to i De a t n fElcr ncEngn e ig, ii ie st fElcr ncTe h olg Guln 5 0 4) ie rn Gu l Unv riy o eto i c n o y, i 41 0 n i

g n r l v i b l y a d i c n a c mp ih t e f u t da n s sa d l c t n p o e l . e e a al i t , n t a c o a a i l h a l ig o i n o a i r p ry s o Ke wo d : M TM - s b u d r c n t s ;t s y t m y rs u B ; o n a y s a e t e ts s e

边界扫描测试原理

边界扫描测试原理边界扫描测试是一种黑盒测试方法,其中测试人员专注于程序的边界条件。

该方法旨在检测程序在处理边界条件时是否存在问题,例如程序的最大和最小输入值,以及输入值与最大和最小值之间的情况。

边界扫描测试方法适用于各种程序,包括软件应用程序、Web应用程序和嵌入式系统等。

边界扫描测试方法可以确保程序在处理边界条件时具有正确的行为,并且不会出现错误或异常情况。

这种测试方法可以帮助测试人员发现程序的潜在缺陷,并且可以改进程序的质量和可靠性。

边界扫描测试方法通常包括以下步骤:1. 确定输入值的最大和最小值测试人员需要确定程序所期望的最大和最小输入值。

这可以通过查看程序的规范或文档来实现。

如果程序没有明确的规范或文档,则测试人员需要自己确定最大和最小值。

2. 确定输入值与最大和最小值之间的情况测试人员需要确定输入值与最大和最小值之间的情况。

例如,如果程序要求输入数字,则测试人员需要确定输入数字的最大和最小值,并确定输入数字与这些值之间的情况。

3. 编写测试用例测试人员需要编写测试用例来测试程序的边界条件。

测试用例应包括最大和最小输入值以及输入值与最大和最小值之间的情况。

测试用例应覆盖所有可能的情况,并且应该能够测试程序的所有功能。

4. 运行测试用例测试人员需要运行测试用例并记录测试结果。

如果测试用例中出现错误或异常情况,则测试人员需要将其记录下来并报告给开发人员。

5. 分析测试结果测试人员需要分析测试结果,并确定程序在处理边界条件时是否存在问题。

如果存在问题,则测试人员需要将其报告给开发人员,并协助开发人员解决问题。

总结边界扫描测试方法是一种有效的黑盒测试方法,可以帮助测试人员发现程序在处理边界条件时的潜在缺陷,并改进程序的质量和可靠性。

边界扫描测试方法需要测试人员确定输入值的最大和最小值,并编写测试用例来测试程序的边界条件。

测试人员需要运行测试用例,并记录测试结果。

最后,测试人员需要分析测试结果,并将问题报告给开发人员。

jtag边界扫描的概念

jtag边界扫描的概念

边界扫描(Boundary Scan)是一种测试技术,用于在集成电路板内进行测试,特别是对于那些无法通过传统的测试方法进行测试的复杂电路板。

它利用在每个芯片的输入输出管脚上增加的移位寄存器单元(Boundary-Scan Register Cell),这些寄存器单元分布在芯片的边界上,被称为边界扫描寄存器。

在JTAG调试中,边界扫描是一个非常重要的概念。

当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制。

对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。

正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

它可以串行地输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制。

一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过TAP(Test Access Port)Controller来完成。

以上内容仅供参考,如需更多信息,建议查阅相关文献或咨询专业人士。

边界扫描测试系统

边界扫描测试系统一、IEEE1149.1产生的背景当今电子制造商正面临着越来越大的降低成本、提高质量及缩短生产周期的压力,电路板越来越密、器件越来越复杂、电路性能要求也越来越苛刻,这一切直接导致了电子器件的生产商和电子产品的制造商都在倾向于采用最新的器件技术,如GA、CSP、TCP 等更小的封装,以更小的体积提供更强的功能。

但是随之而来的接入问题却日益成为测试的巨大障碍。

为了解决此类问题,IEEE1149.1———边界扫描测试技术应运而生。

二、边界扫描测试的原理边界扫描测试是一种可测试结构技术,它采用集成电路的内部外围所谓的“电子引脚”(边界)模拟传统的在线测试的物理引脚,对器件内部进行扫描测试。

它是在芯片的I/O端上增加移位寄存器,把这些寄存器连接起来,加上时钟复位、测试方式选择以及扫描输入和输出端口,而形成边界扫描通道。

IEEE1149.1标准规定了一个四线串行接口(第五条线是可选的),该接口称作测试访问端口(TAP),用于访问复杂的集成电路(IC),例如微处理器、DSP、ASIC 和CPLD等。

在TDI(测试数据输入)引线上输入到芯片中的数据存储在指令寄存器中或一个数据寄存器中。

串行数据从TDO(测试数据输出)引线上输出。

边界扫描逻辑由TCK(测试时钟)上的信号计时,而且TMS(测试模式选择)信号控制驱动TAP控制器的状态。

TRST*(测试重置)是可选项,可作为硬件重置信号,一般不用。

详细边界扫描结构及信号流程参考图1。

图1中“TAP Controller”其实质上是一个状态切换到6个不同的状态,具体状态逻辑参考图2。

从一个状态切换成另一个状态总是发生在TCK的上升沿,由TMS 从两个状态选择其中一个状态。

在测试向量寄存器中,既有指令寄存器(IR),又有数据寄存器(DR),而且,为了区分是指令还是数据,扫描链路中的状态图有两个独立的完全类似的结构(Scan DR/ Scan IR)。

测试操作的最重要步骤是移入和同步移出测试数据(DR SHIFT),新的数据进入移位链,测试数据传送到测试单元DR-update)的输出锁存器中,对于指令寄存器(IR-shift,IR-capture,IR-update)同样如此。

boundaryscan应用实例 -回复

boundaryscan应用实例-回复什么是boundary scan技术?Boundary scan技术,又称JTAG(Joint Test Action Group)技术,是一种用于芯片级电路板测试和诊断的技术。

它使用了IEEE标准1149.1定义的边界扫描链(Boundary Scan Chain),通过在电路板上的闩锁功能来实现对芯片上的引脚的测试和调试。

Boundary scan技术的原理和功能如何工作?Boundary scan技术的原理基于一种边界扫描链结构(Boundary Scan Chain),该链将所有芯片引脚连接起来形成一个环。

这个环具有使能信号和测试控制信号,通过这些信号的控制,可以将测试数据从一个引脚传输到另一个引脚,实现对芯片引脚的测试和调试。

Boundary scan技术的功能主要有以下几个方面:1. 电路连通性测试:通过boundary scan技术,可以检测和诊断电路板上信号线的连通性是否良好,以及是否存在断路和短路。

2. 引脚功能测试:通过boundary scan技术,可以实时测试和诊断芯片引脚的功能是否正常。

这对于芯片级的调试和故障排除非常有用。

3. 元件配置和诊断:通过boundary scan技术,可以识别和配置电路板上的各种元件,例如存储器、逻辑门等。

这可以帮助工程师更好地了解电路板的组成和功能。

4. 容错性检查:通过boundary scan技术,可以检查电路板上的信号线是否遵循电气特性,例如正确的电阻和电容值。

这对于确保电路板的稳定性和可靠性至关重要。

Boundary scan技术的应用实例1. 电子设备制造:Boundary scan技术可以在生产线上用于测试和验证电子设备的电路板,以确保其质量和可靠性。

它可以有效地检测和排除电路板上的连通性问题和故障,提高生产效率和产品质量。

2. 电路板维修:当电子设备发生故障时,boundary scan技术可以用于定位和修复故障点。

jtag标准ieee1149.1解析

IEEE1149.1标准是一项用于测试和故障诊断集成电路的重要标准,而JTAG(Joint Test Action Group)是这项标准的主要推动者之一。

本文将对IEEE1149.1标准进行解析,从其定义、原理、应用等多个角度进行分析,帮助读者更好地理解和应用这一标准。

一、 IEEE1149.1标准的定义IEEE1149.1标准,也称为边界扫描标准或JTAG标准,是一项由IEEE 制定的用于测试集成电路的标准。

该标准于1990年发布,已被广泛应用于半导体工业、电子制造业等领域。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试和调试,从而提高了集成电路的可靠性和稳定性。

二、 IEEE1149.1标准的原理1. 边界扫描链IEEE1149.1标准的核心是边界扫描链(boundary scan ch本人n),通过在集成电路的引脚上添加扫描逻辑,实现了对芯片内部连接和状态的测试。

这种边界扫描链可以将芯片的内部引脚与外部引脚进行连接,从而实现对芯片内部信号的观测和控制。

2. TAP控制器IEEE1149.1标准还引入了TAP(Test Access Port)控制器,用于与边界扫描链进行通信和控制。

TAP控制器可以对边界扫描链进行初始化、数据传输和状态控制,从而实现对集成电路的测试和调试。

三、 IEEE1149.1标准的应用1. 芯片测试IEEE1149.1标准最主要的应用是用于集成电路的测试。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试,从而发现潜在的故障和缺陷。

2. 芯片调试除了测试功能,IEEE1149.1标准还可以用于集成电路的调试。

通过边界扫描链和TAP控制器,工程师可以对集成电路进行状态观测和信号控制,从而快速定位和分析故障原因。

3. 芯片编程IEEE1149.1标准还可以用于集成电路的编程。

一些可编程逻辑器件(如FPGA)可以通过边界扫描信息口进行编程,实现对逻辑器件内部配置和状态的控制。

Boundray scan技术原理

1边界扫描测试技术原理2.边界扫描指令集Extest指令--强制指令用于芯片外部测试,如互连测试测试模式下的输出管脚,由BSC update锁存驱动BSC scan锁存捕获的输入数据移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存原先EXTEST指令是强制为全“0”的,在IEEE 1149.1—2001中,这条强制取消了。

选择边界扫描寄存器连通TDI和TDO。

在这种指令下,可以通过边界扫描输出单元来驱动测试信号至其他边界扫描芯片,以及通过边界扫描输入单元来从其他边界扫描芯片接受测试信号。

EXTEST指令是IEEE 1149.1标准的核心所在,在边界扫描测试中的互连测试(interconnect test)就是基于这个指令的。

Sample/Preload指令编辑Sample/Preload指令--强制指令在进入测试模式前对BSC进行预装载输入输出管脚可正常操作输入管脚数据和内核输出数据装载到BSC的scan锁存中。

移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存。

原先这两个指令是合在一起的,在IEEE 1149.1--2001中这两个指令分开了,分成一个SAMPLE指令,一个PRELOAD指令。

选择SAMPLE/PRELOAD指令时,IC工作在正常工作模式,也就是说对IC的操作不影响IC的正常工作。

选择边界扫描寄存器连通TDI和TDO。

SAMPLE指令---通过数据扫描操作(Data Scan)来访问边界扫描寄存器,以及对进入和离开IC的数据进行采样。

PRELOAD指令---在进入EXTEST指令之前对边界扫描寄存器进行数据加载。

Bypass指令编辑Bypass指令--强制指令提供穿透芯片的最短通路。

输入输出管脚可正常操作选择一位的旁路(Bypass)寄存器强制全为1和未定义的指令为Bypass指令BYPASS指令为全“1”。

边界扫描技术及其应用

边 界 扫 描 技 术 及 其 应 用

焦 运 良 ,徐 炳 吉 ,刘 凯

( 中国地 质大学 ( 京)信 息工程学院 ,北京 北 10 8 ) 0 0 3

摘要 :边界 扫描技术作 为新技 术下高集成度 电路板 的测量工具 ,已经越来越受到人们 的青睐。介 绍 了边界 扫 描各模块 的功能及 它们之间的相 互关 系, 以及 国 内外广泛 使用 的边界 扫描 软件 A S T的原理 和工 作过 程, SE 避 免在使用 A S T软件过程 中,因导入错误 的网络表 而导致 扫描 失败 。 SE 关键词 :边界 扫描;A S T;针床 ;寄存器 SE 中图分类号 :T 3 4 2 2: M90 1 P 3 . T 3 . 2 文献标识码 :A

2 1 年 第 5期 01

3 边 界扫描 过 程的 1 6种 状态 边界 扫描 过程 可 以分 为 l 6种状 态 ,也 就是 边 界

个 边界 扫描 指令 ,见表 l 。每个 指 令 采 用 6位 二 进 制

扫描 控 制 单 元 中 T P控 制 器 的 1 A 6种 不 同 的状 态 。 T P的 l A 6种不 同状 态是 在 T MS ( 试 模式 设 置 ) 的 测 不 同设 置 ,在 T K的驱动 下 而转化 的 ,转化 过 程如 2 C

T MS ( et d l St T s Moue e,测 试模 式设 置 ) R T ( et 、T S T s

边 界 扫 描 技 术 是 IE 组 织 在 19 年 推 行 的 EE 90

I E I 4 1 1边 界扫 描标 准后 形成 的一 种 流行 的可测 E E 9 . 1

制边界扫描控制单元实现的。边界扫描控制单元中包

收稿 日期 :2 1—3 0 ;修 回 日期 :2 1-5 1 0 10 —9 0 10 .8

边界扫描技术在板级可测性设计中的应用

Group, 简称JTAG ) 提出了边界扫描技术, 后来在

1990 年被批准为 IEEE 1149.1 标准。边界扫描测试 ( BST ) 是面向电路板测试的一种芯片可测性设计

由图 1 可知,每个 1/O 管脚都有一个 BSC,每 测试数 个 BSC 有两个数据通道— 正常数据通道、

据通道 。各边界扫描单元 ( BSC ) 以串行方式连接 成扫描链 ,既可以通过扫描输人端将测试矢量以串

方法1 它通过存在于器件输人输出管脚与内核电 21,

路之间的边界扫描单元 ( BSC ) 对器件及外围电路 进行测试,从而大大提高了器件的可控性和可观察

行扫描的方式输人,对相应的管脚状态进行设定, 实现测试矢量的加载; 也可以通过扫描输出端将系 统的测试响应串行输出,进行数据分析与处理。可 见 ,边界扫描技术不仅可测芯片或 PCB 的逻辑功 能,还可以测试 IC 之间或 PCB 之间的连接是否存 在故障。 边界扫描测试的物理基础是边界扫描测试总线 和设计在器件内的边界扫描结构。边界扫描测试总 线由 TDI , TDO, TMS , TCK, TRST 构成,主要

器件管脚的设定、读取和隔离。TAP 控制器控制整 个边界扫描机制的操作, 其核心是 16 个工作状态转 换机制,状态转换由 TCK 采样 TMS 的值来实施。

结构。利用这些扫描结构实现一个和多个的扫描链

2 基于 J丁 的测试类型及可测性设计方法 AG

2.1 基于JTAG 可实现的测试类型

应用边界扫描技术,可实现器件间互连通路测

性,很方便地完成从器件级直至系统级的测试。 边界扫描技术很快就得到了世界大多数集成电 路制造商和测试商的支持,目 90% 以上复杂的芯 前 片 ( 尤其 VLSI ) 都带有边界扫描结构,支持 IEEE 1149.1 标准。

边界扫描测试方法

边界扫描测试方法

嘿,咱今儿来聊聊边界扫描测试方法呀!这玩意儿可神奇啦,就像是给电子设备做了一次全面又精细的体检。

你想啊,一个电子设备里面那么多复杂的电路和元器件,就好像是一个庞大的迷宫。

那怎么才能知道这个迷宫里有没有问题呢?边界扫描测试方法就派上用场啦!它就像是一个超级侦探,能一点点地去排查每一个角落。

它是通过在芯片的边界上设置一些特殊的引脚来实现的。

这些引脚就像是一个个小眼睛,能观察到芯片内部的情况。

比如说,它可以检测芯片之间的连接是否正常,有没有短路或者开路的情况。

这多重要啊,要是连接有问题,那整个设备不就乱套啦!

而且哦,边界扫描测试方法还特别灵活。

它可以根据不同的需求和情况,进行各种不同的测试。

就好像你有一套工具,你可以根据要修的东西不同,选择不同的工具来干活儿。

它还能帮助我们在生产过程中及时发现问题。

你想想,要是生产了一大批产品,最后才发现有问题,那得多麻烦,多浪费啊!但有了边界扫描测试方法,就能早早地把问题揪出来,及时解决,多省心啊!

这就好比是我们出门前要照照镜子,看看自己有没有穿戴整齐。

边界扫描测试方法就是给电子设备照镜子,确保它们能以最好的状态工作。

它还能提高设备的可靠性呢!就像我们锻炼身体,让自己更强壮,不容易生病一样。

通过边界扫描测试,能让设备更稳定地运行,减少出故障的概率。

咱再想想,要是没有这个方法,那电子设备出问题了可咋办?那可就像没头苍蝇一样,不知道从哪儿开始找问题啦!所以说,边界扫描测试方法真的是太重要啦!它是电子设备领域的好帮手,是保障设备正常运行的关键一环啊!大家可千万别小瞧了它哟!。

基于边界扫描技术的PCB测试

信 号和控 制信 号 ,就 可以方 便 的观察 和

控 制处在调 试状态 下的 芯片 。 图l 展示了一个芯片的边界扫描逻辑

sa elsg as c n c l in l)

1引言 .

我们知道早期雷达 的数字处理技术水 平较低 ,我国第一 代采 用脉 冲压缩技 术的 警戒雷达甚至是用模拟器件 ( 声表面波滤 波 器)而非数字 器件来压缩雷达 回波 。随 着大规 模集成电路和计算 机技术的发展 越 来越 多的 高性 能 通用 及 专用 C P U 、

边界扫描寄存器。当芯片处于调试状态 l 的时 候 ,这些 边界扫 描寄 存 器可以将 芯 】

些边界 扫描 单 元 ,可以 实现对 芯 片输 入 :

片和 外 围的输 入输 出隔离 开来 。通 过这 I sg a s in l)

D P P S 、F GA等超 大规模数 字器件在雷达 输 出信号 的观察 和控 制 。 对于 芯 片的输 入 管脚 ,可 以通 过 与 中被广泛使用 。 雷达 中使用的 P B 来越 C 越 之相 连 的 边界 扫 描单 元 把 信 号 ( 据 ) 数 复杂 ,器件安装密度也越来越高 ,我们 以

来 ,在 芯 片 的 周 围 形 成 一 个 边 界 扫 描 链

2 边界扫描技术 的能力及应用条 .

件

上 世纪八 十年 代 ,联 合测 试行 动工 作组 (TAG)开发出边界扫描的测试规 J

范 , 个 规 范 后 来 被 制 定 为 I E l4 . 这 E E 9 卜 1

TAP ( s Ac es P r )是一个 Tet c s o t

是通过 J A T G端口来进行配置、加载的。1

Boundary Scan测试原理及实现

什么是边界扫描(boundary scan)?Boundary Scan测试原理及实现JTAG标准的IC芯片结构IEEE 1149.1 标准背景JTAG什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

dft的测试方法

dft的测试方法DFT的测试方法概述DFT(Design for Testability,测试性设计)是一种设计方法,旨在确保电子设备的可测试性和可靠性。

它包括在设计过程中引入测试功能,以便更容易地检测和诊断设备的故障。

本文将介绍DFT的测试方法,并探讨其在电子设备制造过程中的重要性和应用。

1.扫描链测试扫描链测试是DFT中最常用的测试方法之一。

它通过在设计中引入扫描链,将电路分成多个扫描链,使得测试信号可以从输入端口进入电路,然后通过扫描链输出。

这种方法可以大大简化测试过程,提高测试覆盖率和效率。

同时,扫描链测试还可以检测到电路中的短路、开路和延迟故障等问题。

2.边界扫描测试边界扫描测试是一种用于测试集成电路(IC)边界的DFT技术。

它通过在IC设计中引入边界扫描链,将输入和输出端口与边界扫描链相连接,从而实现对IC边界的测试。

边界扫描测试可以有效地测试IC边界上的逻辑和电气特性,并提供高测试覆盖率和可靠性。

3.存储器BIST测试存储器BIST(Built-In Self-Test,内建自测试)是一种用于测试存储器的DFT技术。

它通过在存储器中内置测试电路和算法,实现存储器的自测试。

存储器BIST测试可以在芯片制造过程中自动进行,无需外部测试设备,大大提高了测试效率和可靠性。

4.电路自适应测试电路自适应测试是一种基于DFT的自适应测试方法。

它通过在电路中引入自适应测试电路,实现对电路的自动测试和故障诊断。

电路自适应测试可以根据电路的实际工作状态和测试需求,自动选择最佳的测试算法和参数,提高测试效率和准确性。

5.故障模拟测试故障模拟测试是一种基于DFT的故障检测方法。

它通过在设计中引入故障模拟电路,模拟故障情况,然后利用模拟结果进行故障检测和诊断。

故障模拟测试可以帮助设计人员了解电路的故障情况,优化设计和测试策略,提供更可靠的电子设备。

6.片上监测测试片上监测测试是一种用于监测电子设备工作状态的DFT技术。

边界扫描测试的原理及应用

C T R R 时 ,所 有 的扫 描 单 元 都 能 在 CL K AP U E D OC

DR 的上 升 沿取 样输 入 数据 。 测试 数据 的输 出也相 类

似 , 它是 在T AP状 态 在 P A E D 的下 降沿 时 将 扫 D T R

描 输入 端锁存 并输 出。 所有 的扫描 单 元都 能完成 以上

数据 稳 定后 ,第 二个 锁存 器 由UP A EDR控制 锁 存 D T

输 出第 一个 锁 存器 移 出 的数据 。 MODE信 号 的 电平 决定 是 测试模 式还 是工作 模式 。边 界扫描 单 元 既有 输

入又 有输 出。 一般 来说 ,在每 一 个物理 引脚 不论输 入

还是 输 出 ,都 有一 个独 立 的边 界扫 描单 元 ,但 区别是 输 入在每 一个 物理 引脚 的后面 ,而对于 所 有的输 出是

图 1中 “ APC nrl r 其 实 质 上 是 一 个 状 态 T ot l ” oe

机 , 它根 据 不 同 的操 作 指 令 能 产 生 1 6个 不 同 的 状 态 ,具 体状 态 逻辑 参 考 图2 从 一个 状 态切 换 成另 一 。 个状 态 总 是 发生 在T K 的上升 沿 , 由T C MS从 两个 状

试 。 它是 在 芯 片 的I / 上 增加 移 位 寄 存器 ,把 这 些 O端

寄存 器连 接起来 ,加 上 时钟复 位 、测试 方式选 择 以及

62

f 墼

维普资讯

( C N)或 者 是 扫描 输 入 的数 据 ( A A I) S AN I D T ,并 N 且 由C OC R 制锁 存输 出。 在第 一个 锁存 器移 出 L KD 控

在每 一个 物理 引脚 的前面 。 态。 T S 测 试 重置) 可选 项 ,可作 为硬件 重 置信 RT( 是 号 ,一般 不用 。详 细边界 扫描 结构 及信号 流 程参 考图

边界扫描测试技术

移位寄存器波形

16

(1)抽样/预加载指令模式

移位寄存器波形 抽样/预加载指令码通过TDI引脚移入,TAP控制器向前移

到CAPTURE-DR状态,然后进入SHIFT-DR状态,如果TMS维 持在低电平,则TAP控制器始终保持在该状态。从TDO引脚移 出的数据由在捕获阶段之后存于捕获寄存器的数据组成。移入 TDI引脚的新测试数据在时钟的控制下通过整个边界扫描寄存 器之后,出现在TDO引脚上。

边界扫描单元bsc的连接图核心逻辑为了测试两个jtag设备的连接首先将jtag设备1的某个输出测试脚的bsc置为高或低电平输出至ndo然后让jtag设备2的输入测试脚来捕获从管脚输入的ndi值再通过测试数据通道将捕获到的数据输出至tdo对比测试结果即可快速准确地判断这两脚是否连接可靠

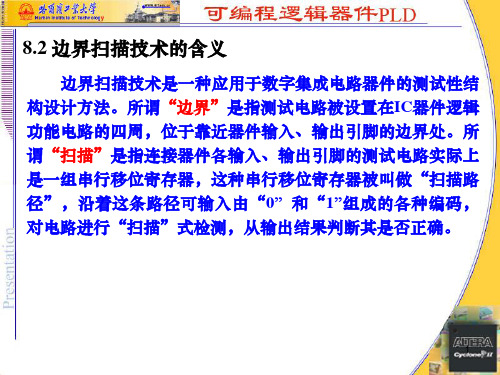

8.2 边界扫描技术的含义

IC3的F引脚寄存器接收IC1的E脚寄存器信号,正

常情况下F脚的值应该为1,但如果引线EF发生了断路,

则从F脚得到的值不是1,而是0。

19

UESCODE串行移到TDO。

选 择 UESCODE 寄 存 器 放 置

0000000110 在 UETSDCIO和DET串DO行之移到间T,D1O3允。许

8.5 BST操作控制

为了启动BST操作,必须选择指令模式。方法是使TAP控 制器向前移位到指令寄存器移位(SHIFT_IR)状态,然后由时 钟 控 制 TDI 引 脚 上 相 应 的 指 令 码 。 从 RESET 状 态 开 始 , TMS(测试模式选择引脚)受时钟作用,使TAP控制器运行前进 到SHIFT-IR状态。具有代码01100

边界扫描在线缆测试中的应用

边界扫描在线缆测试中的应用摘要:针对传统的电缆检测,如采用万用表、试灯、兆欧表等设备逐点检测电缆中每条电线的通断及绝缘特性的方法,检测效率较低,而且易造成错检、漏检,无法满足生产和使用的要求。

本文设计出一种计算机和边界扫描相结合的线缆故障检测系统方案,并阐述了测试原理和系统组成结构。

关键词:电缆检测边界扫描自动测试1引言随着测试技术的发展,边界扫描测试技术以其非常高的故障覆盖率、故障诊断时间短、设备量低、成本低、测试工程开发简单等优势,越来越广泛的应用于电子测试中。

随着武器装备的现代化,线缆的使用也呈现多批量、多品种、多芯数,测试也愈发的困难。

急需一种能实时、高效准确测量线缆通断、短路、错接性能的测试方法。

本文根据电线电缆测试技术的发展及工作现场的实际需要,设计了一种电缆组件快速测试系统。

该系统以边界扫描技术为基础,利用边界扫描器件为接口电路,从而实现多种电缆的测试,检测电缆的通断、错接、短路的情况,从而达到快速检测电缆联通性能的目的。

2工作原理及电路设计:2.1 系统原理描述该测试系统由上位机、测试底板、适配器等组成。

测试底板主要由边界扫描器件,测试插槽组成,其中测试插槽中包涵成组常用的各种连接器,测试原理如下图所示:2.2 测试底板测试底板以一块大规模集成电路EP10K50为核心,若干路TTL输入输出接口,TTL输入输出接口均与FPGA相连。

从FPGA输出的信号,通过接口电路,经被测电缆,返回到FPGA中.3系统应用举例以J30J-21电缆为例,说明边界扫描测试的开发流程,该测试系统主要由装有ScanWorks软件的上位机,边界扫描控制器和JTAG桥组成。

由于该测试底板只包涵一块FPGA,若干路TTl输入输出接口,TTl输入输出接口均与FPGA相连。

从FPGA输出的信号,通过接口电路,经被测电缆,返回到FPGA中,因此仅需进行SPV测试以及互连测试。

3.1扫描链完整性测试分析原理图找到扫描链路后,输入该被测板上边界扫描器件的BSDL文件,这里,必须注意BSDL文件是由器件厂商提供,语法和语义有存在错误的可能,因此要校验BSDL文件的正确性,当确定无误,输入所有相关信息后,即可进行扫描链完整性测试。

用边界扫描技术检测非边扫器件

用边界扫描技术检测非边扫器件I. 引言- 简述非边扫描器件的概念及应用背景- 阐述目前检测非边扫描器件所面临的困难和挑战II. 综述边界扫描技术- 介绍边界扫描技术的基本原理和特点- 讨论边界扫描技术在检测集成电路中的应用情况III. 基于边界扫描技术的非边扫描器件检测方案- 提出基于边界扫描技术的非边扫描器件检测方案- 阐述该方案的实现方法IV. 方案实验与结果分析- 设计实验样本集并进行实验测试- 分析实验结果,评估方案的检测能力和鲁棒性V. 结论- 总结该非边扫描器件检测方案的优势和局限性- 展望该方案在未来的应用前景及发展方向附:参考文献边界扫描技术是针对数字集成电路(Integrated Circuit,IC)的一种测试技术。

随着集成电路技术的飞速发展,集成度逐渐提高,而集成度的提高也意味着芯片的复杂度将会不断增加,测试成为设计和制造中的核心问题之一。

因此,边界扫描技术应运而生,被广泛应用于芯片测试、故障定位等领域。

其主要原理是在芯片电路的边缘添加额外的控制逻辑,使得这些逻辑可以通过扫描链(SCAN Chain)或者测试向量实现对芯片中部的逻辑单元(logic cell)的任意访问,从而实现对芯片进行完整测试和故障检测。

目前,边界扫描技术已经成为了集成电路测试领域的主流技术之一。

边界扫描技术最初是用于边缘所处的测试程序,常被称为Boundary-Scan,后来不断发展,并广泛应用于各种汽车、飞机、医疗等电子器件的测试中。

据统计,目前已经有超过90%的现代器件集成了边界扫描技术。

此外,随着数字系统的迅速变化,复杂性越来越高,加上我们要减少设计调试的时间,遇到放大比赛技术上的小问题也可能成为一场惨痛的经验,因此边界扫描技术也可以用于故障诊断和电路分析的方面。

但是,在实际应用中,边界扫描技术仅适用于带有边缘扫描逻辑的芯片。

而对于一些没有边缘扫描逻辑的非边缘扫描器件,如异步逻辑、多级管脚等,传统的边缘扫描技术往往无法应用。

边界测试技术原理

4.7 边界扫描的主要应用-VCCT

4.8 边界扫描的主要应用-VCCT

VCCT:Virtual Component Cluster Test

4.10 边界扫描的主要应用-PPT

PPT:Parallel Port Test

通 过 计 算 机 并 口 进 行 BS测 试 , 不 需 要 其 他 任 何 设 备 可 以 测 试 到 5种 类 型 的 网 络 : 纯 粹 的 BS器 件 之 间 的 网 络 ( VIT) ; VC C T的 网 络 ; 上 下 拉 的 网 络 ; 有 测 试 点 的 网 络 ; TAP 口 的 网 络 。

5.1 边界扫描设计规范

JTAG 管脚上下拉须符合规 范,且都有测试点。 尽可能使用 2× 5PIN 插 座。 尽可能连成一条菊花链。 应能保证菊花链的信号质 量。 DKBA01-200101-010 《 JTAG 接口电路设计规 范》 DKBA3551-2001.08 《 ICT 可测性设计规范》

0 0

0

0

2.5 TAP控制器

TAP 控 制 器 是 16-states 的 有 限 状 态 机 TAP 控 制 器 的 状 态 在 TCK 的 上 升 沿 变 化 TAP 控 制 器 在 上 电 时 进 入 逻 辑 复 位 状 态 Shift-IR state 扫 描 IR , TDO 输 出 有 效 Shift-DR state 扫 描 DR , TDO 输 出 有 效 其 它 状 态 下 TDO 输 出 无 效

3.4 BYPASS指令的执行

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

What FPT Can TEST?

• 類比元件的值 • 特性

Intelligent Boundary Scan Solutions®

• Resistor • Capacitor • Inductor • Transistor

• 臨近元件的短路測試 • Non-BGA IC腳的

• 無治具 ICT 測試

Bscan Cell

BScan nets

BScandevice

non

BScan IC

BScandevice

BScandevice

TAP

TAP

TAP

TMS TCK

Testbus interconnection

TDI

測試存取埠

TAP = Test Access Port

9/21/2014

TMS = Test Mode Select TCK = Test Clock TDI = Test Data In TDO = Test Data Out

• 簡易型AOI功能 • 速度稍慢 • 可涵蓋所有被動零

開路測試 • 上電後電壓/電流測試

BScan Basics

件測試 • 短路測試為選擇性 考量

What Boundary Scan Can Test

• 數位邏輯 IC 零件: •

Intelligent Boundary Scan Solutions®

9/21/2014 BScan Basics No. 13

IEEE-1532=> In-System-Programming

Conclusion

Intelligent Boundary Scan Solutions®

• IEEE 1532 can be used for programming of

<5> Non-BGA IC腳的開路測試

<6> 可在板上燒錄資料(ISP) Flash / EEPROM

(ISP) PLD / FPGA Devices <7> 內部邏輯電路之功能測試

BScan Basics

IEEE-1149.1

Testbus Signals

Intelligent Boundary Scan Solutions®

TCK TMS TDO TDI

PIN2 PIN4 PIN6 PIN8

GND GND GND GND NC

TRST PIN10

BScan Basics

串接方式為TMS,TCK,TRST並聯 ,TDI,TDO串聯

Intelligent Boundary Scan Solutions®

TDI

TDO

TDO TMS TCK TDI

n

Bypass Register

0

TDO

Instructions Register TCK TMS

TAP Controller

9/21/2014

BScan Basics

No. 12

IEEE-1532

In-System Programming

Intelligent Boundary Scan Solutions®

• Programming devices (volatile or non-volatile)離散元件

mounted on a PCB through IEEE-1149.1 compliant TAP =>PLD / FPGA Devices • Programmable devices compliant to IEEE-1532 have a system mode and a test mode: • System mode: differentiates 4 system modal states: • Unprogrammed (在未寫入資料前) • ISC Accessed (ISC Data file寫入) • ISC Complete (ISC Data file完成 ) • Operational (驗證) • Test mode :conform to IEEE-1149.1

3. Test Mode Select (TMS) 4. Test Clock 5. Test Reset (TCK) (TRST) =>可以省略不用

BScan Basics

*註=>通常用六個Clock,當作一個Reset

Intelligent Boundary Scan Solutions®

Boundary Scan Test測試之原理(三) 所謂[測試存取埠]:TAP(Test Access Port) =>係指為進行測試邏輯電路之指令,測試 數據或測試結果等數據加入輸入/輸出之串 列介面,上述4條信號線,經由外界之電 腦主機加以控制,以便執行BScan測試。

BScan Basics

Boundary Scan Test測試之功能

Intelligent Boundary Scan Solutions®

<1> 元件之誤插接及臨近元件的短路測試

<2> 外界電路與元件間之輸入/輸出信號監視

<3> 元件間之互接測試(Interconnecting Test)

<4> 可測試BGA元件之開路與短路作測試

BScan Basics

TDI,TDO串接方式注意

Intelligent Boundary Scan Solutions®

• Boundary Scan controller 的連接器上的

TDI ,接到串接上第一個 BS IC 的 TDI ,第一個 BS IC 的 TDO 接第二個 IC 的 TDI,以此類推; 最後一個 IC 的 TDO 則接連接器上的 TDO。

*註=>通常用六個Clock,當作一個Reset

BScan Basics

板子上整個連接到 Boundary Scan 的介面連接器

Intelligent Boundary Scan Solutions®

• I/O Interface,10PIN 100mil公的連接器

PIN1 PIN3 PIN5 PIN7 PIN9

BScan Basics

Intelligent Boundary Scan Solutions®

Boundary Scan Test測試之原理(二)

若PCB印刷基板採用BScan測試相容元件時, 最多僅需5條(通常為4條)之專用線,即可測試:

1. Test Data In 2. Test Data Out (TDI ) (TDO)

(包含 BGA )的開短路 測試 • Boundary Scan IC ID 檢查 • DRAM讀寫測試 • Flash , EEPROM 讀寫 測試及資料在板燒錄 (On Board programming)

•

• •

•

特性: 測試速度快(可在一分鐘之 內測完一片主機版) 主要針對有提供 Boundary Scan IC 的量測 主要針對開短路的製程問題 做測試 可分為做治具及不做治具的 方法,治具成本遠比 ICT 治具類便宜。(因測試點變少)

Intelligent Boundary Scan Solutions®

BScan Cell

Test Data In Test Clock

(TDI) (TCK)

Test Access Port

Test Mode Select (TMS)

9/21/2014

(TAP) TCK

Test Data Out (TDO)

• IEEE-1149.5=> system level test • IEEE-1149.6=> Differential & AC coupled

networks

• IEEE-1532

9/21/2014

=> In-System-Programming

BScan Basics No. 3

Intelligent Boundary Scan Solutions®

BScan Basics

TDO

No. 9

IEEE-1149.1

Intelligent Boundary Scan Solutions®

Standard Device

Pin Core Logic

9/21/2014

BScan Basics

No. 10

IEEE-1149.1

BScan Device

Pin Core Logic ... some extra “intelligence” is needed fபைடு நூலகம்r Test Access

No. 11

BScan Basics

IEEE-1149.1

Intelligent Boundary Scan Solutions®

Test Access Port (TAP ) 測試存取埠

Data Register

n 0

BScan Register

31 0

0

MUX

IDcode Register, opt. TDI

History of the Standard

1985 – JETAG (Joint European Test Action Group) 1986 – JTAG (Europe and North America) 1988 – P1149 JTAG v2 (proposal) 1990 – IEEE Std 1149.1 -1990 1993 – IEEE Std 1149.1a-1993 1994 – IEEE Std 1149.1b-1994 (BSDL) 2001 – IEEE Std 1149.1 - 2001