EDA技术与VHDL语言课程大作业设计

eda技术与vhdl设计答案

eda技术与vhdl设计答案eda技术与vhdl设计答案【篇一:eda技术与vhdl复习练习题】/p> 一、填空题1、pld的中文含义是:________。

2、asic的中文含义是:________。

3、“与-或”结构的可编程逻辑器件主要由四部分构成:________、________、____________和____________。

4、可编程逻辑器件结构图中一般用“x”表示此编程单元为________。

6、可编程逻辑器件结构图中无任何标记表示此编程单元为________。

7、可编程逻辑器件按规模的大小一般分为________和_________。

8、低密度可编程逻辑器件的主要有________和_________。

9、gal器件________取代全部pal器件。

10、pal器件只能________次编程。

11、gal器件能________次编程。

12、gal器件________取代ttl器件。

13、gal器件采用________擦除。

14、pal和gal器件________在系统编程。

15、pal和gal器件需要使用________编程。

二、选择题1、可编程逻辑器件pld的基本结构形式是_______:a:与——与b:与——或c:或——与d:或——或2、可以多次编程的器件是_______:a:prom b:plac:pal d:gal3、pld器件未编程时_______:a:有逻辑功能 b:没有逻辑功能c:pal器件有逻辑功能d:gal 器件有逻辑功能 4、gal器件可以用擦除:a:普通光 b:紫外线c:红外线 d:电5、gal16v8器件的输出引脚最多有______:a:16b:4 c:8 d:206、pal16v8器件的输入引脚最多有_______:a:16 b:4 c:8 d:207、gal16v8不能取代_________:a:pal16v b:74ls138c:74ls373 d:isplsi1032e-70plcc848、gal16v8的_______不可编程:a:与阵列b:或阵列c:输出逻辑宏单元olmc d:a、b都三、判断题1、gal器件的输出逻辑宏单元olmc不能实现pal器件的所有输出形式。

EDA大作业

EDA大作业信号发生器的设计要求:(1) 产生方波、三角波、锯齿波、正弦波(2)产生波形的模式可选(3)频率为10KHz设计方案:1.总体设计思路1.1 设计步骤此设计将按模块式实现,据设计要求,设计总共分四大步份完成:(1)产生波形(四种波形:方波、三角波、矩形波和锯齿波)信号;(3)频率为10KHZ幅度固定;1.2设计思想利用VHDL编程,依据基本数字电路模块原理进行整合。

系统各部分所需工作时钟信号由输入系统时钟信号得到。

总体设计框图如下图1所示:波形输出2. 方案论证2.1方案采用VHDL语言来编程,然后下载文件到FPGA来实现。

VHDL语言是电子设计领域的主流硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大降低了硬件设计任务,提高了设计效率和可靠性,要比模拟电路快得多。

该方案是利用FPGA具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性,设计图如图2。

图2 FPGA总体设计图(需要修改) 通过FPGA软件扫描方式将波形数据读出传输给DAC0832(为8分辨率的D/A转换集成芯片)产生波形输出。

这种方法在软、硬件电路设计上都简单,且与我们的设计思路紧密结合。

㈠3硬件选择4软件设计4.1.1 波形产生模块本设计用VHDL语言根据傅立叶函数采集点进行扫描,分别产生正弦波、三角波和矩形波。

以下介绍各种常用周期信号的傅立叶函数展开式。

4.1.3正弦波(1)设计思想正弦波发生分为两个步骤,即正弦波幅值采样存储和正弦波波形的还原输出。

幅值采样是将一个周期正弦波进行64等分,如图3所示,将64个采样点进行量化处理,量化值=255*sin360/64(V),将64点量化值存入存储器ROM。

正弦波形的产生是通过循环反复将存储器中的64点采样值通过DAC0832进行还原输出,得到幅值正比于64点采样值的正弦波。

重庆大学EDA课程设计-EDA课程设计-vhdl语言-12.24小时时钟-乐曲播放电路-函数信号发生器

附录一、12/24小时数字时钟VHDL设计1,系统顶层逻辑图:时序仿真波形管脚定义以及锁定2,分频模块。

①各个分频模块的模块图:②,分别对应的仿真波形:③50mhz分频至1k模块代码:library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity wh4574_divto1k isport(clk50m:in std_logic;clk1k:out std_logic);end wh4574_divto1k;architecture behav of wh4574_divto1k issignal count1:std_logic_vector(14 downto0);signal count2:std_logic;signal co:std_logic;beginprocess(clk50m)beginif clk50m'event and clk50m='1' thenif count1="110000110100111" thencount1<="000000000000000";co<='1';elsecount1<=count1+'1';co<='0';end if;end if;end process;process(co)beginif co'event and co='1' thencount2<=not count2;end if;end process;clk1k<=count2;end behav;50mhz分频至2k模块代码:library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity wh4574_divto2k isport(clk50m:in std_logic;clk2k:out std_logic);end wh4574_divto2k;architecture behav of wh4574_divto2k issignal count1:std_logic_vector(13 downto0);signal count2:std_logic;signal co:std_logic;beginprocess(clk50m)beginif clk50m'event and clk50m='1' thenif count1="11000011010011" thencount1<="00000000000000";co<='1';elsecount1<=count1+'1';co<='0';end if;end if;end process;process(co)beginif co'event and co='1' thencount2<=not count2;end if;end process;clk2k<=count2;end behav;1k分频至5hz代码:library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity wh4574_div1kto5 isport(inclk1k:in std_logic;clk5hz:out std_logic);end wh4574_div1kto5;architecture behav of wh4574_div1kto5 is signal count1:std_logic_vector(6 downto 0);signal count2:std_logic;signal co:std_logic;beginprocess(inclk1k)beginif inclk1k'event and inclk1k='1' thenif count1="1100011" thencount1<="0000000";co<='1';elsecount1<=count1+'1';co<='0';end if;end if;end process;process(co)beginif co'event and co='1' thencount2<=not count2;end if;end process;clk5hz<=count2;end behav;5分频代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity wh4574_div_5 isport(clk:in std_logic;q:out std_logic);end wh4574_div_5;architecture behav of wh4574_div_5 is signal count:std_logic_vector(2 downto 0); beginprocess(clk)beginif clk'event and clk='1' thenif count="100"thencount<="000";q<='1';elsecount<=count+1;q<='0';end if;end if;end process;end behav;。

EDA课程设计报告(交通信号控制器的VHDL的设计)

交通信号控制器的VHDL的设计一、设计任务模拟十字路口交通信号灯的工作过程,利用实验板上的两组红、黄、绿LED作为交通信号灯,设计一个交通信号灯控制器。

能达到的要求:(1)交通灯从绿变红时,有4秒黄灯亮的间隔时间;(2)交通灯红变绿是直接进行的,没有间隔时间;(3)主干道上的绿灯时间为40秒,支干道的绿灯时间为20秒;(4)在任意时间,显示每个状态到该状态结束所需的时间。

支干道主干道图1 路口交通管理示意图二、设计原理1、设计目的:学习DEA开发软件和QuartusII的使用方法,熟悉可编程逻辑器件的使用。

通过制作来了解交通灯控制系统,交通灯控制系统主要是实现城市十字交叉路口红绿灯的控制2、设计说明(1)第一模块:clk时钟秒脉冲发生电路在红绿灯交通信号系统中,大多数情况是通过自动控制的方式指挥交通的。

因此为了避免意外事件的发生,电路必须给一个稳定的时钟(clock)才能让系统正常运作。

模块说明:系统输入信号:Clk: 由外接信号发生器提供256的时钟信号;系统输出信号: full:产生每秒一个脉冲的信号;(2)第二模块:计数秒数选择电路计数电路最主要的功能就是记数负责显示倒数的计数值,对下一个模块提供状态转换信号。

模块说明:系统输入:full: 接收由clk电路的提供的1hz的时钟脉冲信号;系统输出信号:tm:产生显示电路状态转换信号tl:倒计数值秒数个位变化控制信号th:倒计数值秒数十位变化控制信号(3)第三模块:红绿灯状态转换电路本电路负责红绿灯的转换。

模块说明:系统输入信号:full: 接收由clk电路的提供的1hz的时钟脉冲信号;tm: 接收计数秒数选择电路状态转换信号;系统输出信号:b_out: 负责红绿灯的状态显示。

(4)第四模块:时间显示电路本电路负责红绿灯的计数时间的显示。

模块说明:系统输入信号:tl:倒计数值秒数个位变化控制信号;th:倒计数值秒数十位变化控制信号;系统输出信号:led7s1: 负责红绿灯的显示秒数个位。

EDA课程设计--VHDL四路智力抢答器

VHDL四路智力抢答器EDA课程设计一、任务与目的1.1熟练掌握EDA工具软件Quartus的使用1.2熟悉使用VHDL硬件描述语言描述数字电路1.3学会使用VHDL进行大规模集成电路设计1.4学习使用CPLD/FPGA实验系统硬件验证电路设计的正确性1.5初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力二、设计题目与要求2.1设计题目四路智力竞赛抢答器2.2设计要求1.按所布置的题目要求,每一位学生独立完成全过程2.分模块层次化的设计;3.各功能模块的底层文件必须用VHDL语言设计,顶层文件可以用VHDL语言设计,也可以用原理图设计。

2.3设计内容设计一个可容纳四组参赛者同时抢答的数字抢答器。

主持人可控制系统发的清零和抢答的开始,控制电路可实现最快抢答选手按键抢答的判别和锁定功能,并禁止后续其他选手抢答。

抢答选手确定后给出选手编号的显示,抢答选手的编号显示保持到系统被清零为止,若提前抢答则对相应的抢答组发出警告。

*扩展内容:增加答题限时的功能,在确定了抢答成功有效后,有主持人按下答题限时功能键,开始9s的倒计时。

在计时结束后,超时提示LED闪烁。

在主持人按下clear开关时限时复位。

三、功能分析四路智力竞赛抢答器按功能设计分为三个模块1.抢答锁存模块,在主持人发出抢答指令后(start=’1’),若有参赛者按下抢答按钮,则显示器显示抢答组别,同时电路处于自锁状态,使其它组的抢答器不起作用。

主持人可以用清零按钮进行清零(clr=’0’).若抢答指令未发出(start=’0’),而有参赛者按下抢答按钮,则发出警告信号(alm=1).2.显示功能模块,在参赛者抢答信号(组别)发出后,对参赛者信号进行译码,然后用7段数码管显示出来。

3.计时模块,在确定了抢答成功有效后,有主持人按下答题限时功能键,开始9s的倒计时。

在计时结束后,超时提示LED亮。

在主持人按下clear开关时限时复位。

(扩展模块)四、设计思路分析,设计方案合理性分析与选择。

EDA实验报告:基于VHDL语言的交通灯控制系统设计与实现

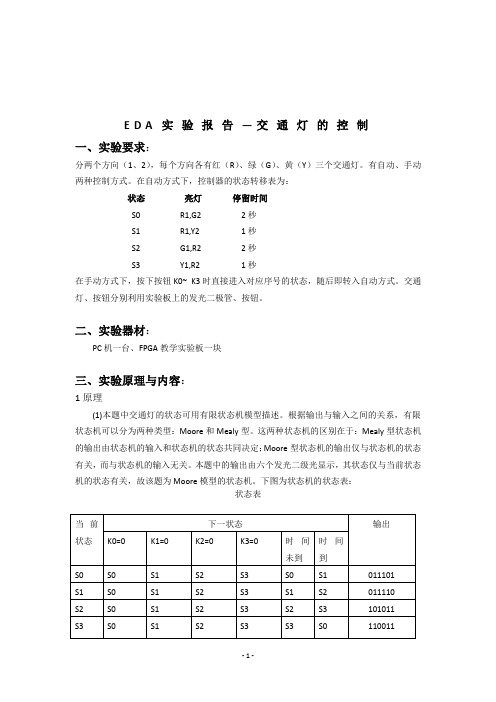

图为k1=0时的输出状态s1,输出恒为011110。即亮灯为R1,y2。保持时间1S。

(k2=0)

上图为k2=0时的输出状态s2,输出恒为101011。即亮灯为G1,R2。保持时间2S。

(k3=0)

上图为k3=0时的输出状态s3,输出恒为110011。即亮灯为R1,G2。保持时间1S。

四、小结及心得体会

else

if counter<5 then

next_state<=s3;

else

next_state<=s0;

end if;

end if;

end if;

end if;

end if;

end case;

end process;

ouput:process(current_state)

begin ——显示程序

begin

u1: jiaotongdeng port map(

clk=>clki,

k0=>k0,

k1=>k1,

k2=>k2,

k3=>k3,

r1=>r1,r2=>r2,g1=>g1,g2=>g2,y1=>y1,y2=>y2

);

u2: div port map(clk=>clk1,clk_out=>clki);

end if;

end if;

end if;

when s3=>

if k0='0' then

next_state<=s0;

else

if k1='0' then

next_state<=s1;

西电eda大作业

EDA实验报告班级:021211班指导老师:杨明磊实验一:QUARTUS II软件使用及组合电路设计仿真一、实验目的:学习QUARTUS II软件的使用,掌握软件工程的建立、VHDL源文件的设计和波形仿真等基本内容;二、实验内容:1.四选一多路选择器的设计首先利用QuartusⅡ完成4选1多路选择器的文本编辑输入(mux41a.vhd)和仿真测试等步骤,给出仿真波形。

(1)、功能及原理原理:数据选择器又称为多路转换器或多路开关,它是数字系统中常用的一种典型电路。

其主要功能是从多路数据中选择其中一路信号发送出去。

所以它是一个多输入、单输出的组合逻辑电路。

功能:当选择控制端s10=00时,输出ay=;s10=01时,输出by=;s10=10时,输出cy=;s10=11时,输出dy=。

(2)、逻辑器件符号(3)、VHDL语言(4)、波形仿真(5)、仿真分析由波形可知:当s10=00时,y的波形与a相同;当s10=01时,y的波形与b相同;当s10=10时,y的波形与c相同;当s10=11时,y的波形与d相同;与所要实现的功能相符,源程序正确。

2、七段译码器程序设计仿真(1)、功能及原理7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD中实现。

实验中的数码管为共阳极,接有低电平的段发亮。

例如当LED7S输出为 "0010010" 时,数码管的7个段:g、f、e、d、c、b、a分别接0、0、1、0、0、1、0,于是数码管显示“5”。

(2)、逻辑器件符号(3)、VHDL语言(4)、波形仿真(5)、仿真分析由仿真波形可以直观看到,当A=“0000”时,led7s=1000000,数码管显示为0;A=“0001”时,led7s=1111001,数码管显示为1;....依此可验证波形仿真结果完全符合预期,源程序正确。

EDA技术与VHDL语言课程设计

课程设计语言班级:电信11-2班姓名:董元伟学号:1106110205指导教师:李铁成绩:电子与信息工程学院信息与通信工程系目录摘要 .............................................................................................................................. - 3 -一、设计目的............................................................................................................... - 4 -二、设计内容和要求................................................................................................... - 4 -1、用户开锁........................................................................................................... - 5 -2、管理员解除警报............................................................................................... - 5 -3、管理员修改密码............................................................................................... - 5 -4、定时返回........................................................................................................... - 6 -三、设计思路和系统结构............................................................................................. - 6 -1、设计模块........................................................................................................... - 6 -2、系统结构和数字密码锁原理图....................................................................... - 7 -3、设计思路........................................................................................................... - 8 -四、实验设计程序如.................................................................................................... - 9 -五、创建测试平台仿真结果....................................................................................... - 21 - 参考文献....................................................................................................................... - 24 -摘要本文介绍一种利用 EDA 技术和 VHDL 语言,在MAX+PLUSⅡ环境下,设计了一种新型的智能密码锁。

eda基于vhdl的课程设计

eda基于vhdl的课程设计一、课程目标知识目标:1. 让学生掌握EDA工具的使用,理解VHDL语言的基本结构和语法。

2. 使学生能够运用VHDL语言进行数字电路设计与仿真。

3. 帮助学生理解并掌握基于VHDL的硬件描述方法。

技能目标:1. 培养学生运用VHDL语言进行实际数字电路设计的能力。

2. 提高学生使用EDA工具进行硬件设计、仿真和验证的技能。

3. 培养学生团队协作、问题解决和创新能力。

情感态度价值观目标:1. 培养学生对电子设计自动化技术及VHDL语言的兴趣和热情。

2. 培养学生严谨的科学态度,注重实验数据和实验结果的准确性。

3. 增强学生的国家意识,认识到我国在EDA领域的发展重要性,激发学生的爱国情怀。

本课程针对高年级学生,结合学科特点和教学要求,将课程目标分解为具体的学习成果。

通过本课程的学习,使学生能够掌握EDA工具和VHDL语言的基本知识,具备实际数字电路设计能力,同时注重培养学生的团队协作、问题解决和创新能力,提升学生的情感态度价值观。

为实现课程目标,后续教学设计和评估将围绕这些具体学习成果展开。

二、教学内容本章节教学内容紧密围绕课程目标,确保科学性和系统性。

教学内容主要包括:1. EDA工具介绍:使学生了解EDA工具的作用,掌握相关软件的操作方法。

- 教材章节:第1章 EDA技术概述2. VHDL语言基础:教授VHDL的基本语法、数据类型、信号和变量等概念。

- 教材章节:第2章 VHDL语言基础3. 数字电路设计方法:通过实例讲解基于VHDL的数字电路设计方法。

- 教材章节:第3章 数字电路设计方法4. VHDL程序结构:介绍VHDL程序的结构,包括实体、架构、过程等。

- 教材章节:第4章 VHDL程序结构5. 常用数字电路设计:教授计数器、寄存器、状态机等常用数字电路的VHDL 实现。

- 教材章节:第5章 常用数字电路设计6. 课堂实践:组织学生进行EDA工具和VHDL语言的实践操作,巩固所学知识。

EDA课程设计(基于VHDL语言的8位数字密码锁设计)

东华理工大学机械与电子工程学院基于VHDL语言的8位数字密码锁设计一、摘要:数字控制的电子密码锁已经广泛应用在办公室、公司、宾馆、小区住宅等场所。

EDA技术的应用引起了电子产品系统开发的革命性变革。

利用先进的EDA工具,基于硬件描述语言,可以进行系统级数字逻辑电路的设计。

本文简述了VHDL语言的功能及其特点,并以8位串行数字锁设计为例,介绍了在QUARTUS II 6.0开发软件下,利用VHDL硬件描述语言设计数字逻辑电路的过程和方法。

关键词: QUARTUS II 6.0 EDA 电子密码锁(电子设计自动化) VHDL语言语言设计串行密码锁硬件描述语言数字逻辑电路Based on VHDL language 8 digits combination lock design Digital control of electronic locks has widely used in office, companies, hotels, residential area and etc.EDA technology application caused a electronic product development system of the revolutionary transformation. Using advanced EDA tools, hardware based description language, can undertake system in digital logic circuit design. This paper describes the function and characteristics of VHDL language, and eight serial number lock design as an example, this paper introduces QUARTUS II 6.0 software development in of VHDLhardware design of digital logic circuit process and method.Keywords: QUARTUS II 6.0, EDA (electronic design automation), electronic locks and VHDL language, language design, serial, locks and hardware description language, digital logic circuit二、引言:电子密码锁系统主要由电子锁体、电子密匙等部分组成,一把电子密匙里能存放多组开锁密码,用户在使用过程中能够随时修改开锁密码,更新或配制钥匙里开锁密码。

南京邮电大学EDA-VHDL程序设计报告 2

南京邮电大学课程设计报告设计类别: EDA-VHDL专业名称: 电子信息工程班级学号: b10010910学生姓名: 0基本题 : 矩阵键盘按键的数码管显示综合题 : 信号发生器设计指导教师: 梅中辉日期: 2013年9月15日—9月30日一课题内容:要求学生设计出4*4矩阵键盘对某一按键按下就在数码管显示一个数字。

按键从左上角到右下角依次为1,2, (16)二对选题的理解键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,我们的思想是,首先固定输出4行为高电平,然后输出4列为低电平,在读入输出的4行的值,通常高电平会被低电平拉低,如果读入的4行均为高电平,那么肯定没有按键按下,否则,如果读入的4行有一位为低电平,那么对应的该行肯定有一个按键按下,这样便可以获取到按键的行值。

同理,获取列值也是如此,先输出4列为高电平,然后在输出4行为低电平,再读入列值,如果其中有哪一位为低电平,那么肯定对应的那一列有按键按下。

获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。

二、获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。

三、实现方案系统原理图1234567890A B CDEF弹跳消除电 路键盘译码电 路键盘扫描电路键盘扫描信号键盘输入按键数据数码管显示分频电路弹跳消抖时钟信号键盘扫描时钟信号系统时钟信号3.1.1 矩阵式键盘扫描的工作原理1234567890A B CDEFKY0(00) 1110KY1(01) 1101KY2(10) 1011KY3(11) 0111键盘扫描信号经提升电阻至VCCKX3KX2KX1KX0图3.2 4*4矩阵式键盘的面板配置矩阵式键盘是一种常用的电子输入装置,在平常的生活中,矩阵式键盘在通信设备如手机,信息终端如计算机,家用电器如油烟机等各式电子产品上都具有很重要的作用。

EDA技术与VHDL第五版课程设计

EDA技术与VHDL第五版课程设计课程设计背景EDA(Electronic Design Automation)技术是电子设计领域的一种重要技术,在现代电子设计中得到广泛应用。

EDA技术可以帮助设计人员提高设计效率、降低设计成本、提高设计质量等方面的效果。

在电子工程的教学中,引入EDA技术是必不可少的。

VHDL(VHSIC Hardware Description Language)是一种硬件描述性语言,用于数字电路、数字系统和数字信号处理系统的设计。

在现代电子设计中,VHDL的应用越来越广泛,为电子设计人员提供了一种快速开发数字电路设计的工具。

因此,在现代电子工程教育中,VHDL的教学也变得十分重要。

本课程设计将结合EDA技术与VHDL第五版的课程内容,提供一种基于FPGA的数字电路设计方法。

在课程设计中,我们将介绍EDA技术的基本概念及其在数字电路设计中的应用,讲解VHDL语言的基本知识和常用语法,以及将EDA技术与VHDL语言结合起来,快速开发数字电路的方法。

课程设计目标本课程设计的主要目标如下:•帮助学生了解EDA技术的基本概念及其在数字电路设计中的应用;•帮助学生学习VHDL语言的基本知识和常用语法;•将EDA技术与VHDL语言结合起来,快速开发数字电路的能力;•提高学生的实际操作能力,培养学生的创新能力和实践能力。

课程设计内容第一部分 EDA技术基础本部分主要介绍EDA技术的基本概念、电路模拟和电路仿真、EDA工具的分类、EDA设计流程等内容。

•EDA技术概述•电路模拟和电路仿真•EDA工具的分类及其特点•EDA设计流程第二部分 VHDL语言基础本部分主要介绍VHDL语言的基本知识、常用语法和应用范围等内容。

•VHDL语言基础•VHDL语言常用语法•VHDL语言应用范围第三部分 FPGA数字电路设计本部分主要介绍FPGA数字电路设计的基本知识、常用工具和开发流程等内容。

•FPGA数字电路设计基础•FPGA数字电路设计常用工具•FPGA数字电路设计开发流程第四部分 VHDL语言在FPGA数字电路设计中的应用本部分主要介绍如何使用VHDL语言在FPGA数字电路设计中快速开发数字电路。

VHDL语言与EDA课程设计-数字频率计【完整版】

VHDL语言与EDA课程设计-数字频率计【完整版】(文档可以直接使用,也可根据实际需要修订后使用,可编辑放心下载)湖南人文科技学院课程设计报告课程名称:VHDL语言与EDA课程设计设计题目:数字频率计系别:通信与控制工程系专业:电子信息工程班级:08级电信二班学生姓名:学号:起止日期: 11年6月13日~ 11年6月23日指导教师:教研室主任:摘要数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置,是计算机,通讯设备、音频设音频视频等科研生产领域不可缺少的测量仪器。

本次课程设计设计以EDA工具作为开发手段,运用VHDL语言,将使整个系统大大简化,提高整体的性能和可靠性。

EDA〔Electronic Design Automation〕即电子设计自动化。

EDA技术指的是以计算机硬件和系统软件为根本工作平台,以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统设计的主要表达方式,自动完成集成电子系统设计的一门新技术。

本设计用VHDL在CPLD器件上实现一种8 位十进制数字频率计测频系统,能够用十进制数码显示被测信号的频率,能够测量正弦波、方波和三角波等信号的频率,具有体积小、可靠性高、功耗低的特点,设计出的频率计能够准确的测出输入信号的频率,最后通过系统仿真,下载、验证和调试运行,实现了一个性能良好的8位数字频率计初步实现了设计目标。

其根本原理是使用一个频率稳定性高的频率作为基准,比照测量其他信号的频率,即计算每秒钟内待测信号的脉冲个数。

该数字频率计可以在不更改硬件电路的根底上,对系统进行各种改良还可以进一步提高系统的性能,而且整个系统非常精简,具有高速、精确、可靠、抗干扰性强和现场可编程等优点,实用性极高。

本文详细描述了数字频率计的设计流程及正确实现。

关键词:数字频率计;EDA;VHDL;QuartusⅡ目录设计要求 (1)1、方案论证与比照 (1)1.1方案比照 (1)1.2方案选择 (2)2.总体模块设计 (2)3.单元模块设计 (3)3.1 顶层模块设计 (3)3.2 测频控制模块 (4)3.3十进位计数模块 (5)3.4 测频锁存模块 (7)4.系统仿真 (8)5.硬件下载测试 (9)6.总结与致谢 (10)参考文献 (11)附录 (12)数字频率计设计要求1.能够显示的频率为8位10进制;2.测量的波形的电压最大值小于5V;3.能测量正弦波、三角波、方波或其他周期性波形的频率;3.用数码管显示测试的结果。

EDA技术与VHDL程序开发教程课程设计

EDA技术与VHDL程序开发教程课程设计1. 课程设计介绍本课程设计是针对电子电路设计与自动化专业的本科生开设的EDA技术与VHDL 程序开发教程。

本课程的目的是让学生学会使用EDA工具设计数字电路,以及用VHDL语言编写数字电路程序。

本课程设计的教学模式为理论教学与实践相结合,学生将在课程学习中完成与数字电路设计相关的实验任务,学习并掌握EDA工具的使用和VHDL语言的应用。

2. 课程设计内容2.1 EDA技术的应用EDA技术是电路设计的重要工具,它包含了原理图输入、仿真、综合、布局、布线等多个方面,可以大大缩短电路设计的时间和成本。

本课程将通过EDA工具的实验任务让学生了解和掌握以下内容:•学习使用EDA工具进行电路设计的基本流程•使用EDA工具进行原理图输入和仿真•了解EDA工具中的基本元件库和模型库•学习使用EDA工具进行电路综合、布局和布线2.2 VHDL程序的开发VHDL是一种数字逻辑设计语言,具有结构化编程和行为描述的特点。

本课程将通过VHDL程序设计的实验任务让学生了解和掌握以下内容:•VHDL程序设计基本语法和结构•VHDL程序的仿真和调试•VHDL程序升级、维护与管理•VHDL程序在FPGA器件上的应用3. 实验任务设计本课程的实验任务是在EDA工具和VHDL语言的指导下,完成数字电路的设计和程序编写。

具体的实验任务包括以下内容:3.1 实验任务一:基本数字逻辑电路设计与仿真根据给定的数字电路需求,学生应使用EDA工具进行数字电路的设计和仿真,并输出仿真结果报告。

3.2 实验任务二:进阶数字电路设计与布局根据给定的数字电路需求和器件参数,学生应使用EDA工具进行数字电路的设计和布局,并输出设计报告。

3.3 实验任务三:VHDL程序编写与仿真根据给定的数字电路需求,学生应使用VHDL语言编写对应的数字电路程序,并进行仿真和调试,输出仿真结果报告和程序调试报告。

3.4 实验任务四:VHDL程序升级与维护学生需要从已有的VHDL程序中进行修改和升级,以适应新的数字电路需求,并保持指定的电路性能。

EDA技术与VHDL基础课程设计

EDA技术与VHDL基础课程设计IntroductionEDA (Electronic Design Automation) technology is widely used in the design and verification of complex digital systems. VHDL (VHSIC Hardware Description Language) is a popular hardware description language usedfor digital circuit design. This article will provide an introduction to EDA technology and VHDL, and discuss a basic course design for students in digital circuit design.BackgroundAs technology advances, the demand for complex digital systems is increasing. The design and verification process of these systems requires a significant amount of time and effort. EDA technology plays a critical role in simplifying the design and verification process by providing automated tools and methodologies. EDA technology is used in integrated circuit design, system-on-chip design, and electronic system-level design.VHDL is a widely used hardware description language that allows designers to specify the behavior of digital circuits. VHDL is used to design digital systems of various complexities, including ASICs (Application Specific Integrated Circuits) and FPGAs (Field Programmable Gate Arrays). VHDL consists of a number of predefined constructs and libraries that provide designers with the ability to describe digital circuits at various levels of abstraction.EDA TechnologyEDA technology is used in various phases of the design cycle, including design entry, simulation, synthesis, and verification. These phases are discussed in more detl below:Design EntryDesign entry refers to the process of creating the initial design using a design entry tool such as a schematic capture tool or a hardware description language editor. The design entry tool allows designers to enter the design of the digital system using either graphical or textual representations.SimulationSimulation refers to the process of verifying the functionality of the digital system using a simulation tool. The simulation tool generates waveforms that represent the behavior of the digital system under different conditions. Simulation is used to verify the correctness of the design and identify potential issues that may arise during the implementation phase.SynthesisSynthesis refers to the process of transforming the high-level design description into a low-level implementation that can be programmed onto an FPGA or ASIC. Synthesis tools take the high-level abstraction of the design and convert it to a functionally equivalent low-level representation. The resulting design can then be programmed onto the target device.VerificationVerification refers to the process of confirming that the implemented design behaves correctly and meets the design specifications. Various verification techniques are used to ensure that the design meets the required functionality and performance criteria, including simulation, formal verification, and hardware emulation.VHDL BasicsVHDL is used to describe the behavior of digital systems atdifferent levels of abstraction. The following constructs are commonly used in VHDL:EntityThe entity defines the interface of the digital system. It specifies the input and output ports of the system, as well as any behavior associated with the ports.ArchitectureThe architecture describes the behavior of the digital system. It defines the functionality of the system and the relationship between the inputs and outputs.ProcessThe process describes the behavior of the digital system during one clock cycle. It defines the behavior of the system based on the valuesof the inputs and internal signals.SignalSignals are used to transfer data between components of the digital system. They are used to represent the inputs, outputs, and internal state of the system.Concurrent AssignmentConcurrent assignment is used to define the behavior of the digital system through Boolean expressions. It allows designers to define the behavior of the system using a combination of Boolean operators such as AND, OR, and NOT.Course DesignThe basic course design for EDA technology and VHDL can focus on the following topics:Introduction to Digital DesignThis topic provides an introduction to digital design and its fundamentals. It includes topics such as number systems, Boolean algebra, logic gates, and combinational and sequential circuits.Introduction to VHDLThis topic provides an introduction to VHDL and its syntax,including the use of entities, architectures, processes, signals, and concurrent assignments.Behavioral Modeling in VHDLThis topic covers the behavioral modeling of digital circuits using VHDL. It includes the modeling of various types of circuits, such as combinational and sequential circuits.Structural Modeling in VHDLThis topic covers the structural modeling of digital circuits using VHDL. It includes the modeling of components such as adders, multipliers, and registers.Synthesis and ImplementationThis topic covers the synthesis and implementation of digitalcircuits using EDA tools. It includes the use of synthesis tools to convert high-level abstract designs into low-level implementations, and the use of implementation tools to program the designs onto FPGAs or ASICs.VerificationThis topic covers the verification of digital circuits using simulation, formal verification, and hardware emulation. It includes the use of simulation tools to verify the functionality of the designs, the use of formal verification tools to prove the correctness of the designs, and the use of hardware emulation tools to verify the designs on actual hardware.ConclusionEDA technology and VHDL are essential tools for digital circuit design. The basic course design for EDA technology and VHDL should covertopics such as digital design fundamentals, VHDL syntax and constructs, behavioral and structural modeling, synthesis and implementation, and verification. With a solid understanding of these topics, students will be equipped with the necessary skills to design and verify complex digital systems.。

EDA技术与VHDL第五版教学设计

EDA技术与VHDL第五版教学设计前言EDA技术(Electronic Design Automation)是现代电子工程中不可或缺的技术手段。

EDA技术主要是指借助EDA(Electronic Design Automation)软件工具来进行电子系统及芯片的设计、生产和测试等各个环节中所需的CAD技术。

而VHDL(VHSIC Hardware Description Language)则是用来描述数字系统的硬件特性的一种表示语言。

本文将针对EDA技术和VHDL第五版的教学内容进行简要讨论。

EDA技术EDA技术的应用范围非常广泛,包括模拟电路和数码电路的设计、布局、验证和测试等各个环节。

EDA技术的使用可以大大简化电路设计的过程,提高电路设计的效率和准确性。

目前市面上主流的EDA软件有Altium Designer、Protel、PADS、Eagle、OrCAD等。

EDA技术在电子工程教育中的意义非常重要,对于培养学生的电路设计能力和实践能力有着重要作用。

在课堂教学中,可以通过以下几个方面来进行EDA技术的教学:1.EDA软件的基本操作首先,需要对常用的EDA软件进行介绍。

学生需要了解如何打开、创建和保存项目,如何进行电路设计和模拟,如何进行元器件库的管理等。

其中最重要的是掌握软件的快捷键和常用操作。

2.电路设计流程其次,需要讲解电路设计的流程,包括电路分析、元器件选型、电路设计、仿真和测试等各个环节。

通过实践操作,使学生掌握电路设计的基本流程和步骤。

3.实验实践最后,对于EDA技术的实验实践也是非常重要的一环。

学生可以通过设计一些小的实验电路,并进行仿真和测试,来巩固自己的掌握程度。

比如设计一个简单的加法器,然后通过仿真来验证电路的正确性。

VHDL第五版VHDL是一种常用的数字电路设计语言,它可以用来描述数字电路中各种电路的行为与结构。

VHDL第五版是目前最新版的VHDL标准。

学习VHDL第五版对于培养学生的数字电路实践能力具有非常重要的作用。

EDA课程设计——基于VHDL语言的数字时钟设计(可编辑)

EDA课程设计——基于VHDL 语言的数字时钟设计(可编辑)(文档可以直接使用,也可根据实际需要修改使用,可编辑推荐下载)一、设计要求 0二、设计原理及框图 01、设计原理 02、结构框图 0三、设计过程 (1)1、模块化设计 (1)2、顶层文件生成 (2)四、仿真调试过程 (3)1、各模块时序仿真图 (3)2、仿真过程中遇到的问题 (4)五、设计体会及收获 (4)一、设计要求1、稳定的显示时、分、秒。

2、当电路发生走时误差时,要求电路有校时功能。

3、电路有整点报时功能。

报时声响为四低一高,最后一响高音正好为整点。

二、设计原理及框图1、设计原理系统框图由六个模块组成,分别为:秒、分、时计数模块,整点报时模块,LED动态显示扫描模块,调时控制模块组成。

其工作原理是:基准脉冲输入信号同时加到秒、分、时、分隔符的脉冲输入端,采用并行计数的方式,秒的进位接到分的使能端上,秒的使能借到分隔符的使能上,分得接到时的使能端上,完成秒、分、时和分隔符的循环计数。

整点报时是根据分的A、B输出同时为0时,整点报时模块输出高电平控制报时。

LED显示扫描模块根据输入的扫描信号CKDSP轮流选通秒、分、时、分隔符的8位八段数码管,LED显示译码器完成计数器输出的BCD的译码。

2、结构框图三、设计过程1、模块化设计(1)秒计时模块秒计时模块由一个60位计数器为主体构成,其输入输出端口组成为:Clk:计时时钟信号Reset:异步清零信号Setmin:分钟设置信号Enmin:使能输出信号Daout[6:0]:BCD码输出(2)分计时模块分计时模块由一个60位计数器为主体构成,其输入输出端口组成为:Clk、clk1:计时时钟信号Reset:异步清零信号Sethour:小时设置信号Enmin:使能输出信号Daout[6:0]:BCD码输出(3)时计时模块时计时模块由24位计数器为主体构成,其输入输出端口组成为:Clk:计时时钟信号Reset:异步清零信号Daout[6:0]:BCD码输出(4)显示模块系统时间输出由六个七段数码管显示。

EDA大作业

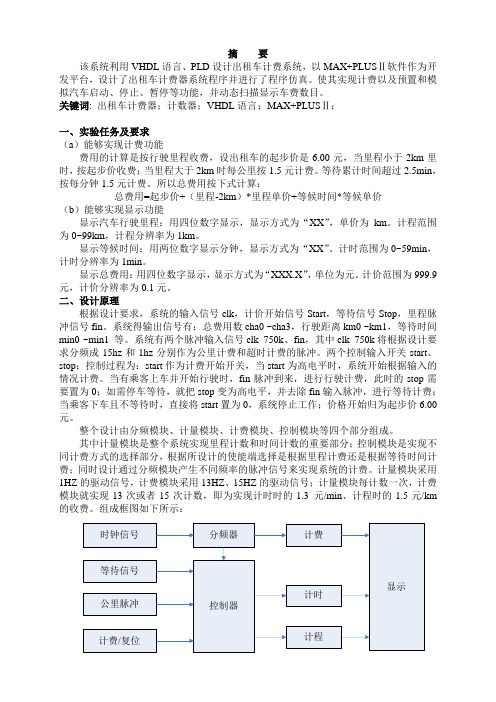

摘要该系统利用VHDL语言、PLD设计出租车计费系统,以MAX+PLUSⅡ软件作为开发平台,设计了出租车计费器系统程序并进行了程序仿真。

使其实现计费以及预置和模拟汽车启动、停止、暂停等功能,并动态扫描显示车费数目。

关键词: 出租车计费器;计数器;VHDL语言;MAX+PLUSⅡ;一、实验任务及要求(a)能够实现计费功能费用的计算是按行驶里程收费,设出租车的起步价是6.00元,当里程小于2km里时,按起步价收费;当里程大于2km时每公里按1.5元计费。

等待累计时间超过2.5min,按每分钟1.5元计费。

所以总费用按下式计算:总费用=起步价+(里程-2km)*里程单价+等候时间*等候单价(b)能够实现显示功能显示汽车行驶里程:用四位数字显示,显示方式为“XX”,单价为km。

计程范围为0~99km,计程分辨率为1km。

显示等候时间:用两位数字显示分钟,显示方式为“XX”。

计时范围为0~59min,计时分辨率为1min。

显示总费用:用四位数字显示,显示方式为“XXX.X”,单位为元。

计价范围为999.9元,计价分辨率为0.1元。

二、设计原理根据设计要求,系统的输入信号clk,计价开始信号Start,等待信号Stop,里程脉冲信号fin。

系统得输出信号有:总费用数cha0 ~cha3,行驶距离km0 ~km1,等待时间min0 ~min1 等。

系统有两个脉冲输入信号clk_750k、fin,其中clk_750k将根据设计要求分频成15hz和1hz分别作为公里计费和超时计费的脉冲。

两个控制输入开关start、stop;控制过程为:start作为计费开始开关,当start为高电平时,系统开始根据输入的情况计费。

当有乘客上车并开始行驶时,fin脉冲到来,进行行驶计费,此时的stop需要置为0;如需停车等待,就把stop变为高电平,并去除fin输入脉冲,进行等待计费;当乘客下车且不等待时,直接将start置为0,系统停止工作;价格开始归为起步价6.00元。

eda

课程设计EDA 技术与VHDL 语言课程设计报告班级:姓名:学号:指导教师:成绩:电子与信息工程学院1 前言在科技高度发展的今天,集成电路和计算机应用得到了高速发展。

尤其是计算机应用的发展。

它在人们日常生活已逐渐崭露头角。

大多数电子产品多是由计算机电路组成,如:手机、mp3 等。

而且将来的不久他们的身影将会更频繁的出现在我们身边。

各种家用电器多会实现微电脑技术。

电脑各部分在工作时多是一时间为基准的。

这次课程设计就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字秒表。

秒表在很多领域充当一个重要的角色。

在各种比赛中对秒表的精确度要求很高,尤其是一些科学实验。

他们对时间精确度达到了几纳秒级别。

1.1 课程设计的目的本次设计的目的就是在掌握EDA 实验开发系统的初步使用基础上,了解EDA 技术,对计算机系统中时钟控制系统进一步了解,通过对数字秒表的设计,进行理论与实际的结合,提高与计算机有关设计能力,提高分析、解决计算机技术实际问题的能力。

通过课程设计深入理解计算机结构与控制实现的技术,达到课程设计的目标。

1.2 课程设计的内容设计一块数字秒表,能够精确反映计时时间,并完成复位、计时功能。

秒表计时的最大范围为1小时,精度为0.01秒,并可显示计时时间的分、秒、0.1秒等度量。

1.3 课程设计的要求给出系统总体组成框图,设计思路,完成以上模块的VHDL实现及功能仿真,顶层文件及整体仿真。

2 设计过程 2.1 设计规划本系统设计采用自顶向下的设计方案,系统的整体组装设计原理图如图2-1 所示,它主要由控制模块、时基分频模块,计时模块和显示模块四部分组成。

各模块分别完成计时过程的控制功能、计时功能与显示功能。

1 数字秒表计时控制电路计时电路显示电路控制状态机时基分频电路计数器扫描电路七段译码器一百进制计数器六十进制计数器图2-1 系统组成框图 2.2 各模块的原理及其程序CB10 OUTPUTCLK CLK CO COCLR CLR OUTPUT CLK ENSP SP EN CTRL CLK CLR BCD7 EN OUTPUT BCD3..0 LED6..0 S_1MS3..0 S_1MS3..0 EN LED6..0 S_10MS3..0 OUTBCD3..0 S_10MS3..0 S_100MS3..0 CLK S_100MS3..0 OUTPUT S_1S3..0 SEG7..0 CLR S_1S3..0 S_10S3..0 EN S_10S3..0 SEG7..0 M_1MIN3..0 M_1MIN3..0 M_10MIN3..0 M_10MIN3..0 OUTPUT HOUR3..0 HOUR3..0 OUTBCD3..0 COUNT MULX 图2-2 系统的整体组装设计原理图本系统设计由控制模块、时基分频模块,计时模块和显示模块四部分组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA技术与VHDL语言课程大作业

设计题目:电子分频器

姓名:李露

班级:自动化10(2)

学号: 208

目录

1. 设计背景

2. 设计方案

计数器模块

任意偶数分频模块

任意奇数分频模块

设计思路

3. 数字分频器模块的VHDL源程序

任意偶数分频的VHDL源程序()

任意奇数分频的VHDL源程序()

4. 源程序总体描述

5. 波形仿真图

6. 总结

7. 参考文献

1.设计背景

EDA技术作为计算机硬件设计中的关键设计技术之一,是每一位将来希望从事涉及电子系统与集成电路设计研究领域工作的人所必须掌

握的一门技术。

时序逻辑电路作为其主要设计与研究的电路类型之一,在EDA中占据着重要的位置,而时钟信号在时序逻辑电路有占据着重要的位置,它决定了时序逻辑单元中的状态何时更新。

时钟信号作为一种有固定周期并与运行状态无关的信号量,在边沿触发机制中,只有上升沿或下降沿才是有效信号,才能控制逻辑单元状态量的改变。

为满足不同的时序电路要求,对时钟信号进行分频也显得格外重要

基于EDA技术的数控分频器设计,采用的是用软件的方法设计硬件的EDA (电子设计自动化)技术。

作为EDA技术重要组成部分的VHDL硬件描述语言是一种符合IEEE工业标准的建模语言。

用它设计的数控分频器可作为一个模块,移植到很多数字电路系统中,且极易修改,只要修改程序中的某几条语句,就可使最大分频系数得到改变。

整个设计过程简单、快捷。

可从根本上减少硬件调试的时间,为总体设计完成争取宝贵的时间。

2. 设计方案

计数器模块

通过计数器来记录clk的信号个数,分别有以上升沿计数和以下降沿计数。

偶数计数器可采用以上升沿计数,即每当clk从0变为1时记一个数,下降沿计数是当clk从1变为0时记一个数

任意偶数分频模块

定义一个计数器对输入时钟进行计数,在计数的前一半时间里,输出高电平,在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,6分频,计数值为0~2输出高电平,计数值为3~5输出低电平。

任意奇数分频模块

定义两个计数器,分别对输入时钟的上升沿和下降沿进行计数,然后把这两个计数值输入一个组合逻辑,用其控制输出时钟的电平。

这是因为计数值为奇数,占空比为50%,前半个和后半个周期所包含的不是整数个clk的周期。

例如,5分频,前半个周期包含个clk 周期,后半个周期包含个clk周期。

设计思路

原理图

不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有计时器溢出位与预置数加载输入信号相接即可。

3. 数字秒表计时模块的VHDL源程序

任意偶数分频的VHDL源程序()

library ieee;

use dvf is

port(clk_in:in std_logic;

fout:out std_logic);

end;

architecture one of dvf is

signal cnt: integer range 0 to 2000;

signal clk_out:std_logic;

begin

process(clk_in)

begin

if clk_in'event and clk_in = '1' then if cnt=2000 then

cnt <=0;

clk_out <=not clk_out;

else

cnt<=cnt+1;

end if;

end if;

end process;

fout<=clk_out;

end one;

任意奇数分频的VHDL源程序()

library IEEE;

use

use use

entity division5 is

port (clk : in std_logic;

out1: out std_logic);

end division5;

architecture Behavioral of division5 is signal out2, out3 : std_logic := '0';

signal temp1,temp2 : integer range 0 to 10; begin

process(clk) --输出占空比为50%的奇数5分频时钟 begin

if clk'event and clk = '1' then

temp1<=temp1+1;

if temp1=2 then

out2<='1';

elsif temp1=4 then

out2<='0';

temp1<=0;

end if;

end if;

end process;

process(clk) --同样输出占空比为50%的奇5分频时钟

begin

if clk'event and clk = '0' then

temp2<=temp2+1;

if temp2=2 then

out3<='1';

elsif temp2=4 then

out3<='0';

temp2<=0;

end if;

end if;

end process;

p3:process(out2,out3)

begin

out1<=out2 or out3;

end process p3;

--或运算,得到占空比为50%的奇数5分频时钟 end process;

end Behavioral;

4. 源程序总体描述

对任意频率的偶数‘N’倍分频,通过定义一个模为N的计数器,输出至1,每当计数到N/2时对其进行反向。

对clk进行奇数倍分频时定义两个计数器,分别对输入时钟的上升沿和下降沿进行计数( n-1)/2,然后把这两个计数值输入一个与或逻辑,用其控制输出时钟的电平。

5. 波形仿真图

6. 总结

经过了这次课程设计,使我对VHDL语言有的更深刻的理解。

通过数字分频器课程设计,使我加深了对VHDL语言设计程序的了解。

学会了层次设计概念,将程序分为若干模块,分别完成各个模块,最后再将各个模块连接起来。

通过这次课程设计,对VHDL的语言有了更深刻的认识,对课题设计的基本流程有了一定的认识,同时也是一次把原来所学的书本知识和实践相联系的过程。

并通过实践,建立起了学习EDA的浓厚兴趣,基本掌握了这个软件的基本使用方法,并顺利的对程序进行编辑及仿真。

为实现预期功能,能够对系统进行快速的调试,并能够对出现的功能故障进行分析,及时修改相关软硬件。

对软件编程、排错调试。

了解了关于EDA技术及VHDL语言的基本编程形式及原理图的绘制,为今后的学习打好基础。

在此之后,我会继续学习关于VHDL语言的运用。

我还意识到了我对这门课掌握还有一定的不足,还有许多的知识我不了解;有的是一知半解;有的即使原理懂了,但在应用方面却是丝毫不知。

所以在今后的学习中,我会更加努力,不仅要学好理论知识,还要把它应用到实践中去,使两者很好的结合起来,互补互助。

7. 参考文献

【1】江国强·EDA技术与应用·电子工业出版社·2007年3月第二版

【2】张亦华、延名·数字电路EDA入门·北京邮电大学出版社

【3】《基于EDA技术的计算机组成原理实验》方恺晴湖南大学出版社

【4】《数字设计原理与实践》(原书第四版)

思科系统公司斯坦福大学著

林生金京林葛红王腾译

林生审校

机械工业出版社出版

【5】《逻辑与数字系统设计学习指导及题解》李晶皎李景宏王爱侠清华大学出版社

网址:

(1)《注:晶振的百度词条》

(2)《注:小数分频原理》。