数字逻辑实验指导书

数字逻辑实验指导书(multisim)(精)

实验一集成电路的逻辑功能测试一、实验目的1、掌握Multisim软件的使用方法。

2、掌握集成逻辑门的逻辑功能。

3、掌握集成与非门的测试方法。

二、实验原理TTL集成电路的输入端和输出端均为三极管结构,所以称作三极管、三极管逻辑电路(Transistor -Transistor Logic 简称TTL电路。

54 系列的TTL电路和74 系列的TTL电路具有完全相同的电路结构和电气性能参数。

所不同的是54 系列比74 系列的工作温度范围更宽,电源允许的范围也更大。

74 系列的工作环境温度规定为0—700C,电源电压工作范围为5V±5%V,而54 系列工作环境温度规定为-55—±1250C,电源电压工作范围为5V±10%V。

54H 与74H,54S 与74S 以及54LS 与74LS 系列的区别也仅在于工作环境温度与电源电压工作范围不同,就像54 系列和74 系列的区别那样。

在不同系列的TTL 器件中,只要器件型号的后几位数码一样,则它们的逻辑功能、外形尺寸、引脚排列就完全相同。

TTL 集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对我们进行实验论证,选用TTL 电路比较合适。

因此,本实训教材大多采用74LS(或74系列TTL 集成电路,它的电源电压工作范围为5V±5%V,逻辑高电平为“1”时≥2.4V,低电平为“0”时≤0.4V。

它们的逻辑表达式分别为:图1.1 分别是本次实验所用基本逻辑门电路的逻辑符号图。

图1.1 TTL 基本逻辑门电路与门的逻辑功能为“有0 则0,全1 则1”;或门的逻辑功能为“有1则1,全0 则0”;非门的逻辑功能为输出与输入相反;与非门的逻辑功能为“有0 则1,全1 则0”;或非门的逻辑功能为“有1 则0,全0 则1”;异或门的逻辑功能为“不同则1,相同则0”。

三、实验设备1、硬件:计算机2、软件:Multisim四、实验内容及实验步骤1、基本集成门逻辑电路测试 (1测试与门逻辑功能74LS08是四个2输入端与门集成电路(见附录1,请按下图搭建电路,再检测与门的逻辑功能,结果填入下表中。

《数字逻辑》实验指导书

《数字逻辑》实验指导书四、实验提示1.74LS73引脚11是GND,引脚4是VCC。

2.D触发器74LS74是上升沿触发,JK触发器74LS73是下降沿触发;3.在测试D触发器和J-K触发器时,注意CLK在按下之前和按下之后对输出Q/Q的影响。

五、实验报告要求1.根据实验内容1~4的结果作出各触发器的功能表;2.根据实验内容5的实验结果画出电路的数字波形图,并分析电路的工作原理。

5实验五计数器一、实验目的1.掌握异步计数器和同步计数器的工作原理;2.掌握集成同步十进制计数器74LSl62的功能和使用方法。

二、实验器件和设备1.双J-K触发器74LS73 2.同步4位BCD计数器74LS162 3.四2输人正与门74LS08 4.TDS-2数字电路实验系统三、实验内容1.图5-1为J-K触发器构成的3位异步二进制计数器。

输出Q2、Q1、Q0分别接LED指示灯,使用单脉冲做为计数时钟,测试计数器的功能,观测计数状态,并记录。

2片 1片 1片 1台图5-1 3位异步二进制计数器2.图5-2为J-K触发器构成的3位同步二进制计数器。

输出Q2、Q1、Q0分别接LED指示灯,使用单脉冲做为计数时钟,测试计数器的功能,观测计数状态,并记录。

图5-2 3位同步二进制计数器3.图5-3为集成4位同步十进制计数器74LSl62的应用图例,RCO、QD、QC、QB、QA分别LED指示灯,使用单脉冲做为计数时钟,测试计数器的功能,观测计数状态,并记录。

四、实验报告要求1.作出实验内容1和2的功能表,并画出在连续计数脉冲下Q2、Q1、Q0的波形图;2.根据实验3的结果画出在连续计数脉冲下RCO、Q2、Q1、Q0的波形图。

图5-3 4位同步十进制计数器6实验六集成计数器的应用一、实验目的1.掌握计数器74LSl62的功能和级连方法; 2.掌握任意模计数器的构成方法。

二、实验说明1.计数器器件是应用较广的器件之一。

它有很多型号,各自完成不同的功能,供不同的需要选用。

[工学]数字逻辑实验指导书

![[工学]数字逻辑实验指导书](https://img.taocdn.com/s3/m/b319c6f85022aaea998f0fc8.png)

《数字逻辑实验指导书》实验一组合逻辑电路分析与设计一、实验目的:1、掌握PLD实验箱的结构和使用;2、学习QuartusⅡ软件的基本操作;3、掌握数字电路逻辑功能测试方法;4、掌握实验的基本过程和实验报告的编写。

二、原理说明:组合电路的特点是任何时刻的输出信号仅取决于该时刻的输入信号,而与信号作用前电路的状态无关。

(一)组合电路的分析步骤:(二)组合逻辑电路的设计步骤首先根据给定的实际问题进行逻辑抽象,确定输入、输出变量,并进行状态赋值,再根据给定的因果关系,列出逻辑真值表。

然后用公式法或卡诺图法化简逻辑函数式,以得到最简表达式。

最后根据给定的器件画出逻辑图。

三、实验内容(一)组合逻辑电路分析:1.写出函数式,画出真值表;2.在QuartusⅡ环境下用原理图输入方式画出原理图,并完成波形仿真;3.将电路设计下载到实验箱并进行功能验证,说明其逻辑功能。

(必做)(二)1. 设计一个路灯的控制电路,要求在四个不同的路口都能独立地控制路灯的亮灭。

(用异或门实现)画出真值表,写出函数式,画出实验逻辑电路图。

在Quartus Ⅱ环境下实现设计,完成对波形的仿真,并将设计下载到实验箱并进行功能验证。

(必做)要求:用四个按键开关作为四个输入变量;用一个LED 彩灯(发光二极管)来显示输出的状态,“灯亮”表示输出为“高电平”,“灯灭”表示输出为“低电平”。

2. 设计一个保密锁电路,保密锁上有三个键钮A 、B 、C 。

要求当三个键钮同时按下时,或A 、B 两个同时按下时,或按下A 、B 中的任一键钮时,锁就能被打开;而当不符合上列组合状态时,将使电铃发出报警响声。

试设计此电路,列出真值表,写出函数式,画出最简的实验电路。

(用最少的与非门实现)。

在Quartus Ⅱ环境下实现设计,完成对波形的仿真,并将设计下载到实验箱并进行功能验证。

(选做)(注:取A 、B 、C 三个键钮状态为输入变量,开锁信号和报警信号为输出变量,分别用F 1用F 2表示。

《数字逻辑》实验指导书

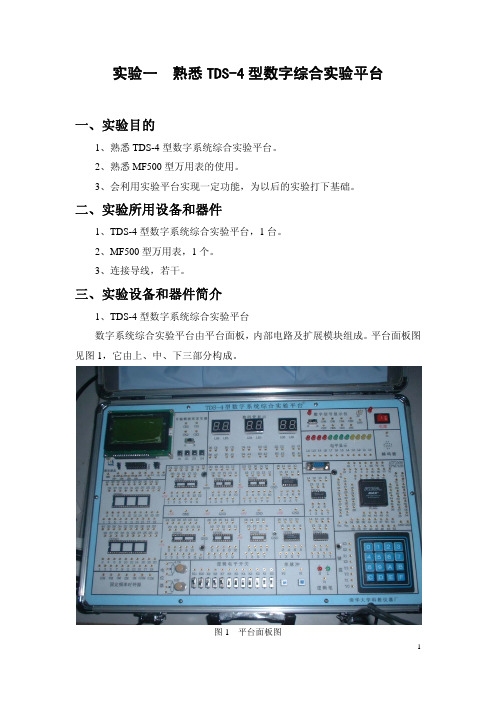

《数字逻辑》实验指导书计算机科学系硬件教研室二○一三年九月实验一基本逻辑门和逻辑电路一、实验目的1.掌握TTL与非门、或非门和异或门的输入与输出之间的逻辑关系;2.掌握组合逻辑电路的基本分析方法;3.熟悉TTL小规模数字集成电路的外型、引脚和使用方法;4.初步掌握“TDS-4数字系统综合实验平台”和常规实验仪器的使用方法。

二、实验器件和设备1.四2输入与非门74LS00 1片2.四2输入或非门74LS28 1片3.四2输入异或门74LS86 1片4.三态输出的四总线缓冲器74LS125 1片5.TDS-4数字系统综合实验平台1台6.万用表1个三、实验内容1.按图1.1测试与非门、或非门和异或门的输入和输出的逻辑关系;图1.1 基本逻辑门2.测试并分析下图1.2逻辑电路的功能。

图1.2 组合逻辑电路四、实验提示1.将被测器件插入实验台上的14芯插座中,器件的引脚7与实验台的“地(GND)”连接,引脚14与实验台的+5V连接;2.用实验台的电平开关输出作为被测器件的输入,拨动开关,则改变器件的输入电平;3.将被测器件的输出引脚与实验台上的电平指示灯连接,指示灯亮表示输出电平为1,指示灯灭表示输出电平为0;4.用万用表的电压档测量被测器件的输入引脚和输出引脚的电压值。

五、实验报告要求1.分别用真值表和电压值表的形式表示实验内容1的结果;2.用真值表的形式表示实验内容2的结果,写出电路的逻辑函数并分析其功能。

实验二译码器、编码器和数据选择器一、实验目的1.掌握译码器、编码器、数据选择器的逻辑功能和使用方法;2.掌握TTL中规模集成电路的应用方法。

二、实验器件和设备1.3-8线译码器74LSl38 1片2.8-3线优先编码器74LS148 1片3.双4选1数据选择器74LSl53 1片4.TDS-2数字电路实验系统1台5.万用表或逻辑笔1个三、实验内容1.测试3-8线译码器74LSl38的逻辑功能。

使能输入端G1、G2A、G2B和编码输入端C0、C1、C2分别接电平开关,译码输出端Y0~Y7分别接LED指示灯。

数字逻辑试验指导书

数字逻辑实验要求随着大规模集成电路的迅速发展,数字电路技术已非常广泛地应用到各行各业之中。

数字系统的设计方法也发生了根本的变化由原来的标准集成电路,如从开始的TTL集成电路,到后来的GAL 编程芯片,再到现在迅速普及使用的ASIC专用集成电路和VHDL硬件描述语言的出现及系统级仿真和综合技术,成为电子设计自动化(EDA)技术向更高层次发展的重要因素,采用EDA技术可以极大的提高设计效率和设计精度。

其特点主要包括两个方面:1,采用可编程逻辑器件后对系统硬件的改造。

在各种大规模的高速数据采集和处理系统中,可编程逻辑部件可以高速、准确的完成一些控制算法,并且简化了系统结构。

2,改进了系统设计方案。

EDA环境下的系统设计一般都采用自上而下的设计方法,它采用概念输入模式,突破破了具体工艺的束缚。

对于模拟电路和数字电路的设计,EDA提供了丰富的参数优化工具及模型库和建模工具,其硬件描述语言(HDL)不依赖于特定的工艺和固定的设计方法。

并且能够提供统一的防真环境,使模拟电路、数字电路和硬件描述语言动态的连接起来,同步协调地运行。

系统的软硬、件还可以同时设计,从而有效解决设计中的瓶颈问题,缩短了设计时间。

同时,EDA技术可以对系统产生测试向量,进行故障仿真,从而可以大大降低实际系统的故障率。

因此,在我们的数字逻辑实验设计内容中,将按照上述几种典型的常用芯片进行设计,如TTL电路用EDA进行设计方法,GAL芯片使用方法,又必须了解掌握和使用新的数字系统的设计方法,如FPGA芯片的使用方法及用VHDL等硬件描述语言进行编程等。

目的就是让我校计算机系的本科学生了解掌握和使用先进的电路设计方法。

《数字逻辑电路设计》是计算机专业硬件设计必修基础课,是一门理论与实践紧密结合的课程,其目的在于切实加强学生数字电路技术的分析和应用。

与《数字逻辑电路设计》相配套的数字逻辑实验是一门实验性较强的课程,是教学中的一个非常重要环节,通过实验不仅可以使学生在消化、巩固、加深理解开拓课堂教学内容,培养学生严谨认真求实的科学态度,培养学生实际动手的实践技能,提高学生分析和解决问题的能力,还可以帮助学生了解多种常用芯片的特性,及使用方法,掌握计算机局部逻辑的设计和调试和验证过程。

数字逻辑设计实验室指导书说明书

LAB BROCHUREDigital Logic Design Lab DEPARTMENT OF ELECTRICAL ENGINEERINGCONTENTS...................................................................................................................... Lab Venue 3............................................................................................. Lab Objectives & Courses 3 Lab Description & Experiments 4....................................................................................................................................................................................... Hardware Experiments 5 ....................................................................................................... Verilog Experiments 6 Lab Resources 7...............................................................................................................DLD Lab Venue: Computer Interfacing Lab First Floor, Electrical DepartmentLab VenueThe Digital Logic Design Lab (DLD Lab) is one of the most important and well equipped lab of the Department of Electrical Engineering at University of Engineering and Technology, Lahore. This lab is conducted at the Computer Interfacing Lab situated at the first floor of the Electrical Engineering Department.Scope of the LabThe DLD Lab is for undergraduate coursework related to the course EE131. It is one of the core modules of B. Sc. Electrical Engineering therefore the lab has a significant importance in the department.Related CoursesThis lab is designed such that thestudents get a hands on familiaritywith the concepts they come acrossin the course EE131 that is the DigitalSystems course. This is anundergraduate course which dealswith the basics of digital systemsdesign and is a core module of theB. Sc. Electrical Engineeringcoursework as it provides theprerequisites for advance courses indigital electronics. Because of thesignificance of this course the DLDLab has been carefully designed tomeet the course requirement.Brief Overview of the LabThe Lab is well equipped withboth hardware and software facilitiesrequired by the students to performthe necessary experiments designedfor this lab. Details of the labequipment has been discussed in aproceeding section.Experiments are designed insuch a way that the students becomewell aware of the concepts they learnin the theory sessions. A list ofexperiments that are conducted inthis lab has also been mentioned in aproceeding section.Experiments are related to bothdigital hardware and VerilogProgramming.Objectives & CoursesLab Description & ExperimentsLab DescriptionThe Experiments in the Lab have been divided into two major portions:•Hardware Labs•Hardware Description Language (Verilog) LabsHardware Labs have been designed to familiarize students with the Combinational Digital Logic Design and Sequential Digital Logic Design through the implementation of Digital Logic Circuits using ICs of basic logic gates and some simple digital logic circuits.HDL (Verilog) Labs havebeen designed tofamiliarize students with theHDL based Digital DesignFlow. These labs introducestudents with differentlevels of coding available inVerilog i.e. Gate level,Dataflow level andBehavioral level. Xilinx ISE7.1 tools have been used inthese labs. Finally, theskills learnt in the HDLlabs are employed toimplement some digitallogic circuits on Spartan-3FPGA, using Xilinx StarterKit Development Board.Expected OutcomesWith the help of the twothreads of the labmentioned above, studentswill have clearunderstanding of all thethree paradigms ofimplementation of digitallogic circuits:•Implementation usingICs for basic logic gatesand simple circuits•Implementationthrough the Developmentof Dedicated IC(ASIC)•Implementationthrough ReconfigurableLogic (i.e. FPGA)This makes studentsadept in basic conceptsinvolved in digital logicdesign. The lab contributesa lot to the basic learning ofdigital systems.This shows theindispensability of theDLD Lab.List of ExperimentsList of experiments isgiven on page 5 and 6. Asmentioned before the labhas two major portionstherefore there are two listsof experiments one relatedto the hardware labs andthe other related to thehardware descriptionlanguage (verilog) labs. Allthese experiments aremandatory and each lab isfollowed by speciallydesigned assignments.A Lab DemonstrationA Digital Chip (inside view)TITLE TOPICS1To Verify the Behavior of Logic Gates using Truth Table and Familiarization with Digital Integrated Circuits Basic Logic Gates, Truth Table, Integrated Circuits2Implementation of Boolean Function using Logic Gates and Introduction to Hierarchical Design of Digital Logic Circuits Boolean Functions,Boolean Algebra,Hierarchical Design of Digital Logic Circuits3Familiarization with the Different Portions of the Datasheet fora Digital IC and Using the Datasheet to Gather RelevantInformation to Utilize the IC as a Component in another DigitalLogic Circuit Datasheet of a Digital Logic IC, Hierarchical Design of Digital Logic Circuits4Implementation of 8 bit Binary Comparator using 4 bit Binary Comparators Binary Comparator,Hierarchical Design of Digital Logic Circuits5Implementation of 4bit into 3bit Binary Multiplier using 4bit Binary Adders Binary Multiplication,Hierarchical Design of Digital Logic Circuits6Implementation of BCD Adder using 4bit Binary Adders, 4 to 7 Segment Decoder and 2Digit 7 Segment Display BCD addition,Hierarchical Design of Digital Logic Circuits7Implementing a Full Adder using(a) Decoder(b) Multiplexer Implementation of Boolean function using Decoder,Implementation of Boolean function using Multiplexer8Flip Flops Different Types of Flip Flops9To study the fundamentals of basic counters and to construct various types of counters CountersHardware ExperimentsTITLE TOPICS1Introduction to HDL based Digital Design Methodology HDL based Digital Design Flow usingVerilog,Introduction to Outsourcing Business Model2Introduction to Basic Syntax of Verilog and Gate level Modelingthrough implementation of half adder at gate level and itssimulation using Xilinx ISE tools Basic Concepts of Verilog, Modules and Ports, Gatelevel coding in Verilog,3Introduction to the concepts of Instantiation and HierarchicalDesign in Verilog through the implementation of full adderusing the previously designed half adder modulesHierarchical Design in Verilog4Introduction to the Concept of Vectors and Introduction to Dataflow modeling through implementation of half adder andfull adder at dataflow level Vectors in Verilog,Dataflow level coding in Verilog5Consolidation of the concepts of Dataflow level modeling and Introduction to the concept of Synthesis by the CAD tool Dataflow level coding in Verilog, Logic Synthesis6Introduction to Behavioral modeling through implementation ofhalf adder and full adder at behavioral level.Behavioral level coding in Verilog7Introduction to if else statement and case statement inBehavioral modeling through implementation of Multiplexerif else and case statements in Verilog8Introduction to the Concepts of Sequential Circuit anda TestBench module (Stimulus Block)Sequential circuits in Verilog, Concept of Testbench module in Verilog9Behavioral Level Coding of Basic Sequential Circuits andConsolidation of the concepts of TestBench module (StimulusBlock)Sequential circuits in Verilog10Introduction to Field Programmable Gate Array(FPGA) and Steps involved in its Programming Need for Reconfigurable Logic, Xilinx ISE Tools for Programming the Xilinx FPGAsVerilog ExperimentsLab ResourcesHardware ResourcesThe lab is fully equipped with all the hardware required to conduct the above mentioned experiments. The hardware resources of the lab are:•Pentium-IV PCs (with MS WinXp OS)•Hardware trainers for logic circuit design and analysis•Electronic Chips of all digital gates•Spartan-III FPGA board kits•Power SuppliesThese resources allowthe students to have ahands on experience ofbasic digital logic designconcepts. This activitygreatly leverages what thestudents learn in the theorysessions.Software ResourcesThe lab also consists ofthe software resourcesrequired by the studentsnamely:•Veriwell•ModelSim•Xilinx IDE•MatlabSoftware resources areequally important ashardware resources are.These software resourcesare sufficient for thestudents to performexperiments. Thesesoftwares provide thestudents with thenecessary platform to workon HDL that is the Verilog.These softwares are alsorequired to work with thesophisticated hardwareslike Spartan-III FPGAboards.The lab has all theresources whether relatedto hardware or software sothat the students becomeadept in the basic field ofdigital electronics.Students areencouraged to use the labresources to performactivities andexperiments which helpthem strengthen theirconcepts.Lab StaffLike other labs of thedepartment there is atrained and able staffconsisting of skilled labtechnicians that take careof the lab equipment.They also guidestudents about handlingthe lab equipment and theprecautionary measuresrequired for the studentswhile working in the lab.A Digital Circuit BoardA SimulationDIGITAL LOGIC DESIGN LAB1st Floor, Department of Electrical Engineering UNIVERSITY OF ENGINEERING & TECHNOLOGY, LAHORE-54890, PAKISTAN..pkurl:Ph: + 92 42 9029229, Fax: + 92 42 9250224Computer Interfacing Lab。

数字逻辑实验指导书

照附录熟识各管脚的功能。

(一)测试门电路逻辑功能

测量以上四种门的逻辑功能,输入接高低电平开关,输出接高低电平指示灯。列出

真值表,并填入测试结果,写出逻辑表达式。

(二)实现其它逻辑门的功能

1、按图 1-1 和图 1-2 组成逻辑电路。测试输出与输入的逻辑关系并列出真值

表。填写实验结果。写出表达式。

1

数字逻辑实验指导书

可见这些触发器的动作时间各异。计数器由 RD 输入负脉冲置零后,计数脉冲从 CP 端

输入,第一个计数脉冲输入后,计数器状态均为 Q4Q3Q2Q1 = 0001,随着计数脉冲的继 续输入,计数器的状态根据二进制码顺序依次递增,第十五个脉冲输入后,计数器状态

为 1111。第十六个脉冲输入后,计数器恢复起始状态 0000,并在 RD 端送出一个进位脉

(1)QA、QB、QC、QD 四个输出端分别接发光管二极管显示,CP 端接连续脉冲或单脉 冲。

(2)在 CP 端接连续脉冲,观察 CP、QA、QB、QC、QD 的波形。 (3)画出 CP、QA、QB、QC、QD 的波形。

图 3-3 异步二 — 十进制加法计数器

六、实验报告 1、画出实验内容要求的波形及记录表格。 2、总结时序电路特点。

9

数字逻辑实验指导书

实验四 电子秒表的电路实现

一、实验目的

1、学习数字电路中基本 RS 触发器、单稳态触发器、时钟发生器及计数、译码显示 等单元电路的综合应用。

2、学习电子秒表的调试方法。

二、实验设备及器件

1、+5V 直流电源 3、数字万用表 5、单次脉冲源 7、逻辑电平开关 9、译码显示器

2、双踪示波器 4、数字频率计 6、连续脉冲源 8、逻辑电平显示器 10、74LS00×2 555×1 74LS90×3

《数字逻辑》实验指导书

目录实验1: 基本逻辑门电路 (2)EDA设计实验的基本步骤和注意事项 (4)实验2: 译码器及其应用 (10)实验3 触发器、移位寄存器的设计和应用 (15)实验4: 计数器 (18)实验5: 数字系统的设计 (19)实验报告格式和内容 (20)实验1: 基本逻辑门电路一、实验目的1: 掌握各种门电路的逻辑功能及测试方法。

2: 学习用与非门组成其它逻辑门电路。

二、实验用的仪器、仪表TEC —5实验箱 74LS00二输入四与非门 三态门74LS125三、实验原理与非门的逻辑功能是: 当输入端中有一个或一个以上低电平时, 输出端为高电平。

只有当输入端全为高电平时, 输出端才为低电平(即有“0”得“1”, 全“1”出“0”)。

三态输出门是一种特殊的门电路。

它与普通的逻辑门电路不同, 它的输出状态除了高、低电平两种状态(均为低阻状态)外, 还有第三种状态,即高阻态。

处于高阻态时, 电路与负载之间相当于开路。

三态门主要用途之一是实现总线传输。

三态输出门符号与功能表如下(此例以低有效的使能器件为例)。

四、实验内容 1: 测试二输入与非门的逻辑功能与非门的输入端接逻辑开关电平, 输出端接发光二极管。

按表1-2所示测试与非门, 并将测试结果填入表中。

B A F •= 表1-1AB2: 学习用二输入与非门构成其他逻辑电路的方法, 并测试。

与门逻辑功能实现:根据布尔代数的理论, ,所以用2个与非门即可实现与门逻辑功能。

输入A 、B 接逻辑开关, 输出端接发光二极管。

参考表1-1, 设计表格, 并将测试结果填入表中。

或门逻辑功能实现:根据布尔代数的理论, ,所以用3个与非门即可实现或门逻辑功能。

输入A 、B 接逻辑开关, 输出端接发光二极管。

参考表1-1, 设计表格, 并将测试结果填入表中。

异或门逻辑功能实现:根据布尔代数的理论, ,根跟据此异或逻辑表达式经过变换, 逻辑图如下, 请自行验证此逻辑图的正确性, 同时思考如果直接据逻辑表达式画逻辑图, 效果如何, 近而体会变换的作用。

数字逻辑专题实验指导书

目录第1章数字逻辑电路实验基础知识 (1)1.1 实验的基本过程 (1)1.1.1 实验预习 (1)1.1.2 实验数据记录 (1)1.2.3 实验报告 (2)1.2 实验操作规范和常见故障检查方法 (3)1.2.1 实验基本操作规程 (3)1.2.2 电路连接操作 (4)1.2.3 故障检查方法 (5)1.3 常用数字集成芯片的参数与主要性能 (6)1.3.1 集成电路的型号命名法 (6)1.3.2 数字集成电路的分类 (6)1.3.3 数字集成电路特点及使用须知 (9)1.4 数字逻辑电路的测试方法 (11)1.4.1组合逻辑电路的测试 (11)1.4.2时序逻辑电路的测试 (11)第2章数字逻辑实验基本技能 (12)2.1 实验基本目标要求 (12)2.2 实验技能基本要求 (12)2.3 实验内容基本要求 (14)第3章数字逻辑电路基本实验 (16)实验一:EDA软件QuartusII的使用 (16)实验二:实验仪器的使用及元器件测试 (16)实验三:组合电路险象观察与排除 (17)实验四:简单逻辑电路功能分析与变换 (18)实验五:运算器电路分析与设计 (18)实验六:状态监测电路设计 (19)实验七:符合判别电路设计 (20)实验八:多数表决器设计 (22)实验九:译码器测试实验 (22)实验十:数据选择器测试实验 (24)实验十一:逻辑函数发生器设计 (25)实验十二:二进制码∕BCD码变换器设计 (26)实验十三:格雷码变换器设计 (27)实验十四:BCD码加法器设计 (27)实验十五:触发器功能测试 (28)实验十六:四相时钟分配器设计 (29)实验十七:四位二进制计数器功能测试 (31)实验十八:异步十进制计数器设计 (32)实验十九:集成计数器测试实验 (33)实验二十:集成计数器应用设计 (34)实验二十一:数码显示电路实验 (35)第4章数字逻辑综合设计实验 (37)设计项目一:数字时钟设计 (37)设计项目二:出租车计价器设计 (40)设计项目三:交通灯控制器设计 (50)设计项目四:电子密码锁设计 (55)设计项目五:智力竞赛抢答器设计 (59)其他参考选择题目 (64)。

数字逻辑实验指导书

《数字电路》实验指导书×××编写适用专业:电类专业运算机专业巢湖学院物理与电子科学技术系2020年1月巢湖学院实验教学中心制前言本书是数字逻辑及数字电子技术的实验教材,在必然理论基础指导下,注重实验方式和实验技术能力的培育。

更注重学生主观能动性的发挥,尽可能不用固定的实验方式去限制学生的思维,因此本书的指导思想是用有限的内容、开放性的实验方式取得尽可能多的收成。

本书包括逻辑电平和门电路,组合逻辑电路,触发器,时序逻辑电路,脉冲单元电路,存储器,A/D和D/A转换电路的实验等内容。

每一个实验大体都代表数字电路的一个知识点或几个部份内容的综合应用,并以小结的形式给出了较充分的专题实验,各专题实验的内容和现行数字电路课堂教学的内容大体对应,可是完全采纳了实验的研究方式;在实验进程中,教师能够依如实验时刻确信必做和选做项,学生能够在完成必做项的基础上,尽可能地多做一些内容,让能力强的学生取得更多的锻炼,关于实验方式不做过量的限制,给学生更多的思维空间,调动学生自主试探的踊跃性,每一个实验都有预习要求和相应的试探问题要回答,这些内容都是学生实验报告上必需回答的,是通过实验以后,反映学生理论和实践的一个提高。

咱们依照数字电路本身的课程体系来安排实验教学的内容,希望学生通过实验教学,既能提高自己的观看能力、思维能力、工程实践能力和设计创新能力,同时又能够对整个数字电路课程体系有深切透彻的明白得。

学生实验报告大体内容要求每门课程的所有实验项目的报告必需以课程为单位装订成册,原那么上利用此刻各系执行“实验报告”。

实验报告应事前预备好,用来做预习报告、实验记录和实验报告,要求这三个进程在一个实验报告中完成。

1.实验预习在实验前每位同窗都需要对本次实验进行认真的预习,并写好预习报告,在预习报告中要写出实验目的、要求,需要用到的仪器设备、物品资料和简要的实验步骤,形成一个操作提纲。

对实验中的平安注意事项及可能显现的现象等做到心中有数,但这些不要求写在预习报告中。

《数字逻辑》实验指导书(BB2013)概述

福建农林大学计算机与信息学院《数字逻辑》实验指导书2012年3月编电子技术实验室实验守则一、实验课前:每个学生必须认真预习实验指导书和与本实验有关的教材内容,写出实验预习报告。

明确实验目的和实验原理,了解实验内容与步骤,掌握仪器、仪表的使用方法,作好实验准备工作。

二、上实验课:学生必须认真听讲,接好线路后,需经指导教师复查批准,才准接通电源。

三、实验时,每个学生都应严肃认真,勤于动手、独立思考、细心操作,注意观察、如实作好记录。

教师根据每个学生的实验技能,动手能力评定平时成绩。

四、实验过程中,如发现仪器设备有冒烟、焦味、异响、漏电等异常现象,应立即切断电源,保持现场,请指导教师检查处理。

五、实验完成后,需请指导教师检查预习报告和实验数据以及所使用的仪器设备,经教师检查签字后方可离开实验室。

六、学生因请假而需要补做实验者,应本人申请,经指导教师同意,并安排好时间补做。

七、每个学生必须爱护实验室的仪器设备,使用前,若发现故障及时请指导教师检查。

与本实验无关的仪器设备不准动用,凡不听教师讲解,进行错误操作以致损坏设备者,按赔偿条例酌情处理。

八、实验室是教学场所,应保持整洁,安静,不得喧哗打闹,不准吸烟,不准随地吐痰,不准乱抛纸屑,不准在实验室内吃东西,不准在仪器设备上或桌面上涂写,穿拖鞋者一律不准进入实验室。

九、对违反上述规则又不听劝阻者,教师有权令其退出实验室实验一 TTL与非门参数及功能测试一、实验目的1. 了解TTL 与非门电路的主要参数。

2. 掌握TTL 与非门电路的主要参数和传输特性的测试方法。

3. 熟悉TTL 门电路的逻辑功能的测试方法。

二、实验仪器与器件1. 数字电路实验箱1个2. 万用表1只3. 示波器1台4. 元器件TTL与非门74LS00 2片电阻、电容若干三、实验原理TTL 门电路是最简单、最基本的数字集成电路元件,利用其通过适当的组合连接便可以构成任何复杂的组合电路。

因此,掌握TTL 门电路的工作原理,熟练、灵活地使用它们是数字技术工作者必备的基本功之一。

数字逻辑实验指导_李静锴

图5 数码管区

可编辑数字波形发生器区

该区包括图形液晶,调光电位器,连接插座,四个控制按钮,四路输出插孔 CK0, CK1, CK2, CK3 和内置的单片机及控制电路组成, 提供给用户多种选择。

图6 可编辑数字波形区

小喇叭电路

向“In”插孔输入不同频率的数字信号,通过驱动三极管的基极控制喇叭按 希望的频率鸣叫,可做报警或电子琴输出用。

输入 B 0 0 1 1 C 0 1 0 1

输出 Y 0 0 1 1

(三)74LS02 逻辑功能测试 1、测试电路如图 7 所示。

接K12开关 接L12指示灯 接K11开关 万用 表

地

图 7 或非门接线图

2、按表 4 的要求,分别拨动或非门输入引脚的电平开关,用万用表测量输 出端的电压值,观察电平指示灯是亮还是灭,把结果填入表中。

11

(一)74LS00 逻辑功能测试 1、测试电路连接如图 6 所示。

接 K12开 关 接 L12指 示 灯 接 K11开 关 万用 表

地

图6 与非门接线图

2、按表 1 的要求,分别拨动与非门输入引脚的电平开关,用万用表测量输 出端的电压值,观察电平指示灯是亮还是灭,把结果填入表 1 中。

表 1 74LS00 逻辑功能表

8

测试时应谨慎从事。 Ⅶ. 仪表应经常保持清洁和干燥,以免影响准确和损坏仪表。

四、实验内容

1、 通过连线实现用开关控制 LED 指示灯, 说明实现过程, 并在设备上实现。 2、在 6 个数码管上显示 1 2 3 4 5 6,说明实现过程,并在设备上实现。 3、用万用表测量数字系统综合实验平台+5V 和 GND 之间的直流电压。

实验一

熟悉 TDS-4 型数字综合实验平台

数字逻辑 实验指导书

数字逻辑实验讲义实验一 基本逻辑门电路测试一.实验目的:1. 掌握TTL 与非门主要外部特性参数的测试方法。

2. 掌握TTL 与非门逻辑功能测试方法。

2. 熟悉数字电路实验箱、数字万用表的使用。

二.实验仪器及器件:1.数字电路实验箱 1台2.数字万用表 1块3.器件: 74LS00 四2输入与非门 1片 电阻:200Ω 1个三.实验预习:复习TTL 与非门的逻辑功能、主要参数及其测量方法和电压传输特性。

四.实验原理:TTL 与非门电路是目前较为普遍的一种集成门电路。

本实验采用四2输入与非门74LS00,即在一块集成块内含有四个互相独立的与非门,每个与非门有2个输入端。

其电路图、逻辑符号及引脚排列如图1(a)、(b)、(c)所示。

图1出0。

与非门的逻辑函数式:Y=AB 对于使用集成电路者来说,所关心的是集成门电路从导通到截止所需要的转Y A B (b)+ V (+5V) (c) 74LS00换条件其所表现出来的转换特性,诸如开门电平、输出高电平、输出低电平等这样一些静态参数,以及诸如平均传输延迟时间一类动态参数的测量,下图所示为与非门电路的转换特性(电压传输特性)曲线,它表示输入由低电平变到高电平时输出电平的相应变化,所有这些都是选择和设计电路所必须了解的。

五.实验内容:1.测试TTL 与非门的静态参数:(1)输入短路电流I IS 和输入漏电流I IH : I IS (或I IL ):指被测输入端接地,其余输入端和输出端悬空时,由被测输入端流出的电流。

也称低电平输入电流。

在由多级门构成的电路中,I IS 相当干前级门输出低电平时,后级向前级门灌入的电流。

因此,I IS 关系到前级门的灌电流负载能力,I IS 越小,前级门带负载的个数就越多。

测试电路如图2(a )所示。

I IH :指被测输入端接高电平,其余输入端接地,输出端悬空时,流入被测输入端的电流。

也称高电平输入电流。

在由多级门构成的电路中,它相当于前级门输出高电平时,前级门的拉电流负载。

答案数字逻辑实验指导书(multisim)答案

答案数字逻辑实验指导书(Multisim)答案本文档旨在为数字逻辑实验中使用Multisim软件的学生提供详细的步骤和答案解析。

以下是针对常见实验的答案。

实验一:简单门电路实验1. 题目描述设计一个两输入门电路,使用Multisim软件验证其功能。

2. 答案在Multisim软件中,选择“逻辑门”部分。

在工作区中拖动两个输入开关和一个输出指示灯到工作区。

在两个输入开关的属性设置中,将“初始状态”设置为1(ON)。

连接两个开关和输出指示灯,使电路完成。

3. 实验过程1.打开Multisim软件。

2.在组件库中找到“逻辑门”部分,并从中选择两个输入开关和一个输出指示灯。

3.拖动这些组件到工作区。

4.右键单击其中一个输入开关,选择属性编辑。

5.在属性编辑对话框中,将“初始状态”设置为1(ON),然后点击“确定”。

6.重复上一步,将另一个输入开关的属性也设置为1(ON)。

7.连接两个输入开关和输出指示灯,以完成电路。

8.在工具栏上点击“运行”按钮,观察输出指示灯的状态。

4. 实验结果在两个输入开关的状态均为1(ON)时,输出指示灯也将亮起。

实验二:组合逻辑电路实验1. 题目描述设计一个组合逻辑电路,使用Multisim软件验证其功能。

2. 答案在Multisim软件中,选择“逻辑门”部分。

在工作区中拖动两个输入开关和一个输出指示灯到工作区。

在两个输入开关的属性设置中,将“初始状态”设置为1(ON)。

连接两个开关和输出指示灯,使电路完成。

3. 实验过程1.打开Multisim软件。

2.在组件库中找到“逻辑门”部分,并从中选择两个输入开关和一个输出指示灯。

3.拖动这些组件到工作区。

4.右键单击其中一个输入开关,选择属性编辑。

5.在属性编辑对话框中,将“初始状态”设置为1(ON),然后点击“确定”。

6.重复上一步,将另一个输入开关的属性也设置为1(ON)。

7.连接两个输入开关和输出指示灯,以完成电路。

8.在工具栏上点击“运行”按钮,观察输出指示灯的状态。

《数字逻辑》实验指导书级软件

实验要求及考核方式1、实验预习预备知识+熟悉实验内容2、必备工具实验指导书+笔+预习实验报告+理论教材3、操作要求实验前认真学习注意事项+实验后仪器及工作台整理4、实验完毕上交完整实验报告5、考核方式(考试卷面成绩50%+平时成绩50%(包括操作成绩+实验报告)实验一熟悉数字逻辑实验箱及万用表的使用一、实验目的1、熟悉数字逻辑实验箱各大模块的组成掌握其使用方法。

2、熟悉数字万用表的使用方法。

二、实验设备及器件1、数字逻辑实验箱1台2、数字万用表1台三、实验预备知识1、数字万用表常用功能及使用方法?2、基本门电路的运算逻辑?3、集成芯片的常用封装形式有哪些?4、常用的电子显示器件有哪些?四、实验内容与步骤1、学会用数字万用表测电压、电阻等的使用方法;①测出实验箱电源电压;②测出连接导线电阻;2、电源及开关模块(1)熟悉电源及地的引出点?(2)熟悉用开关输出高低逻辑电平?3、基本逻辑门模块及逻辑功能测试测试二输入与门、或门、与非的逻辑功能。

按表1-1要求用开关改变输入端A,B的状态,借助指示灯和万用表,把测试结果填入表1-1中。

表1-14、熟悉DIP封装的集成模块的引脚分布及与插座安装方法(1)DIP封装?英文全称?(2)学会如何分辨集成芯片的引脚排列?(3)集成芯片如何安插到芯片座?5、熟悉显示模块及功能测试(1)如何用发光二极管显示一组(如4位)逻辑状态?(2)数码管的显示原理及使用?6、了解实验箱其他功能模块及用途(1)实验箱其他功能模块有?(2)使用注意事项?五、实验要求1、掌握数字万用表常用使用方法。

2、分析基本门电路的逻辑功能,将实验结果填入各相应表中。

3、回答思考题实验箱上的发光二极管是共阳极还是共阴极?如何分辨?4、独立完成实验,交出完整的报告。

实验二TTL门电路功能测试一、实验目的1、熟悉TTL各种门电路的逻辑功能及测试方法。

2、熟悉数字万用表的常用功能及使用方法。

3、掌握门电路相互转换方法。

数字逻辑(实验指导书)

数字逻辑实验指导书2012-3目录实验一TTL集成逻辑门的参数测试(基本)...............................2学时实验二组合逻辑电路的设计(设计)..... .....................................2学时实验三BCD七段显示译码器(应用).. ............... ............... .......2学时实验四触发器的功能测试(基本)...............................................2学时实验五数据选择器的功能分析与设计(综合)...........................2学时实验六移位寄存器及其应用(应用)............. ....... .....................2学时实验七555定时器的应用(综合)...............................................2学时实验一 TTL集成逻辑门的参数测试实验学时:2实验类型:基本实验要求:必做一、实验目的1、了解TTL与非门各参数的意义。

2、掌握TTL集成门电路的逻辑功能和参数测试方法。

3、熟悉TPE-D3数字电路实验箱的基本功能和使用方法。

二、实验原理、方法和手段TTL集成与非门是数字电路中广泛使用的一种逻辑门,使用时,必须对它的逻辑功能、主要参数和特性曲线进行测试,以确定其性能好坏。

本实验主要是对TTL集成与非门74LS20进行测试,该芯片外形为DIP双列直插式结构。

原理电路、逻辑符号和管脚排列如图1-1(a)、(b)、(c)所示。

图1-1 74LS20芯片原理电路、逻辑符号和封装引脚图1. 与非门的逻辑功能与非门的逻辑功能是:当输入端有一个或一个以上的低电平时,输出端为高电平;只有输入端全部为高电平时,输出端才是低电平。

(即有“0”得“1”,全“1”得“0”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑实验指导书计算机科学与技术学院应用教研室目录实验的基本步骤 (3)实验的注意事项 (3)实验报告书写要求 (3)实验用到的资源和原理 (4)实验1:基本逻辑门电路功能测试 (6)实验2:译码器及其应用 (14)实验3:触发器 (18)实验4:计数器 (23)实验5 加法器 (28)实验6 移位寄存器及其应用 (32)实验的基本步骤本实验指导书的所有实验基于EDA实验台进行。

采用软件为Quartus II 5.0,硬件芯片为ALTERA 的Cyclone 系列FPGA芯片EP1C6Q240C8。

使用本EDA实验台进行数字逻辑实验,不需要进行手工接线。

实验工作分2步进行:1:在PC机上,基于Quartus II软件进行原理图(逻辑图)的设计,设计完成后,需要经过引脚锁定、编译下载到EDA实验台上的FPGA芯片EP1C6Q240C8中。

下载完成后,即在FPGA芯片中形成物理的逻辑电路。

此步工作相当于传统实验的基于物理器件的接线操作。

2:基于第一步形成的逻辑电路(在FPGA中),进行测试验证。

此过程可以用万用表、逻辑笔、示波器等测试FPGA的相应引脚,实现对逻辑电平、波形的测试,从而验证实验的正确性。

实验的注意事项1:Quartus II的工程名和顶层实体名字必须为英文,存储路径最好不要含中文和空格。

2:Quartus II的设计中所有的命名中,名字不要有空格。

3:Quartus II的设计中放置“input”“ouput”引脚符号时,引脚符号的虚线框和原件的虚线框要刚好对上,以保证连接上,虚线框分开和部分重叠都不能正确连接。

4:所用到的脉冲/时钟信号必须锁定到29脚,具体原理参考“实验用到的资源和原理”部分。

实验报告书写要求书写实验报告,语言要简练,书写端正、作图正规。

实验报告一般应包括以下内容;1:实验名称、目的;所用仪器、仪表;实验原理图。

2:实验项目(指导书的详细内容不必抄入);测试记录表;波形图及现象记录。

3:实验数据的整理4:实验分析,包括于理论只的比较、现象分析实验用到的资源和原理需要的资源:1:逻辑开关2:发光二极管指示灯3:单脉冲/1M-8M方波时钟数字逻辑实验需要用到的输入为逻辑0、1,由逻辑开关提供,实验台提供了16个逻辑开关,为SD0、SD1……SD15,和FPGA的连接关系如下表1-1。

输出的逻辑0、1接到发光二极管,实验台提供了很多发光二极管,具体只列了部分于表1-1中。

从表中可以看出,SD0连接于200脚,SD1连接于200脚,41脚到83脚分别接有一个发光二极管指示灯。

具体原理如下图0所示(只列处了两个逻辑开关和两个发光二极管,其余同理)。

通过拨动逻辑开关实现逻辑0、1的输入,输出的逻辑0、1通过发光二极管指示,1亮0灭。

时序电路的实验要用到脉冲和1M-8M方波,由29脚的提供,原理如图0所示。

当短路子DZ3短接时,DZ4断开时,29脚和单脉冲(按一下出一个高电平的单脉冲)连接,当DZ4短接时,DZ3断开时,29脚接方波,此时频率由DZ5、DZ65、DZ75、DZ85的短接情况决定。

DZ5短接时为8M, DZ6短接时为4M,DZ7短接时为2M,DZ8短接时为1M。

图0实验1:基本逻辑门电路功能测试一、实验目的1:测试与非门及与非门组成的其它逻辑门电路的功能。

2:熟悉EDA 实验系统的使用方法和操作流程。

二、实验用的仪器、仪表EDA 实验台 万用表 PC 机三、实验原理与非门的逻辑功能是:当输入端中有一个或一个以上低电平时,输出端为高电平。

只有当输入端全为高电平时,输出端才为低电平(即有“0”得“1”,全“1”出“0”)。

三态输出门是一种特殊的门电路。

它与普通的逻辑门电路不同,它的输出状态除了高、低电平两种状态(均为低阻状态)外,还用第三种状态,即高阻态。

处于高阻态时,电路与负载之间相当于开路。

三态门主要用途之一是实现总线传输。

三态输出门符号与功能表如下(此例以高有效的使能器件为例)。

四、实验内容1:测试二输入与非门的逻辑功能与非门的输入端接逻辑开关电平,输出端接发光二极管。

按表1-2所示测试与非门,并将测试结果填入表中。

A BB A F ∙=2:学习用二输入与非门构成其他逻辑电路的方法,并测试。

● 与门逻辑功能实现:根据布尔代数的理论,B A B A F ∙=∙=,所以用2个与非门即可实现与门逻辑功能。

输入A 、B 接逻辑开关,输出端接发光二极管。

参考表1-2,设计表格,并将测试结果填入表中。

AB● 或门逻辑功能实现:根据布尔代数的理论,B A B A F +=∙=,所以用3个与非门即可实现或门逻辑功能。

输入A 、B 接逻辑开关,输出端接发光二极管。

参考表1-1,设计表格,并将测试结果填入表中。

AB● 异或门逻辑功能实现:根据布尔代数的理论,B A B A F +=,根跟据此异或逻辑表达式经过变换,逻辑图如下,请自行验证此逻辑图的正确性,同时思考如果直接据逻辑表达式画逻辑图,效果如何,近而体会变换的作用。

输入A 、B 接逻辑开关,输出端接发光二极管。

参考表1-1,设计表格,并将测试结果填入表中。

3:测试三态门的逻辑功能 三态门输入端、使能端分别接逻辑开关,输出端接发光二极管。

将测试结果填入表1-3中。

表1-3五、实验步骤(1)PC 机端的工作1:启动QUARTUS II 5.02: 创建新的Quartus II 工程(在创建新工程前,需要创建一个工作目录) 打开File —New Project Wizard 菜单,创建工程。

首先出现图1,参考如下图示进行。

指定工作目录和工程名。

接着点击“Next ”按钮,一直到图2二所示,选择参考图示,指定芯片为EP1C6Q240C8。

接着,点击“Finish ”图1图23: 建立顶层模块设计文件(.bdf ),选择File ->New,选择Block Diagram/Schematic File,按OK。

注意:此文件必须与上一步骤的顶层文件名称相同,Save时自动出现顶层文件名称,保持不变。

在BDF文件设计窗口内的空白处双击, 出现Symbol对话框,如下图3所示,展开“logic”,选nand2即二输入与非门,如图4所示,点击“OK”即可实现二输入与非门的放置。

按实验内容要求画出所用的逻辑图(画逻辑图过程中,利用”COPY”即可实现更多nand2门的放置)。

其中连线用鼠标左键即可实现。

三态门在“buffer”中,名字为”tri”。

选中即可实现三态门的放置(注意:原件的放置可以直接输入原件名,如图3、4所示)。

最终如图5所示。

在此直接输入原件名字即可实现原件选择图3在此直接输入原件名字即可实现原件选择图4图5在图5中完成了所有需要测试的逻辑图的连接,还需要放置端口(即把此逻辑电路引到对应的FPGA 的引脚)。

放置过程同上,选“pin ”中的“input ”和“output ”即为对应的输入、输出端口,在所用的逻辑图中输入端放输入端口,输出端放输出端口。

结果如图6所示。

端口放完后需要改名字,以便后边的实验过程的易于识别。

名字都调整好后,保存。

图64:进行编译选择菜单”Processing-Start Compilation”,实现编译。

在编译完成后,进行引脚锁定。

5:引脚锁定引脚锁定的目的是把逻辑图中的逻辑输入、输出引到对应的FPGA的物理实际引脚上。

选择菜单“Assignments-Pins”,出现如图7所示窗口。

“To”列为对应的端口,“Location”列为锁定的实际位置,用鼠标单击选定对应的位置,如图7所示,直接输入相应的物理引脚号,如7,就会出现“PIN_200”,回车,即可实现对一个引脚的锁定。

在锁定完所有引脚后,保存然后重新编译即可。

编译完成后,在当前工作窗口点击鼠标邮件,在弹出的菜单中选择“Show---Show Pin and Location Assignments”显示图8,可以看到对应的引脚锁定关系。

因本实验所有输入端均接逻辑开关,输出端均接LED指示灯。

如下图,把与门的两个输入andInput1、andInput2分别锁定到200和201脚,而200和201和逻辑开关相连。

与门的输出andOut锁定到41脚,而41和LED发光二极管连接,从而形成图9原理图连接关系,从而只需要拨动SD0,SD1即可实现输入端的0、1输入,输出端对应的41脚的指示灯会“1”亮“0”灭。

其余的同理。

这里的锁定关系仅为参考,可以把输入锁定到16个开关中的任意一个,输出同样选择16个LED中的任一个均可。

图7图8图96:编译下载再次编译本系统,完成后选“Tools-Programmer”,出现图10窗口,在“Hardware Setup…”后如果为“No Hardware”,需要点击“Hardware Setup…”进行编程线缆的设置,选“ByteBlaster[LPT1]”即可。

当线缆配置好后,”Start”按钮有效,在”Program/Confgure”处选中,按”Start”按钮即实现配置下载。

下载完成后,即可进行测试。

图10(2)实验箱端的工作本部分工作主要完成对逻辑电路功能的测试,采用对输入逻辑开关的切换,实现不同的“0”“1”输入,从而输出端输出不同的逻辑电平,使指示灯亮或灭。

完成实验内容中各个表的填入,完成实验工作。

如用二输入与非门实现的与门的两个输入andInput1、andInput2分别锁定到200和201脚,而200和201和逻辑开关SD0,SD1相连。

与门的输出andOut锁定到41脚,而41和LED发光二极管连接,从而形成图9原理图连接关系,从而只需要拨动SD0,SD1即可实现输入端的0、1的四种组合输入,输出端对应的41脚的指示灯会“1”亮“0”灭,把结果填入对应的表中即可。

实验的电平测试采用万用表,把万用表打到直流电压20V档,黑表笔接试验台右上脚的地(GND),红表笔测输出端的LED指示灯的一个管脚。

注意:红表笔测量时不要同时碰到两个及以上管脚,以免短路。

六、实验报告记录、整理实验结果,并用布尔代数的理论进行分析实验2:译码器及其应用一、实验目的1:掌握译码器的逻辑功能及应用。

2:学习并掌握双踪示波器的使用。

二、实验用的仪器、仪表EDA实验台万用表示波器PC机三、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态。

译码器在数字系统中有广泛的用途,如代码变换、数据分配、存储器寻址、组合控制信号等。

本实验以74138为主要实验对象,图2-1为74138的逻辑图和管脚排列图。

其中A,B,C 为地址输入端,Y0N~Y8N为译码输出端,G1,G2AN,G2BN为使能端(这里的N均为低有效的意思)。