数电课件第4章(N1)

《数字电路与数字逻辑》第四章-1.ppt

CO

图 4.1.1 (b) 在进行信息传输时,为检测信息是否出错,常 在信息后附加一个校验部分:校验和 。

2021年3月11日星期四

第四章 组合逻辑电路

8

例如,传输的信息为“ China “,则校验和的求

法如下: 信息 C

ASCII 1000011

h

1101000

i

1101001

n

1101110

a

2021年3月11日星期四

第四章 组合逻辑电路

2

第二节 中规模集成组合逻辑电路

一、编码器

1. 二进制编码器 (1) 8—3线普通编码器 (2) 8—3线优先编码器74148 (3) 74148的级联 2. 二—十进制优先编码器74147

2021年3月11日星期四

第四章 组合逻辑电路

3

第四章 组合逻辑电路

2021年3月11日星期四

第四章 组合逻辑电路

5

(3)确定逻辑功能

例4.1.1 分析如图4.1.1(a)所示的逻辑电路的逻辑

1

2

功能。

&

A

&

&

S

B

D

&

1

C

图 4.1.1(a)

2021年3月11日星期四

第四章 组合逻辑电路

6

解 : (1)写出逻辑表达式

S = A AB B AB = A AB + B AB = AB + AB

=1 F

图 4.1.2

2021年3月11日星期四

第四章 组合逻辑电路

11

解: (1)写出逻辑表达式 F = D1⊕ D2 ⊕ D3 ⊕ D4 = D1⊕ D2 ⊕ D3 ⊕ D4 (2) 列真值表 (3) 确定逻辑功能 奇校验码产生电路

数电第4章触发器课件

与该当前的输入信号有关,而且与此前电路的状态有关。

结构特征:由组合逻辑电路和存储电路组成,电路中存在反馈。 锁存器和触发器是构成时序逻辑电路的基本逻辑单元 。

2

4.1 概述 一、触发器的概念及特点 1.概念:

FF: (Flip-Flop, 简称FF)能够存储1位二进制信号 的基本单元电路。

2.特点: (1)有两个稳定的状态:0状态和1状态。 (2)在触发信号控制下,根据不同输入信号可置成 0或1状态。 (触发信号为时钟脉冲信号)

第4章 触发器

4.1 概述

4.2 基本SR触发器(SR锁存器)

4.3 同步触发器(电平触发)

4.4 主从触发器(脉冲触发)

4.5 边沿触发器(边沿触发) 4.6 触发器的逻辑功能及描述方法 4.7 集成触发器 4.8 触发器应用举例

作业题

【5】【6】【8】【11】

1

时序逻辑电路与锁存器、触发器: 时序逻辑电路: 工作特征:时序逻辑电路的工作特点是任意时刻的输出状态不仅

1、电路结构 以基本SRFF为基础,增加两个与非门。

置1端 时钟信号 (高电平有效) (同步控制)

置 0端 (高电平有效)

图4-5 同步SRFF

13

2、工作原理

分析CLK=0时: 有 SD’ =RD’=1, 则Q、Q’不变。 分析CLK=1时: (1)S=R=0时,有SD’ =RD’=1:Q、Q’不变(保持原态) (2)S =0, R=1:输出Q=0, Q’=1 (置0状态) (3)S =1, R=0:Q=1, Q’=0 (置1状态) (4)S=R=1:Q=Q’=1(未定义状态)

t t

1

主

O

Q

从

O

图4-13 主从JKFF波形

数字电子技术基础第4章数字电子技术基础课件

S

Q & G2

R

SD,RD

Qn1SRQn

D DQn D

(CP = 1期间有效)

G3 & S

Байду номын сангаас

& G4 R

1

CP

D

简化电路:省掉反相器。把G3的输出送到R端。 G3的输出为S·CP=S·1=S=D=R

(4-29)

二、主要特点

1、时钟电平控制,无约束问题 在CP=1期间,若D=1,则Qn+1=1;若D=0,

EN

内含 4 个基本 RS 触发器

2. 由或非门组成:CC4043(略)

(4-21)

二、TTL 集成基本触发器

74279、74LS279

Q

&

&

S

R

Q

&

&

S1 S2

R

+VCC

RSSRSRSSRS––––––––––11233412341212

1 2 3 5 6 10 11 12 14 15

16

1R

4

CP-控制时序电路工作节奏的固定频率的脉冲信号 ,一般是矩形波。

具有时钟脉冲CP控制的触发器称为同步触发器,或 时钟触发器,触发器状态的改变与时钟脉冲同步。

同步触发器: 同步 RS 触发器 同步 D 触发器

(4-23)

4.2.1 同步RS触发器

一、电路组成及工作原理 1. 电路及逻辑符号

控制门 只有CP=1时, G3、G4导通

&

01

1

11

不变

S1

1R

③R=1、S=1时:根据与非门的逻辑功能不难推知,触发器保 持原有状态不变,即原来的状态被触发器存储起来,这体现了 触发器具有记忆能力。

数字电路PPT课件第四章

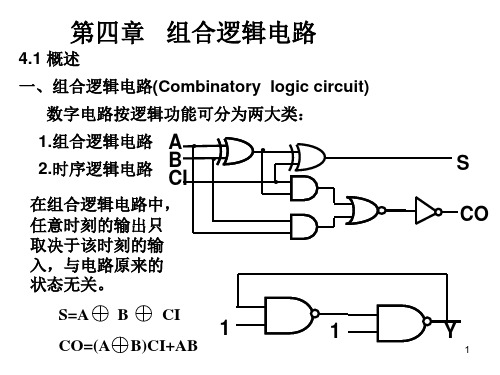

第四章 组合逻辑电路

目的与要求:

1.掌握组合逻辑电路的定义、特点。 2.掌握组合电路的分析方法和设计方法。 3.掌握常用中规模器件及其应用。

重点与难点:

组合电路的分析和设计方法。

第四章 组合逻辑电路

4.1组合逻辑电路分析 4.2常用组合逻辑电路的介绍 4.3单元级组合逻辑电路的分析方法 4.4组合逻辑电路的设计 4.5组合逻辑电路中的竞争与冒险

4.2.4译码器

译码是编码的逆过程,译码即是将输入的某个二进制编 码翻译成特定的信号。

具有译码功能的逻辑电路称为译码器。

译码是编码的逆过程,是将输入的二进制代码赋予的含 义翻译过来,给出相应的输出高、低电平信号。常用的 译码器电路有二进制译码器、二-十进制译码器和显示 译码器。

4.2常用组合逻辑电路的介绍

Si Ai BiCi1 Ai BiCi1 Ai BiCi1 Ai BiCiC1i - 1 A00i

∑ 0 0 0

011

00S i

Ai Bi Ci1

Ci Ai Bi BiCi1 AiCi1

B0i 1 & 0 1 0

C

0 i1- 1

110

0C I 0 C O1

I0 I1 I2 I3 I4 I5 I6 I7

ST

74148

YS

QA QB QC

YEX

逻辑符号图

41 52 63 74 EI 5 A2 6 A1 7 GND 8

16 VCC 15 EO 14 GS 13 3 12 2 11 1 10 0 9 A0

引脚图

4.2常用组合逻辑电路的介绍

3)74148的扩展应用 ST

A1 B1 × × ×

×

第4章(N1) 时序电路基础

D触发器的应用(1)

清0脉冲

移位寄存器

所有触发器CP端都连 在一起——同步时序 电路

由于Q1(D2)相对于 t3有tpd延迟,故到 达t3时, D2仍为1, 则D3=1 1 1 1 1

右移的移位 寄存器 1

四、D触发器的应用

1、D触发器组成1位二进制计数器 计数器:能累加所收到的时钟脉冲个数的逻辑电路 D=Qn

5、画出输出波形图;

6、总结逻辑功能。

§4-2-3 米里型电路的分析

例1:

1、写出激励方程和输出方程 J1 K 1 1

n J 2 K 2 x Q1 n n n z Qn Q x Q Q 2 1 2 1x

2、求出次态方程

n 1 n n Q1 J1 Q1 K1Q1 n Q1 1 n n Qn J Q K Q 2 2 2 2 2 n ( x Q1 ) Qn 2

§4-1-1 §4-1-2 §4-1-3 §4-1-4 §4-1-5 §4-1-6 §4-1-7

基本R-S触发器 时钟R-S触发器 D触发器 J-K触发器 T与Tˊ触发器 触发器小结 异步计数器

§4-1-1 基本R-S触发器

基本R-S触发器:最简单的触发器,是构成其他触发器的 基础。

输入端定义符 号

关联对象号m(此处是1) 的含义: 仅当控制输入(此处是CP)

有效时,具有对应关联号码

(此处1)的输入信号(此处

控制关联符

关联对象号

是R、S)才能对电路起作用。

逻辑符号

2. 时钟R-S触发器状态真值表

状态真值表

3. 时钟R-S触发器的状态图

状态图:表示触发器状态转换的图形。它是触发器从 一个状态变化到另一个状态或保持原状不变时,对输 入信号(R、S)提出的要求。

数字电子技术基础简明教程第4章触发器PPT课件

R S Qn 000 001 010 011 100 101 110 111

Qn+1 × × 0 0 1 1 0 1

说明 触发器状态不定

触发器置0 触发器置1 触发器保持原状态不变

(4-12)

基本RS触发器的特性表

R S Qn

000 001 010 011 100 101 110 111

Qn+1

0 1 1 1 0 0 不用 不用

第4章 触发器

(4-1)

第一部分

整体概述

THE FIRST PART OF THE OVERALL OVERVIEW, PLEASE SUMMARIZE THE CONTENT

第4章 触发器

概述 4.1 基本触发器 4.2 同步触发器 4.3 边沿触发器 4.4 触发器的电气特性

(4-3)

概述

&

01

1

11

不变

S1

1R

③R=1、S=1时:根据与非门的逻辑功能不难推知,触发器保 持原有状态不变,即原来的状态被触发器存储起来,这体现了 触发器具有记忆能力。

(4-9)

? Q 1

1Q

&

&

S0

0R

SR 10 01 11 00

Q 0 1 不变 不定

④R=0、S=0时:Q=Q=1,不符合触发器的逻辑关系。并且由 于与非门延迟时间不可能完全相等,在两输入端的0同时撤除 后,将不能确定触发器是处于1状态还是0状态。所以触发器不 允许出现这种情况,这就是基本RS触发器的约束条件。

Q RQ

逻辑 符号 有两个输 出端,一 个无小圆 圈,为Q 端,一个 有小圆圈, 为Q端。

(4-6)

二、工作原理

清华大学数电4组合课件

G1门是 非门, 强调低 电平有 效

YS ' ( I 0 ' I1 ' I 2 ' I 3 ' I 4 ' I 5 ' I 6 ' I 7 ' S )'

YEX ' (YS ' S )'

S’是“使能”信号 低电平有效 代表无输入信号 11

代表“有输入信号”

Y2' [( I 7 I 6 I 5 I 4 ) S ]'

一、编码器(Encodor)

编码: 用二值代码表示具体事物(变量)。 如:用0101表示十进制数5。 编码器分为普通编码器和 优先编码器。 (一)普通编码器 普通编码器任何时刻只允许 一个输入有效。 以3位二进制编码器的设计 为例:

注意这个名称

8

1.真 值表

2.函数式

' ' ' ' ' ' ' ' ' ' ' ' Y2 I 7 I 6 I 5 I 4 I 3 I 2 I1' I 0 I 7 I 6 I 5 I 4 I 3 I 2 I1' I 0

Z 3 m ( 2,3,5) ( m m m )

' 0 ' 2

' ' 5 ' 4 ' ' 7

Z 4 m (0,2,4,7 ) ( m m m m )

由于译码器输出 低电平有效,故 选用与非门

25

(四)显示译码器 1.七段字符显示器 这种显示器可用多种发光器件构 成。例如半导体发光二极管、液晶等。 这里以发光二极管为例进行说明。 半导体数码管BS201A的外形图、 等效电路: 驱动电路 共阴极接法 VCC T R 共阳极接法 VCC D

南邮数电第4章-(1)

2)工作原理及动作特点( 1 触发有效) 动作特点(钟控原理): 在 CP = 1 的全部时 CP 间里,R、S 端信号 RD 的变化都将引起触发 S 器输出状态的变化。

1 2

干扰信号

缺点:抗干扰能力差。

R

Q

跳变

26

4.3 钟控电位触发器

4.3.1 钟控SRFF(SR锁存器)

CP=0 时,G3、G4 门封锁,触发信号不起作用。 CP=1 时,G3、G4 门打开,触发信号可加到基本触发器上。 1 G1 & 0 G3 & 1 S 1 CP & 0 R

Q

Q 0

& 1 G4 G2

Q 0

G1 & 1 G3 & 0 S 1 CP

Q

&

1 G2 0

& R

G4 1

25

4.3 钟控电位触发器

表 4.3.3 钟控DFF功能表

CP 0 1 1 D ф 0 1

Q

n +1

n

n+1

=Q

n

n+1

=D

表 4.3.4 钟控DFF激励表

Q

0 0

n

(2)功能表和激励表

Q

n + 1

D 0 1 0 1 32

Q

0 1 0 1

0 1

1 1

4.3 钟控电位触发器

4.3.3 钟控触发器的触发方式与空翻 1)触发方式: (1)电位触发: 高电平触发、低电平触发 (2)边沿触发: 上升沿触发 、下降沿触发 2)空翻 定义:在一个CP周期内,触发器的状态发生 两次或两次以上变化的现象。

干扰信号跳变3逻辑功能及其描述1次态方程cp0时q逻辑功能及其描述1次态方程cp0时qn1qnn43钟控电位触发器431钟控srffsr锁存器27qqn1srqnnsr0cp1时sr0cp1时cpsr1?nq0nq2功能表和激励表3逻辑功能及其描述43钟控电位触发器431钟控srffsr锁存器280q100nq10101101111表表431钟控srff功能表2功能表和激励表3逻辑功能及其描述43钟控电位触发器431钟控srffsr锁存器nq1?nqsr29表表432钟控srff激励表000011010011103波形图cps3逻辑功能及其描述43钟控电位触发器431钟控srffsr锁存器30srqq1电路结构及逻辑符号qq43钟控电位触发器432钟控dffd锁存器311dc1dcpc国标符号cp0时qn1qnncp11时qqn1dd2逻辑功能及其描述1次态方程2逻辑功能及其描述1次态方程43钟控电位触发器432钟控dffd锁存器32cp1时qqdd2功能表和激励表cpd1?nq0nq100111表表433钟控dff功能表nq1?nqd000011100111表表434钟控dff激励表1电位触发

数字逻辑电路第4章触发器PPT课件

.

35

三、主从型触发器 1.主从RS触发器

下降沿 触发

第4章 4.2

CP上升沿到来主触发 器接收信号,从触发

器保持原态。

延迟输出

CP下降沿到来主触

发器被封锁,从触

发器接收主触发器

.

信号。

36

主从型触发器的动 作特点:

(触发器分两步动作) 当CP=1时,输入信号 进入主触发器,从触 发器CP=0被封锁; 当CP=0时,主触发器 被封锁,从触发器 CP=1被开启。

基本RS触发器亦称之为置位、复位触发器。

.

18

用或非门构成的基本RS触发器

第4章 4.2

输入高电 平有效

.

19

第4章 4.2

用或非门构成的基本RS触发器

特性表

用与非门构成的基本RS触发器

特性表

SD RD Qn Qn+1

000

001

1 01 1 00 010 011 110 111

0 保持 1

1 置‘1’

第四章 触发器

第4章目录

4.1 基本触发器

4.2 同步触发器 4.3 主从触发器 4.4 边沿触发器 4.5 时钟触发器的功能分类和转换

4.6 触发器的逻辑功能表示方法及转换

.

1

概述

和门电路一样,触发器也是构成各种复杂数字系 统的基本逻辑单元。触发器的基本逻辑功能是可以保 存1位二进制信息。

触发器具有什么功能 ?

特性方程: Qn+1=J Qn + K Qn

.

53

3. T 触发器与T 触发器

第4章 4.3

(1) T 触发器

把JK触发器的J、K端接在一起可构成T触发器。(一 般无专门定型产品)

数字电子技术基础PPT第四章 触发器

2020/6/22

分析结果:

(1)若J=1,K=0,则CP=1时主触发器置“1” (无论Q是0还是1),待CP=0后,从触发器也置 “1”(2)。若J=0,K=1,则CP=1时主触发器置“0” (无论Q是0还是1),待CP=0后,从触发器也置 “0(”3)若。J=0,K=0,则主、从触发器都保持原

在整个CP=1期 间,输出随输入 变化而变化。是 电平触发而不是 边沿触发。

2020/6/22

若CP在=1电时路段中:增假加如

①上②升两沿根到连来线时,,则S=G03,、

GR5=是1而一使个Q基=1本,R若S触此发后

器的,CPG=41、期G间6是出一现个R=基0,

③

本S=R1S,触即发R器欲。使输出置

本节是站在逻辑功能的角度对触发器进行 了分类:有RS触发器、JK触发器、D触发器和 T触发器。

值得注意的是:电路结构和逻辑功能不具 有一一对应关系。

2020/6/22

值得注意的是:电路结构和逻辑功能不具 有一一对应关系。

以D触发器为例:

(1)P222图5.3.4,由电平触发的触发器构 成,且为电平触发;

状态。

(4)若J=1,K=1,若Qn =0,则Qn+1=1;若Qn =1,则Qn+1=0。即Qn+1 = Qn 。换句话说, J=K=1时,每遇到一个CP的下降沿,则Q翻转 一次。

2020/6/22

2.动作特点: (1)分两拍; (2)输出Q是由下降沿来临之前的Q’决定

的; (3)J=K=1时,触发器遇一个CP下降沿就

也因称此维称持③线④。为阻塞线。 2020/6/22

3.利用传输延迟时间的边沿触发器(下降沿触 发器)

数字电子技术基础(第四版)-第4章-组合逻辑电路解析PPT课件

-

54

设计实例2:用2N选一数据选择器实现 N+1个变量的逻辑函数。

设计思想: ①将N个变量接数据选择器的选择输入端(即地址端) ②余下的一个变量作为数据选择器的数据输入端。

-

55

例:用74153实现三变量函数。

F (A ,B ,C ) m (1 ,3 ,5 ,6 )

解一:设B接A1,C接A0。

A

' 0

)

m2

'

...

Y7 ' ( A2 A1A0 ) m 7 '

-

45

-

46

-

47

三、用译码器构成函数发生器P186

例1:

请写出Y的逻辑函数式

Y(Y3'Y4'Y5')' Y3Y4 Y5

m3 m4 m5

m(3, 4,5)

Y A 'B C A B 'C ' A B 'C

-

48

例2:用74138构成下 列函数发生器:

F A 'B 'C A 'B C A B 'C A B C ' 0 B 'C ' ( A ' A ) B 'C A B C ' A 'B C

0 m 0 1 m 1 A m 2 A 'm 3

D 0 m 0 D 1 m 1 D 2 m 2 D 3 m 3

-

56

解二:设A接A1,B接A0。

4)画逻辑图(略)

-

31

三、优先编码器 8线-3线优先编码器

74HC148

-

1、功能表

输入:I 0 ~ I 7 ,共8个输入端

精品课件-数字电子技术-第4章

第4章 小规模时序电路及其应用

图4-15 例4.3波形

第4章 小规模时序电路及其应用

当第1个CP脉冲的下降沿到来时, JK=10,则触发器置1, Q为1;当第2个CP脉冲的下降沿到来时,JK=00,则触发器状 态保持不变,Q仍为1;当第3个CP脉冲的下降沿到来时, JK=01,则触发器置0,Q为0;当第4个CP脉冲的下降沿到来 时,JK=00,则触发器状态保持不变,Q仍为0;当第5个CP脉 冲的下降沿到来时,JK=11,则触发器状态翻转,Q 转变为1。

第4章 小规模时序电路及其应用

【例4.4】 上升沿触发的JK触发器的CP脉冲和输入信号 J、 K的波形如图4-16 所示, 画出触发器输出Q的波形(设Q 的初始状态为“0”)。

解: 由于上升沿JK触发器是上升沿触发的, 因此作图时 应首先找出各CP脉冲的上升沿,再根据当时的输入信号J、K 得出输出Q,作出波形如图4-16所示。

第4章 小规模时序电路及其应用

表4-1 基本RS触发器真值表

第4章 小规模时序电路及其应用

2) 特征方程 基本RS触发器的次态与现态及输入间的关系也可以用逻辑 函数表示。将基本RS触发器的真值表填入卡诺图,得到Qn+1函 数的卡诺图,如图4-4所示。通过卡诺图化简得到

第4章 小规模时序电路及其应用

第4章 小规模时序电路及其应用

图4-8 时钟RS (a) 逻辑图; (b) 国标符号;(c) 用74HC00实现的Байду номын сангаас钟RS触发器

第4章 小规模时序电路及其应用

2.

当CP=0 当CP=1时,触发器的状态随输入信号的不同而改变,变 化的规律可用图4-9(a)所示的状态图、图4-9(b)所示的状态 卡诺图、表4-3所示的特性表以及下述特征方程及约束条件 来描述。

数电第四章 触发器课件

电子技术数字电路部分第四章触发器第四章触发器§ 4.1 概述§ 4.2 触发器的基本形式§ 4.3 触发器按逻辑功能的分类§ 4.4 触发器逻辑功能的转换§ 4.5 触发器的触发方式§ 4.6 触发器应用举例§ 4.1 概述触发器触发器输出有两种可能的状态:0、1;输出状态不只与现时的输入有关,还与原来的输出状态有关;触发器是有记忆功能的逻辑部件。

按功能分类:R-S触发器、D型触发器、JK触发器、T型触发器等。

& a& b Q Q D R D S 反馈两个输入端两个输出端 § 4.2 触发器的基本形式& a & b Q Q D R D S D D 1 1 00 1 0 10 输出仍保持: 10==Q Q& a & b Q Q D R D S D D 0 1 11 1 0 10 输出变为: 10==Q QDD 10==Q Q 1 01 01 0 1 1 输出变为: 01==Q Q & a & b Q Q D R D SD D 01==Q Q 0 0 11 0 1 01 输出保持: 01==Q Q & a & b Q Q D R D SDD 10 1 11 0 0 1 输出保持原状态: 01==Q Q 01==Q Q & a & b Q Q D R DSD D 10==Q Q 0 1 1 1 0 1 10 输出保持原状态: 10==Q Q & a & b Q Q D R D S输入R D =0, S D =0时1 1 输出全是1 但当R D =S D =0同时变为1时,翻转快的门输出变为0,另一个不得翻转。

& a & bQ Q DR DS基本触发器的功能表R D S D QQ 1 1 保持原状态0 1 0 11 0 1 0 0 0 同时变为1后不确定1. 基本触发器是双稳态器件,只要令R D =S D =1,触发器即保持原态。

精品课件-数字电子技术(第三版)(刘守义)-第4章

第 4 章 编码器与译码器

2. 二-十进制编码 (1) 8421BCD码是用4位二进制数表示1位十进制数, 这4位二进制数的权分别为8、 4、 2、 1。 (2) 2421BCD码的4位二进制数的权分别是2、 4、 2、 1, 这种BCD码的编码方案不是惟一的, 表4.5中列出了其中 两种。

第 4 章 编码器与译码器

第 4 章 编码器与译码器

5) 74LS147 (1) 编码功能。 给一块74LS147接通电源和地, 在 74LS147的9个输入端加上输入信号(按表4.2所示, 依次给 I1~I9加信号), 用逻辑试电笔或示波器测试Y0、 Y1、 Y2、 Y3 4个输出端的电平, 将测试结果填入表4.2中。

第 4 章 编码器与译码器

第 4 章 编码器与译码器

从表4.4中可见, 循环码中每一位代码从上到下的排列 顺序是以固定周期进行循环的。 其中右起第一位的循环周期 是“0110”, 第二位是“00111100”, 第三位是 “0000111111110000”, 等等。 4位循环码以最高位0与1之 间位轴对折, 除反射位外, 其他3位均互为镜像。 故有时 也将循环码称为反射码。

第 4 章 编码器与译码器

第 4 章 编码器与译码器

4.1.3 当要求信号传输或处理的错误概率小时, 应选用具有单

位间距特性的编码。 因为这类编码的各相邻码组之间只有一 位码不同, 因此在连续传输、 译码时的可靠性高, 能消除 译码噪声产生的逻辑错误。

第 4 章 编码器与译码器

一般数字设备多采用8421BCD码, 因而在应用时应尽量 采用8421BCD码, 以避免增加码制转换电路。

第 4 章 编码器与译码器

2. 实训设备: 逻辑试电笔, 示波器, 直流稳压电源, 集成电路测试仪。 实训器件: 实验电路板、 实训3中调试好的抢答器实验 板、 二-十进制编码器74LS147、 字符译码器74LS48、 共 阴极数码管、 非门74LS04各一块。

数字电子技术4[1]

![数字电子技术4[1]](https://img.taocdn.com/s3/m/1021454378563c1ec5da50e2524de518964bd3b5.png)

Qn+1 Qn 1 0 不定

数字电子技术4[1]

(三)基本 RS 触发器的优缺点

优点 电路简单,是构成各种触发器的基础。 缺点 1. 输出受输入信号直接控制,不能定时控制。

2. 有约束条件。

PPT文档演模板

数字电子技术4[1]

二、同步触发器 Synchronous Flip - Flop

PPT文档演模板

数字电子技术4[1]

二、触发器的类型

根据逻辑功能不同分为

RS 触发器 D 触发器 JK 触发器 T 触发器 T 触发器

根据触发方式不同分为

电平触发器

边沿触发器

主从触发器

根据电路结构不同分为

基本 RS 触发器 同步触发器 主从触发器 边沿触发器

三、触发器逻辑功能的描述方法

主要有特性表、特性方程、驱动表 (又称激励表)、状态转换图和波形图 (又称时序图)等。

PPT文档演模板

数字电子技术4[1]

2. D 触发器的特性表、特性方程、驱动表和状态转换图

D 触发器特性表

D Qn Qn+1 000 010 101 111

特性方程 Qn+1 = D

无约束

Qn+1 在 D = 10 时 就为 10,与 Qn 无关。

D 触发器驱动表 Qn Qn+1 D 00 0 01 1 10 0 11 1

输出

QQ 不定

01 10 不变

Q

输出既非 0 状态,

1 也非 1 状态。当 RD 和 SD 同时由 0 变 1 时, 输出状态可能为 0,也

G2 可能为 1,即输出状态 不定。因此,这种情况

禁用。

RD 0

数电4-1

第二步:列真值表。 第三步:归纳逻辑功能。 该电路为异或逻辑电路。

A B

&

α

&

F

γ

图4-1-1 异或电路逻辑图

表4-1-1 例4-1真值表 A B F

0

0 1 1

0

1 0 1

0

1 1 0

4.1.2 全加器

1.1位全加器 按照组合逻辑电路的分析步 骤,首先写出各级逻辑门的输出

4.1 组合逻辑电路分析

4.1.1 4.1.2 4.1.3 4.1.4 组合逻辑电路分析方法 全加器 编码器 译码器

4.1.5

4.1.6 4.1.7

数值比较器

数据选择器 奇偶产生/校验电路

4.1.1 组合逻辑电路分析方法

分析:根据给定的逻辑电路图,归纳出该逻辑电路的逻辑

功能。 组合逻辑电路的分析通常采用代数法,一般按照以下步骤 进行: (1) 根据给定组合逻辑电路的逻辑图,从输入端开始,逐级

A0 A1 A2 A3

1 2 4 8

0 1 2 3 4 5 6 7 8 9

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9

图4-1-15 4线-10线译码器

演

示

逻辑符号

无效输入状态。

4.译码器的功能扩展 用2线-4线译码器扩展成3线-8线译码器。

Y7 Y6 Y5 Y4 3 2 1 0 BIN/OCTⅡ 1 2 EN ST Y3 Y2 Y1 Y0 3 2 1 0 BIN/OCTⅠ 1

A0 A1 1 2 4 & EN BIN/OCT 0 1 2 3 4 5 6 7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

§4-2 同步时序电路

同步时序电路:

电路中所有触发器的CP脉冲都连接在同一个输入CP 脉冲上,触发器状态的更新和CP脉冲是同步的。

同步时序电路

§4-2-1 §4-2-2 §4-2-3 §4-2-4 §4-2-5 §4-2-6 §4-2-7 §4-2-8

同步时序电路的结构和描述 同步时序电路的分析步骤 米里型电路的分析 莫尔型电路的分析 功能表描述 自启动 异步信号的处理 小结

问题: 如何构成加/减法计数器

问题: 响应CP下降沿

§4-1-4 J-K触发器

一、下降沿触发的J-K触发器

二、 J-K触发器的应用 三、常用的J-K触发器

一、下降沿触发的J-K触发器

用中没有约束条件。 常见的JK触发器有主从结构的,也有边沿型的。

JK触发器是在RS触发器基础上改进而来,在使

1. 逻辑符号及状态真值表

§4-2-1 同步时序电路的结构和描述

同步时序电路: 电路分成米里(mealy)型和莫尔(moore)型两种。 米里型:输出与当前的输入和状态有关。

Z i f i ( x1 , x2 , , xk , Q1 , Q2 , , Qr ) i 1,2, , m W j g j ( x1 , x2 , , xk , Q1 , Q2 , , Qr ) j 1,2, , R

n n

串 行 加 法 器

§4-2-3 莫尔型电路的分析

n Q n 1 D 2 (A, B, Q1 ) m(1,2,4,7) 2 n n n n n A BQ1 ABQ1 A BQ1 ABQ 1 A B Q1

n n Q1 1 D1 (A, B, Q1 ) m(3,5,6,7)

三、时钟R-S触发器的应用

四、时钟R号

关联对象号

控制关联符

逻辑符号

在CP=0期间,G3、G4被封锁,触发器状态不变。 在CP=1期间,由R和S端信号决定触发器的输出状态。 只有CP=1时,触发器的状态才由输入信号R和S来决定。

2. 时钟R-S触发器状态真值表

Q0n 0 1 0 1 0 1 0 1

Q2n+1 0 0 0 1 1 1 1 0

Q1n+1 0 1 1 0 0 1 1 0

Q0n+1 1 0 1 0 1 0 1 0

Z 0 0 0 0 1 1 1 1

同步、莫尔型、模八计数器

§4-2-5 自启动

自启动性:电路在无效状态时,经有限个CP脉冲后 能自动回到有效状态。

n n n n n n ABQ1 A BQ1 ABQ1 ABQ 1 AB AQ1 BQ1

n Q n 1 D 2 (A, B, Q1 ) m(1,2,4,7) 2 n n n n n A BQ1 ABQ1 A BQ1 ABQ 1 A B Q1

逻辑符号

状态真值表

2. JK触发器的状态图和状态表

状态图 状态转换真值表

次态方程: Q

n 1

J Q KQ

n

n

状态表

3.下降沿触发的J-K触发器的工作波形

在CP的下降沿更新状态,次态由CP下降沿到来之 前的J、K输入信号决定。

二、 J-K触发器的应用

J-K触发器组成二进制计数器

J-K触发器组成十六进制减法计数器

触发器的分类: 按逻辑功能不同:RS触发器、D触发器、JK触

发器、T触发器和T′触发器等。

按触发方式不同:电平触发器、边沿触发器和

主从触发器等。

边沿触发器:靠CP脉冲上升沿或下降沿进行触发。

上升沿触发器:靠CP脉冲上升沿触发。

下降沿触发器:靠CP脉冲下降沿触发。

可提高触发器工作的可靠性,增强抗干扰能力。

Q n 1 J 2 Q n K 2 Q n 2 2 2

n ( x Q1 ) Q n 2

米里型电路的分析(续1)

3、画状态表 4、画状态图

Q1n 1 J1 Q1n K1Q1n Q1n

n n n n Q2 1 J 2 Q2 K 2Q2 ( x Q1n ) Q2 n n z Q2 Q1n x Q2 Q1n x

无自启动性

有自启动的电路

开机复位、置位电路

刚开电源时,触发器状态是随机的,为了 使触发器状态确定,要加入复位或置位电路。

三、时钟R-S触发器的应用

构成数据锁存器(D锁存器)

次态方程:Q

n 1

S RQ D DQ D

n n

约束方程:R S D D 0

四、时钟R-S触发器的空翻现象

空翻现象:在一个CP周期内,触发器状态发生一

次以上的翻转现象。 在CP为高时,不允许输入信号变化。

§4-1-3 D触发器

(由输入信号直接控制) 在实际工作中,要求触发器的状态按一定的时间 节拍进行状态更新。

时钟R-S触发器:具有时钟脉冲CP控制的触发器。

该触发器状态的改变与时钟脉冲同步。

时钟触发器的状态更新时刻:受CP输入控制。 触发器更新为何种状态:由触发输入信号决定。

触发器逻辑功能的描述:通常用功能表、时序

图、状态表、特性方程和状态图表示。

莫尔型:输出只与当前状态有关。

Z i f i (Q1 , Q2 , , Qr ) i 1,2, , m W j g j ( x1 , x2 , , xk , Q1 , Q2 , , Qr ) j 1,2, , R

§4-2-2 同步时序电路的分析步骤

步骤:

1、写出各触发器的激励方程和电路输出方程; 2、导出各触发器的次态方程; 3、由次态方程填写卡诺图得到状态表; 4、由状态表画出状态图;

一、D触发器逻辑功能 二、D触发器的工作波形 三、D触发器的应用 四、D触发器的脉冲工作特性 五、常用的D触发器

一. D触发器逻辑功能

1. 逻辑符号及状态真值表 D 0 1 D触发器逻辑符号 “∧”表示边沿触发方式 Qn+1 0 1

状态真值表

上升沿触发的D触发器:

在CP脉冲的上升沿,激励端D的输入将置入触发器。

n n Q1 1 D1 (A, B, Q1 ) m(3,5,6,7)

n n n n n n ABQ1 A BQ1 ABQ1 ABQ 1 AB AQ1 BQ1

串 行 加 法 器

例2:莫尔型电路分析

Q2n 0 0 0 0 1 1 1 1

Q1n 0 0 1 1 0 0 1 1

5、画出输出波形图;

6、总结逻辑功能。

§4-2-3 米里型电路的分析

例1:

1、写出激励方程和输出方程 J1 K 1 1

n J 2 K 2 x Q1 n n z Q n Q1 x Q n Q1 x 2 2

2、求出次态方程

n n n Q1 1 J1 Q1 K1Q1 n Q1

§4-1-5 T与Tˊ触发器

T触发器:具有保持和翻转功能。

1. T触发器的次态方程

Q

n 1

TQ

n

Tˊ触发器:(T≡1)

Qn 1 Qn

T触发器逻辑符号

状态图

状态表

2. JK触发器、D触发器构成D触发器

J-K触发器组成T触发器

D触发器组成T触发器

3. 由T触发器构成的异步计数器

4. 异步计数器小结

异步电路:电路中触发器的CP不是连接在 同一个输入CP脉冲上,由于电路的延时不 同,各触发器翻转的时间有差异。

异步2n进制计数器的结构

五进制计数器构成十进制计数器

§4-1-6 常用集成触发器

目前市场上出售的集成触发器产品通常为JK触 发器和D触发器两种类型。

§4-1-7 触发器小结

基本RS触发器的触发方式:逻辑电平直接触发。

§4-4

§4-5

§4-6

集成触发器 同步时序电路 集成计数器其及应用 集成移位寄存器其及应用 随机访问存储器 应用实例

§4-1 集成触发器

触发器:一种常用的记忆元件,能存储一位二进制数码,是构成

时序逻辑电路的基本单元电路。

§4-1-1 §4-1-2 §4-1-3 §4-1-4 §4-1-5 §4-1-6 §4-1-7

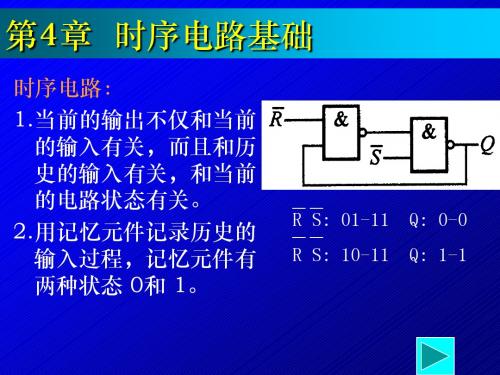

第4章 时序电路基础

时序电路: 1.当前的输出不仅和当前 的输入有关,而且和历 史的输入有关,和当前 的电路状态有关。 2.用记忆元件记录历史的 输入过程,记忆元件有 两种状态 0和 1。

R S: 01-11 Q: 0-0 R S: 10-11 Q: 1-1

时序电路基础

§4-1 §4-2

§4-3

3. 基本R-S触发器的状态图和状态表

状态真值表

状态图

次态方程:Q n 1 S Q n R 约束方程:R S 1

状态表

二、基本R-S触发器的工作波形

三、或非门构成的基本R-S触发器

或非门构成的基本R-S触发器 状态真值表

逻辑符号

§4-1-2 时钟R-S触发器

基本RS触发器的触发方式:逻辑电平直接触发。 (由输入信号直接控制) 在实际工作中,要求触发器按统一的节拍进行状 态更新。措施:

一、与非门构成的基本R-S触发器

1. 电路组成及逻辑符号

Reset为置0端(或复位端) Set为置1端(或置位端) 非号“-”:表示低电平有 效

与非门构成的基本R-S 触发器

逻辑符号

2. 基本R-S触发器状态真值表

与非门构成的基本R-S 触发器

状态真值表

现态:指触发器输入信号变化前的状态,用Qn表示; 次态:指触发器输入信号变化后的状态,用Qn+1表示。 状态转换真值表:次态Qn+1与输入信号和现态Qn之间 关系的真值表。