组合逻辑VHDL设计——译码器

实验三组合逻辑电路应用——译码器、数据选择器

实验三组合逻辑电路应用——译码器、数据选择器

译码器和数据选择器是现代数字电子学中常用的两种组合逻辑电路。

它们可以将输入

的二进制信号转换为对应的输出信号,并且在数字电路中具有广泛的应用。

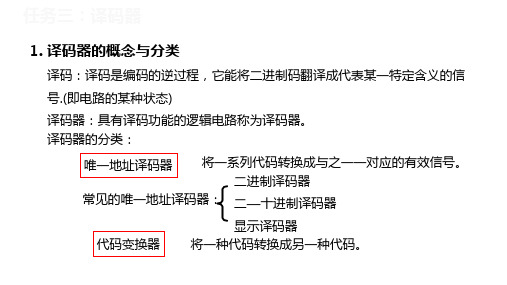

一、译码器

译码器是一种将输入的二进制信号转换成对应输出信号的数字电路。

译码器的作用是

将输入的地址码转换成溢出电路所能识别的控制信号,通常用来将不同的地址码映射到不

同的设备或功能上。

比如在存储器系统中,根据不同地址码,从RAM或者ROM中取出相应

的数据或指令。

除此之外,译码器还可以用于数据压缩、解码、解密等领域。

在一些数字电路中,译

码器还可以充当多路复用器、选择器等电路的功能。

译码器的分类按照其输入和输出的码制不同,可以分为译码器、BCD译码器、灰码译

码器等。

其中,最常见的是2-4译码器、3-8译码器、4-16译码器等。

二、数据选择器

数据选择器是一种多路选择器,根据控制信号选择输入端中的一个数据输出到输出端。

选择器的控制信号通常由一个二进制码输入到它的控制端,二进制码的大小由选择器的通

道数决定。

数据选择器广泛用于控制、多媒体处理、信号处理等方面。

数据选择器与译码器相比,最主要的区别在于其输出可以不仅限于数字信号。

数据选

择器可以处理模拟信号、复合信号等多种形式的信号,因为它可以作用于信号的幅度、相位、频率等方面。

数据选择器按照输入和输出的端口取数的不同,可以分为单路选择器和多路选择器。

常见的有2-1选择器、4-1选择器、8-1选择器、16-1选择器等。

译码器设计组合逻辑电路的方法步骤

译码器设计组合逻辑电路的方法步骤宝子,今天咱来唠唠用译码器设计组合逻辑电路这事儿。

译码器呢,就像是一个翻译官。

那怎么用它来设计组合逻辑电路呢?咱得先了解下要实现的逻辑功能是啥。

比如说,要实现一个判断输入信号是不是满足某个特定关系的功能。

这就好比你要知道自己要做一个啥样的小发明一样。

接着呢,要确定输入变量的个数。

这就像是你要知道自己有多少种原料可以用。

如果有3个输入变量,那就得找合适的3 - 8线译码器之类的。

然后呀,要列出逻辑函数的真值表。

这个真值表就像是一个规则手册。

把输入变量的各种可能取值,以及对应的输出结果都写清楚。

这就好比把每种原料组合能做出啥东西都写下来。

再之后呢,把逻辑函数用最小项表示出来。

这一步就像是把你的小发明的原理用一种特定的数学语言描述出来。

之后就是关键啦,要把译码器的输出和逻辑函数联系起来。

译码器的输出端那些信号就像是一个个小助手,你要根据逻辑函数的要求,把这些小助手合理地组合起来。

比如说,可能需要把某些输出端通过与门或者或门连接起来,就像把小助手们按照你的计划组队一样。

在这个过程中,可能会遇到一些小麻烦哦。

比如说,可能会发现译码器的输出和你想要的逻辑函数不太匹配。

这时候别慌,就像你做手工的时候发现材料有点不对一样,可以调整下连接方式或者再思考下逻辑关系。

最后呢,画出电路图。

这个电路图就是你的设计成果啦,就像你把自己的小发明从想法变成了实实在在的图纸一样。

宝子,用译码器设计组合逻辑电路其实也不是很难啦,只要一步一步来,就像搭积木一样,慢慢就能把它搞定啦。

而且在这个过程中,你还能发现很多逻辑的小乐趣呢。

要是遇到问题也不怕,多试几次,总能成功的哦。

3-8译码器设计

EDA实验报告

学院:专业:班级:

点击菜单项File->New Project Wizard 帮助新建工程。

参看图打开Wizard 之后,界面如2-3

5.选择设计所用器件。

由于本次实验没有使用开发板,故可先随意选择。

8.培养良好的文件布局。

Quartus II 默认把所有编译结果放在工程根目

2.2 使用VHDL完成硬件设计指定单独的编译结果文件目录

9.添加所需设计文件。

本次实验通过VHDL 来描述所设计的硬件,因此要添加VHDL 设计文件到工程文件中去。

74LS138 是常用的小规模集成电路芯片,用于译码。

它有

12.分析与综合。

点击菜单项Processing->start->Start Analysis &

13.全编译文件。

点击菜单项Processing->start compilation

15. Pins 菜单项执行之后,会出现一个引脚配置窗口。

参看图

为了将逻辑分配到 FPGA 外围引脚上,必须根据所用的 FPGA 型号配置输出引脚。

根据所提供的对应开发板指导手册,将 3-8 译码器的输入与输出分别配置到开发板的3 个选择开关(SW2,SW1,SW0)以及8 个LED (LEDR7-LEDR0)上。

16.全编译文件。

完成分配引脚后,点击菜单项Processing->start

18.之后的输出画面如图2-23 所示。

◆本实验指导结束Pins引脚配置窗口:。

项目六 数码管显示译码器的VHDL设计

四、项目实施——1. QuartusⅡ VHDL设计输入法

(3) 项目编译

分析综合

点击Quartus Ⅱ软件工具条上的快捷按钮 进行分析综合。

,对抢答器工程

根据提示信息,处理错误,直至无误为止。

四、项目实施——1. QuartusⅡ VHDL设计输入法

四、项目实施

硬件平台准备

微机一台(Windows XP系统、安装好 Quartus Ⅱ5.0等相关软件)

EDA学习开发板一块 USB电源线一条 ISP下载线一条。

四、项目实施——1. QuartusⅡ VHDL设计输入法

(1) 创建工程

在D:\altera\Quartus50\example\seg7下建立项目seg7 选择EPM240T100C5作为目标器件

三、项目分析

VHDL源程序

--****************************************************** --seg7.vhd library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; --********************************************** entity seg7 is

输入端 ABCD 0000 0001 0010 0011 0100 0101 0110 0111

输出端 abcdefgh 11111100 01100000 11110010 11110010 01100110 10110110 10111110 11100000

EDA实验三组合逻辑电路设计(一)--编译码器设计

西安邮电学院实验中心实验报告院系电子工程学院班级学号姓名成绩教师签字实验日期实验名称组合逻辑电路设计(一)--编译码器设计_______________________________________________________一、实验目的二、实验所用仪表及主要器材三、实验原理简述四、实验测量记录:(如数据、表格、曲线、计算等)五、实验遇到的问题及解决办法:(余留问题,体会等)一、实验目的(1)熟悉组合逻辑电路的VHDL描述方法。

(2)掌握利用CPL器件实现组合逻辑数字电路的方法和过程。

(3)熟练掌握“case”语句与“if…else…”语句的用法。

二、实验所用仪表及主要器材PC,可编程逻辑实验电路板,下载线,USB电源线,双踪示波器,数字万用表,导线若干。

三、实验原理简述应用VHDL设计简单的逻辑电路四、实验内容在MAX+PULSII环境下,用VHDL语言按照输入—>编译—>仿真。

(1)8421BCD码转换为余3码转换表.在MAX+plusII 环境下,用VHDL 语言描述下列逻辑电路,并编译,仿真。

程序仿真结果:(2)设计一个优先编码器。

程序实现如下:仿真结果:五、实验结果见上述内容。

六、实验心得在本次实验中我学会了使用MAX+PLUSII软件的文本编程的方式设计电路。

在本次实验的文本编译环节中出现不少问题:(1)保存时文件名与实体名不一致,导致程序编译结果不正确。

(2)写程序时没有按照语法规则编写,使得文件编译频繁报错,标点的错误也会导致整个程序无法编译。

经过本次实验,加深了我对VHDL的文本编译设计的理解,今后我应该多练习MAX+PLUSII软件以减少错误。

实验四:VHDL语言组合电路设计

实验四:VHDL语言的组合电路设计一、实验目的学习用VHDL语言设计组合电路的方法、熟悉总线数据输入方式。

二、实验内容编程实现一个优先编码、译码及显示的电路。

三、实验条件(1)电脑。

(2)开发软件:Quartus II(3)开发设备:EL —EDA—V型;EDA实验开发系统。

(4)拟用芯片:ACEX1K;EP1K100QC208-3。

四、实验要求1、用VHDL设计10线——4线优先编码器模块。

2、用VHDL设计BCD码——7段译码器模块。

3、用VHDL完成编码、译码及显示的描述。

4、对设计结果进行仿真、下载及硬件测试。

五、实验设计(1)10线—4线优先编码器模块(2)7段译码器模块Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;ENTITY display ISPort(clkdsp: in std_logic;D0,D1,D2,D3,D4,D5,D6,D7:IN STD_LOGIC_VECTOR(3 DOWNTO 0);SEL: out std_logic_vector(2 downto 0);Led7s: OUT std_logic_vector(6 downto 0));END ENTITY display;Architecture one of display isSignal cnt8: std_logic_vector(2 downto 0);Signal y: std_logic_vector(3 downto 0);BeginP1:Process(clkdsp) --8进制计数器BeginIf clkdsp' event AND CLKDSP='1' thenCnt8<=cnt8+1;End if;SEL<=cnt8;End process P1;P2:PROCESS(cnt8,D0,D1,D2,D3,D4,D5,D6,D7) --8选1数据选择器BEGINCASE cnt8 ISWHEN "000"=> Y<= D0;WHEN "001"=> Y<= D1;WHEN "010"=> Y<= D2;WHEN "011"=> Y<= D3;WHEN "100"=> Y<= D4;WHEN "101"=> Y<= D5;WHEN "110"=> Y<= D6;WHEN "111"=> Y<= D7;WHEN OTHERS=>NULL;END CASE;END PROCESS P2;P3:PROCESS(y) --显示译码器BEGINCASE y(3 DOWNTO 0) isWHEN "0000"=>LED7S<="0111111";WHEN "0001"=>LED7S<="0000110";WHEN "0010"=>LED7S<="1011011";WHEN "0011"=>LED7S<="1001111";WHEN "0100"=>LED7S<="1100110";WHEN "0101"=>LED7S<="1101101";WHEN "0110"=>LED7S<="1111101";WHEN "0111"=>LED7S<="0000111";WHEN "1000"=>LED7S<="1111111";WHEN "1001"=>LED7S<="1101111";WHEN "1111"=>LED7S<="1000000";WHEN OTHERS=>NULL;END CASE;END PROCESS P3;END one;3)编码、译码及显示模块的VHDL程序LIBRARY IEEE;USE IEEE.std_logic_1164.all;ENTITY ENCODER_DEC7S ISPORT(I:IN BIT_VECTOR(9 DOWNTO 0);LED7S:OUT BIT_VECTOR (6 DOWNTO 0));END ENCODER_DEC7S;ARCHITECTURE one OF ENCODER_DEC7S IS SIGNAL Y:STD_LOGIC_VECTOR(3DOWNTO 0); BEGINP1:PROCESS(I)BEGINIF(i(9)='0')THEN y<="1001";ELSIF(i(8)='0')THEN y<="1000";ELSIF(i(7)='0')THEN y<="0111";ELSIF(i(6)='0')THEN y<="0110";ELSIF(i(5)='0')THEN y<="0101";ELSIF(i(4)='0')THEN y<="0100";ELSIF(i(3)='0')THEN y<="0011";ELSIF(i(2)='0')THEN y<="0010";ELSIF(i(1)='0')THEN y<="0001";ELSIF(i(0)='0')THEN y<="0000";ELSE y<="0000";END IF;END PROCESS P1;P2:PROCESS(Y)BEGINCASE Y isWHEN"0000"=>LED7S<="0111111";WHEN"0001"=>LED7S<="0000110";WHEN"0010"=>LED7S<="1011011";WHEN"0011"=>LED7S<="1001111";WHEN"0100"=>LED7S<="1100110";WHEN"0101"=>LED7S<="1101101";WHEN"0110"=>LED7S<="1111101";WHEN"0111"=>LED7S<="0000111";WHEN"1000"=>LED7S<="1111111";WHEN"1001"=>LED7S<="1101111";WHEN OTHERS=>NULL;END CASE;END PROCESS P2;END one;4)仿真波形5)管脚锁定电路引脚 CLKCLR EN UP ...... LED7 CO EP1K100QC208-3芯片Pin78 Pin7 Pin8 Pin90 ...... Pin97 Pin36 EDA 实验开发系统 CLK5 d0 d1 a ...... g LED0五、实验结果及总结1)系统仿真情况从系统仿真结果可以看出,本系统完全符合设计要求。

用VHDL设计三八译码器。。超赞版

3-8译码器的设计1 设计目的与要求随着社会的进一步发展,我们的生活各个地方都需要计算机的参与,有了计算机,我们的生活有了很大的便利,很多事情都不需要我们人为的参与了,只需要通过计算机就可以实现自动控制。

由此,计算机对我们的社会对我们每个人都是很重要的。

所以我们要了解计算机得组成,内部各种硬件,只有了解了计算机基本器件已经相应的软件,才能促进社会的发展。

编码器和译码器的设计是计算机的一些很基础的知识,通过本次对于编码器和译码器的设计,可以让我知道究竟这种设计是如何实现的,这种设计对我们的生活有什么帮助,这种设计可以用到我们生活的哪些方面,对我们的各种生活有什么重大的意义。

1.1 设计的目的本次设计的目的是通过简单的译码器的设计掌握基本的计算机的一些有关的知识,通过查资料已经自己的动手设计去掌握EDA技术的基本原理已经设计方法,并掌握VHDL硬件描述语言的设计方法和思想。

以计算机组成原理为指导,通过将理论知识,各种原理方法与实际结合起来,切实的亲手设计,才能掌握这些非常有用的知识。

通过对编码器和译码器的设计,巩固和综合运用所学知识,提高IC设计能力,提高分析、解决计算机技术实际问题的独立工作能力。

也能通过这种自主设计,增强自己的动手能力,将理论知识切实应用的能力,这对我们将来的发展是很有帮助的。

1.2 设计要求根据计算机组成原理中组合逻辑电路设计的原理,利用VHDL设计计算机电路中译码器的各个模块,并使用EDA 工具对各模块进行仿真验证和分析。

译码器由三-八译码器为实例代表。

关键词:输入、输出、译码2 VHDL的简单介绍2.1 VHDL的简介VHDL语言是一种用于电路设计的高级语言。

它在80年代的后期出现。

最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。

VHDL翻译成中文就是超高速集成电路硬件描述语言,主要是应用在数字电路的设计中。

目前,它在我过的应用多数是用在FPGA/CPLD/EPLD的设计中。

eda第二次实验 38译码器

实验二组合逻辑电路的VHDL模型实验一、实验目的1、掌握组合逻辑和时序逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。

3、了解通用同步计数器,异步计数器的使用方法。

4、理解积分分频器的原理。

二、硬件要求拨位开关、FPGA主芯片EP1K30QC208、LED显示模块三、实验原理译码器是输入数码和输出数码之间的对应关系,也就是说,“输入码和输出码之间的对应表”这应该算是设计译码器的必须条件。

译码器常用来做码和码之间的转换器,也常被用于地址总线或用作电路的控制线。

例如下面为常见的3×8译码器的真值表:实验中可根据需要,为3×8译码器加入使能控制脚。

一般的分频器可获得的分频频率种类分布不均匀,积分分频,能比较好的解决这个问题。

1、分频结果=来源频率×N/(2ⁿ-1);2、频率波形不均匀。

四、实验内容及步骤本实验内容是完成38译码器和5/8分频器的设计,然后将3×8译码器的结果在实验箱上实现,5/8分频器则能正确仿真、显示,实验步骤如下:1、编写3×8译码器的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连线。

6、给目标板下载代码,在开关输入键值,观看实验结果。

7、编写5/8分频器的VHDL代码。

8、用MaxPlusII对其进行编译仿真。

9、使用WaveForm进行波形仿真。

五、程序代码1. 38译码器library ieee;use ieee.std_logic_1164.all;entity a3toy8 isport (en:in std_logic;a:in std_logic_vector(2 downto 0);b:in std_logic_vector(2 downto 0);y:out std_logic_vector(7 downto 0);YM: out std_logic_vector(7 downto 0));end entity a3toy8;architecture a3y8 of a3toy8 issignal t:std_logic_vector(3 downto 0);signal v:std_logic_vector(3 downto 0);begint <= en & a(2 downto 0);process(t(3 downto 0))begincase t(3 downto 0) iswhen "1000" => Y(7 downto 0) <= "00000001";when "1001" => Y(7 downto 0) <= "00000010";when "1010" => Y(7 downto 0) <= "00000100";when "1011" => Y(7 downto 0) <= "00001000";when "1100" => Y(7 downto 0) <= "00010000";when "1101" => Y(7 downto 0) <= "00100000";when "1110" => Y(7 downto 0) <= "01000000";when "1111" => Y(7 downto 0) <= "10000000";when others => Y(7 downto 0) <= "00000000";end case;end process;v <= t;process(v(3 downto 0))begincase v(3 downto 0) isWHEN "1000" => YM(7 downto 0) <= "01100000";WHEN "1001" => YM(7 downto 0) <= "11011010";WHEN "1010" => YM(7 downto 0) <= "11110010";WHEN "1011" => YM(7 downto 0) <= "01100110";WHEN "1100" => YM(7 downto 0) <= "10110110";WHEN "1101" => YM(7 downto 0) <= "10111110";WHEN "1110" => YM(7 downto 0) <= "11100000";WHEN "1111" => YM(7 downto 0) <= "11111110";when others => YM(7 downto 0) <= "00000000";end case;end process;end architecture a3y8;本代码是通过控制拨动开关来控制led灯,并且在数码管上显示发亮的是第几盏led。

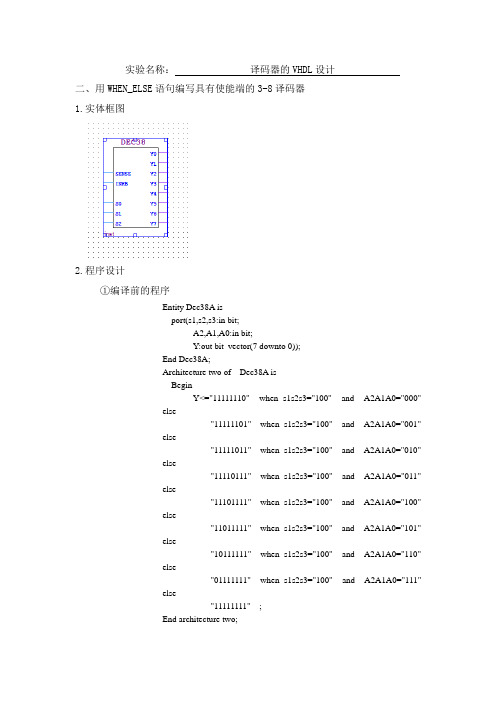

译码器的VHDL设计

实验名称:译码器的VHDL设计二、用WHEN_ELSE语句编写具有使能端的3-8译码器1.实体框图2.程序设计①编译前的程序Entity Dec38A isport(s1,s2,s3:in bit;A2,A1,A0:in bit;Y:out bit_vector(7 downto 0));End Dec38A;Architecture two of Dec38A isBeginY<="11111110" when s1s2s3="100" and A2A1A0="000"else"11111101" when s1s2s3="100" and A2A1A0="001"else"11111011" when s1s2s3="100" and A2A1A0="010"else"11110111" when s1s2s3="100" and A2A1A0="011"else"11101111" when s1s2s3="100" and A2A1A0="100"else"11011111" when s1s2s3="100" and A2A1A0="101"else"10111111" when s1s2s3="100" and A2A1A0="110"else"01111111" when s1s2s3="100" and A2A1A0="111"else"11111111" ;End architecture two;②程序编译错误情况错误1:Error (10482): VHDL error at Dec38A.vhd(15): object "s1s2s3"is used but not declared错误2:Error (10482): VHDL error at Dec38A.vhd(15): object "A2A1A0"is used but not declared③正确的程序Entity Dec38A isport(s1,s2,s3:in bit;A2,A1,A0:in bit;Y:out bit_vector(7 downto 0));End Dec38A;Architecture two of Dec38A issignal s:bit_vector(1 to 3);signal A:bit_vector(2 downto 0);Begins<=s1 & s2 & s3;A<=A2 & A1 & A0;Y<="11111110" when s="100" and A="000" else"11111101" when s="100" and A="001" else"11111011" when s="100" and A="010" else"11110111" when s="100" and A="011" else"11101111" when s="100" and A="100" else"11011111" when s="100" and A="101" else"10111111" when s="100" and A="110" else"01111111" when s="100" and A="111" else"11111111" ;End architecture two;3.仿真波形图4.仿真波形分析S1、S2、S3是使能端,A0、A1、A2是选通端,Y7~Y0是输出端当S1、S2、S3为100时,译码器工作A="000"时,Y="11111110"A="001"时,Y= "11111101"A="010"时,Y="11111011"A="011"时,Y="11110111"A="100"时,Y="11101111"A="101"时,Y= "11011111"A="110"时,Y="10111111"A="111"时,Y= "01111111" ;使能端无效时为"11111111" ;二、用WHEN_ELSE语句实现驱动共阳极数码管七段显示译码器1.实体框图2.程序设计①编译前的程序Library ieee;Use ieee.std_logic_1164.all;Entity DD isport(A: in std_logic_vector(3 downto 0);DOUT:out std_logic_vector(6 downto 0));End DD;Architecture three of DD isBeginDOUT<="1111110" when A="0000" else"0110000" when A="0001" else"1101101" when A="0010" else"1111001" when A="0011" else"0110011" when A="0100" else"1011011" when A="0101" else"1011111" when A="0110" else"1110000" when A="0111" else"1111111" when A="1000" else"1111011" when A="1001" else"0000000" ;End architecture three;②程序编译错误情况错误:无3.仿真波形图4.仿真波形分析A为输入端,DOUT为输出端A="0000" 时,DOUT="1111110",显示0A="0001" 时,DOUT= "0110000",显示1A="0010" 时,DOUT= "1101101",显示2A="0011" 时,DOUT= "1111001",显示3A="0100" 时,DOUT="0110011",显示4A="0101" 时,DOUT= "1011011",显示5A="0110"时,DOUT= "1011111",显示6A="0111" 时,DOUT= "1110000",显示7A="1000"时,DOUT= "1111111",显示8A="1001" 时,DOUT= "1111011",显示9否则不满足要求时,输出"0000000",不显示;。

3-8译码器设计

摘要EDA技术是以微电子技术为物理层面,现代电子设计技术为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC为目的的一门新兴技术。

而VHDL语言是硬件描述语言之一,其广泛应用性和结构的完整性使其成为硬件描述语言的代表。

随着社会经济和科技的发展,越来越多的电子产品涌如我们的日常生活当中,在日常生活中译码器起着不可忽视的作用。

本设计就是运用VHDL语言设计的3-8译码器。

3-8译码器电路的输入变量有三个即D0,D1,D2,输出变量有八个Y0-Y7,对输入变量D0,D1,D2译码,就能确定输出端Y0-Y7的输出端变为有效(低电平),从而达到译码目的。

关键词 EDA 输入,输出,译码器AbstractEDA technology is for the physical plane microelectronics technology, modern electronic design technology for the soul, and computer software technology as the means, and finally form integrated electronic system or application-specific integrated circuit ASIC for the purpose of a new technology. And VHDL language is one of the hardware description language, which are widely applied and theintegrity of the structure to make it a hardware description language representative.Along with the social economy and the development of science and technology, more and more electronic product surged into our daily life in the daily life of decoder plays an important role. This design is theuse of the design of 3-VHDL language 8 decoder. 3-8 decoder circuit, input variables have three namely D0, D1, D2, output variable has eight Y0-Y7, D0 to input variables, D1, D2 decoding, can determine the output, the output terminal of the Y0-Y7 into effective (low level), so as to achieve the purpose decoding.Key word EDA input output decode目录引言EDA(Electronic Design Automation)技术是现代电子工程领域的一门新技术。

VHDL的编码器和译码器的设计

长沙理工大学《计算机组成原理》课程设计报告王大为学 院 城南学院 专 业 计算机科学与技术 班 级 计算机06-02 指导教师 廖泰长 学生姓名 王大为 学 号 200686250216 课程成绩 完成日期 2009年1月18日课程设计任务书城南学院学院计算机科学与技术专业课程名称计算机组成原理课程设计时间2007~2008学年第一学期19~20周学生姓名王大为指导老师廖泰长题目基于VHDL的编码器和译码器的设计主要内容:本课程设计要求利用硬件描述语言VHDL的设计思想,设计计算机电路中编码器和译码器的各个模块,系统设计要求采用自顶向下的设计方法,系统采用VHDL语言编程实现,并对各模块进行仿真验证和分析。

要求:(1)通过对相应文献的收集、分析以及总结,给出相应课题的背景、意义及现状研究分析。

(2)通过课题设计,掌握计算机组成原理的分析方法和设计方法。

(3)学生按要求编写课程设计报告书,能正确阐述设计和实验结果。

(4)学生应抱着严谨认真的态度积极投入到课程设计过程中,认真查阅相应文献以及实现,给出个人分析、设计以及实现。

应当提交的文件:(1)课程设计报告。

(2)课程设计附件(主要是源程序)。

课程设计成绩评定学院城南学院专业计算机科学与技术班级计06-02 班学号200686250216学生姓名王大为指导教师廖泰长课程成绩完成日期2008年1月18日指导教师对学生在课程设计中的评价评分项目优良中及格不及格课程设计中的创造性成果学生掌握课程内容的程度课程设计完成情况课程设计动手能力文字表达学习态度规范要求课程设计论文的质量指导教师对课程设计的评定意见综合成绩指导教师签字年月日基于VHDL的编码器和译码器的设计学生姓名:王大为指导老师:廖泰长摘要编码器与译码器是计算机电路中基本的器件,本课程设计采用EDA技术设计编码和译码器。

编码器由八-三优先编码器作为实例代表,而译码器则包含三-八译码器和二-四译码器两个实例模块组成。

3-8译码器VHDL设计实验 实验报告

3-8译码器VHDL设计实验实验报告本实验以3-8译码器的设计为主要内容,通过编码器和译码器的学习,深入了解数字电路中常用的译码器,并掌握VHDL语言的应用技巧。

主要技术路线为:定义输入和输出端口->生成选择结构->设计三个MUX组合成8:1 MUX->仿真波形验证。

本实验虽然简单,但对数码管、数码显示器等电路的实现有很大的帮助作用。

一、实验目的1.了解译码器的作用及其应用2.掌握VHDL语言的的原理二、实验器材1.电脑2.EDA软件三、实验原理及过程1.定义输入和输出端口在VHDL设计中,首先要定义输入和输出端口。

根据输入和输出端口的设计,并将其定义到ENTITY中。

2.生成选择结构基于译码器的设计特点,输入是一个二进制数,输出是一个信号。

故可以采用CASE结构生成选择结构。

同时,由于译码器需要将一个二进制数译到一个信号,还需要一个PROCESS处理,将选择的结果赋值到输出信号上。

3.设计三个MUX组合成8:1 MUX通常情况下,8:1 MUX可以用一个MUX8191,但本实验旨在学习三个MUX组合成一个8:1 MUX的方法。

设计时要考虑如下事项:1)MUX中DP、EN、INV等控制信号的设置,由于多个控制信号互相独立,因此采用分别激活的方式;2)由于MUX的输出是显式定义的信号,不能使用临时变量。

因此,采用以下方法生成MUX输出处理:SIGNAL MUX_out : STD_LOGIC := '0';4.仿真波形验证经过以上步骤的设计,就可以进行仿真波形的验证。

经实验验证,设计正确。

其输出信号可以由输入端口激励生成。

四、实验内容1.阅读数据手册及规范表,画出流程图。

2.代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY decoder_3X8 ISPORT (--Define Input & Output SIGNALB : IN STD_LOGIC_VECTOR(2 DOWNTO 0);Y : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END decoder_3X8;ARCHITECTURE structural OF decoder_3X8 ISCOMPONENT mux4x1 ISPORT (D0 : IN STD_LOGIC;D1 : IN STD_LOGIC;D2 : IN STD_LOGIC;D3 : IN STD_LOGIC;S : IN STD_LOGIC_VECTOR(1 DOWNTO 0);Y : OUT STD_LOGIC);END COMPONENT;COMPONENT mux2x1 ISPORT (D0 : IN STD_LOGIC;D1 : IN STD_LOGIC;S : IN STD_LOGIC;Y : OUT STD_LOGIC);END COMPONENT;SIGNAL out1, out2, out3, out4, out5, out6, out7, out8 : STD_LOGIC;BEGINM1: mux2x1 PORT MAP (X => B(0), Y => out1, S => B(1));M2: mux4x1 PORT MAP (X0 => B(2), X1 => out1, X2 => ‘0’, X3 => ‘0’, S => B(1 DOWNTO 0), Y => out2);M3: mux4x1 PORT MAP (X0 => B(2), X1 => ‘0’, X2 => out1, X3 => ‘0’, S => B(1 DOWNTO 0), Y => out3);M4: mux4x1 PORT MAP (X0 => B(2), X1 => ‘0’, X2 => ‘0’, X3 => out1, S => B(1 DOWNTO 0), Y => out4);M5: mux2x1 PORT MAP (X => out2, Y => out5, S => B(2));M6: mux2x1 PORT MAP (X => out3, Y => out6, S => B(2));M7: mux2x1 PORT MAP (X => out4, Y => out7, S => B(2));M8: mux4x1 PORT MAP (X0 => out5, X1 => out6, X2 => out7, X3 => ‘0′, S => B(1 DOWNTO 0), Y => out8);Y <= out8;END structural;ARCHITECTURE rtl OF mux4x1 ISBEGINY <= D0 WHEN S = ‘00’ ELSED1 WHEN S = ‘01’ ELSED2 WHEN S = ‘10’ ELSED3 WHEN S = ‘11’ ELSE’0’;END ARCHITECTURE rtl;3.仿真波形验证:进入仿真 --> Add ----> Signals ----> 选择需要记录的信号 ----> Run ----> 波形记录。

组合逻辑电路—译码器(电子技术课件)

1

A2 1

1

E3 1

E2

1

&

E1

1

& & & & & & & &

逻辑图

&

Y0

&

Y1

& Y2

& Y3

&

Y4

&

Y1 5

&

Y6

& Y7

任务三:译码器

74HC138集成译码器功能表

输

入

输

出

E3 E 2 E 1 A2 A1 A0 Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7

×H××××HHHHHHHH ×XH×××HHHHHHHH L ×××××HHHHHHHH HL L L L L LHHHHHHH HL L L LHHLHHHHHH HL L LHLHHLHHHHH HL L LHHHHHLHHHH HL LHL LHHHHLHHH HL LHLHHHHHHLHH HL LHHLHHHHHHLH HL LHHHHHHHHHHL

×H××××HHHHHHHH ×XH×××HHHHHHHH L ×××××HHHHHHHH HL L L L L LHHHHHHH HL L L LHHLHHHHHH HL L LHLHHLHHHHH HL L LHHHHHLHHHH HL LHL LHHHHLHHH HL LHLHHHHHHLHH HL LHHLHHHHHHLH HL LHHHHHHHHHHL

显示译码器 将一种代码转换成另一种代码。

任务三:译码器

2线 - 4线译码器的逻辑电路(分析)

E

1

A0

1

EDA用VHDL语言设计一个2-4译码器知识讲解

E D A用V H D L语言设计一个2-4译码器2-4译码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY decoder 2 _4 ISPORT( a:IN STD_LOGIC_VECTOR(1 DOWNTO 0); s:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END decoder2_4;ARCHITECTURE Behavioral OF decoder2 _4_t IS BEGINPROCESS(sel)BEGINCASE a ISWHEN "00"=>s<=”0001”;WHEN "01"=>s<=”0010”;WHEN "10"=>s<=”0100”;WHEN "11"=>s<=”1000 “;WHEN OTHERS=>s<=’’0000”END CASE;END PROCESS;END Brhavioral;4选1数据选择器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY sel4 ISPROT(d:IN STD_LOGIC_VECTOR(3DOWNTO 0); a:IN STD_LOGIC_VECTOR(1 DOWNTO 0);s:OUT STD_LOGIC);END sel4:ARCHITECTURE Behavioral OF sel4 ISBEGINROCESS(a,d)BEGINCASE a ISWHEN "00"=>s<=d(0)WHEN "01"=>s<=d(1)WHEN "10"=>s<=d(2)WHEN "11"=>s<=d(3) “;WHEN OTHERS=>s<=’Z’END CASE;END PROCESS;END Brhavioral;100进制加法计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT(clk,en,load,rst:IN STD_LOGICd;IN STD_LOGIC_VECTOR(6 DOWNTO 0);q: OUT STD_LOGIC_VECTOR(6DOWNTO 0):END counter 100;ARCHTECTURE Behavioral OF counter 100 ISsignal qtemp:STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINPROCESS(clk,d,en,load,rst)BEGINIF rst= ’1’ THENqtemp<=”00000000”;ELSIF rising-edge(clk) THEN\IF en=’1’ THENIF load=’1’ THEN qtemp<=d,ELSIF qtemp=”1100011” THEN qtemp<=”00000000”;ELSIF qtemp<=qtemp+’1;END IF;END IF;END IF;END PROCESS;q<=qtemp;END Behavioral;8位从高至低串入串出移位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY shift.register ISPORT( d,clk:IN STD_LOGIC;q:OUT STD_LOGIC);END d shift.register;ARCHITECTURE Behavioral OF shift.register IS signal qtemp:STD_LOGIC_VECTOR(7 DOWNTO 0); BEGINPROCESS(d,clk)BEGINIF rising-edge(clk) THENq<=dtemp(0);dtemp<=d&dtemp(7 DOWNTO 1);END IF;END PROCESS;END Behavioral;状态机LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY fsm ISPORT(tin,clk:IN STD_LOGIC;yout:OUT STD_LOGIC_VECTOR(1DOWNTO 0)); END fsm;ARCHITECTURE Behavioral OF fsm ISTYPE state-type IS (S0,S1,S2)signal state,next_state:state_type;BEGINSYNC_PROC:PROCESS(clk)BEGINIF rising_edge(clk) THENstate < = next_state;END IF;END PROCESS;OUTPUT_DECODE:PROCESS(state)BEGINCASE state ISWHEN S0=> yout <=”00”;WHEN S1=> yout<=”01”;WHEN S2=> yout<=”10”;WHEN OTHERS =>yout<=”zz”;END LAST;END PROCESS;NEXT_STATE_DECODE:PROCESS(state,tin)BEGINnext_state<=state;CASE state ISWHEN S0=>next_state<=S1;WHEN S1=> next_state<=S2;WHEN S2=>IF tin=’0’ THEN next_state<=S1;ELSIF tin=’1’ THEN next_state<=S0;ELSE NULL;END IF;WHEN OTHERS=>NULL;END CASE;END PROCESS;END Behavioral;。

译码器的VHDL设计

3-8译码器的V H D L设计(共4页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--3-8译码器的VHDL设计1.实体框图2.程序设计正确的程序LIBRARY IEEE;USE DECODER38A ISPORT(A2,A1,A0,S1,S2,S3:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY DECODER38A;ARCHITECTURE ONE OF DECODER38A ISSIGNAL S: STD_LOGIC_VECTOR(5 DOWNTO 0);BEGINS<=A2&A1&A0&S1&S2&S3;WITH S SELECTY<="" WHEN "000100","" WHEN "001100","" WHEN "010100","" WHEN "011100","" WHEN "100100","" WHEN "101100","" WHEN "110100","01111111" WHEN "111100","" WHEN OTHERS;END ARCHITECTURE ONE;3.仿真波形图4.仿真波形分析当S1 S2 S3=100时,只有当A2 A1 A0=111时,Y[7]才输出低电平,否则为高电平,当A2 A1 A0=110时,Y[6]才输出低电平,否则为高电平,当A2 A1A0=101时,Y[5]才输出低电平,否则为高电平,Y[4]到Y[0]同理。

基于VHDL语言的数据比较器和译码器的设计PPT学习教案

➢ VHDL语言可以与工艺无关编程; ➢ VHDL语言已做为一种IEEE的工业标准,便于使用、交流

和推广。

VHDL语言的不足之处

➢ 设计的最终实现取决于针对目标器件的编程器,工具的不同 会导致综合质量不一样。

第4页/共15页

WHEN OTHERS=>NULL;

END CASE;

END IF;

END IF;

DOUT<=TMP;

END PROCESS;

第6页/共15页

END ARCHITECTURE ART;

quartus ‖软件的基本使用方法

➢ 新建工程:FILE→New Project Wizard(实体名要和工程名一致) ➢ 新建文件:在当前工程下File →New 选择VHDL File,然后将程序输入,输入完成之后保存文

件FILE →Save AS 输入与实体名一致的文件名 ➢ 编译:首先要分配器件Assignments →Device 在Device family下选择CycloneⅢ系列的芯片;然

后双击左边小窗口的task栏下的Compile Design或者是点击快捷栏上的红色三角型按钮,等待 编译报告,如果有编译不成功有错误则需要检查并修改程序,然后保存并再次编译直至编译 无误 ➢ 仿真:分为时序和功能仿真;先功能仿真Processing →Simulator Tool →Simulation mode: functional →Generate Functional Simulation Netlist成功之后,File →New →Vector Waveform File 然后在空白处右击Insert →Insert Node or Bus将所用的管脚依次添加进去,再给输入管脚赋值, 然后保存(注意:文件名也要和实体名一致) Processing →Start Simulation,观察仿真报告及仿真结果。

第3章-3 VHDL基本逻辑电路设计

【例3.65】8线-3线优先编码器 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY ENCODER IS PORT (A,B,C,D,E,F,G,H:IN STD_LOGIC: Y0,Y1,Y2:OUT STD_LOGIC);

Y(5)<=„1‟ WHEN SR="101" ELSE "0";

Y(6)<=„1‟ WHEN SR="110" ELSE "0"; Y(7)<=„1‟ WHEN SR="111" ELSE "0"; END ARCHITECTURE ART3;

第3章

VHDL 编程基础

方法4:使用CASE-WHEN 语句 ARCHITECTURE ART4 OF DECODER IS SIGNAL SR:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN SR <= C&B&A; PROCESS(SR) IS

END ENTITY ENCODER;

第3章

VHDL 编程基础

方法1:使用条件赋值语句

ARCHITECTURE ART1 OF ENCODER IS

SIGNAL SY:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN SY (2 DOWNTO 0) <= "111" WHEN H=„1‟ ELSE "110" WHEN G=„1‟ ELSE "101" WHEN F=„1‟ ELSE "100" WHEN E=„1‟ ELSE "011" WHEN D=„1‟ ELSE "010" WHEN C=„1‟ ELSE "001" WHEN B=„1‟ ELSE "000" WHEN A=„1‟ ELSE "XXX";

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验名称: 组合逻辑VHDL设计——译码器 班级: 09电气2Z 学号: 09312213 姓名: 钱雷

一、3—8译码器的VHDL设计(S1.S2.S3分别为1.0.0时,译码器工作,

译码器的输出端口只有一个输出低电平,其余为高电平;否则,译码器

输出全为1)

1.实体框图

2.程序设计

①编译前的程序

library ieee;

use ieee.std_logic_1164.all;

entity decoder38a is

port(A2,A1,A0:in std_logic;

S2,S1,S0:in std_logic;

Y:out std_logic_vector(7 downto 0));

end entity decoder38a;

architecture one of decoder38a is

signal A:std_logic_vector(2 downto 0);

begin

A<=A2&A1&A0&S2&S1&S0;

with A select

Y<="11111110" when "000100",

"11111101" when "001100",

"11111011" when "010100",

"11110111" when "011100",

"11101111" when "100100",

"11011111" when "101100",

"10111111" when "110100",

"01111111" when "111100",

"ZZZZZZZZ" when others;

end architecture one;

②程序编译错误情况

③正确的程序

library ieee;

use ieee.std_logic_1164.all;

entity decoder38a is

port(A2,A1,A0:in std_logic;

S1,S2,S3:in std_logic;

Y:out std_logic_vector(7 downto 0)); end entity decoder38a;

architecture one of decoder38a is

signal A:std_logic_vector(5 downto 0); begin

A<=A2&A1&A0&S1&S2&S3;

with A select

Y<="11111110" when "000100",

"11111101" when "001100",

"11111011" when "010100",

"11110111" when "011100",

"11101111" when "100100",

"11011111" when "101100",

"10111111" when "110100",

"01111111" when others;

end architecture one;

3.仿真波形图

4.仿真波形分析

真值表如下所示:

S1

S2'+S3'A2 A1

A0

Y7' Y6' Y5' Y4' Y3' Y2' Y1'

Y0'

0 x x x

x

1

1

1

1 1 1 1 1

x 1x x

x

1

1

1

1 1 1

1

1

1 0 0 0

1

1

1

1 1 1

1

1 00 0

1

1

1

1

1 1 10 1

1 00 1

1

1

1

1 1 0

1

1

0 1 1 1 1

1 0 1 1 1 0 1 1

1 01 0

1

1

1

0 1 1

1

1

1 01 0

1

1

1

1 1 1 1 1

1 01 1

1

1

1 1 1

1

1

1 01 1

1

1

1

1 1 1

1

1

二、七段显示译码器的VHDL设计(共阳极)

1.实体框图

2.程序设计

①正确的程序

library ieee;

use ieee.std_logic_1164.all;

entity disply_decoder is

port(A:in std_logic_vector(3 downto 0);

DOUT:out std_logic_vector(6 downto 0));

end disply_decoder;

architecture aaa of disply_decoder is

begin

with A select

dout<="0000001" when "0000",

"1001111" when "0001",

"0010010" when "0010",

"0000110" when "0011",

"1001100" when "0100",

"0100100" when "0101",

"0100000" when "0110",

"0001111" when "0111",

"0000000" when "1000",

"0000100" when "1001",

"1111111" when others;

end aaa;

3.仿真波形图

4.仿真波形分析

由真值表可以看出:

字形

输入 输

出

D C B A a b c d e f

g

0 0 0 00 0 0 0 0 0

1

1

0 0 0 11 0 0 1 1 1

1

2

0 0 1 00 0 1 0 0 1

0 0 1 10 0 0 0 1 1

3

4

0 1 0 01 0 0 1 1 0

0 1 0 10 1 0 0 1 0

5

6 0 1 1 00 1 0 0 0 0

7 0 1 1 10 0 0 1 1 1

1

1 0 0 00 0 0 0 0 0

8

9 1 0 0 10 0 0 0 1 0。