基于CPLD的PowerQUICC与工业现场总线接口

基于 CPLD 的计算机接口电路设计技巧

基于CPLD的计算机接口电路设计技巧郭志友孙慧卿华南师范大学光电子材料与技术研究所广州 510631摘要:本文介绍了利用计算机ISA、PCI总线和打印机接口设计密码电路。

基于CPLD 设计密码电路,具有加密性能好的特性。

通过并行打印机接口设计一个密码电路,密码存储在电路中,通过操作接口读取密码。

ISA总线可以直接读取电路密码,PCI总线可以通过W89C940af对密码电路进行操作,读取设置密码。

关键词:计算机密码电路ISA和PCI总线Dsigned Skill of Computer Interface Circuit Based on CPLDGuoZhiYou SunHuiqing(South China Normal University of School for Information and Optoelectronic Science and Engineering, Guangzhou 510631, China)Abstract: The paper proposes a password circuit that by using computer ISA and PCI bus and printer interface. A password circuit is designs by using CPLD. Its characteristic is very secure. Using serial printer interface designs a circuit of password deposited in circuit. The circuit may read and get passwords. ISA buses read and get passwords directly. PCI buses may be manipulated by W89C940af in order to read and get and set passwords.Key words: computer; password circuit; ISA and PCI buses1 引言随着计算机CPU的运行速度在不断提高,至今已经到约2GHz,基本内存也达到了1M~512M,给计算机的应用软件运行提供了较好的运行条件,同时也足金促进了计算机软件的发展。

基于cpld的内燃机车逻辑控制模块的设计

随着社会的发展,内燃机车在工业界有着广泛的应用。

然而,由于其复杂的控制系统,传统的控制方式往往低效、费时费力,严重影响了内燃机车的运行状况和使用寿命。

为了解决这个问题,将CPLD应用于内燃机车的控制中,开发出一套逻辑控制模块。

CPLD(Complex Programmable Logic Device),是一种复杂的可编程逻辑器件,可以实现复杂的逻辑功能,比单片机更加灵活。

由于其具有较强的可编程性,可以实现内燃机车控制系统的实时性和稳定性。

在CPLD的应用中,可以采用分析、模拟和控制等多种技术来设计各种控制系统,从而实现内燃机车控制的自动化和可靠性。

例如,使用分析技术,可以根据内燃机车的运行情况,对控制系统进行实时分析,并及时采取措施;使用模拟技术,可以模拟内燃机车的运行情况,模拟出各个系统的工作状态;使用控制技术,可以根据模拟得到的结果,实时调整内燃机车的运行状态,实现自动化控制。

通过这一套逻辑控制模块,可以提高内燃机车的运行效率,提升运行安全性,提高维护效率。

此外,CPLD技术还可以实现故障诊断,排除故障,同时可以改善内燃机车的控制精度,实现高精度的控制。

总之,基于CPLD的内燃机车逻辑控制模块的设计,可以有效提高内燃机车的性能,提高内燃机车的可靠性和安全性,为内燃机车的发展提供了重要的技术支持。

基于CPLD的PLC背板总线协议接口芯片设计

Ke r s b c o a k u ;rtc l hp ;o lx po a b l lgc e ie ( P D)p ga b l lgc o — y wo d :a k t b c b spooo c is c mpe rg mma e o i r d vc C L ; rr mma e oi c n o

t l r P C) r l (L oe

可 编程逻 辑控制 器 ( L P C 主机是 通过背 板 总线 支持扩 展模块 的连接 .背 板总线 是 P C主机 同 I L / O

网等 . 般来说 . 多作 为 P C主 芯 片 的单 片 机 自 一 很 L 身 都集 成 了这些 外 设 部件 但 是单 片 机 内 部 集成

d ti fho t d sg sae eal w o o ei n tt ma hn c ie, fa o t l r a d rme c n r l o e n FI FO c ntolr n o r l i Ve io HDL a g a e s de c ie i e rl g ln u g i s rb d n te ril .Th sa e h a t e c e tbl wo k ef r a e f p oo o c p i 2 r p rom nc o r tc l his n 5MHz r v d ha he e i i fa i l. p o e t t t d sg s e sbe n

Hale Waihona Puke 2 0 9 , hn ;.h n h iEe tc p rts R sac n tueGru ) o,t. h n h i2 0 6 , hn ) 0 0 3 C ia2 a g a lcr a Ap aau ee rh I stt( o p C .Ld, a g a 0 0 3 C ia S il i S

CPLD模块及接口说明

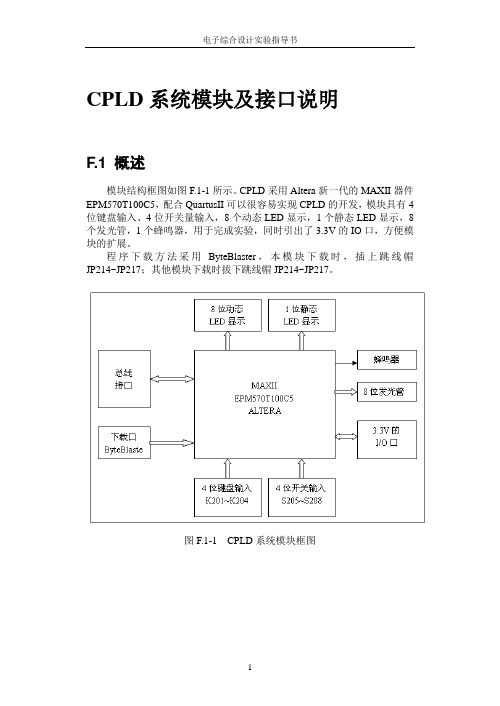

CPLD系统模块及接口说明F.1 概述模块结构框图如图F.1-1所示。

CPLD采用Altera新一代的MAXII器件EPM570T100C5,配合QuartusII可以很容易实现CPLD的开发,模块具有4位键盘输入、4位开关量输入,8个动态LED显示,1个静态LED显示,8个发光管,1个蜂鸣器,用于完成实验,同时引出了3.3V的IO口,方便模块的扩展。

程序下载方法采用ByteBlaster,本模块下载时,插上跳线帽JP214~JP217;其他模块下载时拔下跳线帽JP214~JP217。

图F.1-1 CPLD系统模块框图F.2 电路说明F.2.1 ByteBlasterⅡ下载电路本模块的ByteblasterII下载电路图如图F.2-1,通过25针计算机并口进行。

整个实验箱系统共有3块FPGA/CPLD模块,均通过本模块ByteblasterII 口进行程序下载。

注意:本模块下载程序时,插上JP214~JP217跳线帽。

其他模块通过本ByteblasterII口下载程序时,拔下JP214~JP217跳线帽。

图F.2-1 ByteblasterII下载电路图F.2.2 数码管驱动缓冲电路MAXII器件为低电压器件采用3.3V供电,一般采用一级缓冲和5V的外设相连接。

图F.2-2给出数码管驱动缓冲电路。

8位动态数码管的段由U202驱动,位由U203驱动。

1位静态数码管由U204驱动。

图F.2-2数据缓冲电路F.2.3 键盘、开关量输入及发光管显示本模块设有4位键盘输入(也可由跳线JP206~JP209选择TP201~TP204输出,见表F.3-9),4位开关量输入及8位发光管输出。

键盘输入为负脉冲。

图F.2-3键盘、开关量输入及发光管电路F.3 接口说明F.3.1 总线接口(JT201)总线接口JT201定义见表F.3-1。

F.3.2 键盘输入接口(K201~K203)表F.3-2是键盘K201~K204接口表。

CPLD基本结构

CPLD的基本结构1.基于乘积项的CPLDCPLD (Complex Programmable Logic Device)直译的话称为复杂可编程逻辑芯片。

它也属于大规模集成电路LSI (Large Scale Integrated Circuit)里的专用集成电路ASIC (Application Specific Integrated Circuit).适合控制密集型数字型数字系统设计,其时延控制方便。

CPLD是目前集成电路中发展最快的器件之一。

结构C PLDPLD即programmable logic device,译为可编程逻辑器件,是一个可以产生任意逻辑输出的通用型数字逻辑电路器件。

PLD有很高的集成度,足以满足设计一般的数字系统的需要,与门、或门、非门是PLD最基本的构成.的结构是基于乘积项(Product-te rm)的,现在以Xilinx公司的XC9500XL 系列芯片为例介绍CPLD的基本结构,如图1所示,其他型号CPLD的结构与此非常类似.CPLD可分为3部分:功能模块(Functi ON Block)、快速互连矩阵(FastCON NEC T ⅡSwitch Matrix)和I/O控制模块。

每个功能模块包括可编程与阵列、乘积项分配器分配器是有线电视传输系统中分配网络里最常用的部件,用来分配信号的部件。

它的功能是将一路输入信号均等地分成几路输出,通常有二分配、三分配、四分配、六分配等. 有线电视网的频率不断提升,功能不断加强,因此对分配器的要求不断提高。

在接口设备上分配器是将音视频信号分配至多个显示设备或投影显示系统上的一种控制设备。

它是专门分配信号的接口形式的设备。

[全文]和18个宏单元,功能模块的结构如图2所示。

快速互连矩阵负责信号传递,连接所有的功能模块。

I/O控制模块负责输人输出的电气特性控制,比如可以设定集电极开路输出、三态输出等。

图1中的I/O/GCK,I/O/GSR,1/0/GTS 是全局时钟、全局复位和全局输出使能信号,这几个信号有专用连线与CPLD 中每个功能模块相连,信号到每个功能模块的延时相同并且延时最短.图1 基于乘积项的CPLD内部结构图2 功能模块的结构宏单元是CPLD的基本结构,由它来实现基本的逻辑功能。

基于CPLD的ARINC429总线接口系统设计

基于CPLD的ARINC429总线接口系统设计屈凌翔;单悦尔;杨兵【摘要】文章首先简单介绍了ARINC429航空总线的应用背景和总线传输协议的基本内容.然后根据ARINC429航空总线标准的要求,提出一种基于ACTEL公司CPLD的透明数据传输系统方案.在QUARTUS Ⅱ和MODELSIM的设计平台上,该系统成功实现12路ARINC429信号接收和4路ARINC429信号发送的功能,每个通道都包括32×8的数据FIFO,ARINC429字长为32位,主机接口采用16位,429数据速率支持12.5 kbps与100 kbps,数据传输实时可靠,能较好地满足ARINC429通信系统的要求.该电路系统采用正向设计,Verilog HDL硬件语言描述,ACTEL公司A3P250VQG1001实现,规模十四万门左右,采用VQFP100封装,双电源设计,功耗低至0.4W,能较好地满足工业级电路系统低功耗的设计要求.【期刊名称】《电子与封装》【年(卷),期】2010(010)009【总页数】5页(P24-27,48)【关键词】ARINC429总线;接收发送系统;透明传输;复杂可编程逻辑器件【作者】屈凌翔;单悦尔;杨兵【作者单位】中国电子科技集团公司第58研究所,江苏,无锡,214035;中国电子科技集团公司第58研究所,江苏,无锡,214035;中国电子科技集团公司第58研究所,江苏,无锡,214035【正文语种】中文【中图分类】TN402ARINC429数据总线是美国航空无线电公司制定的一种民用航空标准数据总线。

它作为波音、空中客车、麦道等飞机上机载计算机及导航设备之间信息交联的主要总线,在我国民用、军用飞机上也被普遍采用。

通常ARINC429总线数据传输的接口电路设计都是采用专用芯片实现的,这就使接收发送的通道数量和储存数据的缓存受到限制,并且价格昂贵,尤其不适用于需要备份关键数据的系统。

本设计利用CPLD内部丰富的资源,可以增加数据通路,并且使存储容量得到很大提高,同时有效地缩小系统体积,降低成本。

基于CPLD的ARINC429总线接口系统设计

( hn l t n c n l yG op C roain o5 ee r s tt W x 2 4 3 ,h a Ci aEe r i T hoo ru o rt N .8 sac I tu , u i 10 5C i ) co c e g p o R hn i e n

A b t a t Thep pe n r d c st ea plc to a k r u f sr c : a ri to u e h p iai n b c g o nd o ARI C4 usa d t s o tn ft e N 29b n heba e c n e to h

te ei P 5 V G10 f C E , hc c d s 0 o sn a s n ak gdb Q 0 h h vc A3 2 0 Q I A T Lw i i l e 0 h uad t dipce e V GI . e d e o 0 hn u 4 t g ea s y T O

第1 0卷, 9期 第

Vo 1 1 0, N O 9

.

电 子

与

封

装

.

ELECTRON I CS & P ACKA GI G N

总 第8 9期 2l O 0年 9月

、

Hale Waihona Puke l 0 ,_0计 屯 路; | _ 设

基于 C L P D的 AR NC 2 总线接 口系统设计 I 49

p o o o . e c e fata s a e t aata s s ins se i c o d n ewihAR1 r t c 1Th nas h meo n p r n t n miso y tm na c r a c t NC4 u tn ad r d r 29b ssa d r

基于CPLD的单片机之间的通信接口设计

本 设计 利用 MA X+pu Ⅱ开发 软件 , 通信 控制 ls 在

板 上用 E 1 0芯 片设计 了一个 三 通道 F F 存 储器 P K3 IO

阵列 , 过复 用方 式 分别 与 通 信控 制 板 和 有线 传输 板 通 上 C8 5 F 2 0 1 0 0单 片机 的 总线 系统 连 接 , 通 信控 制板 使

可 以通 过单 片机 总线 与 3 有线 传输 板进 行高 速数据 块

输 出端 口

通 信 , 两 块 E 1 0芯 片可 与 6块 有 线 传输 板 进行 用 P K3 高速 数据通 信 。

2 F F 存 储 器 阵列 的设 计 IO

本设 计 采用 了 自下 向上 的 层 次化 设 计 方法 , 底 在 层 设计 中 , 图形 编辑 输 入 法 设 计 双 向 F F 存 储 器 用 IO 模块 、 语 言 描述 输人 法 设计 了与 有 线传 输 板 接 口的 用 单 路 逻 辑 端 口和 与 通 信 控 制 板 上 C 0 1 0 0单 片 机 8 5F 2

旭

000) 3 0 6

厦 f 31 0 ,. 方 自动 控 制 技 术 研 究 所 , 原 - 6052 北 I 太

摘 要 : 绍 了 AL E 介 T RA 公 司 C L 器 件 E I 0芯 片 的特 点 , 用 M AX+p u P D P K3 利 lsⅡ开 发 软 件 在 E 1 0芯 片 上 设 计 了 一 个 P K3

接 口的多路 逻辑端 口等 3个 功能模 块 ; 在顶 层设计 中 ,

表 2 L M— I O D P F F — C存 储 器 读 写 操 作 逻 辑

直 接调 用 了 3 双 向 F F 存 储器模 块 、 个 单路 逻辑 个 IO 3 端 口和 一 个 多路 逻 辑 端 口, 过 逻 辑 组 合 组成 一 个 3 通 通 道 双 向 F F 存 储 器 阵列 , 现 了一个 C 0 1 0 0 IO 实 85F 2 单 片机 系统 与其 他 3个 C8 5 F 2 0 1 0 0单 片 机 系 统 之 间 的 总线 接 口, 于通 信 控制 板 与 3块有 线 传输 板 之 间 用 的实 时通 信 。

多总线与CPLD在水质监测中的应用

G M模 块 主要用 来 发送 短 信 给 维 护 工程 师 , S

当采 集到 的仪 表 开 关信 号 或者 参 数 信 号 有误 时 ,

即仪 表可 能损坏 时 , 通过 G M 模块 及 时地 群 发 给 S 相应 的工程 师 , 而 避 免 因 发现 不 及 时 而 造 成 的 从

CL P D逻辑 译 码 电路 和 复 位 电路 组 成 , n B sM A y u- 主站接 口模块通 过一 个 D R M 与外 部处 理 器相 PA

连, 通过 P 14对 D R M 的访 问来 实 现 主站 与 C0 PA

复位 电路

场 总 线 接

口

图 6 主 站 接 口框 图

中 图分 类 号

T23 P 7

文 献 标 识 码 B

文 章 编 号 10 —9 2 2 1 ) 8 9 50 0 033 ( 0 1 0 - 7 — 0 3

我 国是 一 个严 重 缺 乏水 资 源 的 国家 , 之 近 加

几年 , 随着工 业 的不断 发展 , 环境 恶化 问题 日趋 严

d 内置德 国西 门子公 司 G M 模 块 T 3 ; . S C 5

[ ] 刘韬 , 兴华 . P A数字电子系统设计与 开发实例 4 楼 FG 导航 [ . M]北京 : 民邮电 出版社 ,0 5 人 20 . [ ] 汤伟 , 庆瑜 , 5 戴 王孟 效等. 采用 Pob s 场总线 的 r u现 i f 碱 回收集成优化控制 系统 [ ] 化2 自动化及仪表 , J. 1 2

污染 严重 的后果 。笔 者采 用三 线制 串 口的 G 0 A 10

笔者 介绍 了一种 基 于多总 线水 质在 线监 测 的

【doc】基于CPLD技术扩展单片机IO口

基于CPLD技术扩展单片机IO口工程师笔记?基于CPLD技术扩展单片机10口CPLD是复杂可编程逻辑器件(ComplexProgrammableLogicDevice)的缩写,可编程逻辑器件是一种数字集成电路的半成品,在其芯片上按一定排列方式集成了大量的门和触发器等基本逻辑元件,使用者可利用某种开发工具对其进行加工,也就是说按照设计要求将这些片内的元件连接起来,我们称此过程为编程,使之完成某个逻辑电路或系统的功能,成为一个可以在实际电子系统中使用的集成电路.由于可编程逻辑器件引脚比较灵活,又有可擦除可编程的能力,因此对原设计进行修改时,只需要修改原设计文件,再对可编程逻辑器件芯片重新编程即可,而不需要修改电路布局,更不需要重新加工印刷线路板,这就大大提高了系统的灵活性,还有很好的保密性,同时在设计完成后可立即进行功能仿真,也可现场编程进行验证,有利于及早发现问题,完善设计.单片机是把中央处理器CPU,随机存取存储器RAM,只读存储器ROM,定时器/计数器以及I/O接口电路等主要计算机部件集成在一块集成电路芯片上的微型计算机.单片机又叫微控制器,具有体积小,功耗低,可靠性高,功能强,面向控制等特点,主要应用在控制系统中.使用单片机用软件取代硬件的控制技术,称之为微控制技术,随着单片机技术的发展和应用普及,微控制技术在智能化方面早已不是硬件控制所能比拟的,它带来了一场对控制技术的革命.单片机最大的优点在于控制能力强,最大的缺点是IO口少,而由于可编程逻辑器件有丰富,灵活的IO口,所以我们使用可编程逻辑器件来扩展单片机IO口,以弥补单片机l0口的不足.对于一些规模比较大些的电子系统,使用单片机+可编程逻辑器件(CPLD)技术是目前比较流行的技术和比较合理的方案....'函.i'函'..'''''..总体设计方案_-_-_--___-____--___-一一一--●---_______●__●一-_---_ :VCC:(b)I_-----___?.___.-_-..----._________一-一--_--._.-一图210口输入,输出电路本设计使用ALTER公司的可编程逻辑器件EPM7128LC84—1O来扩展单片机的IO口,单片机使用AT—MEAL公司的AT89S52,图1所示是总体设计框图.本设计有30个输出端口,由集成电屯早世界?2009.04一一幸坤涛路ULN2803驱动,以增加输出口的驱动能力,其中24个输出是24V输出口,用于驱动24V外设如汽缸,电磁阀,6个输出是5V输出口,用于驱动各种信号灯.还有16个输入端口,其中8个24V输入端,用于检测24V传感器如汽缸霍尔传感器的输入,8个5V输入端用于检测光电开关的输八.可编程逻辑器件EPM7128和51单片机AT89S52间由数据端口DO~D7来进行数据传输,A13~A15配合RD或WR 信号,来控制是输入还是输出,是哪路输入或输出.上位机通过串口来对单片机控制,完成数据的控制与传输.硬件设计lO口输入,输出电路图2所示是l0口输入,输出电路,其中(a)是输入电路,左侧是24V输入端,通过三极管电平转换成5V,送到可编程逻辑器件EPM7128的输入端,右侧是5V输入端,直接送到可编程逻辑器件EPM7128的输入端,可编程逻辑器件EPM7128的输入端采集信号的变化.(b) 是输出电路,左侧是24V输出驱动,右侧是5V输出驱动.可编程逻辑器件EPM7128和51单片机AT89S52的接口电路EPM7128带有独立清零,预置,时钟和时钟使能控制的可编程宏逻辑单元触发器,附加带有反向功能的2个全局时钟信号,逻辑驱动输出使能信号等增强特性.EPM7128的I/O控制块允许每个I/O 脚分别设置成输入,输出或双向工作方式,所有的I/O脚都有一个三态缓冲器,它由全局输出使能信号中的一个控制,或者把使能端直接连接到地(GND)或电源(VCC)上.当三态缓冲器的控制端接地(GND)时,输出为高阻态,此时,I/O引脚可用作专用输入引脚.当三态缓冲器的控制端接电源(VCC)时,输出被使能(即有效).另外,每个寄存器的复位功能可以由低电平有效的,专用的全局复位引脚GCLRn信号来驱动.图3所示是可编程逻辑器件EPM7128和51单片机AT89S52的接口电路,我们将2个输出使能端OE1,0E2(EPM7128的84,2脚)及复位端GLCR(EPM7128的1脚)接电源(VCC),使输出使能,计数不清零,由软件控制清零.AT89S52的14,15脚外接晶振和电容组成单片机的振荡电路,4脚是复位端, 由lPM810控制,IPM810具备上电复位, 手动复位及欠压复位功能.AT89S52使用PLCC44脚封装的贴片器件,利用单片机AT89S52的P1口和复位口进行在线编程,使用at89isp软件在线编程,进行程序的烧写.EPM7128的83脚是全局时钟,外接工作用的时钟信号,这个时钟信号可以使用有源晶振来产生,也可以使用无源晶振加振荡器产生.EPM7128的14,71, 23,62脚分别是TDI,TD0,TMS,TCK端,是jtag编程口.EPM7128也是采用在线编程方式进行程序的烧写,采用jtag在线编程.本设计中可编程逻辑器件EPM7128和51单片机AT89S52共有13根线相连,进行数据通讯和控制,其中,DO~D7是数据通讯,A13~A15,RD,WR是控制信号.软件设计本系统中ALTERA公司可编程逻辑器件EPM7128的内核程序采用VHDL 硬件描述语言编写,使用MAX+plusll1O.1编译系统或QuartusII4l2编译系统编译.VHDL的全称为VHSIC(V eryHigh SpeedIntegratedCircuit)HardwareDe—scriptionLangunge,中文译为甚高速集成电路的硬件描述语言.51单片机AT89S52用C语言编程,使用KeilC51 编译系统编译.可编程逻辑器件EPM7128的软件工程师笔记?可编程逻辑器件EPM7128的软件代码如下:libraryieee;useieee.std—logic一1164.all;useieee.std——logic——arith.all;useieeestd——logic——unsignedall;entity10MU×isport(WR:instd—logic;RD:instd—logic;ADDR:instd~logic_vector(2downto0):DATA(7downtoO):D0UTdowntoO):noutstd—logic_vectoroutstd——logic——vector(31DIN:instd—logic_vector(15downto0)):end;一一ADDR(2)iSA15图3可编程逻辑器件EPM7128和51单片机AT89S52的接口电路屯子世界?2009.04工程师笔记?一一ADDR(1)isA14一一ADDR(0)isA13architecturebehaverofIOMUXissignalDoutEn:STD—LOGICECTOR(3downtoO):signalDinEn:STD—LOGICVECTOR(1downto0):begmPR0CESS(WR,RD,ADDR,DA TA, DlN)beginIf(WR=.^.0)thenIf(DoutEn(3)='1.)thenDOUT(31downto24)<=DATA(7downtoO):eIsIf(DoEn(2)='1.)thenD0UT(23downto16)<=DATA(7downtoO)elsif(DoutEn(1)=1')thenDOUT(15downto8)<=DATA(7downto0):elsif(DoutEn(0)=1.)thenD0UT(7downto0)<=DATA(7downtoO):endif:elsif(RD=.0)thenif(DinEn(1)='1)thenDA丁A(7downto0)<=DIN(15downto8):elsif(DinEn(O)='1.)thenDATAf7downto0)<=DIN(7downtoO):endif:elseDA1.A(7downto0)<:"ZZZZZZZZ":endif:endPROCESS;DoutEn(3)<=ADDR(2)andADDR(1) andADDR(0);DoutEn(2)<=ADDR(2)andADDR(1) and(notADDR(0));DoutEn(1)<=ADDR(2)and(notAD—DR(11)andADDR{0};DoutEn(0)<=ADDR(2)and(notAD—DR(1))and(notADDR(O)):DinEn(1)<=ADDR(2)and(notADDR (1))DinEn(0)<=ADDR(2)andADDR(1): endbehaver;在上述代码中,需注意的是ADDR(2),ADDR(1),ADDR(0)的逻辑组合一定要和单片机中读取外部存储器的的定义是一致的.如DoutEn(3)=111O,对应的51单片机AT89S52软件中的定义是#define OUTPUT_DATA4XBYTE【0xE000].当单片机发出输出命令时,CPLD收到WR写信号,再根据单片机的A13~A15信号,决定是哪路输出.当单片机发出查询输入命令时,CPLD收到RD信号,再根据A15, A14信号决定读取哪路信号,最后送到单片机.51单片机AT89S52的软件在单片机AT89S52中读取外部存储器的的定义如下,需要和可编程逻辑器件EPM7128中的ADDR(2),ADDR(1), ADDR{0)的逻辑组合一致.#defineOUTPUTDATA1XBYTE【0x8000】#defineOUTPUTDATA2XBYTE【0xA000】#defineOUTPUTDATA3XBYTE【0xC0001#defineOUTPUTDATA4XBYTE【0xE0001#defineJNPUTDATA1XBYTE[0x8000】#defineINPUTDATA2×BYTE【0xC000】在主程序中使用查询法不断给出调用读取输入Readlnput()函数,来查询16 个传感器中的任一个是否发生变化,根据不同的传感器的输入,来调用相关的输出函数.同时在串口中断程序中根据上位机的数据命令,发出调用组控制或单点控制命令.51单片机AT89S52的部分代码如下组控制下面的函数可以实现对3O个输出口的同时操作,outdata中为1的位,EPM7128输出1;反之,输出0. voidGroupOutput(unsignedlong outdata){uchartempl,temp2,temp3,temp4;屯子世界?2009.042g——OutputStatus=outdata;templ=OutputStatus&0xff;temp2=(OutputStatus>>8)& Oxff;temp3=(OutputStatus>>16)& 0xff;temp4=《OutputStatus>>24)& 0xff;OUTPUT—DATA1=templ: OUTPUTDATA2=temp2; OUTPUTDATA3=temp3;OUTPUT_DATA4=temp4;)单点控制下面的函数可以对30个输出口的某一个口单独控制,OutNo是某个输出口的端口号,state是0或1状态, state为1,EPM7128输出1反之,输出0ovoidSingleOutput(ucharOutNo, ucharstate){unsignedlongtemp;temp=1temp<<=OutNo;if(state==1)temp=tempIOutputSta-tus;elsetemp=(~temp)&Output—Status;GroupOutput(temp);)读取输入下面的函数是读取16个输入口的状态,根据读取的数值,可以判断是哪个传感器有信号变化.51单片机AT89S52使用查询法不断判断是否有传感器的信号变化,以执行某个动作. uintReadInput(void)fuInttemp;uchartempl,temp2;templ=lNPUT_DATA1:temp2=lNPU[DATA2;temp=templ+(temp2<<8/; returntemp;)。

用Verilog语言写的CPLD和MCU通讯的SPI接口程序

用Verilog语言写的CPLD和MCU通讯的SPI接口程序2010-04-12 21:32近日,在调试Altera的MAXII系列的一款CPLD,做了一个SPI接口同MCU通讯,MCU做主机通过SPI对CPLD做读写操作,经过测试验证,效果不错。

程序代码如下,独立模块,可以根据实际应用直接实例化使用。

说明: 代码中的"\* ... *\"注释不能在网页上显示出来,源文件可在链接博客中直接下载.*************************************************************************** spi** Filename : spi.v* Programmer: jose.huang* Project :* Version : V1.0* TOP MODULE: SpiModule.v* Describel : spi总线,数据移位处理模块;* 发送,接收均为8位数据;* 接收时,上升沿移入数据;* 发送时,上升沿来之前放上数据* 用于SPI从动模式* ************************************************************************* Date Comment Author Email TEL* 08-31 original jose.huang work_email@* ------- ----*************************************************************************** module spi (rst,clk,sdi,sdo,sck,cs,OData,IData,ReceiveFlag,TransFlag,TransEndFlag);input rst; // 异步清零input sdi; // spi data inputinput sck; // spi clk, MAX 25MHzinput cs; // spi enableinput clk; // cpld main clk,MIN 50MHzinput[7:0] IData; // Input 8bit Data want to transmit to mcuinput TransFlag; // 发送标志output reg sdo; // spi data outputoutput reg[7:0] OData; // Receive 8bit Data 命令字或数据output reg ReceiveFlag; // 收到8bit Data 标志output reg TransEndFlag; // 发送结束标志reg[2:0] CPLDPort;reg[2:0] TempPort;reg[2:0] BufferPort; // sampling CPLD IO Data to BufferPortreg[7:0] samplnum;always@(posedge clk)beginCPLDPort[0] <= sdi;CPLDPort[1] <= sck;CPLDPort[2] <= cs;endalways@(posedge clk or negedge rst)beginif(!rst) // 异步清零beginsamplnum <= 8'b0;endelse if(TempPort == CPLDPort)beginsamplnum <= samplnum + 1'b1;endelsebeginsamplnum <= 8'b0;TempPort <= CPLDPort;endendalways@(posedge clk or negedge rst)beginif(!rst) // 异步清零beginBufferPort[0] <= 1'b0; //CPLDPort[0] <= sdi; BufferPort[1] <= 1'b0; //CPLDPort[1] <= sck; BufferPort[2] <= 1'b1; //CPLDPort[2] <= cs;endelsebeginif(samplnum > 10) // set by cpld main clk and spi clk beginBufferPort <= TempPort;endelse BufferPort <= BufferPort;endendwire wsdi;wire wsck;wire wcs;assign wsdi = BufferPort[0]; //CPLDPort[0] <= sdi; assign wsck = BufferPort[1]; //CPLDPort[1] <= sck; assign wcs = BufferPort[2]; //CPLDPort[2] <= cs;// 计数reg[7:0] ShiftCounter;reg[7:0] ClrFlagCounter;reg Bwsck;always@(posedge clk or negedge rst or posedge wcs) beginif(!rst) // 异步清零beginShiftCounter <= 8'b0;ReceiveFlag <= 1'b0;TransEndFlag <= 1'b0; // shift状态清接收标志Bwsck <= 1'b0;endelse if(wcs) // 结束异步清零beginShiftCounter <= 8'b0;Bwsck <= 1'b0;if(ClrFlagCounter == 10)beginReceiveFlag <= 1'b0; // SPI操作结束清接收标志TransEndFlag <= 1'b0; // shift状态清接收标志endelse ClrFlagCounter <= ClrFlagCounter + 1'b1;endelsebeginBwsck <= wsck;ClrFlagCounter <= 8'b0;if(wsck && (!Bwsck)) // 上升沿处理beginif(ShiftCounter == 7)beginShiftCounter <= 8'b0;if(!TransFlag) // receive data from mcu ReceiveFlag <= 1'b1; // 收到8bit dataelseTransEndFlag <= 1'b1; // 发送完成endelsebeginShiftCounter <= ShiftCounter + 1'b1;ReceiveFlag <= 1'b0; // shift状态清接收标志TransEndFlag <= 1'b0; // shift状态清接收标志endendendend// 移位always@(posedge clk or negedge rst or posedge wcs) beginif(!rst)sdo <= 1'b0;else if(wcs)sdo <= 1'b0;else if(wsck && (!Bwsck)) //上升沿处理beginif(!TransFlag) // receive data from mcubeginOData <= {OData[6:0],wsdi};endelse // transmit data to mcubeginsdo <= IData[7-ShiftCounter];endendendendmodule波形图。

基于PCI总线的Power PC8245处理器嵌入式系统硬件的设计与实现

在 国 内 该 处 理 器 也 应 用 较 多 ,从 PowerPC6XX,Power⁃

存储器、NVSRAM 存储器、调试串口、输入/输出离散量

生产。由于其可升级性好,功耗低而应用最为广泛,同时

器、以太网和 PCI 设备也由外设逻辑直接控制,FLASHTM

based on PCI bus

FAN Jiangfeng,XU Lianbo,YE Bo,WANG Xudong

(AVIC Computing Technique Research Institute,Xi’an 710119,China)

Abstract:MPC8245 is a processor chip with high capability and low power consumption. It is integrated with MPC603E

收稿日期:2015⁃01⁃28

PCI_SYNC_IN 输 入 到 MPC8245,在 经 内 部 PLL 和 DLL

备使用。MPC8245 的 PLL 配置引脚为PLL_CFG[0..4],对

于 给 定 的 输 入 时 钟 SYSCLK,PLL 配 置 对 应 的 CPU 和

VCO 的操作频率,PLL 的配置时钟对应关系见图 3。

1.3

存储器电路设计实现

MPC8245 处 理 器 内 部 集 成 高 性 能 存 储 器 控 制 器 ,

Copyright©博看网 . All Rights Reserved.

樊江锋,等:基于 PCI 总线的 PowerPC8245 处理器嵌入式系统硬件的设计与实现

easily.

Keywords:PowerPC8245;processor;PCI;I2C controller

基于CPLD的数据采集与显示接口电路仿真设计

基于CPLD的数据采集与显示接口电路仿真设计黄崇富;李建华【摘要】常规数据采集与显示方法是应用CPU或DSP通过软件控制数据采集的模/数转换,这样将会频繁中断系统的运行,从而降低系统的运算速度,数据采集的速度也将受到限制.通过CPLD实现由硬件控制模/数转换和数据显示,最大限度地提高系统的信号采集和处理能力.这里运用VHDL硬件编程语言,通过状态机设计程序,完成A/D转换芯片与可编程逻辑芯片的接口.将A/D转换结果以BCD码形式通过CPLD芯片进行显示,实时观测转换进程,给出了BCD码转换流程图,完成相应电路设计,通过QuartusⅡ软件进行仿真,并在开发系统上成功实现功能验证,提高了系统的运算速度.【期刊名称】《现代电子技术》【年(卷),期】2009(032)024【总页数】4页(P147-150)【关键词】可编程逻辑器件;模数转换;二-十进制码显示;接口电路【作者】黄崇富;李建华【作者单位】重庆工程职业技术学院,重庆,400037;重庆工程职业技术学院,重庆,400037【正文语种】中文【中图分类】TP368.10 引言CPLD称为复杂可编程逻辑设计芯片,它是大规模可编程器件,具有高集成度、高可靠性、高速度的特点。

CPLD是利用EDA技术进行电子系统设计的载体。

硬件描述语言是EDA技术进行电子系统设计的主要表达手段,VHDL语言是常用的硬件描述语言之一;软件开发工具是利用EDA技术进行电子系统设计的智能化的自动化设计工具,常用开发工具有QuartusⅡ,Ispexpert,Foundation等。

CPLD 以高速、高可靠性、串并行工作方式等特点在电子设计中广泛应用。

它打破了软硬件之间的界限,加速了产品的开发过程。

同样单片机具有性价比高、功能灵活、良好的数据处理能力等特点。

CPLD芯片与单片机结合在高性能仪器仪表中应用广泛。

1 电路的仿真设计1.1 硬件电路功能用一片MCS-51芯片、一片CPLD/FPGA芯片、模/数转换器ADC0809和数/模转换器DAC0832构成一个数据采集系统[1,2],并用CPLD/FPGA实现数据采样、D/A转换输出、有关数据显示的控制,单片机完成对A/D转换数据运算。

用CPLD实现单片机与ISA总线接口的并行通信

用CPLD实现单片机与ISA总线接口的并行通信用CPLD实现单片机与ISA总线接口的并行通信摘要:介绍了用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104ISA总线接口之间的关行通信。

给出了系统设计方法及程序源代码。

关键词:CPLD ISA总线并行通信CPLD(Complex Programmable Logic Device)是一种复杂的用户可编程逻辑器件,由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确。

CPLD是标准的大规模集成电路产品,可用于各种数字逻辑系统的设计。

近年来,由于采用先进的集成工艺和大指量生产,CPLD器件成本不断下降,集成密度、速度和性能大幅度提高,一个芯片就可以实现一个复杂的数字电路系统;再加上使用方便的开发工具,使用CPLD器件可以极大地缩短产品开发周期,给设计修改带来很大方便[1]。

本文以ALTERA公司的MAX7000系列为例,实现MCS51单片机与PC104ISA总线接口的并行通信。

采用这种通信方式,数据传输准确高速,在12MHz晶振的MCS51单片机控制的数据采集系统中,可以满足与PC104 ISA总线接口实时通信的要求,通信速率达200Kbps。

1 系统总体设计方案用CPLD实现单片机与PC104ISA总线接口的并行通信,由于PC104主要完成其它方面的数据采集工作,只是在空闲时才能接收单片机送来的数据,所以要求双方通信的实时性很强,但数据量不是很大。

因此在系统设计中,单片机用中断方式接收数据,PC104采用查询方式接收数据。

系统设计方案如图1所示。

在单片机部分,D[0..7]是数据总线,A[0..15]是地址总线,RD和WR分别是读写信号线,INT0是单片机的外部中断,当单片机的外部中断信号有效时,单片机接收数据。

在CPLD部分,用一片MAX7000系列中的PM7128 ESLC84来实现,用来完成MCS51与PC104ISA总线接口之间的数据传输、状态查询及延时等待。

PXI模块触发总线接口的CPLD实现

今日电子 · 2007年4月FPGA 和PLD 特刊PXI 模块触发总线接口的CPLD 实现桂林电子科技大学电子工程学院 王朋 何锋引言PXI是PCI eXtension forInstrumentation的缩写,是为了将PCI总线扩展到测试仪器领域而推出的以PCI计算机局部总线为基础的模块仪器结构。

PXI相对于cPCI系统的一个重要特点是定义了8根触发总线,这可以实现系统中各模块间的同步和通信。

PXI触发总线规范PXI总线规范(PXI HardwareSpecification)的内容根据强制性的强弱,被分为三个等级,分别是:第一级是定则,第二级是推荐,第三级是容许。

根据PXI硬件规范的要求,本触发总线接口的设计实现了规范中所定义的如下定则和推荐。

定则1:上电复位时,PXI_TRIG[0:7]驱动线及驱动源必须保持为高阻状态,直到由软件配置为输入或者输出。

定则2:PXI_TRG[7:0]的I/O缓冲器应当遵循如表1所示的直流(DC)协议。

推荐1:接受或者发送触发信号的模块应该跟系统中别的7个模块互连,任何一个模块都可以作为触发信号的发送或者接受端。

推荐2:在触发应用中,如果一个模块接入某触发总线的子系统中,则它应该跟背板的PXI_STAR和PXI_TRG[0:n-2]管脚相连,这里n是触发总线的数目,第n-1根总线一般用来传输时钟信号。

推荐3:为了避免输入浮置,PXI模块的接口各触发总线输入端可以接一上拉电阻对其进行上拉。

推荐4:触发总线上的电平有可能是中间电平(Vol<V<Voh),为了避免电平处于中间电平波动时带来的误触发,触发信号的产生应当由施密特触发器来实现。

PXI触发接口实现原理图这里只给出一路触发总线实现的原理图,由于8路触发总线之间是独立工作的,因此,每一路都可以用同样的原理来实现,只是实际应用中,8路信号可以共用一些控制线而已。

一路触发总线接口的原理如图1所示。

图1所示,由N1、N2、R1、R2组成了门电路施密特触发器,其原理图如图2所示。

用CPLD实现基于PC104总线的429接口板

用CPLD实现基于PC104总线的429接口板

PC104总线系统是一种新型的计算机测控平台,作为嵌入式PC的一种,在软件与硬件上与标准的台式PC(PC/AT)体系结构完全兼容,它具有如下优点:体积小、十分紧凑,并采用模块化结构,功耗低,总线易于扩充,紧固堆叠方式安装,适合于制作高密度、小体积、便携式测试设备,因此在军用航空设备上有着广泛的应用,但也正是PC104板的这种小尺寸结构、板上可用空间少给设计带来了一定的困难,所以本设计采用了复杂可编程器件CPLD,用CPLD完成了PC104总线与429总线通讯的主要电路,大大节省了硬件资源,本文着重介绍了CPLD部分的设计。

1 系统总体设计

CPLD是一种复杂的用户可编程逻辑器件,由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确。

再加上使用方便的开发工具,如MAX+PLUSII、Quartus等,使用CPLD器件可以极大地缩短产品开发周期,给设计修改带来很大方便。

本论文描述了利用开发工具MAX+PLUS II实现CPLD处理ARINC429数据通信。

系统设计方案如ARINC429收发电路部分,由两组3282和3l82芯片构成,其中每组芯片实现二路接收、一路发送,其中的控制信号均有CPLD编程产生:在CPLD部分,D[0...15]为16位双向数据总线,实现AR1NC429收发电路与PC104总线接口之间的数据通信,IO16为16位芯片选择信号;在PC104总线接口部分,XD[0...15]为16位双向数据总线,XA[1...9]为地址总线,连接CPLD,进行选片操作,XIOR和XIOW 为IO读写信号,XAEN 是允许DMA控制地址总线、数据总线和读写命令线进行DMA 传输以及对存储器和I/O设备的读写。

2 系统硬件组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

lA S I C N EIO O Y IFF l 8 2o N C N EA D TCC L G No a 即. 6 E . W 0

维普资讯

纂 C P

P we Q I C与工业现场总线接 口 o r UC

p o ie r v d d. i i r v n b e p rme t t a t e t s o e y x ei ns h t h p

S Al( 作 为 C N总线协 议控制 器 , J (0 ) 】 A 同 时采用 C L 器件完 成 C U 中断 与 片 P D P 选扩展 、现场总线接 F逻辑、专用安全 I I O总线扩展等功能。主机系统原理结 / 构 框 图如 图 1 示 。 所 其 中的安 全 I O总线是 一种 工业专 / L 其进一步应 用造 成了很大障碍 。而复 用测控总线 ,也 由 CP D 内部实现它 P 杂 可 编 程 逻辑 器件 ( CPLD )为解 决 与 C U总线之间的桥接逻辑 ,本文不 这 一 问题 、建立 3 嵌 入式 微 处理 器 2位 再赘 述 。 与 现场总 线控 制 器的 接 F逻辑 提供 了一 I 种 简便有效 的可靠途径 。

1 引 言 现 场总 线 ( ed u )是 应 用在 Fil b S

B S H 公 司推 出 ,是 一种 在 工业控 制 O C 和汽车 电子领域广为采用的现场总线 。

接 口特 点 , 使 用 复 杂 可 编 程 逻 辑 器 件

(P D C L )设 计 C U总 线 与 C N控 制 嚣之 问 的 接 P A

器作为 核 心 、基于 CAN 现场 总线 的工

业 分布式 控 制系统 ( ) D C S ,使用

n h AN i u r tc lc n rlr a d d s s h i t e C f b s p oo o o toe n ein te 喇 l g

I I c ci o h nefc ew e P u ad o c i u f t I rae bt en C U Is n g r t e t b

一。ຫໍສະໝຸດ 现场总 线;P DsA 0 ;A C L ;J 1 0c N控制嚣 0

T e f l u hs cmpe e s e Ue i te n uty a d h id s a o rh ni s n h i s r n【 eb v d

t& s o s t n o to s s e . f i r o ie t r np r a l c n r l y t ms o t s e ur d O

,

d s n h n e f c b t el i d u a d 2 gs ei t e It r a e e we n e b s n【5 -b g f l

e e d d irp o es r h t d e n t u P r fe mb d e m co r c so t a o s o s p o ' il ; d bs T i p p r a a zs te ca a tr t f i ef c u . h a e n l e h h r ce i i o n ra e s y sc S

随着科技进步和计算需求的提高 , 在工业控制系统中正越来越多地应用高 性 能的 3 2位嵌 入 式 微 处理 器 ,以构 建 专用 工业 计算 机来 代替 传统 的通 用 工控 机。然而很 多嵌入式 微处理器尽管性 能较高 、通讯接 F丰富 ,但并 不一定 I 具 备现场总线控制 接 口,无法直 接连 接 现 场 总 线 或 现 场 总 线 控 制 器 , 这 为

teC N cnrlr bsdo te P D (op x h A otoe ae n h l I C L C m l e Porm al Lg ei ) h s u trw vfr r am b oi Dv e.Te i li1 aeom g e c c m ao

o t e i ig n t e r e s r e l m O a e f h tm n a d h d i r i v I at e S r r i

薛维清 何军 北京 交通 大学电子信息工程 学院 10 4 04 0

现 场总 线在工业 与交通控制 系统 中有着广 泛

应 用,对于不支持现 场总线的 5 2位嵌入 式微 处理 器 ,必须 专 门 设计 其 与 现 场 总 线的 接

口 。 本 文 分 析 了CA 协 议 现 场 总 线控 制 器 的 N

荔 序逻辑 ,给 出 了 真 波形 ,并编制 嵌入 时 仿

式实时操作 系统下 的驱 动程 序 ,实 际试 验证

明其运 行稳 定可靠 ,实现 c U与现场 总 线 P

控 制 器问的 无缝 连接

生 产现场、在数字化测控 设备之 间实 它 的传输 采用短帧格式 ,受干扰概率 现 双 向 串行 多 节点数 字通 信 的底 层控制 低 ,当总 线 上 有 节 点 错 误 时 , 能 够 自 网络系统。它在工业 、交通等方面 的 动 关 闭 , 切 断 其 与 总 线 的 联 系 。 Phi i 司的 CA N 总 线 控 制 器 l S公 P 自动化 系统 中具 有广 泛的应 用前 景 , / 0 0 ei AN ( 扩展 是 当 今 自动 化 领 域 技 术 发 展 的 热 点 之 S A1 0 是一款支持 P lC AN 工 作模 式 )独 立 C AN 总 线 协议 目前 有 几 种 现 场 总 线 技 术 已在 一 C 些特定应用领域显示 出其优势并形成一 控 制 芯 片 , 目前 应 用 十 分 广 泛 。 对 于一 个 以 P weQ C I o r UI C I处理 定影响力。