数电基本逻辑电路

数电讲义--2章

1.0

VOL(max)0.5

输入标 准低电

平

0.4V

VNL

D VNH

E

V V 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

SL VOFF VON

SH

Vi (V)

输入标准

高电平

2. 输入特性

+VCC

1) 输入伏安特性

iI

R1 3kΩ

1

-1.6 mA

<50 uA vI A

31

B

T1

1.4 V

和边沿,T4放大。 VO随iOH变化不大。 当由i于Oi以OHH受↑:线时功性,R耗变4上的化压限。降制增,大i0,H过T大3 、会T4烧饱毁和T,4管V,O随所

功耗 1mW IOH 400 A

输出高电平时的扇出系数 3.6V

R2 750Ω 2T3 Vc2 1 3 R4

VO

+VCC

R 4 +5V 100Ω

抗干扰能力越强。 高电平噪声容限

VNH= VSH ¯ VON 。

VNH越大,输入为1态下

抗干扰能力越强。

Vo (V)

4.0 A B

3.5

3.0

VOH(min)2.5 2.4V

C

2.0

1.5

A(0V, 3. 6V) B(0.6V, 3.6V) C(1.3V, 2.48V) D(1.4V, 0.3V) E(3.6V, 0.3V)

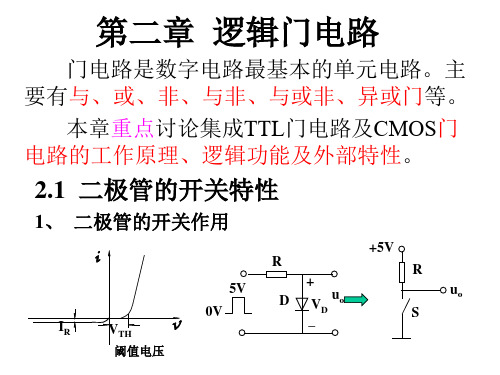

• 导通(VD>VTH) • 2、二极管的开关时间

截止5V(VDR<VT+H)

0V

D VD

uo

_

VF Vi

二极管开关状态的转换需要时间:

t1 t2

《数字电子技术基础》第五版:第四章 组合逻辑电路

74HC42

二-十进制译码器74LS42的真值表

序号 输入

输出

A3 A2 A2 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9

0 0 000 0 111111111

1 0 001 1 011111111

2 0 010 1 101111111

3 0 011 1 110111111

4 0 100 1 111011111

A6 A4 A2

A0

A15 A13 A11 A9

A7 A5 A3

A1

I7 I6 I5 I4 I3 I2 I1 I00

S

74LS 148(1)

YS

YEE Y2 Y1

Y0

XX

I7 I6 I5 I4 I3 I2 I1 I0

S

74LS 148(2)

YS

YE Y2 Y1

Y0

X

&

G3

&

G2

&

G3

Z3

Z2

Z1

&

G3

0时1部分电路工作在d0a1a0d7d6d5d4d3d2d1d074ls153d22d20d12d10d23d21s2d13d11s1y2y1a1a0在d4a0a1a2集成电路数据选择器集成电路数据选择器74ls15174ls151路数据输入端个地址输入端输入端2个互补输出端74ls151的逻辑图a2a1a02274ls15174ls151的功能表的功能表a2a1a0a将函数变换成最小项表达式b将使能端s接低电平c地址a2a1a0作为函数的输入变量d数据输入d作为控制信号?实现逻辑函数的一般步骤cpcp000001010011100101110111八选一数据选择器三位二进制计数器33数据选择器数据选择器74ls15174ls151的应用的应用加法器是cpu中算术运算部件的基本单元

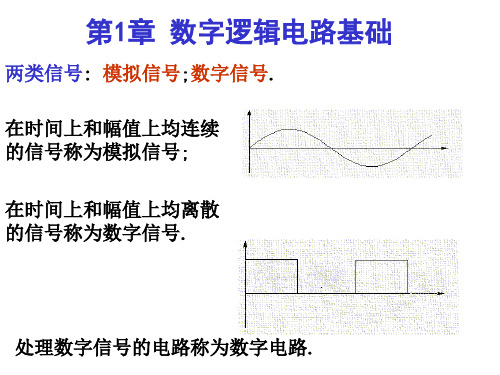

数电 第1章 数字逻辑电路基础

两类信号: 模拟信号;数字信号. 在时间上和幅值上均连续 的信号称为模拟信号; 在时间上和幅值上均离散 的信号称为数字信号.

处理数字信号的电路称为数字电路.

数字电路特点:

1) 工作信号是二进制表示的二值信号(具有“0”和“1”

两种取值);

2) 电路中器件工作于“开”和“关”两种状态,电路的输

与逻辑电路

若将开关断开和灯的熄灭状态用逻辑量“0”表示;将开关 合上和灯亮的状态用逻辑量“1”表示,则上述状态表可表 示为:

A 0 0 1 1 与逻辑真值表 B F=A ·B 0 1 0 1 0 0 0 1

A B

&

F=AB

与门逻辑符号

与门的逻辑功能概括: 1)有“0”出“0”; 2)全“1”出“1”。

非逻辑电路

•

与门和或门均可以有多个输入端.

1.3.2

复合逻辑运算

1. 与非逻辑 (将与逻辑和非逻辑组合而成)

与非逻辑真值表 B F=A ·B 0 1 0 1 1 1 1 0

A 0 0 1 1

A

&

B

F=AB

与非门逻辑符号

2. 或非逻辑 (将或逻辑和非逻辑组合而成)

A 0 0 1 1 或非逻辑真值表 B F=A +B

表示二进制数的方法有三种,即原码、反码和补码

符号位(+)

真实二进制数

B6 B 5 B4 B3 B2 B1 B0 1 0 1 0 0 1 1 =-4510

符号位(-)

补码

用补码系统表示有符号数

1.3.3

+9 +4

补码系统中的加法

0 1001 (被加数) 0 0100 (加数) 0 1101 (和=+13)

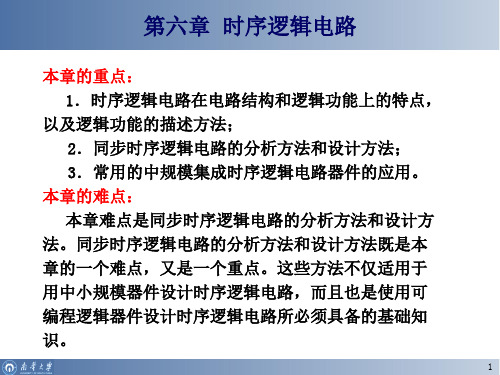

数字电子技术基础-第六章_时序逻辑电路(完整版)

T0 1

行修改,在0000 时减“1”后跳变 T1 Q0 Q0(Q3Q2Q1)

为1001,然后按

二进制减法计数

就行了。T2 Q1Q0 Q1Q0 (Q1Q2Q3 )

T3 Q2Q1Q0

50

能自启动

47

•时序图 5

分 频

10 分 频c

0

t

48

器件实例:74 160

CLK RD LD EP ET 工作状态 X 0 X X X 置 0(异步) 1 0 X X 预置数(同步) X 1 1 0 1 保持(包括C) X 1 1 X 0 保持(C=0) 1 1 1 1 计数

49

②减法计数器

基本原理:对二进 制减法计数器进

——74LS193

异步置数 异步清零

44

(采用T’触发器,即T=1)

CLKi

CLKU

i 1

Qj

j0

CLKD

i 1

Qj

j0

CLK0 CLKU CLKD

CLK 2 CLKU Q1Q0 CLK DQ1Q0

45

2. 同步十进制计数器 ①加法计数器

基本原理:在四位二进制 计数器基础上修改,当计 到1001时,则下一个CLK 电路状态回到0000。

EP ET 工作状态

X 0 X X X 置 0(异步)

1 0 X X 预置数(同步)

X 1 1 0 1 保持(包括C)

X 1 1 X 0 保持(C=0)

1 1 1 1 计数

39

同步二进制减法计数器 原理:根据二进制减法运算 规则可知:在多位二进制数 末位减1,若第i位以下皆为 0时,则第i位应翻转。

Y Q2Q3

数电入门组合逻辑电路

加法器(Adder)*

• 上次我们自己搭了一个“半加器”,而实 际应用的都是全加器,但多位连接方式不 同:

• “串行加法器”:结构简单,延时严重;

• “超前进位加法器”:结构复杂,运算速 度快,常用的有一款74LS283。

• 组合逻辑电路概述 • 数据选择器和数据分配器* • 加法器* • 编码器和译码器 • 结识七段数码管 • 小实验:编码-译码-显示

结识七段数码管

• 数码管大家应该不陌生,它的原理也很简 单,仅仅是由七段长条形的发光二极管拼 成“8”字形,外加上小数点,可以显示数字 和个别字母。

• 二极管公共端为负极:“共阴”数码管, 输入为正逻辑;反之为“共阳”数码管, 负逻辑。

g f GNDa b a

a

b

c

f

Hale Waihona Puke bgde

c

e

d ·dp

f g

编码器(Encoder)

• 普通编码器:任何时刻只允许输入一个编 码信号,否则输出将发生混乱。

• 优先编码器:允许同时输入两个以上的编 码信号,在设计的优先编码器的时候已经 将所有的输入信号按优先顺序排了队,当 几个输入信号同时出现时,只对其中优先 权最高的一个进行编码。例:74LS148。

74LS14 8

• 验证74LS48的功能:D--A接到8个逻辑电平 开关上,输出与共阴极数码管的a--g相连。 观察不同输入时数码管的显示。另外,验证 各附加控制端的功能。

• 也可以自己想办法让数码管显示其他字符!

• 将74LS148和74LS48通过非门相连,构成编 码—译码—显示电路。其中,非门可选用 74LS00。

小实验:编码-译码-显示

• 每人拿到74148、7448、7400、数码管各 一……一会自己有好点子可以多要几 片……

数字电子技术基础第三章逻辑门电路

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

3.MOS管的开关特性

A、MOS管静态开关特性

在数字电路中,MOS管也是作为 开关元件使用,一般采用增强型的 MOS管组成开关电路,并由栅源电压 uGS控制MOS管的导通和截止。

时间。

toff = ts +tf 关断时间toff:从输入信号负跃变的瞬间,到iC 下降到 0.1ICmax所经历的时间。

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

ton和toff一般约在几十纳秒(ns=10-9 s)范围。通常都

有toff > ton,而且ts > tf 。

0 .3V 3 .6V 3 .6V

1V 5V

3 .6V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

3 .6V 3 .6V 3 .6V

2.1V

0 .3V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

数字电子技术基础第三章逻辑门电路

❖ 2.教学重点:不同元器件的静态开关特性,分立元件门电路 和组合门电路,TTL和CMOS集成逻辑门电路基本功能和电气特 性。

❖ 3.教学难点:组合逻辑门电路、TTL和CMOS集成逻辑门4.课时 安排: 第一节 常见元器件的开关特性 第二节 基本逻辑门电路 第三节 TTL和CMOS集成逻辑门电路

数电逻辑门电路

数电逻辑门电路逻辑门电路是数字电路中常见的一种电路结构,用于处理不同的逻辑运算和控制信号。

逻辑门电路通常由不同类型的逻辑门组成,如与门、或门、非门、异或门等。

在这篇文章中,我们将介绍几种常见的逻辑门电路以及它们的应用。

1. 与门电路与门电路是最基本的逻辑门之一,其功能是将两个输入信号进行逻辑与运算,输出结果为如果两个输入信号同时为高电平时输出高电平,否则输出低电平。

与门电路通常用于逻辑运算和控制信号的处理,比如电脑中的逻辑电路、开关控制等。

2. 或门电路或门电路是另一种常见的逻辑门,其功能是将两个输入信号进行逻辑或运算,输出结果为如果任一输入信号为高电平时输出高电平,否则输出低电平。

或门电路也广泛应用于逻辑运算和控制信号处理中,例如电脑中的逻辑电路、开关控制等。

3. 非门电路非门电路是一种单输入单输出的逻辑门,其功能是将输入信号取反输出,即如果输入信号为高电平则输出低电平,如果输入信号为低电平则输出高电平。

非门电路通常用于信号反转、逻辑反相等应用。

4. 异或门电路异或门电路是一种常见的逻辑门,其功能是将两个输入信号进行逻辑异或运算,输出结果为如果两个输入信号不相同则输出高电平,否则输出低电平。

异或门电路在数字电路设计中经常被使用,例如数据的误码检测、加法器电路等。

以上是几种常见的逻辑门电路,下面我们将介绍一个简单的逻辑门电路示例:4位全加器电路。

4位全加器电路是由4个异或门、3个与门和1个或门组成的逻辑电路,用于实现4位二进制数的加法运算。

该电路的原理是将两个4位二进制数相加,得到和输出以及进位输出。

当输入信号为A3-A0、B3-B0时,输出信号为S3-S0代表和值,C代表进位位。

在4位全加器电路中,每个异或门接收两个输入信号A和B,输出一个异或运算结果;每个与门接收三个输入信号A、B和C_in,输出一个与运算结果;一个或门接收四个输入信号S0-S3,输出一个或运算结果。

将这些逻辑门按照接线图正确连接,就可以实现全加器电路的功能。

数电-第三章逻辑门电路

了解和掌握常见时序逻辑电路的原理和应用,如寄存器、 计数器、顺序脉冲发生器等。

可编程逻辑器件应用

1 2

可编程逻辑器件简介

了解可编程逻辑器件的基本概念和分类,如PAL、 GAL、CPLD、FPGA等。

可编程逻辑器件编程

学习使用相应的开发工具和编程语言,对可编程 逻辑器件进行编程和配置,实现特定的逻辑功能。

典型组合逻辑电路

了解和掌握常见组合逻辑电路的 原理和应用,如编码器、译码器、

数据选择器、比较器等。

时序逻辑电路分析与设计

时序逻辑电路分析

分析时序逻辑电路的工作原理,包括触发器的状态转换、 时钟信号的作用等,进而理解电路的功能。

时序逻辑电路设计

根据实际需求,设计实现特定功能的时序逻辑电路。包括 确定输入、输出变量,选择适当的触发器类型,画出状态 转换图或时序图等步骤。

数电-第三章逻辑门 电路

• 逻辑门电路基本概念 • 基本逻辑门电路 • 复合逻辑门电路 • 逻辑门电路应用 • 逻辑门电路实验与仿真 • 逻辑门电路总结与展望

目录

Part

01

逻辑门电路基本概念

逻辑门定义与分类

逻辑门定义

逻辑门是数字电路中的基本单元 ,用于实现基本的逻辑运算功能 ,如与、或、非等。

逻辑符号为带有小圆圈的与门符号。

或非门电路

01

02

03

或非门逻辑功能

实现输入信号的逻辑或操 作,并取反输出结果。

或非门符号

逻辑符号为带有小圆圈的 或门符号。

或非门真值表

输入全为0时,输出为1; 输入有1时,输出为0。

异或门电路

异或门逻辑功能

实现输入信号的异或操作, 即输入信号相同时输出为0, 不同时输出为1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数电基本逻辑电路

数电基本逻辑电路是数字电子技术的基础,广泛应用于计算机、

通信、控制等领域。

通过组合不同的逻辑门,可以实现各种数字逻辑

功能。

本文将介绍几种常见的基本逻辑电路,包括与门、或门、非门、异或门和与非门,希望能够对读者理解数电基础知识起到指导作用。

首先,我们来介绍与门。

与门是最基本的逻辑门之一,它有两个

或多个输入信号和一个输出信号。

只有当所有的输入信号都为高电平时,输出信号才为高电平;否则,输出信号为低电平。

与门的逻辑符

号为“∧”,逻辑公式为Y=A∧B(其中Y为输出信号,A和B为输入

信号)。

接下来是或门。

或门也是常用的逻辑门,它也有两个或多个输入

信号和一个输出信号。

只要有任何一个输入信号为高电平,输出信号

就为高电平;只有所有输入信号都为低电平时,输出信号才为低电平。

或门的逻辑符号为“∨”,逻辑公式为Y=A∨B。

再来是非门。

非门只有一个输入信号和一个输出信号,它将输入

信号取反作为输出信号。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

非门的逻辑符号为“¬”,逻辑公式为Y=¬A。

异或门是一种常用的逻辑门,它有两个输入信号和一个输出信号。

当输入信号相同时,输出信号为低电平;当输入信号不同时,输出信

号为高电平。

异或门的逻辑符号为“⊕”,逻辑公式为Y=A⊕B。

最后是与非门。

与非门是一种特殊的逻辑门,它先进行与运算,

然后再进行非运算。

它有两个输入信号和一个输出信号。

当两个输入

信号都为高电平时,输出信号为低电平;否则,输出信号为高电平。

与非门的逻辑符号为“⇥”,逻辑公式为Y=(A⋅B)⇥。

以上是数电基本逻辑电路的介绍。

通过组合不同的逻辑门,我们

能够实现各种数字逻辑功能,如加法器、减法器、译码器、编码器等。

这些逻辑电路对于计算机的运算和控制起着重要的作用。

在应用中,我们可以通过电路设计软件进行逻辑电路的模拟和验证。

同时,我们还可以根据逻辑功能的需求选择适当的逻辑门进行组合,实现所需的数字逻辑功能。

因此,对于学习和理解数电基本逻辑

电路,掌握逻辑门的原理和运算规则非常重要。

希望本文对读者了解数电基本逻辑电路有所帮助。

通过学习和应

用逻辑电路,读者可以更好地理解数字电子技术的基础,并且能够在

实际应用中灵活运用逻辑电路,为各种数字电子系统的设计和开发提

供支持。

同时,也为进一步学习和深入研究数字电子技术奠定了坚实

的基础。