数字逻辑第三章2

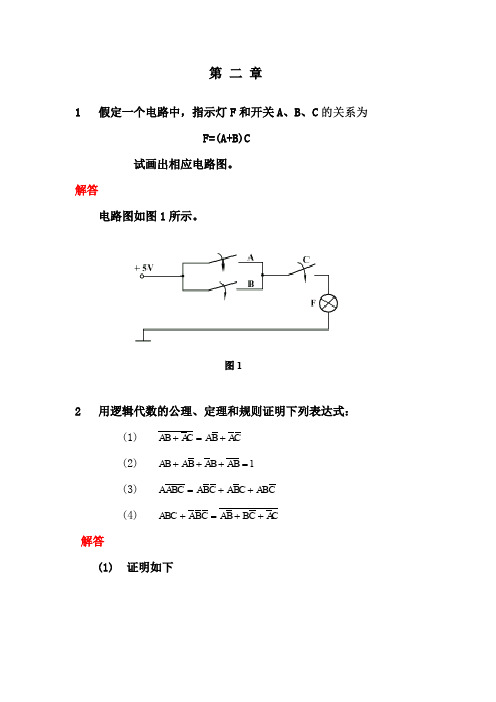

合集下载

数字逻辑与计算机组成原理:第三章 存储器系统(1)

A3 0

字线

地0 A2 0 址

译

A1

0码 器

A0 0

15

读 / 写选通

… …

…

0,0 … 0,7

16×8矩阵

15,0 … 15,7

0

…

7 位线

读/写控制电路

D0

… D7

(2) 重合法(双译码方式)

0 A4

0,00

…

0 A3

阵

A2

译

0码

31,0

…

A1

器 X 31

0 A0

… …

或低表示存储的是1或0。 T5和T6是两个门控管,读写操作时,两管需导通。

六管存储单元

保持

字驱动线处于低电位时,T5、T6 截止, 切断了两根位线与触发器之间的 联系。

六管存储单元

单译码方式

读出时: 字线接通 1)位线1和位线2上加高电平; 2)若存储元原存0,A点为低电

平,B点为高电平,位线2无电 流,读出0。

3)若存储元原存1,A点为高电 平,B点为低电平,位线2有电

流,读出1。

静态 RAM 基本电路的 读 操作(双译码方式)

位线A1

A T1 ~ T4 B

位线2

T5

行地址选择

T6

行选

T5、T6 开

列选

T7、T8 开

T7

T8

读选择有效

列地址选择 写放大器

写放大器

VA

T6

读放

读放

DOUT

T8 DOUT

DIN

1.主存与CPU的连接

是由总线支持的; 总线包括数据总线、地址总线和控制总线; CPU通过使用MAR(存储器地址寄存器)和MDR(存储

西安交通大学《数字逻辑》第三章

X Y Z 0 1 1 1 a b 0 0 1 1 0 1 0 1 c 1 0 1 1 a b H H L L H L H L c L H L L

a b

X ≥1 Z Y

c

0 0 1 1

0 1 0 1

注:本书采用逻辑非符号体制的正逻辑约定。

3.1.5 引端有效级的变换 (Bubble-to-bubble Logic design)

如前面四个变换规则所示: 若与门的输出端无逻辑非符号,则F为高有效; 与门的输出端有逻辑非符号,则/F为低有效。

⑵ 当 输入信号有效级 与其 对应的 输入端有效级 一致时, 当该信号有效时,则器件内部逻辑功能有效。

即 输入端有逻辑非符号,输入信号为低有效, 否则 输入端没有逻辑非符号,输入信号为高有效。 如:下图所示: 选择输入信号SEL连接到与非门①的输入端(无逻辑非 符号),则选择DATA=A时的SEL是高有效; SEL还连接到非门②的输入端(有逻辑非符号),则选择 DATA= B时的SEL是低有效。 即输出数据信号DATA 如下:

32

(b) 框图

8 74LS377 8 (C)逻辑图

8

32

32 位 寄 存 器 框 图 及 逻 辑 图

3. 原理图 (Schematic Diagram)

在逻辑电路图(Logic Diagram)中,详细标明器件类 型、端脚之间的连接、信号名等条件细节,再次细化逻 辑电路图。 逻辑图参见书P79图3.1( c )。 原理图参见书P89图3.19。

由这几个子系统构成说明整个系统 组成的总框图。按子系统再分别构 成其框图。如上例图。

2. 逻辑图 (Logic Diagram)

将框图的粗略表示,具体地用文字说明器件类型。 例如32位寄存器:

a b

X ≥1 Z Y

c

0 0 1 1

0 1 0 1

注:本书采用逻辑非符号体制的正逻辑约定。

3.1.5 引端有效级的变换 (Bubble-to-bubble Logic design)

如前面四个变换规则所示: 若与门的输出端无逻辑非符号,则F为高有效; 与门的输出端有逻辑非符号,则/F为低有效。

⑵ 当 输入信号有效级 与其 对应的 输入端有效级 一致时, 当该信号有效时,则器件内部逻辑功能有效。

即 输入端有逻辑非符号,输入信号为低有效, 否则 输入端没有逻辑非符号,输入信号为高有效。 如:下图所示: 选择输入信号SEL连接到与非门①的输入端(无逻辑非 符号),则选择DATA=A时的SEL是高有效; SEL还连接到非门②的输入端(有逻辑非符号),则选择 DATA= B时的SEL是低有效。 即输出数据信号DATA 如下:

32

(b) 框图

8 74LS377 8 (C)逻辑图

8

32

32 位 寄 存 器 框 图 及 逻 辑 图

3. 原理图 (Schematic Diagram)

在逻辑电路图(Logic Diagram)中,详细标明器件类 型、端脚之间的连接、信号名等条件细节,再次细化逻 辑电路图。 逻辑图参见书P79图3.1( c )。 原理图参见书P89图3.19。

由这几个子系统构成说明整个系统 组成的总框图。按子系统再分别构 成其框图。如上例图。

2. 逻辑图 (Logic Diagram)

将框图的粗略表示,具体地用文字说明器件类型。 例如32位寄存器:

《数字逻辑》第3章习题答案

习

题

【3-1】填空: (1) 逻辑代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算, 分别为 与非 、 或非 、 异或 、 同或 、和 与或非 。 (2) 与运算的法则可概述为:有 0 出 0 ,全 1 出 1 ;类似地,或运算的法则为 有”1”出”1”, 全”0”出”0” 。 (3) 摩根定理表示为: A B = A B ; A B = A B 。 (4) 函数表达式 Y= AB C D ,则其对偶式为 Y ' = ( A B)C D 。 积的形式结果应为 M ( 0,1,2,4,5,8,9,10)。 (5) 函数式 F=AB+BC+CD 写成最小项之和的形式结果应为 m ((3,6,7,11,12,13,14,15)), 写成最大项之

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

1 1 0 0 1 0

【3-8】写出下列函数的反函数 F ,并将其化成最简与或式。 (1) F1 ( A D )( B C D)( AB C ) (2) F2 ( A B )( BCD E )( B C E )(C A) (3) F3 A B C A D (4) F4 ( A B)C ( B C ) D 解: (1) F1 AD C (2) F2 AB A C E (3) F3 AB AC A D (4) F4 BC C D ABD A B C 【3-9】用对偶规则,写出下列函数的对偶式 F ,再将 F 化为最简与或式。 (1) F1 AB B C A C (2) F2 A B C D (3) F3 ( A C )( B C D)( A B D) ABC (4) F4 ( A B )( A C )( B C )(C D) (5) F5 AB C CD BD C 解:题中各函数对偶函数的最简与或式如下: (1) F1 A BC AB C (2) F2 A B D A C D (3) F3 AC A BD (4) F4 A BC B C CD (5) F5 ABC D (6) F6 AB C D 【3-10】已知逻辑函数 F A B C , G=A⊙B⊙C,试用代数法证明: F G 。 解:

题

【3-1】填空: (1) 逻辑代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算, 分别为 与非 、 或非 、 异或 、 同或 、和 与或非 。 (2) 与运算的法则可概述为:有 0 出 0 ,全 1 出 1 ;类似地,或运算的法则为 有”1”出”1”, 全”0”出”0” 。 (3) 摩根定理表示为: A B = A B ; A B = A B 。 (4) 函数表达式 Y= AB C D ,则其对偶式为 Y ' = ( A B)C D 。 积的形式结果应为 M ( 0,1,2,4,5,8,9,10)。 (5) 函数式 F=AB+BC+CD 写成最小项之和的形式结果应为 m ((3,6,7,11,12,13,14,15)), 写成最大项之

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

1 1 0 0 1 0

【3-8】写出下列函数的反函数 F ,并将其化成最简与或式。 (1) F1 ( A D )( B C D)( AB C ) (2) F2 ( A B )( BCD E )( B C E )(C A) (3) F3 A B C A D (4) F4 ( A B)C ( B C ) D 解: (1) F1 AD C (2) F2 AB A C E (3) F3 AB AC A D (4) F4 BC C D ABD A B C 【3-9】用对偶规则,写出下列函数的对偶式 F ,再将 F 化为最简与或式。 (1) F1 AB B C A C (2) F2 A B C D (3) F3 ( A C )( B C D)( A B D) ABC (4) F4 ( A B )( A C )( B C )(C D) (5) F5 AB C CD BD C 解:题中各函数对偶函数的最简与或式如下: (1) F1 A BC AB C (2) F2 A B D A C D (3) F3 AC A BD (4) F4 A BC B C CD (5) F5 ABC D (6) F6 AB C D 【3-10】已知逻辑函数 F A B C , G=A⊙B⊙C,试用代数法证明: F G 。 解:

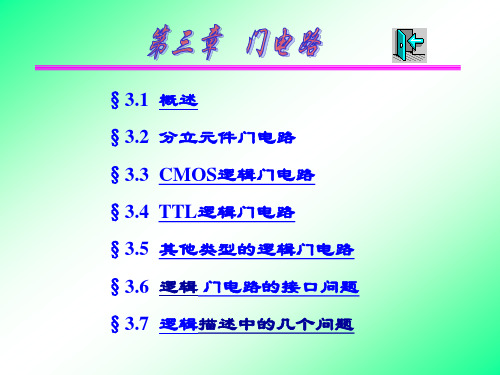

数字逻辑第3章 门电路

逻辑式:Y=A + B

逻辑符号: A 1

B

Y

电压关系表

uA uB uY

0V 0V 0V 0V 3V 2.3V 3V 0V 2.3V 3V 3V 2.3V

真值表

ABY

0

0

0

0

1

1

1

0

1

1

1

1

三、三极管非门

5V

利用二极管的压降为0.7V, 保证输入电压在1V以下时,

电路可靠地截止。

A(V) Y(V) <0.8 5 >2 0.2

II H &

II L &

… …

NOH

I OH (max) I IH

N MIN ( NOH , NOL )

NOL

IOL(max) I IL

六、CMOS漏极开路门(OD)门电路(Open Drain)

1 . 问题的提出

普通门电路

在工程实践中,往往需要将两个门的输出端 能否“线与”?

并联以实现“与”逻辑功能,称为“ 线与 。

输入 0 10% tr tf

tPHL

输出

tPLH

tr:上升时间

tf:下降时间 tw:脉冲宽度 tPHL:导通传输时间

tPLH:截止传输时间

平均传输延迟时间 (Propagation delay)

tpd= tpHL+ tpLH 2

5、功耗: 静态功耗:电路的输出没有状态转换时的功耗。 动态功耗:电路在输出发生状态转换时的功耗。

PMOS

NMOS

3、增强型MOSFET的开关特性

iD管可变子类型恒

VGS1 击开/关的条(件1)N沟道增强开型/M关O的S等FE效T电:路

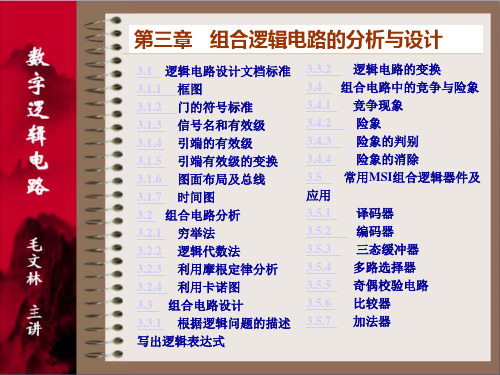

数字逻辑课件-第3章 组合逻辑电路

B

A

1 C

1

1

Z=AB+AC

例2: 设计一个举重裁判表决器。设举重有三个裁判,一

个主裁判和两个副裁判。杠铃的完全举起由每一裁判按一 下自己前面的按钮来确定。只有当两个裁判(其中必须有 主裁判)判明成功,表示成功的灯才亮。试设计该电路。 设: A——主裁判,B,C——副裁判,Z——“成功”与否 B A B &

O 11 输血者的血型用ab表示, 受血者的血型用cd表示。 00——A型 10——AB型 01——B型 11——O型

符合规定——1

不符合规定——0

例5:

输血者血型 00 A 01 B 10 AB 11 O 受血者血型 A 00 B 01 AB 10

ab cd

00 00 00 01 00 10 00 11 01 00 01 01 01 10 01 11 10 00 10 01 10 10 10 11 11 00 11 01 11 10 11 11

Z= RYG+RG+RY

5、用与非门构成逻辑电路 Z= RYG+ RG+ RY =RYG + RG + RY = RYG • RG

1 1

1

• RY

&

R G

Y

& &

&

Z

例4:列车车站的发车优先顺序为:特快、直快、慢车。在

同一时间里,车站里只能开出一班列车,即车站只能给出 一班列车的开车信号。设计一个满足上述要求的电路。

特快直快慢车 A B C 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

红黄绿 ZAZBZC 000 001 010 010 100 100 100 100

数字逻辑 第三章

第一步根据给定的逻辑电路图写出逻辑函数表达式p1abp2acp3b?cp3b?cp4bcp5p1p2abacp6p3p4b?cbcfp5p6abacb?cbc34第二步化简逻辑函数表达式fabacb?cbcabacbcbcbcabacbcbcbcabacbcbcbc35bacbcbcbcbcbcbcbcbcb?c第三步列出逻辑电路的真值表ab000001010110101111cf01110011001001010136第四步逻辑问题评述该电路当输入bc取值不同时输出f为1而当输入bc取值相同时输出f为0

0 0 0

0 1 1

1 1 1

0 0 0

BD

15

BC

由上面表达式得到最简与或表 达式: F=AB+BC+BD

第二步: 对所得的表达式两次求反得到: F(A,B,C,D) = AB • BC • BD 第三步:画逻辑 A 电路图 &

B B C B D

& &

&

F

16

3.2.2 用“或—非”门实现逻辑函 数

29

第二步, 化简逻辑函数表达式。

过程如下: F= A·ABC +B·ABC+ C·ABC =ABC(A+B+C) =ABC+A+B+C =ABC+ABC

30

第三步,列出逻辑电路的真值表

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F 1 0 0 0 0 0 0 1

31

第四步,逻辑问题评述

我们发现:当电路输入一致时,输出为1; 而输入不一致时,输出为0。这表明该电路具 有判断输入信号是否一致的逻辑功能。

0 0 0

0 1 1

1 1 1

0 0 0

BD

15

BC

由上面表达式得到最简与或表 达式: F=AB+BC+BD

第二步: 对所得的表达式两次求反得到: F(A,B,C,D) = AB • BC • BD 第三步:画逻辑 A 电路图 &

B B C B D

& &

&

F

16

3.2.2 用“或—非”门实现逻辑函 数

29

第二步, 化简逻辑函数表达式。

过程如下: F= A·ABC +B·ABC+ C·ABC =ABC(A+B+C) =ABC+A+B+C =ABC+ABC

30

第三步,列出逻辑电路的真值表

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F 1 0 0 0 0 0 0 1

31

第四步,逻辑问题评述

我们发现:当电路输入一致时,输出为1; 而输入不一致时,输出为0。这表明该电路具 有判断输入信号是否一致的逻辑功能。

数字逻辑第3章答案

(4) F A B[(C D)E G]

F, A B[(C D)E G]

5 (1) 如果已知 X + Y 和 X + Z 的逻辑值相同,那么 Y 和 Z 的逻

辑值一定相同。正确吗?为什么? (2) 如果已知 XY 和 XZ 的逻辑值相同,那么那么 Y 和 Z 的逻辑值

一定相同。正确吗?为什么? (3)如果已知 X + Y 和 X + Z 的逻辑值相同,且 XY 和 XZ 的逻辑

(1) F(A, B,C, D) BD AD CD CD ACD ABD

(2) F(A, B,C, D) (AB AB) C (AB AB) C

解答

G(A, B,C, D) AB BC AC (A B C) ABC

(1) 当 b a 时,令 a=1,b=0 能得到最简“与-或”表达式: F BC CD ACD (3 项)

(2) 当 a=1,b=1 时,能得到最简的“与-或”表达式:

F BC CD AC (3 项)

11 用列表法化简逻辑函数

F(A, B,C, D) m(0,2,3,5,7,8,10,11,13,15)

10

0

0

01 0 0 1 1

1

1

10 0 0 1 1

1

1

11 0 1 0 1

0

0

4 求下列函数的反函数和对偶函数: (1) F AB AB

(2) F A B A C C DE E

(3) F (A B)(C DAC)

(4) F A B CD E G

值相同,那么 Y = Z。正确吗?为什么? (4) 如果已知 X+Y 和 X·Y 的逻辑值相同,那么 X 和 Y 的逻辑值

F, A B[(C D)E G]

5 (1) 如果已知 X + Y 和 X + Z 的逻辑值相同,那么 Y 和 Z 的逻

辑值一定相同。正确吗?为什么? (2) 如果已知 XY 和 XZ 的逻辑值相同,那么那么 Y 和 Z 的逻辑值

一定相同。正确吗?为什么? (3)如果已知 X + Y 和 X + Z 的逻辑值相同,且 XY 和 XZ 的逻辑

(1) F(A, B,C, D) BD AD CD CD ACD ABD

(2) F(A, B,C, D) (AB AB) C (AB AB) C

解答

G(A, B,C, D) AB BC AC (A B C) ABC

(1) 当 b a 时,令 a=1,b=0 能得到最简“与-或”表达式: F BC CD ACD (3 项)

(2) 当 a=1,b=1 时,能得到最简的“与-或”表达式:

F BC CD AC (3 项)

11 用列表法化简逻辑函数

F(A, B,C, D) m(0,2,3,5,7,8,10,11,13,15)

10

0

0

01 0 0 1 1

1

1

10 0 0 1 1

1

1

11 0 1 0 1

0

0

4 求下列函数的反函数和对偶函数: (1) F AB AB

(2) F A B A C C DE E

(3) F (A B)(C DAC)

(4) F A B CD E G

值相同,那么 Y = Z。正确吗?为什么? (4) 如果已知 X+Y 和 X·Y 的逻辑值相同,那么 X 和 Y 的逻辑值

《数字逻辑》第3章作业与习题_单选题第六小题已更正版本

。

20.如果某 TTL 与非门的输入低电平噪声容限 VNL=0.7V,输入低电平

ViL=0.2V,那么它的关门电平 Voff 为

。

21.对于或非门,只要有一个输入为高电平,则输出就为 电平,所以

对或非门多余输入端的处理不能接 电平。

22.对于 TTL 与非门,只要有一个输入为低电平,则输出就为 电平,

为

,按抗干扰能力强弱的顺序依次为

,按静态功耗低和高的顺序依次为

。

6. 假设 VGS(TH)为开启电压,一般在 1~3V 范围内,则 NMOS 管当

时

截止,当

时导通;PMOS 管当

时截止,当

时

导通。

7. CMOS 反相器是由

作为驱动管,

作为负载管形成了 电

路结构。

2)单选题

1.硅二极管导通和截止的条件是( )。

不形成

;在外电场作用下,

和

均能参与导电。

7. 半导体中载流子的两种运动方式指

运动和

运动。

8. 硅二极管的截止条件是

,导通条件是

。

9. 数字电路中的晶体三极管作为开关元件,主要工作在

和

。

10. 三种基本逻辑门是

、

、

。

11. 与门是可以实现

的电路。

12. 在 TTL 电路中,输入端悬空等效于逻辑 电平,但为了避免引入干

② 输出端能带同类门的输入端个数

③ 输出端能带同类门的个数

④ 输入端数

7.输出端可直接连在一起实现“线与”逻辑功能的门电路是( )。

① 与非门

② 或非门 ③ OC 门

④ 异或门

8.两输入变量 A、B 的逻辑门的输出、输入如图所示,根据输出波形 Y,该

数字逻辑与计算机组成 第3章 组合逻辑电路

硬件资源:7个4输入与门、1个7输入或门

10

1.4 组合逻辑电路设计

利用布尔代数化简, 以减少逻辑门数和输入端数 X·Y+X·Y’=X

F = SN3N2N1N0(1,2,3,5,7,11,13) =N3’N0+N3’ N2’ N1 N0’+N3 N2’ N1 N0+N3 N2 N1’ N0

非法值 • 信号值不能被有效识别为高电平或低电平,处于不确定状态。 例如:下图中的信号X

不管A是0还是1,F结点都会同时 被高电平和低电平驱动,可能导 致在F结点处之间有较大电流流动 ,使电路发热而被损坏

16

1.5 无关项、非法值和高阻态

例:设计一个检测电路,当NBCD(8421)码数值大于5时,输出为1

最简输出表达式

函数转换:独立逻辑门、中间组件、可编程器件

画出逻辑电路图 逻辑器件的标准符号,输入、输出信号、器件标识

评价电路

电路分析:功能、缺陷、电气特性等

9

1.4 组合逻辑电路设计

例1:素数检测器的设计

列出真值表

• 4-bit input, N3N2N1N0

写出最小项表达式 F = SN3N2N1N0(1,2,3,5,7,11,13)

输出变量:故障信号F 正常工作为0,发生故障为1

故障状态 真 值 表 RY G F

0 0 01 0 0 10 0 1 00 0 1 11 1 0 00 1 0 11 1 1 01 1 1 11

13

1.4 组合逻辑电路设计

逻辑抽象结果

真值表

RY G F

000 1 001 0 010 0 011 1 100 0 101 1 110 1 111 1

每个输入端和输出端只有高电平、

数字逻辑第三章

数字逻辑

华南理工大学出版社

3.2.1组合逻辑电路的设计一般步骤是:

①根据逻辑实际问题分析,确定输入和输出变量,并规定其状态表示法。 ②根据给定关系列出逻辑真值表,由真值表写出逻辑函数最小项的表达式。 ③逻辑函数的化简和变换,考虑实际工程问题,选定所用器件类型。 ④按要求画出逻辑图。

用门电路

A B C F

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

F 1 1 1 0 1 0 0 0

数字逻辑

华南理工大学出版社

3.1.3组合逻辑电路分析中应该注意的问题

组合逻辑电路分析中应该注意的问题包括:

1.充分利用各种分析方法,以达到能快速解决问题的目的。 2.熟悉基本的逻辑符号及其表达式。 3.正确熟练运用公式法或卡诺图法化简,防止化简过程中出现 不必要的错误。 4.化简完成得到最简的函数表达式后,应该应用几组不同的输 入数据来加以验证。

数字逻辑

华南理工大学出版社

3.2 组合电路设计 Combinational Logic Circuit Design 目的: 是根据设计问题的文字描述要求,分析其逻辑关系, 实现其逻辑功能,最后画出实现逻辑功能的逻辑电路图。 要求: 电路用最少的逻辑门(集成块)、最少的输入端数、最 少的电路级数。 (公式化简、卡诺图化简和逻辑函数变换)

化简结果1为:F=C(A B)+AB

F A BC AB C ABC ABC

A B C

逻辑电路图如下:

F1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

数字逻辑-第三章概要PPT课件

开通时间:从反向截止变为正向导通所需要的时间。

反向恢复时间tre:二极管从正向导通到反向截止所需 的时间。

一般反向恢复时间比开通时间大得多。

tre一般为纳秒数量级(通常tre ≤5ns )。

28.01.2021

-

12

3.2.2 三极管的开关特性

1. 静态特性及开关等效电路 在数字电路中,三极管作为开关元件,主要工

28.01.2021

-

36

(使 保3)输与开非出门门电电输平平出达V为到ON低标:电准开平低门时电电所平平允VSV许L的O的N输是最入指小电在输平额入,定高即负电指载平确下。, 它表示使与非门开通的最小输入高电平。

反 时的映抗V了O干高N的扰电产能平品力抗规愈干范强扰值。能为力V,ONV≤O1N.8愈V。小开,门在电输平入的高大电小平

28.01.2021

-

15

图2-4 三极管开关等效电路 (a) 截止时 (b) 饱和时

28.01.2021

-

16

2. 三极管的开关时间(动态特性)

延迟时间td

上升时间tr 开启时间ton

28.01.2021

图2-5 三极管- 的开关时间

存储时间ts 下降时间tf 关闭时间17toff

(1) 开启时间ton 三极管从截止到饱和所需的时间。

半导体二极管、三极管和MOS管,则是构成这 种电子开关的基本开关元件。

28.01.2021

-

6

理想开关的开关特性:

(1) 静态特性: 断开时,开关两端的电压不管多大,等效电阻 ROFF = 无穷,电流IOFF = 0。

闭合时,流过其中的电流不管多大,等效电阻 RON = 0,电压UAK = 0。

数字逻辑 第三章

首先分析给定问题,弄清楚输入变量和输出变量是 哪些,并规定它们的符号与逻辑取值(即规定它们何时 取值 0 ,何时取值1) 。然后分析输出变量和输入变量 间的逻辑关系,列出真值表。 根据真值表用代数法或卡诺图法求最简“与或” 式,然后根据题中对门电路类型的要求,将最简与或 式变换为需要的逻辑函数表达式。

x1

输入信号

F1

F2=f2(x1,…xn)

组合逻辑电路

输出信号

xn

Fm

Fm=fm(x1,…xn)

n个二进制输入变量共有2n种可能的组合。

组合逻辑电路的基本分析方法

分析思路:根据给定逻辑电路,找出输出输入

间的逻辑关系,从而确定电路的逻辑功能。 步骤:

根据逻辑 图,写出 输出函数 的表达式 简化函数 (代数法, 卡诺图法)

F

A3 A4

F2 A3⊕A4 A3 A4 A3 A4

1 2 1 2 1 2

=1

F2

F F ⊕F F F F F

+ A1A 2 A 3 A 4 + A1A 2 A 3 A 4

= A1A 2 A 3 A 4 + A1A 2 A 3 A 4 + A1 A 2 A 3 A 4 + A1 A 2 A 3 A 4 + A1 A 2 A 3 A 4 + A1 A 2 A 3 A 4

3.1.1 简单逻辑门电路

与门 或门 与或非逻辑运算

F1=AB

F2=A+B

F3= A

3.1.2 复合逻辑门电路

与非门

或非门

与或非门

F1=AB

F2=A+B

F3=AB+CD

异或运算

A 0 0 1 1

数字逻辑结构L3第三章 逻辑门电路

F A B AB AB

“同或”运算用符号表示,逻

辑表达式为:

F A B AB AB

F =1 AB (d)

F =1 AB (e)

数字电路是二值逻辑电路,一般用高低电平来表示二值 逻辑中的‘1’和‘0’两种逻辑状态。

开关电路(逻辑电路)中的开关K由二极管或三极管电路 构成。在输入电压Vi的作用下,使二极管或三极管电路处于 导通或截止状态。

0 8V VB 0 13.3 3.3 2.0V 三极管截止,V0=5V时。

AR

(vi) 1

R

vEE=-

8v

2

VCC=5 v

R

cY

(vo)

RC=1K,R1=3.3K,R2=10K,=2,VCE(sat)=0.1v, VIH=5v, VIL=0v

b

R1 + R2

- VEE

e

RB

2.5K

+

VB -

基极电流一定时,集、射极之间电压与集电极电流的关系曲线。

可分为三个工作区: 1.截止区 条件:发射结反偏或两端电压为零。 特点: IB =0,Ic很小。

2.饱和区 条件:发射结和集电结均为正偏。 特点:VCE = VCES。

VCES 称为饱和管压降,小功率硅管约 0.3 V,锗管约为 0.1 V。

3.放大区

VI

B

RB

VBE

VO E IE

当vI=VIH时,三极管饱和,VCE≈0,

相当于开关闭合, vO≈0 ;

三极管饱和导通时,

C

C

相当于C、E间短路;

B E

B E

三极管截止时, 相当于C、E间开路, B、E间, B、C间也开路。

3.3 分离元件逻辑门电路 1. 二极管与门

“同或”运算用符号表示,逻

辑表达式为:

F A B AB AB

F =1 AB (d)

F =1 AB (e)

数字电路是二值逻辑电路,一般用高低电平来表示二值 逻辑中的‘1’和‘0’两种逻辑状态。

开关电路(逻辑电路)中的开关K由二极管或三极管电路 构成。在输入电压Vi的作用下,使二极管或三极管电路处于 导通或截止状态。

0 8V VB 0 13.3 3.3 2.0V 三极管截止,V0=5V时。

AR

(vi) 1

R

vEE=-

8v

2

VCC=5 v

R

cY

(vo)

RC=1K,R1=3.3K,R2=10K,=2,VCE(sat)=0.1v, VIH=5v, VIL=0v

b

R1 + R2

- VEE

e

RB

2.5K

+

VB -

基极电流一定时,集、射极之间电压与集电极电流的关系曲线。

可分为三个工作区: 1.截止区 条件:发射结反偏或两端电压为零。 特点: IB =0,Ic很小。

2.饱和区 条件:发射结和集电结均为正偏。 特点:VCE = VCES。

VCES 称为饱和管压降,小功率硅管约 0.3 V,锗管约为 0.1 V。

3.放大区

VI

B

RB

VBE

VO E IE

当vI=VIH时,三极管饱和,VCE≈0,

相当于开关闭合, vO≈0 ;

三极管饱和导通时,

C

C

相当于C、E间短路;

B E

B E

三极管截止时, 相当于C、E间开路, B、E间, B、C间也开路。

3.3 分离元件逻辑门电路 1. 二极管与门

数字逻辑3-2.ppt

Limitation for output current and resistive load.

Use NAND2 to drive LED

Fig 3-54 74AC Device : VOLmax = 0.37 V

R (5 0.37 1.6) /10 0.303k 303

If an input is not used ?

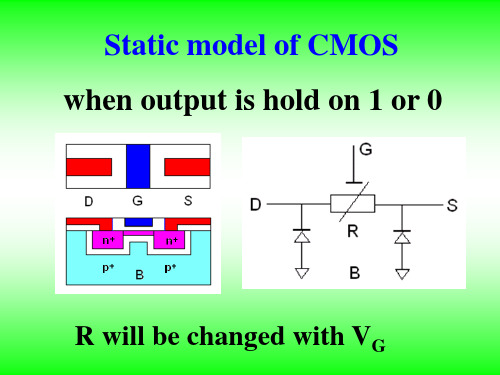

Static model of CMOS when output is hold on 1 or 0

R will be changed with VG

The electric model for basic CMOS circuit

When Vx is increased, Rp will be increased and Rn be decreased !

Hysteresis: the difference between the threshold

Schmitt – Trigger input

It can be used to eliminate noise !

If an input keep floating, the output will be undecided, or the gate may be damaged ! Must connected it to some where !

Can we connect more than one output to a single line?

The resistors are changed with input

Figure 3-8 3-9 The output voltage is changed When input voltage changed.

Use NAND2 to drive LED

Fig 3-54 74AC Device : VOLmax = 0.37 V

R (5 0.37 1.6) /10 0.303k 303

If an input is not used ?

Static model of CMOS when output is hold on 1 or 0

R will be changed with VG

The electric model for basic CMOS circuit

When Vx is increased, Rp will be increased and Rn be decreased !

Hysteresis: the difference between the threshold

Schmitt – Trigger input

It can be used to eliminate noise !

If an input keep floating, the output will be undecided, or the gate may be damaged ! Must connected it to some where !

Can we connect more than one output to a single line?

The resistors are changed with input

Figure 3-8 3-9 The output voltage is changed When input voltage changed.

数字逻辑第三四章讲义

吸收律

0律 1律 重叠律 互补律 非律 长中含短, 留下短。 长中含反 ,去掉反 。

A AB A B

(A+B)(A+C)=A+BC

布尔代数基本定律

Rule 1.

A + 0 = A

OR Truth Table

Rule 2.

A + 1 = 1

2014-11-13

29

Rules of Boolean Algebra

与门

A B A B

F

A B

&

F

或门

A

F

B

A

≥1

F

非门

A A B A

F

1

F

异或门

F

A

B A B

=1

F

与非门

B

F

&

F

逻辑门符号

A B C D

&

?

≥1 Y

A B C

D

F AB CD

F

与或非ቤተ መጻሕፍቲ ባይዱ算

符号举例

第四章 布尔代数与逻辑化简

知识点

1. 两种逻辑表达式的形式: SOP and POS form. 2. 最大项maxterm 和最小项 minterm. 3. 三个基本定律十二个运算法则,以及三个布尔代数基本规则. 4. 摩根定理. 5. 使用布尔代数化简逻辑表达式。

Rule 7.

A · A = A

AND Truth Table

Rule 8.

AA 0

2014-11-13

32

Rules of Boolean Algebra

Rule 9. A A

0律 1律 重叠律 互补律 非律 长中含短, 留下短。 长中含反 ,去掉反 。

A AB A B

(A+B)(A+C)=A+BC

布尔代数基本定律

Rule 1.

A + 0 = A

OR Truth Table

Rule 2.

A + 1 = 1

2014-11-13

29

Rules of Boolean Algebra

与门

A B A B

F

A B

&

F

或门

A

F

B

A

≥1

F

非门

A A B A

F

1

F

异或门

F

A

B A B

=1

F

与非门

B

F

&

F

逻辑门符号

A B C D

&

?

≥1 Y

A B C

D

F AB CD

F

与或非ቤተ መጻሕፍቲ ባይዱ算

符号举例

第四章 布尔代数与逻辑化简

知识点

1. 两种逻辑表达式的形式: SOP and POS form. 2. 最大项maxterm 和最小项 minterm. 3. 三个基本定律十二个运算法则,以及三个布尔代数基本规则. 4. 摩根定理. 5. 使用布尔代数化简逻辑表达式。

Rule 7.

A · A = A

AND Truth Table

Rule 8.

AA 0

2014-11-13

32

Rules of Boolean Algebra

Rule 9. A A

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CP脉冲前沿到触发器翻转的时间 pd cp CP脉冲前沿到触发器翻转的时间

t

Q

t pdCP→Q,,Q = CP→ Q

CP D Q

t pLHCP→Q,Q + t pHLCP→Q,Q 2

t pLHCP→Q

(2级门 级门) 级门

t pHLCP→Q

(3级门 级门) 级门

正边沿D 正边沿D触发器的开关参数

3. 描述CP脉冲宽度的参数 描述CP脉冲宽度的参数

twCP-- >= CP twCP+>= tpd

负脉冲准备数据

CP-Q,Q CP-

正脉冲触发器稳定翻转

Tmin = twCP-- + twCP-CP CP fmax = 1/Tmin

两种基本触发器的应用比较(1) 两种基本触发器的应用比较(1)

例: 4位锁存器和D触发器同时接受加法器的结果: 4位锁存器和 触发器同时接受加法器的结果: 位锁存器和D

触发器-逻辑电路的记忆元件

能存储1位二进制数是基本要求. 能存储1位二进制数是基本要求. 为了好用,便于控制,才有了电位触发, 为了好用,便于控制,才有了电位触发, 边沿触发,主从触发三种触发方式. 边沿触发,主从触发三种触发方式. 抓住了触发方式,就抓住了问题的本质! 抓住了触发方式,就抓住了问题的本质! 不同触发方式,都反应在波形图上! 不同触发方式,都反应在波形图上! 要看懂波形图,理解波形图! 要看懂波形图,理解波形图!

D触发器工作原理

Q

5

Q

6

I

"1"

"0"

III D

1

3

4

2

II CP

cp↑时, D=o, 门3=0, Q=1; 触发器III记忆"0" cp↑ 触发器III记忆 记忆" 维持门3输出为0; 输出和门2相连, 态,维持门3输出为0; 门1门4输出和门2相连, 使门2输出0 维持门4输出为1. 此时即使D 使门2输出0,维持门4输出为1. 此时即使D变 也会保持维持门4输出为1.因此 因此, 化,也会保持维持门4输出为1.因此,黄线称 维持0 阻塞1 "维持0,阻塞1"线.

对于Delay FF:时钟正跳变到来的时候 对于Delay FF:时钟正跳变到来的时候 Data必须确定. Data必须确定.

CP D Q

D可不确定 D可以变化 D不能变化

两种基本触发器的应用比较(5) 两种基本触发器的应用比较(5)

两者使用中都应合理安排好E/CP与 两者使用中都应合理安排好E/CP与D 的配合关系, 可以躲开D端干扰. 的配合关系, 可以躲开D端干扰. D触发器的数据一定要比CP先来,但 触发器的数据一定要比CP先来 先来, 可以先撤,不会影响触发器状态! 可以先撤,不会影响触发器状态! 电位触发器的数据可以比E晚来, 电位触发器的数据可以比E晚来,但不 能早撤,否则就要影响触发器状态! 能早撤,否则就要影响触发器状态!

正边沿D 正边沿D触发型与电位触发器比较

边沿触发器:CP正跳变之前来到的数据 正跳变之前来到的数据, 边沿触发器:CP正跳变之前来到的数据, 一定要延迟到CP正跳变来到时才被接 一定要延迟到CP正跳变来到时才被接 (Store),因此称为"延迟型触发器" 收(Store),因此称为"延迟型触发器" (Delay(Delay-FF). 电位触发器:E=1时 紧跟D 电位触发器:E=1时,Q紧跟D电平的变 的变化立即就反应到Q的状态, 化,D的变化立即就反应到Q的状态, 因此也称对电位是透明的(Level 因此也称对电位是透明的(Level Transparent). Transparent).

QQ

Q

QQ

Q Q Q

QQ

'74(14 pin) 独立的双D 独立的双 FF SD

Q

Q

Q RD SD

Q

RD CP D

CP D '174(16 pin) 6D FF

1Q 2Q 3Q 4Q

5Q

6Q

R CP D D

R CP D D

R CP D D

R CP D D

R CP D D

R CP D D

clear CP

1D 2D 3D 4D 5D 6D

正边沿D 正边沿D触发器的开关参数

1. 描述输入数据和CP之间关系的参数 描述输入数据和CP之间关系的参数

数据建立时间t 数据建立时间tsu(set up) 数据保持时间t 数据保持时间th(hold) tsu =tpd1+ tpd2 (2级门延迟) 级门延迟) CP到来之前 数据应该等在门3 到来之前, 在CP到来之前,数据应该等在门3门4输入 th =tpd3 (1级门延迟) 级门延迟) CP到来以后D不能立即就撤,必须等待触发器稳定, CP到来以后 不能立即就撤,必须等待触发器稳定, 到来以后D 即由门1 组成的触发器已经"记忆" 即由门1门3组成的触发器已经"记忆". 因此,D必须要保持一定的宽度! 因此, 必须要保持一定的宽度!

"攻城不怕坚,读书不怕难,世上无难事,只要肯登攀!" 攻城不怕坚,读书不怕难,世上无难事,只要肯登攀! ——与有 畏难"情绪的同学共勉 ——与有"畏难"情绪的同学共勉 与有" 从今天抓起,从现在抓起. 从今天抓起,从现在抓起. 此时跟进,尚来得及;此时继续放弃,只能来年重修! 此时跟进,尚来得及;此时继续放弃,只能来年重修! 解决学习动力问题: 要我学? 我要学!自觉学! 解决学习动力问题: 要我学? 我要学!自觉学! 为谁学?为自己的前程学! 为谁学?为自己的前程学! 期中不考试,自觉去复习.第二次实验搞清楚! 期中不考试,自觉去复习.第二次实验搞清楚!

正边沿D 正边沿D触发型与电位触发器比较

E/CP D

Q(电位 电位) 电位 Q(正沿 正沿D) 正沿

正边沿D触发器的状态清清楚楚! 端变化不影响 端变化不影响Q! 正边沿 触发器的状态清清楚楚!(D端变化不影响 !) 触发器的状态清清楚楚 电位D触发器只是在 = 时才清楚 时才清楚! 时仍影响Q! 电位 触发器只是在E=0时才清楚!(E=1时仍影响 !) 触发器只是在 时仍影响

电位触发器时序图

时序图(Timing 时序图(Timing Diagram)

E D Q Q=? 尖峰被屏蔽

当E=1时,Q=D.E=0时,屏蔽外部输入. = 时 = . = 时 屏蔽外部输入. 问题: = 时 的变化全部反应的Q端 不好用! 问题:E=1时,D的变化全部反应的 端!不好用! 的变化全部反应的

§1.3 边沿触发型(D触发器) 边沿触发型(D触发器 触发器)

Q

5 6

Q

功能表

CP

↑

D D

Q Q D D

3

4

CP

1 2

结构:门 门 是输入控制 是输入控制, 结构 门1门2是输入控制 D和D在CP控制下引入 和 在 控制下引入 门3门4. 门 . 门2门4, 门1门3, 门5门6 门 门 门 组成3个基本触发器 个基本触发器. 组成 个基本触发器.

D

D触发器工作原理

Q

5

Q

6

I

"0"

"1"

III D

1

3

4

2

II CP

cp↑时, D=1, 门4=0, Q=1; 触发器Ⅱ记忆 cp↑ 触发器Ⅱ 维持门4输出为0; 输出和门3 "0"态,维持门4输出为0; 门4输出和门3相 阻塞输入D的变化对门3影响,维持门3 连,阻塞输入D的变化对门3影响,维持门3输 出为1. 此时即使D变化,也会保持维持门3 出为1. 此时即使D变化,也会保持维持门3输 出为1.因此 黄线称"维持1 阻塞0 因此, 出为1.因此,黄线称"维持1,阻塞0"线.

数据建立时间

Q

1 2

Q

D需要提前于CP形 需要提前于CP形 成互补数据,等候 在门3 在门3,4入口.

4

3

CP

5 6

D

数据保持时间

Data的撤除应该在 正跳变之后 Data的撤除应该在CP正跳变之后 的撤除应该在CP (Delay(Delay-FF)

CP D

tsu

th

2. 描述传输延迟的参数(Propogation)tpd 描述传输延迟的参数(Propogation)t

两种基本触发器的应用比较(5) 两种基本触发器的应用比较(5)

例:译码器输出到锁存器和D触发器 译码器输出到锁存器和 触发器

A B Y0 Y1 Y2 Y3 D0 D1 D2 D3 E Q0 Q1 Q2 Q3

D0 Q0 D1 Q1 D2 Q2 D3 CP Q3

CP

两种基本触发器的应用比较(6) 两种基本触发器的应用比较(6)

§1. 触发器-逻辑电路的记忆元件

§1.1 触发器工作原理(R-S基本触发器) 触发器工作原理(R- 基本触发器) 电位触发器(Latch,锁存器) §1.2 电位触发器(Latch,锁存器) 边沿触发器( 触发器) §1.3 边沿触发器(D触发器) 主从触发器( 触发器) §1.4 主从触发器(J-K触发器)

Q

Q

RD

CP D Q

RD SD

D CP

D触发器功能表

RD

0 1 1

SD

1 0 1

CP x x

D x x D

Q 0 1 D

Q

1 0

↑

D

(波形图见P73) 波形图见P73)

几种D 几种D 触发器集成电路器件

Number '74 '174 '171/'175 '273 '374/'377 '378 '379 Flip-Flop Type Dual Hex Quad Octal Octal Hex Quad D D D D D D D Output Features Pre-set,Clear Clear Clear Clear Output enable Output enable Output enable

t

Q

t pdCP→Q,,Q = CP→ Q

CP D Q

t pLHCP→Q,Q + t pHLCP→Q,Q 2

t pLHCP→Q

(2级门 级门) 级门

t pHLCP→Q

(3级门 级门) 级门

正边沿D 正边沿D触发器的开关参数

3. 描述CP脉冲宽度的参数 描述CP脉冲宽度的参数

twCP-- >= CP twCP+>= tpd

负脉冲准备数据

CP-Q,Q CP-

正脉冲触发器稳定翻转

Tmin = twCP-- + twCP-CP CP fmax = 1/Tmin

两种基本触发器的应用比较(1) 两种基本触发器的应用比较(1)

例: 4位锁存器和D触发器同时接受加法器的结果: 4位锁存器和 触发器同时接受加法器的结果: 位锁存器和D

触发器-逻辑电路的记忆元件

能存储1位二进制数是基本要求. 能存储1位二进制数是基本要求. 为了好用,便于控制,才有了电位触发, 为了好用,便于控制,才有了电位触发, 边沿触发,主从触发三种触发方式. 边沿触发,主从触发三种触发方式. 抓住了触发方式,就抓住了问题的本质! 抓住了触发方式,就抓住了问题的本质! 不同触发方式,都反应在波形图上! 不同触发方式,都反应在波形图上! 要看懂波形图,理解波形图! 要看懂波形图,理解波形图!

D触发器工作原理

Q

5

Q

6

I

"1"

"0"

III D

1

3

4

2

II CP

cp↑时, D=o, 门3=0, Q=1; 触发器III记忆"0" cp↑ 触发器III记忆 记忆" 维持门3输出为0; 输出和门2相连, 态,维持门3输出为0; 门1门4输出和门2相连, 使门2输出0 维持门4输出为1. 此时即使D 使门2输出0,维持门4输出为1. 此时即使D变 也会保持维持门4输出为1.因此 因此, 化,也会保持维持门4输出为1.因此,黄线称 维持0 阻塞1 "维持0,阻塞1"线.

对于Delay FF:时钟正跳变到来的时候 对于Delay FF:时钟正跳变到来的时候 Data必须确定. Data必须确定.

CP D Q

D可不确定 D可以变化 D不能变化

两种基本触发器的应用比较(5) 两种基本触发器的应用比较(5)

两者使用中都应合理安排好E/CP与 两者使用中都应合理安排好E/CP与D 的配合关系, 可以躲开D端干扰. 的配合关系, 可以躲开D端干扰. D触发器的数据一定要比CP先来,但 触发器的数据一定要比CP先来 先来, 可以先撤,不会影响触发器状态! 可以先撤,不会影响触发器状态! 电位触发器的数据可以比E晚来, 电位触发器的数据可以比E晚来,但不 能早撤,否则就要影响触发器状态! 能早撤,否则就要影响触发器状态!

正边沿D 正边沿D触发型与电位触发器比较

边沿触发器:CP正跳变之前来到的数据 正跳变之前来到的数据, 边沿触发器:CP正跳变之前来到的数据, 一定要延迟到CP正跳变来到时才被接 一定要延迟到CP正跳变来到时才被接 (Store),因此称为"延迟型触发器" 收(Store),因此称为"延迟型触发器" (Delay(Delay-FF). 电位触发器:E=1时 紧跟D 电位触发器:E=1时,Q紧跟D电平的变 的变化立即就反应到Q的状态, 化,D的变化立即就反应到Q的状态, 因此也称对电位是透明的(Level 因此也称对电位是透明的(Level Transparent). Transparent).

Q

Q Q Q

'74(14 pin) 独立的双D 独立的双 FF SD

Q

Q

Q RD SD

Q

RD CP D

CP D '174(16 pin) 6D FF

1Q 2Q 3Q 4Q

5Q

6Q

R CP D D

R CP D D

R CP D D

R CP D D

R CP D D

R CP D D

clear CP

1D 2D 3D 4D 5D 6D

正边沿D 正边沿D触发器的开关参数

1. 描述输入数据和CP之间关系的参数 描述输入数据和CP之间关系的参数

数据建立时间t 数据建立时间tsu(set up) 数据保持时间t 数据保持时间th(hold) tsu =tpd1+ tpd2 (2级门延迟) 级门延迟) CP到来之前 数据应该等在门3 到来之前, 在CP到来之前,数据应该等在门3门4输入 th =tpd3 (1级门延迟) 级门延迟) CP到来以后D不能立即就撤,必须等待触发器稳定, CP到来以后 不能立即就撤,必须等待触发器稳定, 到来以后D 即由门1 组成的触发器已经"记忆" 即由门1门3组成的触发器已经"记忆". 因此,D必须要保持一定的宽度! 因此, 必须要保持一定的宽度!

"攻城不怕坚,读书不怕难,世上无难事,只要肯登攀!" 攻城不怕坚,读书不怕难,世上无难事,只要肯登攀! ——与有 畏难"情绪的同学共勉 ——与有"畏难"情绪的同学共勉 与有" 从今天抓起,从现在抓起. 从今天抓起,从现在抓起. 此时跟进,尚来得及;此时继续放弃,只能来年重修! 此时跟进,尚来得及;此时继续放弃,只能来年重修! 解决学习动力问题: 要我学? 我要学!自觉学! 解决学习动力问题: 要我学? 我要学!自觉学! 为谁学?为自己的前程学! 为谁学?为自己的前程学! 期中不考试,自觉去复习.第二次实验搞清楚! 期中不考试,自觉去复习.第二次实验搞清楚!

正边沿D 正边沿D触发型与电位触发器比较

E/CP D

Q(电位 电位) 电位 Q(正沿 正沿D) 正沿

正边沿D触发器的状态清清楚楚! 端变化不影响 端变化不影响Q! 正边沿 触发器的状态清清楚楚!(D端变化不影响 !) 触发器的状态清清楚楚 电位D触发器只是在 = 时才清楚 时才清楚! 时仍影响Q! 电位 触发器只是在E=0时才清楚!(E=1时仍影响 !) 触发器只是在 时仍影响

电位触发器时序图

时序图(Timing 时序图(Timing Diagram)

E D Q Q=? 尖峰被屏蔽

当E=1时,Q=D.E=0时,屏蔽外部输入. = 时 = . = 时 屏蔽外部输入. 问题: = 时 的变化全部反应的Q端 不好用! 问题:E=1时,D的变化全部反应的 端!不好用! 的变化全部反应的

§1.3 边沿触发型(D触发器) 边沿触发型(D触发器 触发器)

Q

5 6

Q

功能表

CP

↑

D D

Q Q D D

3

4

CP

1 2

结构:门 门 是输入控制 是输入控制, 结构 门1门2是输入控制 D和D在CP控制下引入 和 在 控制下引入 门3门4. 门 . 门2门4, 门1门3, 门5门6 门 门 门 组成3个基本触发器 个基本触发器. 组成 个基本触发器.

D

D触发器工作原理

Q

5

Q

6

I

"0"

"1"

III D

1

3

4

2

II CP

cp↑时, D=1, 门4=0, Q=1; 触发器Ⅱ记忆 cp↑ 触发器Ⅱ 维持门4输出为0; 输出和门3 "0"态,维持门4输出为0; 门4输出和门3相 阻塞输入D的变化对门3影响,维持门3 连,阻塞输入D的变化对门3影响,维持门3输 出为1. 此时即使D变化,也会保持维持门3 出为1. 此时即使D变化,也会保持维持门3输 出为1.因此 黄线称"维持1 阻塞0 因此, 出为1.因此,黄线称"维持1,阻塞0"线.

数据建立时间

Q

1 2

Q

D需要提前于CP形 需要提前于CP形 成互补数据,等候 在门3 在门3,4入口.

4

3

CP

5 6

D

数据保持时间

Data的撤除应该在 正跳变之后 Data的撤除应该在CP正跳变之后 的撤除应该在CP (Delay(Delay-FF)

CP D

tsu

th

2. 描述传输延迟的参数(Propogation)tpd 描述传输延迟的参数(Propogation)t

两种基本触发器的应用比较(5) 两种基本触发器的应用比较(5)

例:译码器输出到锁存器和D触发器 译码器输出到锁存器和 触发器

A B Y0 Y1 Y2 Y3 D0 D1 D2 D3 E Q0 Q1 Q2 Q3

D0 Q0 D1 Q1 D2 Q2 D3 CP Q3

CP

两种基本触发器的应用比较(6) 两种基本触发器的应用比较(6)

§1. 触发器-逻辑电路的记忆元件

§1.1 触发器工作原理(R-S基本触发器) 触发器工作原理(R- 基本触发器) 电位触发器(Latch,锁存器) §1.2 电位触发器(Latch,锁存器) 边沿触发器( 触发器) §1.3 边沿触发器(D触发器) 主从触发器( 触发器) §1.4 主从触发器(J-K触发器)

Q

Q

RD

CP D Q

RD SD

D CP

D触发器功能表

RD

0 1 1

SD

1 0 1

CP x x

D x x D

Q 0 1 D

Q

1 0

↑

D

(波形图见P73) 波形图见P73)

几种D 几种D 触发器集成电路器件

Number '74 '174 '171/'175 '273 '374/'377 '378 '379 Flip-Flop Type Dual Hex Quad Octal Octal Hex Quad D D D D D D D Output Features Pre-set,Clear Clear Clear Clear Output enable Output enable Output enable