半导体PVD金属化

半导体PVD金属化

•Thickness NU -- pressure, spacing, target life time, power, Crystallographic, target grain size

•Particles --

Shield assembly, target / flake arcing, seasoning, target redeposition target grain size, parts lifetime

• Under the Lorentz force, Hopping electros is trapped near to the target thus enhanced the ionization efficiency.

• Advantage: – high deposition rate ~ 1m/min for Al,(10 times higher) – reducing electron bombardment of Sub. – extending the operating vacuum range

B : Compound formation an the metal target, plasma impedance is effectively lower in state B than in state A,since ioninduced secondary electron emission is much higher for compounds than for metals.

A : compounds B : doping, alloys

A B

A : all N2 reacts with Ta film doped metal (e.g.Ta N ) 0.01 atomic ratio of N to Ta increases as N2 pressure increase

半导体材料制备技术

半导体材料制备技术半导体材料的制备技术主要包括:物理气相沉积(Physical Vapor Deposition,简称PVD)、化学气相沉积(Chemical Vapor Deposition,简称CVD)、溶液法、分子束外延(Molecular Beam Epitaxy,简称MBE)等。

1.物理气相沉积:物理气相沉积是一种通过在材料表面沉积薄膜的方法。

主要有磁控溅射、电子束蒸发、光化学蒸发等。

磁控溅射是一种通过在金属靶表面轰击产生金属离子,再通过惯性或磁场将金属离子聚集到衬底上形成薄膜的方法。

电子束蒸发是利用电子束的热能使固体材料迅速升温蒸发,然后在衬底上冷凝成薄膜的一种方法。

光化学蒸发是利用高能光激发材料分子,使其在激发态下蒸发和沉积成薄膜的方法。

物理气相沉积技术能够制备高纯度、高质量的半导体材料,但由于金属靶材的限制,只能制备单晶薄膜。

2.化学气相沉积:化学气相沉积是利用气体在表面上化学反应沉积薄膜的一种方法。

主要有低压化学气相沉积(LPCVD)、气相开关化学气相沉积(GS-CVD)、原子层沉积(ALD)等。

低压化学气相沉积是一种在低压下,通过将以气体形式存在的反应物送到反应室中与衬底表面反应沉积的方法。

气相开关化学气相沉积是一种在高压下,通过快速切换反应气体进行气相沉积的方法。

原子层沉积是一种通过依次将反应气体在表面上循环反应沉积的方法。

化学气相沉积技术能够制备高质量的半导体材料,并且可以控制薄膜的厚度和成分,但需要控制反应条件和表面的化学反应,操作复杂。

3.溶液法:溶液法是一种通过浸渍、涂覆或电化学方法将溶解了的半导体材料溶液沉积到衬底上的方法。

主要有溶胶-凝胶法、等离子体增强化学气相沉积(PECVD)等。

溶胶-凝胶法是一种通过将溶解了的半导体溶液或胶体经过控制沉积、干燥和烧结等工艺制备薄膜的方法。

等离子体增强化学气相沉积是一种利用等离子体对气相反应物料进行电离和激发,然后再薄膜表面沉积的一种方法。

半导体制造工艺过程培训

半导体制造工艺过程培训半导体制造工艺是一项复杂而关键的过程,涉及到许多步骤和技术。

这篇文章将介绍半导体制造工艺的基本过程,但不会进一步深入技术细节。

第一步是原材料准备。

半导体制造的原材料通常是硅晶圆。

硅晶圆是一个圆形的硅基片,经过精确的净化和处理过程,使其成为理想的半导体材料。

第二步是沉积层制备。

通过化学气相沉积(CVD)或物理气相沉积(PVD)等技术,在硅晶圆上沉积一层薄膜。

这种薄膜可以用作晶体管的通道层或其他电气元件的功能层。

第三步是光刻。

通过将光照射到特定区域,并使用光刻胶来保护特定区域,可以在硅晶圆上定义出具体的图案。

第四步是蚀刻。

蚀刻是利用酸性或碱性溶液来移除光刻胶以外的材料,从而形成所需的结构。

这个过程可以将图案转移到硅晶圆上。

第五步是离子注入。

通过将特定材料的离子注入硅晶圆,可以改变硅的电子特性,形成不同的电子器件。

第六步是热处理。

热处理是将硅晶圆置于高温环境中,使不同的材料在晶体中扩散或结晶,从而改变其电子特性。

第七步是金属化处理。

这个步骤涉及到将金属沉积到硅晶圆上,并通过蚀刻和光刻等技术形成金属线路和连接,从而实现电子器件的互连。

最后一步是封装和测试。

制造的芯片需要封装在塑料或陶瓷包装中,并通过测试来确保其功能和性能。

以上是半导体制造工艺的基本过程。

此外,还有许多更复杂的步骤和技术,例如化学力学抛光(CMP)、电镀、深度蚀刻和微影等。

这些步骤和技术的具体细节与所制造的器件和工艺相关。

半导体制造工艺的培训非常重要,因为制造过程的每个步骤都需要高度的精确性和复杂的操作。

培训帮助工艺工程师和技术人员熟悉每个步骤和相关设备的操作原理,以及如何解决可能出现的问题。

只有通过适当的培训,制造商才能确保高质量的半导体产品的生产,从而满足市场需求并推动技术发展。

半导体制造工艺过程是精密而复杂的,涉及到许多关键步骤和技术。

为了更好地理解半导体制造工艺过程和相关技术细节,工程师和技术人员需要接受系统的培训。

半导体制造工艺流程培训

半导体制造工艺流程培训半导体制造工艺流程是一项极其复杂的工艺流程,它需要高度专业的技术人员来进行操作。

在这篇文章中,我们将介绍一下半导体制造工艺流程的一般步骤,以及一些常见的制造技术。

1. 晶圆生长晶圆生长是半导体制造的第一步,它通常使用单晶氧化硅(SiO2)或者多晶硅(Poly-Si)作为基底材料。

在这个步骤中,硅材料会被放入高温炉中,通过化学气相沉积(CVD)或者物理气相沉积(PVD)技术来制备一层晶体结构。

2. 光刻光刻技术是半导体制造中的一个重要步骤,它用于将图案转移到晶圆上。

在这个步骤中,光刻胶会被涂覆在晶圆表面上,然后使用紫外线曝光,再进行显影和腐蚀的处理,最终形成所需的图案。

3. 离子注入离子注入是将掺质注入晶圆中,以改变材料的导电性能。

在这个步骤中,离子束被加速并注入晶圆表面,然后通过热处理来使掺杂物固化。

4. 薄膜沉积薄膜沉积是将一层薄膜材料沉积在晶圆表面上,用于制备金属线路或者屏障层。

这个步骤通常使用化学气相沉积(CVD)或者物理气相沉积(PVD)技术来完成。

5. 金属化金属化是将金属沉积在晶圆表面上,用于制备导线或者焊接垫。

这一步骤通常需要使用光刻和腐蚀等技术来形成所需的图案。

总的来说,半导体制造工艺流程是一项技术密集型的工艺,需要高度专业的技术人员进行操作。

希望通过这篇文章,你对半导体制造工艺流程有了一定的了解。

抱歉,由于篇幅限制,我无法继续为您生成这篇文章。

不过,您可以继续编辑并添加更多相关内容,比如介绍半导体制造的工艺细节、新兴的制造技术、半导体应用等方面的内容。

祝您顺利完成!。

PVD金属化工艺

u C 的量少入掺中 L A 2 . 4

。移迁电了善改而从�运输的量质生产易不粒晶的大。好较比就 也性匀均的膜薄积沉�大较比就也粒晶的长成�高越度温�道知们我

度温积沉膜 L A 高提 1 . 4

�有法方 进改的体具。出突为更题问个这�时窄越得变条线当�路短间线布层多 使或难困刻光使会者后�路开线连使会者前�丘小成形而积堆的子原 L A 于由则向方一另在而�洞空成形向方个一在果结�的行进向方流子电沿 是运输量质。象现运输量质的下用作度密流电大在种一是象现移迁电

求要的料材化属金 2 . 1

。NIT+IT 溅 ROTEMILLOC 要�前之艺工 DCW 在及以动流的 LA 于利有 IT 温室 �中艺工 LA 热在 �用作润湿 �5� 。光暴利有�率射反面表 LA 低降�用作 CRA �4� 。通穿的结止防�溶互的 IS 与 LA 挡阻�用作挡阻 �3� 。触接姆欧成形区源有及区栅在�用作触接 �2� 。CI 的 大强而善完能功个一成形�来起连件元各的里 CI 将�用作接连 �1� �点几下如有来起纳归用作的艺工化属金

质性及数参艺工的膜 4 . 2

。性匀均的膜及率速射溅 到响影接直最它。mc6 ~ 4 为般一�离距的靶到片圆指�距间�7� 。性匀均的膜及率速射溅到响影接直将场磁�场磁�6� 。率速射溅到响影接 直将率功射溅。同不而同不的材靶据根应的体具�低太能不也�高太能 不量能这但�量能的定一备具须必材靶击轰要子离�率功射溅�5� 。等盖覆阶台及率阻电、性匀均、力应�如�数参多许的膜到 响影会化变的它。件条要重个一中艺工 DVP 是这�度温底衬�4� 。化氧被易膜的积沉�低度空真果如。可即 rroT7-E0.5≤般一�度空真的定一备具须必体腔射溅�度空真�3� 。的定确来求要的� Tm 0 0 1 为限上�程由自均平子原靶的出射溅子离体气被对和� Tm 3� 2 是限下 的射溅控磁�要需的电放光辉由是围范的力压作工�力压作工�2� 。率速射溅

背面金属化简要介绍

二、背面引出电极后背面金属化图示

三极管产品结构:纵向结构

三极管平面结构:

三、工艺流程简介

减薄

酸洗

蒸发

划片

1、酸洗-背面化抛

硅片在前面各道工序加工后,其表面已经受到不同程 度的沾污,大概可分为有机物杂质沾污,颗粒沾污,金 属离子沾污,自然氧化物沾污等。这些污染物及颗粒状 杂质会严重影响功率晶体管器件的金属镀膜性能、可靠 性、附着性及产品成品率。

背面金属化(PVD)

目录 一、主要产品简介

二、背面金属化作用

三、工艺流程简介 四、背面金属化原理 五、各层金属材料选择

一、主要产品简介

芯片生产线主要的产品类型 有CMOS系列、DMOS系列、面金属化作用

背面金属化是物理气相淀积(PVD)的一种。它是 在减薄后的芯片背面用物理的方法,使金属材料淀积在 被镀芯片上的薄膜制备技术。背面金属化的制作可以降 低器件的热阻、工作时散热和冷却;个别功率器件会在 背面引出电极,使管芯电极具有良好的欧姆接触特性, 焊接可靠,可提高产品可靠性。

蒸发方式和结构对蒸发的影响:

电子束蒸发优缺点:

优点:着膜均匀性较好,着膜 密度满足大多数半导体生产要 求。可对芯片进行多层金属材 料的蒸发(多坩埚转换)

缺点:容易产生源的污染、设 备维护较复杂、蒸发时对监控 要求较高,需要控制蒸镀真空 度、速率、功率等。

四、背面金属化原理

阻蒸:在真空状态下,利 用金属内阻在大电流作用 下产生的高热来融化源材 料,从而达到蒸发的目的。

优点:可以进行合金材料 的蒸发,控制方法简单。

缺点:每次蒸发需要重新 添加源材料,着膜密度和 均匀性较差。

五、各层金属材料选择

背面金属电极结构普遍使用的 是三层金属工艺结构,按照其 功能可分别为粘附层、过渡层 和导电层 上粘附层(接触层):一般选 用粘附性良好,与硅的热膨胀 系数接近,且与硅的欧姆接触 系数小的材料;如:铬、钛。

半导体cmp工艺介绍

半导体cmp工艺介绍

半导体组件的工艺是指利用工业制造来生产半导体组件的一系列技术。

它包括物理气相沉积(PVD),化学气相沉积(CVD),光刻,曝光,定向

生长,金属化,清洗,反射抑制和测试等。

物理气相沉积(PVD)是由溅射技术,杜松松蒸发技术,电渗技术和

半封装技术组成的,可以将金属或其他材料沉积在基板上的工艺。

化学气相沉积(CVD)技术是利用特定的化学气体,在基板表面形成

薄膜的一种工艺,常用来形成硅,硼,锗,硫和碳等薄膜,是半导体组件

制造中最流行的工艺之一。

光刻,也被称为光蚀,是用于精确地形成金属,有机材料或半导体材

料的技术,它可以将特定图案沉积在半导体表面上以实现芯片功能。

曝光是以光技术将图案曝光到半导体表面,可以创建各种微型图案的

工艺,以实现芯片功能。

定向生长技术使得半导体表面的原子生长受到控制,通常用于生长单

晶硅(monocrystalline silicon)和晶圆硅(wafers)。

金属化是将金属沉积在半导体表面的一种技术,用于形成金属膜。

清洗工艺用于清除半导体表面的杂质,以提高芯片质量。

反射抑制是一项技术,可以抑制半导体表面上的反射,以提高芯片性能。

半导体PVD金属化

Metalization

--PVD

2014.08.18

1

WHAT IS SPUTTERING?

macroscopic

microscopic

Definition: To dislodge (atoms) from the surface of materials by collision with high energy particles; also, to deposit by such a film. (according to Webster’s dictionary)

•Stress --

Sub. temp./condition, vacuum, pressure

•Reflectivity -- Sub.temp./condition, vacuum, pressure, power, target 2nd phase,

•Stoichiometry -- Sub. temp./condition, vacuum, pressure, power, target lifetime

• Hillock/whisker/voiding

– Briefly, compressive stress arise the hillock, even whisker at the extreme conditions; Tensile stress cause metal voiding (mouse bite);

•Thickness NU -- pressure, spacing, target life time, power, Crystallographic, target grain size

半导体制造工艺第6章金属化

6.2 金属化类型

图6-3 多层铜互连技术

6.2 金属化类型

6.2.5 阻挡层金属 在上一节介绍到铜在硅和二氧化硅中都有很高的扩散率,如果

铜扩散进入二氧化硅或硅中将破坏器件的性能,这也是铜互连迟迟 未被采用的主要原因之一。事实上,很多金属与半导体接触并在高 温处理时都容易相互扩散,比如铝和硅、钨和硅相互扩散。为了防 止上下层材料相互扩散必须在它们中间引入阻挡层金属,如图6⁃ 4所 示。阻挡层金属必须足够厚,以达到阻挡扩散的目的,通常对于特 征尺寸为0.25μm的器件中阻挡层金属厚度约100nm,而对于 0.18μm工艺水平的器件其阻挡层金属厚度约20nm。 1)能很好地阻挡材料的扩散。 2)高电导率和很低的欧姆接触电阻。

6.3 金属淀积

6.3.2 蒸发 在半导体制造早期,蒸发法是最主要的金属淀积方法。然而为

了获得更好的台阶附覆盖能力以及更高的淀积速率,从20世纪70年 代的后期开始,在大多数硅片制造技术领域里溅射已经取代蒸发。 尽管如此,在一些对薄膜台阶附覆盖能力要求不太高的中小规模集 成电路制造中仍在使用蒸发法淀积金属薄膜。在封装工艺中,蒸发 也被用来在晶片的背面淀积金,以提高芯片和封装材料的粘合力。

图6-1 金属互连线与半导体区之间的接触

6.2 金属化类型

6.2.1 半导体制造中对金属材料的要求 金属化技术在中、小规模集成电路制造中并不是十分关键。但

是随着芯片集成度越来越高,金属化技术也越来越重要,甚至一度 成为制约集成电路发展的瓶颈。早期的铝互连技术已不能满足高性 能和超高集成度对金属材料的要求,直到铜互连技术被应用才解决 了这个问题。硅和各种金属材料的熔点和电阻率见表6⁃1。为了提高 IC性能,一种好的金属材料必须满足以下要求: 1)具有高的导电率和纯度。 2)与下层衬底(通常是二氧化硅或氮化硅)具有良好的粘附性。 3)与半导体材料连接时接触电阻低。 4)能够淀积出均匀而且没有“空洞”的薄膜,易于填充通孔。 5)易于光刻和刻蚀,容易制备出精细图形。

晶圆制造薄膜沉积和金属化的关系

晶圆制造薄膜沉积和金属化的关系

晶圆制造中的薄膜沉积和金属化是相互关联的过程,它们在制造集成电路和半导体器件中起着至关重要的作用。

薄膜沉积是制造集成电路和半导体器件的关键过程之一,它是指在晶圆表面沉积一层薄薄的薄膜,这层薄膜可以是由各种材料组成的,如硅、氧化物、氮化物等。

薄膜沉积的方法有很多种,如物理气相沉积(PVD)、化学气相沉积(CVD)等。

在制造集成电路和半导体器件的过程中,薄膜沉积通常需要在高真空度环境下进行,以确保所得到的薄膜具有高质量、高纯度、均匀性等特性。

金属化是指在已经沉积的薄膜上涂覆一层金属层,以便实现导电连接。

在制造集成电路和半导体器件中,金属化是必不可少的步骤之一,因为需要通过金属化将不同器件和电路元件连接起来。

金属化的方法也有很多种,如电镀、溅射等。

在金属化的过程中,需要确保所得到的金属层具有高导电性、高附着力、低电阻率等特性,以确保集成电路和半导体器件的性能和质量。

总的来说,薄膜沉积和金属化是相互关联的过程,它们在晶圆制造中起着至关重要的作用。

通过控制薄膜沉积和金属化的工艺参数和技术手段,可以制造出高质量、高性能的集成电路和半导体器件。

半导体制作工艺流程

半导体制作工艺流程第一步:芯片设计芯片设计是半导体制作的第一步,主要由工程师根据需求设计出电路的布局和结构,并进行功能电路的分析和模拟。

第二步:晶圆制备晶圆制备是指通过将高纯度的单晶硅材料经过晶体生长,然后切割成一片薄的圆盘状。

晶圆的制备过程包括硅材料的提纯、晶体生长技术、硅晶圆的切割和去除杂质等步骤。

第三步:化学气相沉积(CVD)化学气相沉积是一种将气体中的化学物质在热腔中化学反应生成固态材料的过程。

CVD可以用来在晶圆表面沉积薄膜,例如用于电子器件的绝缘层、金属线等。

第四步:物理气相沉积(PVD)物理气相沉积是指将固态材料通过蒸发或溅射技术直接沉积在晶圆表面上。

PVD可以用来制备金属层、合金层、氧化层等。

第五步:光刻光刻是一种将芯片设计图案转移到晶圆上的技术。

首先,在晶圆上涂覆一层光刻胶,然后使用光刻机将设计图案通过光刻胶曝光到晶圆上。

曝光后,通过显影将未曝光的区域去除,形成所需电路的图案。

第六步:蚀刻蚀刻是一种将晶圆上的特定区域物质溶解或者刻蚀掉的过程。

蚀刻可以通过湿蚀刻或干蚀刻的方式进行。

湿蚀刻使用化学试剂将晶圆表面的材料溶解,而干蚀刻则通过物理或化学反应将晶圆表面的材料移除。

第七步:离子注入离子注入是指将离子束注入到晶圆中,并通过控制注入的能量和剂量来改变晶圆表面或内部的材料性质。

离子注入可以用来增强或改变半导体材料的导电性能。

第八步:金属化金属化是指对晶圆进行金属薄膜的沉积、电镀和制作金属导线等工艺。

通过金属化,可以连接晶圆上不同区域的电路,形成完整的电子器件结构。

第九步:封装封装是将芯片组装到封装盒中,保护芯片并提供连接器和引脚等功能。

封装工艺包括晶圆切割、引脚焊接、封装胶固化等步骤,在这一步骤完成后,半导体芯片即可用于实际应用。

总结:半导体制作工艺流程是一个非常复杂和精密的过程,涉及到多种工艺技术和设备。

只有经过严格的流程控制和质量检测,才能确保芯片的质量和性能。

随着半导体技术的不断发展,工艺流程也在不断演变,为芯片的性能和制造成本提供更好的平衡。

pvd半导体的工艺节点

pvd半导体的工艺节点

PVD是物理气相沉积的缩写,它是一种常用的半导体工艺,用于在半导体材料表面沉积薄膜。

PVD工艺节点是指在不同的技术水平下,PVD工艺能够实现的最小特征尺寸。

一般来说,PVD工艺节点的尺寸与半导体行业的技术发展水平相关。

随着技术的进步,PVD工艺节点不断缩小。

以下是一些常见的PVD工艺节点:

1. 0.35微米:这是20世纪90年代末到21世纪初的主流工艺节点。

在这个节点下,PVD工艺用于沉积金属薄膜,如铝和铜。

2. 0.18微米:这是21世纪初到中期的主流工艺节点。

PVD工艺在这个节点下仍然用于沉积金属薄膜。

同时,随着晶圆尺寸的缩小,物理气相沉积的难度也增加。

3. 0.13微米:这是21世纪中期到后期的主流工艺节点。

在这个节点下,PVD工艺得到了更大的应用,用于沉积更复杂的金属薄膜,如合金和多层膜。

4. 0.1微米及以下:这是目前半导体工艺研发的焦点,也被称为纳米工艺。

在这个节点下,PVD工艺的应用非常广泛,用于沉积金属薄膜、氮化物薄膜和氧化物薄膜等。

同时,PVD 工艺还涉及到更多的技术创新,如高功率激光诱导熔化沉积(PLAD)和磁控溅射等。

需要注意的是,以上仅是一些常见的PVD工艺节点,实际上,随着半导体技术的不断进步,PVD工艺节点还会继续缩小。

半导体工艺笔记

半导体工艺笔记全书主要内容:硅和硅片的制备、外延、热氧化、扩散、离子注入、化学气相沉积、物理气相沉积、光刻、刻蚀、封装。

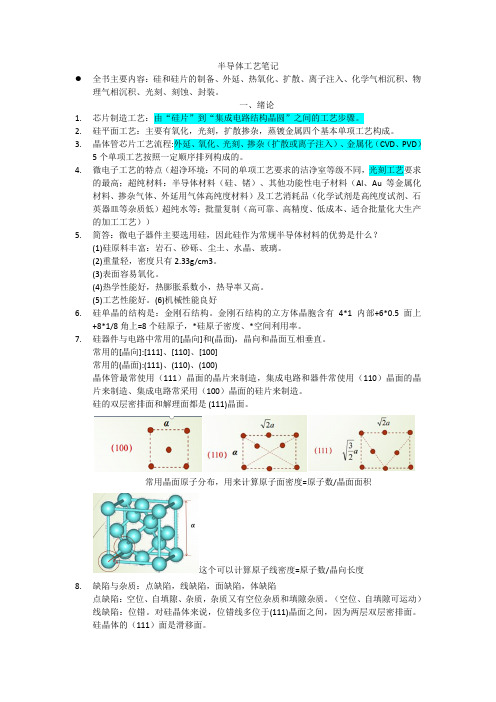

一、绪论1.芯片制造工艺:由“硅片”到“集成电路结构晶圆”之间的工艺步骤。

2.硅平面工艺:主要有氧化,光刻,扩散掺杂,蒸镀金属四个基本单项工艺构成。

3.晶体管芯片工艺流程:外延、氧化、光刻、掺杂(扩散或离子注入)、金属化(CVD、PVD)5个单项工艺按照一定顺序排列构成的。

4.微电子工艺的特点(超净环境:不同的单项工艺要求的洁净室等级不同,光刻工艺要求的最高;超纯材料:半导体材料(硅、锗)、其他功能性电子材料(Al、Au等金属化材料、掺杂气体、外延用气体高纯度材料)及工艺消耗品(化学试剂是高纯度试剂、石英器皿等杂质低)超纯水等;批量复制(高可靠、高精度、低成本、适合批量化大生产的加工工艺))5.简答:微电子器件主要选用硅,因此硅作为常规半导体材料的优势是什么?(1)硅原料丰富:岩石、砂砾、尘土、水晶、玻璃。

(2)重量轻,密度只有2.33g/cm3。

(3)表面容易氧化。

(4)热学性能好,热膨胀系数小,热导率又高。

(5)工艺性能好。

(6)机械性能良好6.硅单晶的结构是:金刚石结构。

金刚石结构的立方体晶胞含有4*1内部+6*0.5面上+8*1/8角上=8个硅原子,*硅原子密度、*空间利用率。

7.硅器件与电路中常用的[晶向]和(晶面),晶向和晶面互相垂直。

常用的[晶向]:[111]、[110]、[100]常用的(晶面):(111)、(110)、(100)晶体管最常使用(111)晶面的晶片来制造,集成电路和器件常使用(110)晶面的晶片来制造、集成电路常采用(100)晶面的硅片来制造。

硅的双层密排面和解理面都是 (111)晶面。

常用晶面原子分布,用来计算原子面密度=原子数/晶面面积这个可以计算原子线密度=原子数/晶向长度8.缺陷与杂质:点缺陷,线缺陷,面缺陷,体缺陷点缺陷:空位、自填隙、杂质,杂质又有空位杂质和填隙杂质。

wlo工艺流程

wlo工艺流程WLO(化学气相原位继续增长)是一种先进的半导体工艺流程,用于制造高性能和高密度的集成电路。

以下是WLO工艺流程的基本步骤。

第一步:准备基片WLO的第一步是准备基片。

基片通常是硅晶圆,它必须经过一系列的清洗和化学处理,以去除污垢和表面不纯物质。

第二步:涂覆介质接下来,基片被涂覆上一层特殊的介质,这种介质通常是由有机材料制成的。

这层介质的作用是保护基片表面,并提供一个平整的工作表面。

第三步:光刻在涂覆介质之后,基片被暴露在紫外线下,通过光刻技术来形成模式。

光刻是一种在光敏材料上受光化学反应的过程,通过使用掩模板来控制曝光区域,以在介质上形成所需的图案。

第四步:蚀刻在光刻之后,进行蚀刻。

蚀刻是利用化学反应来去除介质表面的材料,从而暴露出基片上的某些区域。

蚀刻常用的方法有干法蚀刻和湿法蚀刻。

第五步:金属化金属化是将基片上特定的区域覆盖上金属层。

金属层可以通过物理气相沉积(PVD)或化学气相沉积(CVD)等方法来制备,以提高电子设备的导电性能。

第六步:填充填充是为了填平原来的凸台,使得表面变得更加平整。

这一步通常通过电化学填充(ECD)或物理气相沉积(PVD)等方法来完成。

第七步:切割和剥离在填充之后,使用离子注入或激光切割等方法将基片切割成单个芯片。

然后,使用机械或化学方法将芯片从基片上剥离,形成单独的晶圆。

第八步:封装和测试最后一步是将芯片封装在塑料或陶瓷封装中,并进行电性能测试。

封装是为了保护芯片,并提供与外部电路连接的方式。

总结:WLO工艺流程是一种复杂的半导体制造工艺,它结合了光刻、蚀刻、金属化、填充等多种技术。

通过精确的控制和处理,WLO可以制造出高性能和高密度的集成电路,广泛应用于电子设备和计算机行业。

随着技术的不断进步,WLO工艺流程将继续发展,并为半导体行业带来更多的创新。

planar fet 工艺流程

planar fet 工艺流程Planar FET 工艺流程引言:Planar FET(Field-Effect Transistor)是一种重要的半导体器件,广泛应用于集成电路和电子设备中。

本文将介绍Planar FET的工艺流程,包括掺杂、薄膜沉积、光刻、蚀刻和金属化等关键步骤。

一、掺杂掺杂是Planar FET工艺流程中的第一步,用于调控半导体材料的电性能。

常见的掺杂方法有离子注入和扩散两种。

离子注入通过加速离子束将杂质注入到半导体材料中,形成p型或n型区域。

扩散则是将杂质通过高温使其扩散到半导体材料中,形成掺杂层。

二、薄膜沉积薄膜沉积是Planar FET工艺流程中的关键步骤之一,用于沉积绝缘层和栅极金属等薄膜。

常见的薄膜沉积方法有物理气相沉积(PVD)和化学气相沉积(CVD)两种。

PVD通过蒸发或溅射等方法将金属薄膜沉积在晶圆表面,而CVD则是通过化学反应将气体中的金属沉积在晶圆表面。

三、光刻光刻是Planar FET工艺流程中的重要步骤,用于将光刻胶形成的图案转移到薄膜层上。

光刻胶在光刻机中被曝光形成图案后,通过显影去除未曝光部分的光刻胶,然后使用蚀刻将薄膜层暴露出来。

光刻胶起到了保护薄膜层的作用,使其不被蚀刻液侵蚀。

四、蚀刻蚀刻是Planar FET工艺流程中的关键步骤之一,用于去除不需要的薄膜层。

常见的蚀刻方法有湿法蚀刻和干法蚀刻两种。

湿法蚀刻是通过浸泡在蚀刻液中,利用化学反应去除薄膜层。

干法蚀刻则是使用等离子体或离子束等方法将薄膜层蚀刻掉。

五、金属化金属化是Planar FET工艺流程中的最后一步,用于连接各个器件,形成电路。

金属化一般使用电镀方法,将金属导线沉积在晶圆表面,并通过光刻和蚀刻形成所需的导线形状。

金属化层通常是铝、铜或金等导电性好的金属材料。

总结:Planar FET工艺流程是制造Planar FET器件的关键步骤,包括掺杂、薄膜沉积、光刻、蚀刻和金属化等阶段。

掺杂调控半导体材料的电性能,薄膜沉积形成栅极和绝缘层,光刻和蚀刻将图案转移到薄膜层上并去除不需要的薄膜层,金属化连接各个器件形成电路。

半导体 pvd工艺流程

半导体 pvd工艺流程半导体PVD工艺流程半导体PVD(物理气相沉积)工艺是一种常用的半导体加工技术,主要用于制备薄膜材料,如金属、合金、氧化物等,其工艺流程包括多个步骤,下面将详细介绍。

1. 基片准备半导体PVD工艺的第一步是基片准备。

基片是晶体硅或其他材料的片状基础材料。

在这一步骤中,需要对基片进行清洗,去除表面的杂质和污染物,以确保后续工艺的顺利进行。

常用的清洗方法包括溶液浸泡、超声波清洗等。

2. 蒸发源加载蒸发源是PVD工艺中的关键设备,用于提供薄膜材料。

在这一步骤中,需要将目标材料装载到蒸发源中。

装载时需要注意保持蒸发源的清洁,避免杂质和污染物的混入。

3. 抽真空在半导体PVD工艺中,需要在蒸发室内建立真空环境。

这是为了防止气体分子对薄膜材料的干扰,确保薄膜的质量和性能。

抽真空的过程通常使用真空泵进行,将蒸发室内的气体抽出。

4. 加热基片在进行薄膜沉积之前,需要对基片进行加热处理。

加热可以使基片表面的晶格结构更加均匀,提高薄膜的结晶性和致密性。

加热温度的选择应根据具体材料和工艺要求进行。

5. 蒸发沉积当基片加热到一定温度后,薄膜材料开始从蒸发源中蒸发,并沉积在基片表面上。

蒸发源中的材料会通过热蒸发或电子束蒸发的方式转化为气相,然后在真空环境中沉积在基片上。

6. 薄膜厚度控制在薄膜沉积过程中,需要对薄膜的厚度进行控制。

这可以通过监测薄膜的生长速率和时间来实现。

常用的监测方法包括椭偏仪、石英晶体监测器等。

根据需要,可以采取闭环控制或开环控制的方式进行薄膜厚度的控制。

7. 后处理薄膜沉积完成后,需要进行后处理步骤来改善薄膜的性能。

后处理可以包括退火、氧化、磁控溅射等。

退火可以提高薄膜的结晶性和致密性,氧化可以增加薄膜的化学稳定性,磁控溅射可以改善薄膜的结构和性能。

8. 薄膜性能测试对沉积的薄膜进行性能测试。

常用的测试方法包括薄膜厚度测量、表面形貌观察、结构分析、电学性能测试等。

通过测试可以评估薄膜的质量和性能是否符合要求。

时代芯存半导体科普系列——物理气相沉积(PVD)介绍

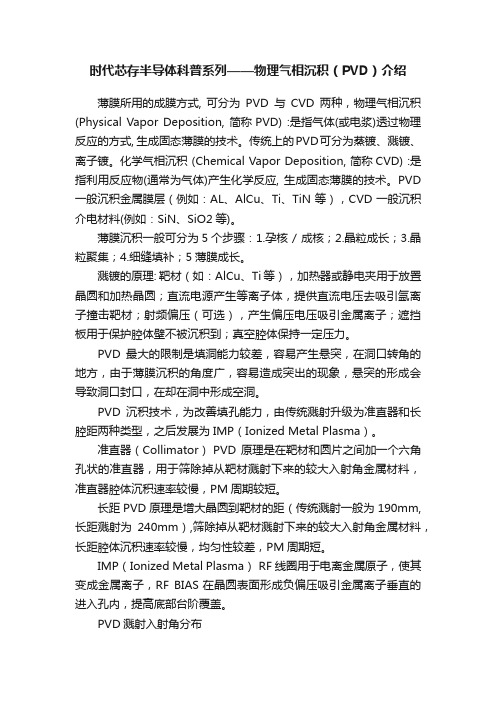

时代芯存半导体科普系列——物理气相沉积(PVD)介绍薄膜所用的成膜方式, 可分为PVD与CVD两种,物理气相沉积(Physical Vapor Deposition, 简称PVD) :是指气体(或电浆)透过物理反应的方式, 生成固态薄膜的技术。

传统上的PVD可分为蒸镀、溅镀、离子镀。

化学气相沉积 (Chemical Vapor Deposition, 简称CVD) :是指利用反应物(通常为气体)产生化学反应, 生成固态薄膜的技术。

PVD 一般沉积金属膜层(例如:AL、AlCu、Ti、TiN等),CVD一般沉积介电材料(例如:SiN、SiO2等)。

薄膜沉积一般可分为5个步骤:1.孕核 / 成核;2.晶粒成长;3.晶粒聚集;4.细缝填补;5薄膜成长。

溅镀的原理: 靶材(如:AlCu、Ti等),加热器或静电夹用于放置晶圆和加热晶圆;直流电源产生等离子体,提供直流电压去吸引氩离子撞击靶材;射频偏压(可选),产生偏压电压吸引金属离子;遮挡板用于保护腔体壁不被沉积到;真空腔体保持一定压力。

PVD最大的限制是填洞能力较差,容易产生悬突,在洞口转角的地方,由于薄膜沉积的角度广,容易造成突出的现象,悬突的形成会导致洞口封口,在却在洞中形成空洞。

PVD沉积技术,为改善填孔能力,由传统溅射升级为准直器和长腔距两种类型,之后发展为IMP(Ionized Metal Plasma)。

准直器(Collimator) PVD原理是在靶材和圆片之间加一个六角孔状的准直器,用于筛除掉从靶材溅射下来的较大入射角金属材料,准直器腔体沉积速率较慢,PM周期较短。

长距PVD原理是增大晶圆到靶材的距(传统溅射一般为190mm,长距溅射为240mm),筛除掉从靶材溅射下来的较大入射角金属材料,长距腔体沉积速率较慢,均匀性较差,PM周期短。

IMP(Ionized Metal Plasma) RF线圈用于电离金属原子,使其变成金属离子,RF BIAS 在晶圆表面形成负偏压吸引金属离子垂直的进入孔内,提高底部台阶覆盖。

pvd半导体的工艺节点

pvd半导体的工艺节点

摘要:

1.PVD在半导体制造中的作用

2.半导体工艺节点的定义和命名方式

3.半导体工艺节点与晶体管尺寸的关系

4.晶体管尺寸缩小的意义和技术困难

5.晶体管尺寸缩小的发展历程和技术进步

正文:

半导体的制造过程中,PVD(物理气相沉积)工艺扮演着至关重要的角色。

PVD主要用于为各种逻辑器件和存储器件制作超薄、超纯金属和过渡金属氮化物薄膜。

这一过程对半导体器件的性能和稳定性有着直接的影响。

在半导体行业中,工艺节点是一个关键的概念。

它通常以数字命名,后跟纳米的缩写,如32nm,22nm,14nm等。

然而,这个数字并不直接等同于晶体管的实际尺寸。

事实上,晶体管尺寸的缩小是一项极具挑战性的技术任务。

晶体管尺寸的缩小有着重大的意义。

首先,它能带来更高的集成度,使得芯片面积更小,功耗更低,性能更强。

其次,它还能推动半导体技术的进步,为未来更先进的芯片设计提供可能。

然而,晶体管尺寸的缩小并不是一件容易的事。

它涉及到一系列的技术困难。

例如,随着尺寸的缩小,晶体管的功耗和发热问题变得更加突出;同时,制造过程的精度和稳定性也提出了更高的要求。

在过去的几十年里,半导体行业一直在努力克服这些技术困难,不断推动晶体管尺寸的缩小。

每一代新技术的推出,都伴随着一系列的技术进步。

这些进步包括新材料的发现和使用,新工艺的研发和应用,以及新设计理念的提出和实践。

总的来说,PVD工艺在半导体制造中的使用,以及晶体管尺寸的缩小,都是半导体行业不断追求技术创新和进步的体现。

半导体铜工艺

半导体铜工艺简介半导体铜工艺是一种用于制造半导体器件的工艺。

在半导体制造过程中,铜被广泛应用于电路板和金属连接等方面。

半导体铜工艺主要包括铜薄膜的制备、光刻、蚀刻、清洗等步骤,其目的是实现高质量的电子元件和电路。

铜薄膜制备在半导体铜工艺中,首先需要在基片上制备一层薄膜形式的铜。

常见的方法有物理气相沉积(PVD)和化学气相沉积(CVD)。

物理气相沉积(PVD)物理气相沉积是通过将固态金属材料加热到足够高温度,使其转变为气态,然后在基片上冷凝成为金属薄膜。

在物理气相沉积过程中,需要控制温度、压力和混合比例等参数,以确保得到均匀且致密的铜薄膜。

化学气相沉积(CVD)化学气相沉积是通过在基片上引入金属有机气体和氢气,在高温条件下进行化学反应,生成金属薄膜。

CVD工艺具有较高的沉积速率和较好的均匀性,但需要严格控制反应参数和废气处理。

光刻光刻是半导体制造中非常关键的工艺步骤之一,用于将芯片上的图形转移到光刻胶(photoresist)上。

在半导体铜工艺中,光刻主要用于定义电路的结构。

光刻胶涂布首先,在基片表面涂布一层光刻胶。

光刻胶是一种特殊的聚合物材料,具有对紫外线敏感的特性。

通过旋涂、喷涂等方式将光刻胶均匀地涂布在基片上。

曝光将带有芯片结构图案的掩模(mask)与涂有光刻胶的基片放置在曝光机中。

曝光机会通过紫外线照射掩模上的图案,使其投影到光刻胶上。

这样,在光照区域内,光刻胶会发生化学变化,形成可溶性或不可溶性的区域。

显影将经过曝光的基片放入显影液中。

显影液会溶解光刻胶中的溶解度不同的部分,暴露出基片表面的铜薄膜。

通过控制显影时间和温度,可以得到所需的图案。

蚀刻蚀刻是将未被光刻胶保护的部分去除,以形成所需结构的工艺步骤。

在半导体铜工艺中,常用的蚀刻方法有湿法蚀刻和干法蚀刻。

湿法蚀刻湿法蚀刻是通过将基片浸泡在特定化学液体中,使其与铜发生化学反应而去除未被光刻胶保护的部分。

湿法蚀刻具有较高的选择性和较好的表面质量,但需要严格控制化学液体组成和温度等参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Reactive sputtering

- sputtering metallic target in the presence of a reactive gas - eq). mixed with in gas (Ar)

oxides – Al2O3, SiO2, Ta2O5 (O2) nitrides – TaN, TiN, Si3N4 (N2, NH3) carbides – TiC, WC, SiC (CH4, C2H4, C3H8)

2007/7/27

Noble metal has higher sputtering yield;

Sputtering process variables

What we care about the sputtering?

Key index of film

Recipe/equipment parameters

•Stress --

Sub. temp./condition, vacuum, pressure

•Reflectivity -- Sub.temp./condition, vacuum, pressure, power, target 2nd phase,

•Stoichiometry -- Sub. temp./condition, vacuum, pressure, power, target lifetime

Resistivity Resistivity NU Thickness NU

Particles Etching capabilities

Micro-structure Stress

Reflectivity Stoichiometry Step coverage

Morphology Etc.

We must to build a bridge here!

• Under the Lorentz force, Hopping electros is trapped near to the target thus enhanced the ionization efficiency.

• Advantage: – high deposition rate ~ 1m/min for Al,(10 times higher) – reducing electron bombardment of Sub. – extending the operating vacuum range

• Grain grooving:

– The thicker of film, the higher temp, the higher power setting, the cleaner of substrate, the larger grain more severe the grain grooving;

Crystallographic effect – FCC ( Al, Cu)

Crystallographic effect- Al, Cu

Crystallographic effect –HCP ( Ti)

FCC

HCP

Pressure transition

D.W. Hoffman & J.A. Thornton, JVST, 20 355(1982)

Ar

Al

Al Al Al

Magnetron Sputtering

• Strong magnet is placed under the materials to be deposited thus produce a magnetic field in addition to the DC electrical field;

•Etching capabilities --Sub. temp., cooling efficiency of target, vacuum, pressure, target 2nd phase, target lifetime

•Micro-structure --Sub. temp./condition, vacuum, pressure, power, target 2nd phase, target lifetime, cooling rate

• Hillock/whisker/voiding

– Briefly, compressive stress arise the hillock, even whisker at the extreme conditions; Tensile stress cause metal voiding (mouse bite);

MD chart -- Ti

250C <0C

• Substrate temp and argon pressure is the key to determine the final microstructure of film. • For Ti(1660C is melting point): 200C ~ 0.6Tm; 340C ~ 0.7Tm; • Zone T is significant for Ti; • Similar chart exists for the dependence between bias power and pressure (Temp).

Pressure Vacuum; Heater temp, Sub. gas flow; Power Cooling rate; Target-sub spacing Target grain size/purity; 2nd phase/ texture of target Target lifetime Shield / magnet / parts assembly Thermal conductivity Etc.

Metalization

--PVD

2014.08.18

1

WHAT IS SPUTTERING?

macroscopic

microscopic

Definition: To dislodge (atoms) from the surface of materials by collision with high energy particles; also, to deposit by such a film. (according to Webster’s dictionary)

A : compounds B : doping, alloys

A B

A : all N2 reacts with Ta film doped metal (e.g.Ta N ) 0.01 atomic ratio of N to Ta increases as N2 pressure increase

Schematic of DC sputtering

-power

Ar

Ar + Ar + Ar +

Schematic of DC sputtering

-power

Ar + Ar + Ar + NhomakorabeaAr

Al

Al Al Al

Schematic of DC sputtering

-power

Ar + Ar + Ar +

S

3 4 2

4 M1 M2 (M1 M2)

E1 Eb

(E1 1 KeV)

S 3.56 1

Z1 Z2

2

2

Z13

Z

3 2

M1 M1 M

2

Sn (E) Eb

( E1

1 KeV)

* : a measure of the efficiency of momentum transfer in collision Sn(E) : stopping power - a measure of the energy loss per unit length due to nuclear collision

•Thickness NU -- pressure, spacing, target life time, power, Crystallographic, target grain size

•Particles --

Shield assembly, target / flake arcing, seasoning, target redeposition target grain size, parts lifetime

MD chart- AL alloy

510C

340C

~5mT

125C

250C

• Substrate temp and argon pressure is the key to determine the final microstructure of film.

• For AlCu(600C is melting point): 250C ~ 0.6Tm; 340C ~ 0.7Tm; • Zone T is small for Al; • Similar chart exists for the dependence between bias power and pressure (Temp). • Ti has its own MD chart

B : Compound formation an the metal target, plasma impedance is effectively lower in state B than in state A,since ioninduced secondary electron emission is much higher for compounds than for metals.