优先权排队电路设计

优先裁决电路

优先裁决电路

该电路为优先裁决电路,主要功能是通过相应的发光二极管发光,来指示出先动作的电路。

例如在游泳比赛中用来自动裁决优先到达者,以下为电路动作分析:

1、初始状态电路初态时,A1、A2为0,复位开关S断开。

比赛开始前,按下复位开关S,RD全部输入信号为低电平,两个基本RS 触发器被清零,输出信号为0,电路不被接通,使发光二极管全部熄灭;同时两个输出信号经过或非门,产生信号为1的高电平输入与A1、A2同输入的与非门,经过触发器后仍产生低电平信号,电路保持稳定。

开关S断开后,RD由电源提供高电平,使清零端无效,电路依然稳定。

2、动作状态当第一个人游到终点,触发设在终点线上的光电检测管,A1输入高电平1,A2不动作。

两个高电平输入与非门变为0再输入触发器,输出为1,则接通发光二极管所在电路使其发光,表示首先到达终点的选手已经产生。

3、保持状态A1所在触发器产生的高电平与A2所在触发器清零后输出的低电平经过或非门后产生低电平,再次与A1(1)、A2(0)信号共同输入电路,产生结果为两个触发器保持原有状态,A1触发器为高电平,A2触发器为低电平。

此后即使其他选手到达终点,A2输入高电平,电路的输出结果也不会改变。

结果便是首先到达终点的选手的灯一直亮,其他选手再也不会亮,从而达到裁决优先到达终点选手的目的。

常用组合逻辑电路种类很多_主要有全加器、译码器、编码器、多路选择...

什么是编码?用文字、数字或符号代表特定对象的过程叫编码。

X/Y二-十进制编码器,同一时刻只允许一个输入端有信号。

不允许许多信号同时出现在输入端。

输入互相排斥。

处理电路111111111111111111111111为选通输出端:Y 00000001Y=EX只要有编码输出否则进行编码。

而且是反码输出。

0Y 1Y 2Y EX Y 0I 1I 2I 3I 4I 5I 6I 7I STS Y 74LS148将8线-3线优先编码器扩展为16线-4线优先编码器。

☆用两片8-3编码器组成16线-4线输出优先编码器。

/I 15优先权最高。

158当:I I 均无输入信号时,按照优先顺序的要求:70才允许对I I 的输入信号进行编码。

因此,只要将第(1)片的“无编码信号输入”信号Y S 作为第(2)片的选通输入信号/ST 即可。

当片(1)有编码信号输入时,片1的/Y EX =0,无编码信号输入时Y EX =1,正好用它输出编码的第四位,以区分8个高位输入信号和8个低位输入信号的编码。

编码输入的低三位应为两片输出/Y 2、/Y 1、/Y 0的逻辑或。

依照上面分析得出扩展逻辑电路图I 7I 6I 5I 4I 3I 2I 1I 0SY SY 0Y 1Y 2Y EX 74LS148(1)I 7I 6I 5I 4I 3I 2I 1I 0SY SY 0Y 1Y 2Y EX 74LS148(2)&&&&G 2G 3G 1G 0Z 0Z 1Z 2Z 3A 09A A 18A A 27A A 36A A 45A A 10A 11A 12A 13A 14A 1511111111111100111111110X 010*********X X 010********X X X 010*******X X X X 010010110X X X X X 01010010X X X X X X 0100000X X X X X X X 00111111111111011111X X X X X X X X 1/Y S /Y EX /Y 0/Y 1/Y 276543210 /SBCD A D B C B C A ++⋅+⋅+=)()()(BC D A BD C AB ++++=BCD A BD C AB +++⋅=BCD A BD C AB +⋅⋅⋅=00011110BC D A D B C B A ++⋅+⋅⋅+=)()()(C B D A BD C AB F +++++=BC D A D B C B C A ++⋅++⋅+=)())(()([]BC D A D B C B C A ++⋅+++++=)()()()(()BCD A BD C B C A ++⋅++=)(BCBD D C B D C A ABD C B A +++++=111111111可用:真值表法、配项法、卡诺图法求最小项表达式。

带优先权排队论模型简介应用案例

0.325 hour

0.033 hour

0.889 hour

0.048 hour

文档仅供参考,如有不当之处,请联系改正。

案例求解 3

即

W1

=W

= Wq

+

1 m

=

Lq l

+

1 m

=

P0(l m)s r s!(1- r)2 l

+

1 m

其中

r= l sm

åé s-1 (l / m)n (l / m)s 1 ù

➢ 非强占性优先权(Nonpreemptive Priorities)——虽然一种高优先级

旳顾客到达,也不能强制让一种正在接受服务旳低优先级顾客返回排队。

➢ 强占性优先权(Preemptive Priorities)——若有高优先级旳顾客到达,

服务员即中断对低优先级顾客旳服务,并立即开始为高优先级顾客服务。

N

l = å li

i=1

r= l m

k

å 【注:】这里假设了 li < sm,

i=1

从而使其能到达稳定状态。

文档仅供参考,如有不当之处,请联系改正。

计算公式 2

抢占性优先权(基于M/M/1)

1/ m

Wk = Bk-1Bk

for k=0,1,2,…,N

文档仅供参考,如有不当之处,请联系改正。

案例求解 3

文档仅供参考,如有不当之处,请联系改正。

案ቤተ መጻሕፍቲ ባይዱ求解 3

W1-1/μ W2-1/μ W3-1/μ

Preemptive Priorities

s=1

s=2

0.024 hour

0.154 hour

控制优先级逻辑电路

控制优先级逻辑电路是一种根据预设的优先级来决定信号处理顺序的电路设计。

这种电路在多个输入信号同时出现时,能够根据每个信号的优先级来选择性地处理。

以下是实现控制优先级逻辑电路的一些基本方法:

1. 编码器设计: 在编码器中,可以设置优先级使得当多个输入端同时为高电平时,只有优先级最高的信号被编码并输出。

2. Verilog编程: 在进行硬件描述语言(如Verilog)编程时,可以通过if-else-if语句来实现优先级控制,其中第一个if条件具有最高优先级,而最后一个else条件具有最低优先级。

3. 逻辑门电路: 利用CMOS或TTL门电路的基本逻辑单元来构建复杂的逻辑功能,其中也可以包含优先级控制逻辑。

这些门电路通过MOS管或BJT管工作在开关状态来实现其逻辑功能。

4. 多路复用器(MUX): 多路复用器可以根据选择信号的不同,从多个数据输入中选择一个输出。

通过合理安排选择信号的优先级,可以实现复杂的控制逻辑。

5. 状态机设计: 在有限状态机的设计中,可以通过不同状态之间的转移条件来体现优先级,确保系统按照既定的优先顺序进行状态转换。

6. 微控制器编程: 在微控制器或微处理器系统中,可以通过编程实现各种基于中断的优先级控制逻辑。

系统工程理论与方法_系统模拟

ห้องสมุดไป่ตู้

应用仿真技术的意义

1、经济

大型、复杂系统直接实验是十分昂贵的,如:空间飞行器的一 次飞行实验的成本约在1亿美元左右,而采用仿真实验仅需其成 本的1/10~1/5,而且设备可以重复使用。

2、安全

某些系统(如载人飞行器、核电装置等),直接实验往往会有 很大的危险,甚至是不允许的,而采用仿真实验可以有效降低 危险程度,对系统的研究起到保障作用。

20

2. 排队规则:服务台从队列中选取顾客进行服

务的顺序 (1) 损失制。服务台都已被先来的顾客占用,那么他 们就自动离开系统永不再来。(打电话) 等 待 制 。 ① 先 到 先 服 务 ( F CF S )/ ② 后 到 先 服 务 (LCFS)/③随机服务(RAND)/④优先权服务(PR) (2)容量有限/无限 (3) 队列单列 / 多列 ( 只讨论队列之间不互相转移,不 中途退出)

系统仿真分类

系统仿真根据模型不同:可以分为物理仿真、数学仿真和 物理—数学仿真(半实物仿真);

根据计算机的类别:可以分为模拟仿真、数字仿真和混合 仿真; 根据系统的特性:可以分为连续系统仿真、离散系统仿真; 根据仿真时钟与实际时钟的关系:可以分为实时仿真、欠 实时仿真(比实际时钟慢 )和超实时仿真等。

系统仿真

内容简介:

系统模拟(亦称系统仿真)是指通过建立和运行系统的数学 模型,来模仿实际系统的运行状态及其随时间变化的规律, 以实现在计算机上进行试验的全过程。这是近30年来发展起 来的一门新兴技术学科。公共管理的对象通常是社会、经济、 军事等复杂系统,一般都不能通过真实的实验来进行分析、 研究。因此,系统模拟技术就成为十分重要甚至必不可少的 工具。三种基本的模拟方法及其模型,即蒙特卡洛模拟方法、 排队模型、系统动力学模拟。通过蒙特卡洛(Monte Carlo)模拟可以具体了解管理系统模拟的基本原理及方法, 排队模型体现了离散事件系统模拟的特点与规律,而系统动 力学模拟则是一种可以广泛应用于公共管理决策及政策分析 的连续系统模拟方法。

基于STM32的嵌入式银行排队系统智能叫号终端设计

基于STM32的嵌入式银行排队系统智能叫号终端设计摘要:本文基于STM32嵌入式系统设计了一款智能叫号终端,该终端可以连接银行排队系统,自动调度顾客,实现优化银行服务的目的。

设计中采用了多种传感器感知顾客状态、LCD显示屏呈现顾客信息、蜂鸣器提示顾客等硬件,结合STM32芯片的高性能和低功耗,实现了高效、稳定的智能叫号功能。

该终端可以广泛应用于银行等有排队需求的场所,提高银行服务质量,优化客户体验。

关键词:STM32、嵌入式系统、智能叫号、银行排队系统、优化服务正文:一、绪论在银行等场所中,排队是常见的现象。

面对人多,服务慢的情况,人们常常感到烦躁,而优化服务,则是银行等企业的共同目标之一。

为此,我们设计了一款智能叫号终端,通过连接银行排队系统,并利用多种感知器实现自动、高效的叫号功能,提高服务效率、优化客户体验。

二、设计方案1.硬件设计:智能叫号终端主板采用STM32F103芯片,该芯片具有较高的性能和低功耗,适用于嵌入式系统应用。

为了感知顾客的队列情况,我们利用了多款传感器,包括红外传感器、超声波传感器等,通过对应的信号线连接至主板。

我们还在主板上设置了LCD显示屏,用以展现顾客的叫号信息,并在终端上加装了蜂鸣器,用于提示正在排队的顾客。

2.软件设计:智能叫号终端的软件设计分为两部分:嵌入式系统程序设计和PC机端程序设计。

(1)嵌入式系统程序设计:嵌入式系统程序可以实现接收银行排队系统的信息,解码数据,进行感知器状态检测,进而计算当前队列状态,自动发送叫号指令等功能。

(2)PC机端程序设计:PC机端程序是终端的图形化管理界面,主要用于设置叫号规则、任务下发等管理工作,方便银行工作人员进行管理和维护工作。

三、实验及结果在实验中,我们将终端连接银行排队系统,并进行了多次叫号实验。

实验结果表明,该终端具有较高的叫号效率和较低的误叫率,并且其LCD显示屏等硬件设计,可以方便顾客查询和排队。

四、结论基于STM32嵌入式系统的智能叫号终端,实现了银行排队系统的自动调度、顾客叫号等智能功能,并在实验中得到了验证。

优先权排队电路设计

千里之行,始于足下。

优先权排队电路设计优先权排队电路是一种常用的数字电路设计方法,用于管理并发处理的多任务系统。

它通过给每个任务分配一个优先级,然后根据优先级来确定任务的顺序执行,从而实现任务的排队和执行控制。

一般情况下,优先权排队电路设计包括两个主要部分:任务优先级编码和任务执行控制。

任务优先级编码将每个任务映射到一个唯一的二进制编码,用于比较任务的优先级。

任务执行控制根据任务的优先级编码和当前执行状态,确定下一个执行的任务。

任务优先级编码可以使用不同的方法实现,常见的有固定优先级编码和动态优先级编码。

固定优先级编码是将每个任务的优先级在设计时确定,并分配一个固定的二进制编码给每个任务。

这种编码方法简单明确,但不灵活,无法根据实际情况调整任务优先级。

动态优先级编码是根据任务的实时要求动态确定其优先级。

这种方法可以根据任务的实际情况灵活地调整任务的优先级,但需要更复杂的电路设计。

任务执行控制是优先权排队电路设计的核心部分。

任务执行控制根据当前执行状态和任务的优先级编码,确定下一个执行的任务。

最简单的任务执行控制是使用一个优先级比较电路和一个多路选择器。

优先级比较电路用于比较两个任务的优先级,并输出优先级高的任务的编码。

多路选择器用于根据优先级编码和当前执行状态,选择下一个执行的任务。

除了基本的优先权排队电路设计,还可以根据具体应用的需求进行扩展和改进。

例如,可以加入中断控制功能,以便处理紧急任务或异常情况。

还可以加入循环任务功能,使得一组任务可以按照一定的顺序循环执行。

另外,还可以通过硬件实现任务调度算法,如最短作业优先调度算法、轮转调度算法等。

第1页/共2页锲而不舍,金石可镂。

总的来说,优先权排队电路设计是一种常用的数字电路设计方法,用于管理并发处理的多任务系统。

它通过给每个任务分配一个优先级,然后根据优先级来确定任务的顺序执行,从而实现任务的排队和执行控制。

在实际应用中,可以根据具体需求灵活地扩展和改进,以适应不同的应用场景。

优先权排队电路课程设计

河南工业职业技术学院电子技术基础设计题目:优先权排队电路课程设计姓名:小雨系别:电气工程系班级:电力1101学号:04指导老师:杨旭目录前言 (1)一、概述 (2)1、数字电路的分类 (2)2、组合逻辑电路的概念 (2)3、组合逻辑电路的结构特点 (2)二、集成门电路分析 (2)1、数字集成门电路介绍 (3)2、数字集成电路型号的组成 (3)三、用集成门电路的设计方法 (3)四、对优先编码器介绍 (3)五、优先权排队电路 (5)1、课程设计目的 (5)2、设计一个优先权排队电路要求 (5)3、优先权排队电路 (5)4、电路工作原理 (6)5、A,B,C,优先状态真值表 (7)6、A,B,C,输入状态图、 (7)7、设计波形图 (8)8、逻辑函数、逻辑图 (8)六、心得总结 (9)参考资料 (10)谢致 (11)前言-一、概述1、数字电路的分类在数字系统中,根据逻辑功能的不同,数字电路分为组合逻辑电路和时序逻辑电路两大类。

2、组合逻辑电路的概念:若一个数字逻辑电路在某一时刻的输出,仅仅取决于这一时刻的输入状态,而与电路原来的状态无关,则该电路称为组合逻辑电路。

3、组合逻辑电路的结构特点·只能由门电路组成·电路的输入与输出无反馈路径·电路中不包含记忆单元·中规模集成(MSI)电路已经是一个功能性逻辑部件,它的名称仅代表了它的主要用途,而不是全部用途。

在学习MSI电路时,主要应熟悉它的逻辑符号、逻辑功能和用途,对它的逻辑电路只需作一般性的了解即可。

二、集成门电路分析1、根据数字集成电路中包含的门电路或元、器件数量,可将数字集成电路分为小规模集成(SSI)电路、中规模集成MSI电路、大规模集成(LSI)电路、超大规模集成VLSI电路和特大规模集成(ULSI)电路。

小规模集成电路包含的门电路在10个以内,或元器件数不超过10个;中规模集成电路包含的门电路在10~100个之间,或元器件数在100~1000个之间;大规模集成电路包含的门电路在100个以上,或元器件数在1,000~10, 000个之间;超大规模集成电路包含的门电路在1万个以上,或元器件数在100,000~1,000,000之间;特大规模集成电路的门电路在10万个以上,或元器件数在1,000,000~10,000,000之间。

EDA技术与CPLD FPGA编程实验指导书

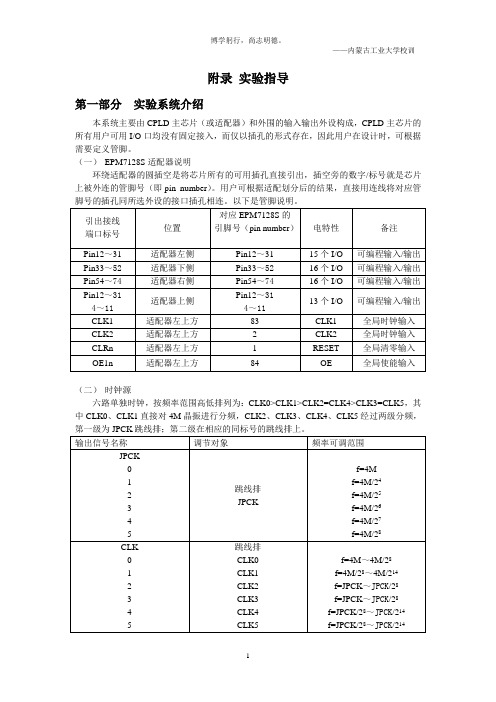

附录实验指导第一部分实验系统介绍本系统主要由CPLD主芯片(或适配器)和外围的输入输出外设构成,CPLD主芯片的所有用户可用I/O口均没有固定接入,而仅以插孔的形式存在,因此用户在设计时,可根据需要定义管脚。

(一)EPM7128S适配器说明环绕适配器的圆插空是将芯片所有的可用插孔直接引出,插空旁的数字/标号就是芯片上被外连的管脚号(即pin number)。

用户可根据适配划分后的结果,直接用连线将对应管脚号的插孔同所选外设的接口插孔相连。

以下是管脚说明。

引出接线端口标号位置对应EPM7128S的引脚号(pin number)电特性备注Pin12~31 适配器左侧Pin12~31 15个I/O 可编程输入/输出Pin33~52适配器下侧Pin33~5216个I/O 可编程输入/输出Pin54~74适配器右侧Pin54~7416个I/O 可编程输入/输出Pin12~31 4~11适配器上侧Pin12~314~1113个I/O 可编程输入/输出CLK1 适配器左上方83 CLK1 全局时钟输入CLK2 适配器左上方 2 CLK2 全局时钟输入CLRn 适配器左上方 1 RESET 全局清零输入OE1n 适配器左上方84 OE 全局使能输入(二)时钟源六路单独时钟,按频率范围高低排列为:CLK0>CLK1>CLK2=CLK4>CLK3=CLK5,其中CLK0、CLK1直接对4M晶振进行分频,CLK2、CLK3、CLK4、CLK5经过两级分频,第一级为JPCK跳线排;第二级在相应的同标号的跳线排上。

输出信号名称调节对象频率可调范围JPCK1 2 3 4 5 跳线排JPCKf=4Mf=4M/24f=4M/25f=4M/26f=4M/27f=4M/28CLK 0 1 2 3 4 5 跳线排CLK0CLK1CLK2CLK3CLK4CLK5f=4M~4M/28f=4M/28~4M/214f=JPCK~JPCK/28f=JPCK~JPCK/28f=JPCK/28~JPCK/214f=JPCK/28~JPCK/214(三)普通输入输出器件接口主要为开关、LED灯。

基于单片机的排队叫号系统设计

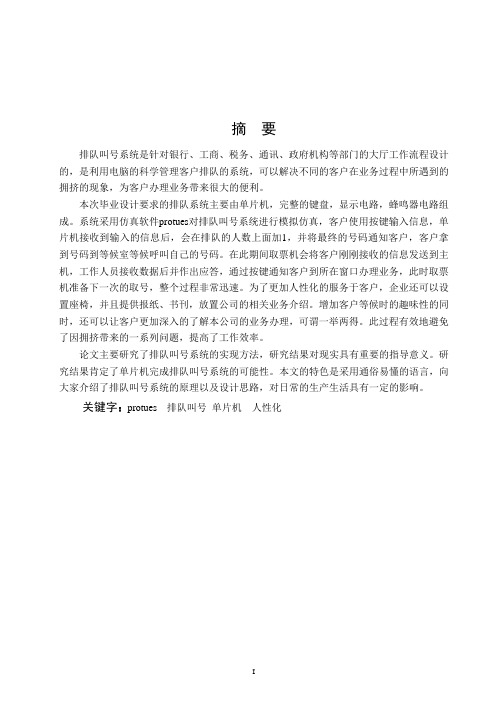

摘要排队叫号系统是针对银行、工商、税务、通讯、政府机构等部门的大厅工作流程设计的,是利用电脑的科学管理客户排队的系统,可以解决不同的客户在业务过程中所遇到的拥挤的现象,为客户办理业务带来很大的便利。

本次毕业设计要求的排队系统主要由单片机,完整的键盘,显示电路,蜂鸣器电路组成。

系统采用仿真软件protues对排队叫号系统进行模拟仿真,客户使用按键输入信息,单片机接收到输入的信息后,会在排队的人数上面加1,并将最终的号码通知客户,客户拿到号码到等候室等候呼叫自己的号码。

在此期间取票机会将客户刚刚接收的信息发送到主机,工作人员接收数据后并作出应答,通过按键通知客户到所在窗口办理业务,此时取票机准备下一次的取号,整个过程非常迅速。

为了更加人性化的服务于客户,企业还可以设置座椅,并且提供报纸、书刊,放置公司的相关业务介绍。

增加客户等候时的趣味性的同时,还可以让客户更加深入的了解本公司的业务办理,可谓一举两得。

此过程有效地避免了因拥挤带来的一系列问题,提高了工作效率。

论文主要研究了排队叫号系统的实现方法,研究结果对现实具有重要的指导意义。

研究结果肯定了单片机完成排队叫号系统的可能性。

本文的特色是采用通俗易懂的语言,向大家介绍了排队叫号系统的原理以及设计思路,对日常的生产生活具有一定的影响。

关键字:protues 排队叫号单片机人性化AbstractQueuing system is working in the lobby for banks, industry and commerce, taxation, telecommunications, government agencies and other departments of design , can solve all kinds of queues , crowded and chaotic phenomena for business customers in the encounter for customers bring great convenience for business .The design requirements for graduation to complete queuing system consists of master and slave system , keyboard, display part of the circuit , buzzer circuit, etc. . Protues system using simulation software to achieve the number queuing system's simulation, customers using the key input information , the microcontroller receives input information will be added to the above, a number of queued and will notify the customer the ultimate number, customers get numbers to the waiting room to wait for their call numbers. Opportunity tickets will be sent during this period the customer has just received information to the host , and the staff made the response data , inform customers to transact business through the key to where the window , then the next time the ticket dispensing machines ready to take a number , the whole process is very fast . For a more personalized service to customers, companies can also set the seat , and provide relevant business presentation newspapers, books , placing the company. Increase customer waiting time fun at the same time , it can also allow customers to more in-depth understanding of the company 's business process sense. This process effectively avoid a series of problems caused by congestion , improve work efficiency .Thesis, the implementation method queuing system , the results have important guiding significance for reality. The results confirmed the possibility of complete single-chip queuing system. Feature of this paper is the use of plain language , to introduce a queuing system principles and design ideas, has some impact on daily production and life .Key words: protues queuing microcontroller huma目录第1章绪论 (1)2.1 系统的基本功能和工作原理 (2)2.1.1 基本功能 (2)2.1.2 工作原理 (2)2.2 排队系统工作流程 (2)2.3 系统整体设计 (2)2.3.1 硬件概要设计 (2)2.3.2 软件概要设计 (3)第3章主要硬件参数 (4)3.1 STC89C52RC单片机 (4)3.1.1单片机的CPU结构 (4)3.1.2 STC89C52RC引脚功能说明 (4)3.1.3单片机的存储器 (6)3.1.4单片机最小系统设计 (7)3.2 液晶显示器 (8)3.2.1液晶显示器的原理及分类 (8)3.2.2 LCD1602液晶 (9)3.2.3 1602液晶模块的读写操作 (10)第4章系统流程图 (11)第5章系统电路及仿真结果 (12)5.1晶振电路 (12)5.2开关电路 (12)5.3 LCD1602电路 (13)5.4 蜂鸣器电路 (14)第6章仿真结果 (16)第7章系统程序 (18)第8章总结 (26)参考文献 (27)附录A 系统电路图 (28)致谢 (29)第1章绪论近年来,随着科学的发展和人们消费水平的提高,社会各界尤其是在办公商务服务业竞争的生活越来越大。

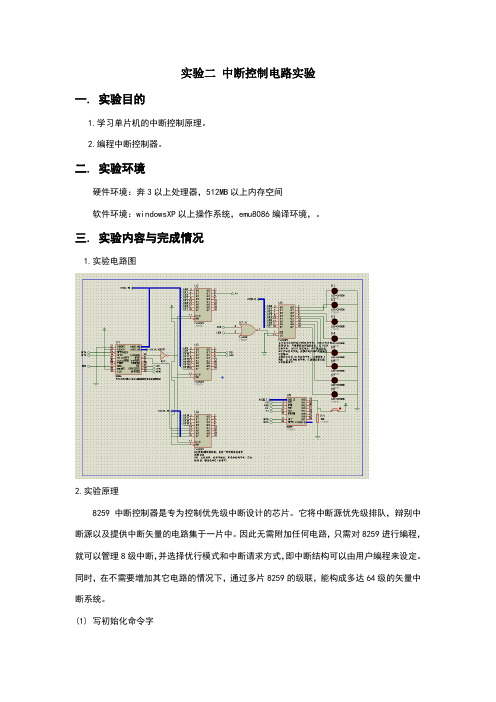

实验二 中断控制电路实验

实验二中断控制电路实验一. 实验目的1.学习单片机的中断控制原理。

2.编程中断控制器。

二. 实验环境硬件环境:奔3以上处理器,512MB以上内存空间软件环境:windowsXP以上操作系统,emu8086编译环境,。

三.实验内容与完成情况1.实验电路图2.实验原理8259中断控制器是专为控制优先级中断设计的芯片。

它将中断源优先级排队,辩别中断源以及提供中断矢量的电路集于一片中。

因此无需附加任何电路,只需对8259进行编程,就可以管理8级中断,并选择优行模式和中断请求方式,即中断结构可以由用户编程来设定。

同时,在不需要增加其它电路的情况下,通过多片8259的级联,能构成多达64级的矢量中断系统。

(1) 写初始化命令字* 写初始化命令字ICW1(A0=0),以确定中断请求信号类型,清除中断屏蔽寄存器,中断优先级排队和确定系统用单片还是多片。

* 写初始化命令字ICW2,以定义中断向量的高五位类型码。

* 写初始化命令字ICW3,以定义主片8259A中断请求线上IR0~IR7有无级联的8259A从片。

第i位=0,表明IRi引脚上无从片第i位=1,表明IRi引脚上有从片* 写初始化命令ICW4,用来定义8259A工作时用8085模式,还是8088模式,以及中断服务寄存器复位方式等。

(2) 写控制命令字* 写操作命令字0CW1,用来设置或清除对中断源的屏蔽。

第i位=0,对应的中断请求IRi开放第i位=1,对应的中断请求IRi屏蔽注: OCW1如不写,则在初始化命令写入后,OCW1为全开放状态。

* 操作命令字OCW2,设置优先级是否进行循环、循环方式及中断结束方式。

注: 8259A复位时自动设置IR0优先权最高,IR7优先权最低。

* 操作命令字OCW3,设置查询方式、特殊屏蔽方式以及读取8259中断寄存器的当前状态。

(3) 8259A查询字通过OCW3命令字的设置,可使CPU处于查询方式,随时查询8259A有否中断请求,有则转入相应的中断服务程序。

数字系统设计答案 (2)

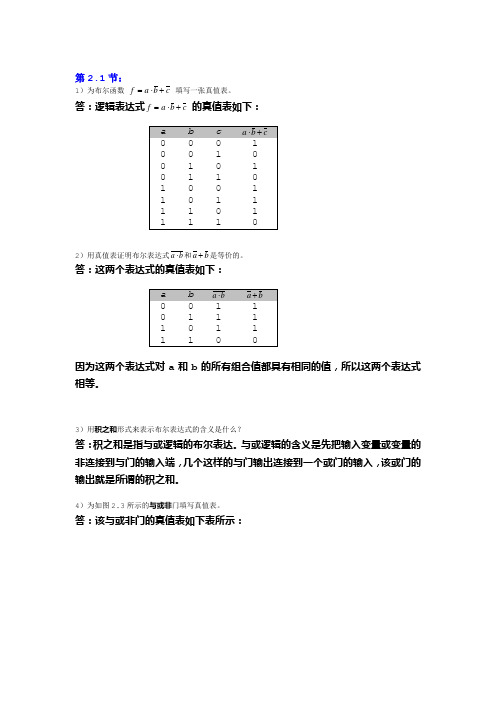

第 2.1 节:1)为布尔函数 f = a ⋅ b + c 填写一张真值表。

的真值表如下: 答:逻辑表达式 f = a ⋅ b + c 的真值表如下: a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1a ⋅b + c1 0 1 0 1 1 1 02)用真值表证明布尔表达式 a ⋅ b 和 a + b 是等价的。

答:这两个表达式的真值表如下: 这两个表达式的真值表如下: a 0 0 1 1 b 0 1 0 1a ⋅ba+b1 1 1 01 1 1 0的所有组合值都具有相同的值, 因为这两个表达式对 a 和 b 的所有组合值都具有相同的值,所以这两个表达式 相等。

相等。

3)用积之和 积之和形式来表示布尔表达式的含义是什么? 积之和积之和是指与或逻辑的布尔表达。

答:积之和是指与或逻辑的布尔表达。

与或逻辑的含义是先把输入变量或变量 的非连接到与门的输入端 几个这样的与门输出连接到一个或门的输入, 的输入端, 连接到一个或门的输入 的非连接到与门的输入端,几个这样的与门输出连接到一个或门的输入,该或 门的输出就是所谓的积之和 积之和。

门的输出就是所谓的积之和。

4)为如图 2.3 所示的与或非 与或非门填写真值表。

与或非答:该与或非门的真值表如下表所示: 该与或非门的真值表如下表所示:a 0 0 0b 0 0 0c 0 0 1d 0 1 0a ⋅b + c ⋅d1 1 10 0 0 0 0 1 1 1 1 1 1 1 10 1 1 1 1 0 0 0 0 1 1 1 11 0 0 1 1 0 0 1 1 0 0 1 11 0 1 0 1 0 1 0 1 0 1 0 10 1 1 1 0 1 1 1 0 0 0 0 05)在数字电路中,为什么要用缓冲器?缓冲器可以用来降低输出的负载, 答:缓冲器可以用来降低输出的负载,当输出必须驱动下一级逻辑门的很多个输 缓冲器可以用来降低输出的负载 入时,其负载是很重的。

优先权排队电路设计

电子技术课程设计优先权排队电路设计姓名:***专业:电力系统自动化班级:电力1101学号:0403110108概述 (3)一:设计目的 (4)二:设计要求 (4)三:设计内容 (5)(1)实验设计 (5)(2)电路设计 (6)(3)实验数据表 (6)总结 (7)参考文献 (8)数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

在asic设计和pld设计中组合逻辑电路设计的最简化是很重要的,在设计时常要求用最少的逻辑门或导线实现。

在asic设计和pld 设计中需要处理大量的约束项,值为1或0的项却是有限的,提出组合逻辑电路设计的一种新方法。

与逻辑表示只有在决定事物结果的全部条件具备时,结果才发生。

输出变量为1的某个组合的所有因子的与表示输出变量为1的这个组合出现、所有输出变量为0的组合均不出现,因而可以表示输出变量为1的这个组合。

组合逻辑电路的分析分以下几个步骤:(1)有给定的逻辑电路图,写出输出端的逻辑表达式;(2)列出真值表;(3)通过真值表概括出逻辑功能,看原电路是不是最理想,若不是,则对其进行改进。

使学生在学习了电子技术基础理论课和进行了基础实验后进一步提高运用电子技术基础掌握分析方法与分析实际电路的基本技能,了解基本逻辑单位电路在实际生活中的运用。

加强对电子技术的理解、学会查阅资料、方案比较以及设计、计算、制作、调试的技能增强分析、解决实际问题能力。

二:设计要求:设计一个优先权排队电路,其框图如下:排队顺序:A=1 最高优先级B=1 次高优先级C=1 最低优先级要求输出端最高只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

EDA实验

一、实验部分实验一仪器的熟悉及半加器的设计一、实验内容:(1)熟悉实验台(2)用VHDL设计半加器及或门,并给出程序设计、软件编译、仿真分析、硬件测试及详细实验过程。

(3)根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析和详细实验过程;给出程序分析报告、仿真波形图及其分析报告。

实验二简单组合电路的设计一、实验目的:熟悉Max+plusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验内容1:利用MAX+plusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出下图所示的仿真波形。

三、实验内容2:将多路选择器看成是一个元件mux21a,利用元件例化语句并将此文件放在同一目录。

以下是参考程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUXK ISPORT (a1,a2,a3,s0,s1 : IN STD_LOGIC;outy : OUT STD_LOGIC );END ENTITY MUXK;ARCHITECTURE BHV OF MUXK ISCOMPONENT MUX21APORT ( a,b,s : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT ;SIGNAL tmp : STD_LOGIC;BEGINu1 : MUX21A PORT MAP(a=>a2,b=>a3,s=>s0,y=>tmp);u2 : MUX21A PORT MAP(a=>a1,b=>tmp,s=>s1,y=>outy);END ARCHITECTURE BHV ;对上例分别进行编译、综合、仿真。

并对其仿真波形作出分析说明,并画出电路结构,说明该电路的功能。

四、实验报告:根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析和详细实验过程;给出程序分析报告、仿真波形图及其分析报告。

电气电子毕业设计158十线——四线优先编码器版图设计

引言随着科学技术的发展和高新技术的广泛应用,电子技术在国民经济的各个领域所起的作用越来越大,并深深地渗透到人们的生活、工作、学习的各个方面。

新的世纪已经跨入以电子技术为基础的信息化社会,层出不穷的电子新业务、电子新设施几乎无处不在、举目可见。

作为一名微电子学专业的大学生,尽快地学习和掌握电子技术基础知识和技能是一项基本的任务。

为了更好地将理论和实际相结合,也为了增强动手能力,同时加深对理论知识的理解,笔者进行了十线-四线优先编码器的设计。

1设计原理分析1.1 编码器介绍用数字或文字对一组事件进行编号排队的过程称为编码。

如邮政编码、宿舍房间编码、计算机键盘上键的编码等等。

编码器是以数字化信息将角度、长度、速度等物理量的信息以数字量0、1编码的方式输出的传感器,由于其具有高精度,大量程测量,反应快,数字化输出特点;体积小,重量轻,机构紧凑,安装方便,维护简单,工作可靠等优良特点,故成为当今工业控制系统备受青睐及不可或缺的一部分。

编码器是由若干个与非门组合而成的,输入端是各事件代号,如n个事件用Y0~Yn-1表示,输出端是相应的二进制各位值N0~Nk-1,2k-1=Yn-1。

编码器分二进制编码器和十进制编码器,各种译码器的工作原理类似,设计方法也相同。

集成二进制编码器和集成十进制编码器均采用优先编码方案。

下面介绍一些编码器的相关概念:二进制编码器:实现以二进制数进行编码的电子电路称二进制编码器。

n位二进制数可对2n个事件进行编码,如8位计算机中地址寄存器是8位,可对28=256个指令进行编码。

二—十进制编码器:用4位二进制对十进制的10个数字0~9进行编码的电路称二-十进制编码器,常用的是8421加权码,简称BCD码。

输入是10个有效数字0~9,输出是10个4位二进制代码0000~1001。

本次设计所做的10线-4线编码器就是其中一种。

优先编码器:在使用二进制编码器和二-十进制编码器中,当两个以上信号同时输入编码器时将产生错误码输出,而优先编码器则对输入信号依照规定的先后顺序进行编码。

中断请求串行判优先电路的设计与实现

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:院(系):计算机学院专业:班级:学号:姓名:指导教师:完成日期:年月日1.总体设计方案1.1设计原理主机与外部设备的信息交换方式主要有:程序查询方式,程序中断方式,DMA方式等。

程序中断方式的主要特点是:程序切换(程序转移)和随机性。

对于小数据量交换的场合,用程序中断方式是很方便和高效的。

程序中断方式是指:CPU在执行程序的过程中,如果因出现某种随机事件而收到中断请求,则暂时停止现行程序的执行,转去执行一段中断服务程序,以处理该事件,并在处理完毕后自动恢复程序的执行。

中断串行判优先电路,是通过链路排队器实现的,它是一种优先级管理的简单实现方案。

每个设备均有一个中断请求输入,优先级别高的设备屏蔽掉优先级别低的设备,以此实现按优先级排队,以实现中断响应的优先。

由于需要产生中断向量,所以在菊花链排队电路的基础上,再加入中断向量产生逻辑。

实用的中断控制器都可以实现对特定中断的屏蔽,所以在上述电路的基础上再加入中断屏蔽电路。

1.2设计思路题目要求设计的电路由中断请求触发器、中断向量寄存器和门电路等逻辑部件组成。

所以电路主要由链路排队器部分(用于中断响应信号INTA的传递或截取)和中断向量产生部分(用于生成当前中断请求中优先级最高的中断请求的中断向量)。

链路排队器部分应包括链路排队电路和中断汇总电路。

中断向量产生部分需要挑选出当前中断请求中优先级别最高的请求,所以一种简单的方案是采用优先编码器生成相应的中断向量。

中断源数目为8,所以只需要使用8-3优先编码器即可完成。

中断设备码用8位二进制数表示,但真正有用的设备码只包含在其低3位,高5位置0即可。

实现特定中断屏蔽功能,只需在上述基础上加入一个中断屏蔽寄存器,输入的中断请求在经过中断屏蔽寄存器过滤后再送菊花链排队部分和中断向量产生部分。

其设计框图如图1.1所示。

中断请求串行判优先电路链路排队器部分中断向量产生部分中断响应图 1.1 总体设计框图1.3 设计环境(1)硬件环境•伟福COP2000型计算机组成原理实验仪COP2000计算机组成原理实验系统实验箱及其配套软件组成。

微机原理与接口技术吉海彦主编机械工业出版社课后习题答案

第一章:答案:人们通常把运算器和控制器看做一个整体称为中央处理器。

随着大规模、超大规模集成电路技术的开展,在微型计算机中已将CPU继承为一个芯片,称为微处理器,通常也称微处理机!微型计算机是以微处理器为核心,加上由大规模集成电路制作的存储芯片〔RAM和ROM〕、i/o接口和系统总线组成的,该层次即使已安装了CPU和内存的条的主板。

微型计算机系统是以微型计算机为核心,在配以相应的外部设备、电源、辅助电路和控制微型计算机工作的软件系统而构成的完整计算机系统。

三者的相互关系:单纯的微处理器不是计算机,单纯的微型计算机也不是完整的微型计算机系统,他们都不能独立工作,只有计算机系统才是完整的数据处理系统,才具有实用意义。

1.2微型计算机是由硬件系统和软件系统组成的整体。

硬件系统是指计算机实际的物理设备,它包括运算器,控制器,存储器,输入接口和输出接口这五个根本局部和相应的外部设备。

运算器是完成数值运算和逻辑运算的部件;控制器是是存储器、运算器以及输入输出设备有序工作的设备;存放器组是在需要重复使用某些操作数或者中间结果时,就可以将他们暂时存放在存放器里,防止对存储器的频繁访问,从而缩短指令长度和指令执行时间,加快CPU的运算速度,同时也给编程带来方便;存储器是保存二进制信息,而且能快速对信息进行读写处理,分为外存和内存;软件系统:一般是指在计算机上运行的各类程序及其相应的文档的集合,硬件系统只有在软件系统的支撑下才能发挥其对数据的处理能力。

1.3总线是一组导线,用来在微机的各部件之间提供数据、地址和控制信息的传输通道。

总线分为三类1、地址总线2、数据总线3、控制总线微型计算机没执行一条指令都是分为三个阶段:取指令、分析指令和执行指令取指令阶段的任务是:根据程序计数器(PC)中的值从存储器里读出现行指令,送到指令存放器IR,然后PC自动加以,指向下一条指令地址。

分析指令阶段的任务:将IR中的指令操作码译码,分析其指令性质。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

优先权排队电路设计 The Standardization Office was revised on the afternoon of December 13, 2020

电子技术课程设计

优

先

权

排

队

电

路

设

计

姓名:李晓楠

专业:电力系统自动化

班级:电力1101

学号:

目录

概述 (3)

一:设计目的 (4)

二:设计要求 (4)

三:设计内容 (5)

(1)实验设计 (5)

(2)电路设计 (6)

(3)实验数据表 (6)

总结 (7)

参考文献 (8)

概述

根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做(简称)。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

在设计和设计中组合逻辑电路设计的最简化是很重要的,在设计时常要求用最少的逻辑门或导线实现。

在asic设计和pld设计中需要处理大量的约束项,值为1或0的项却是有限的,提出组合逻辑电路设计的一种新方法。

与逻辑表示只有在决定事物结果的全部条件具备时,结果才发生。

输出变量为1的某个组合的所有因子的与表示输出变量为1的这个组合出现、所有输出变量为0的组合均不出现,因而可以表示输出变量为1的这个组合。

组合逻辑电路的分析分以下几个步骤:

(1)有给定的逻辑电路图,写出输出端的逻辑表达式;

(2)列出真值表;

(3)通过真值表概括出逻辑功能,看原电路是不是最理想,若不是,则对其进行改进。

一:设计目的:

使学生在学习了电子技术基础理论课和进行了基础实验后进一步提高运用电子技术基础掌握分析方法与分析实际电路的基本技能,了解基本逻辑单位电路在实际生活中的运用。

加强对电子技术的理解、学会查阅资料、方案比较以及设计、计算、制作、调试的技能增强分析、解决实际问题能力。

二:设计要求:

设计一个优先权排队电路,其框图如下:

排队顺序:

A=1 最高优先级

B=1 次高优先级

C=1 最低优先级

要求输出端最高只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

三:设计内容:

用74LS00设计制作一个优先权排队电路。

输入为A、B、C,输出为Fa、Fb、Fc。

A=1,表示A有请求;Fa=1表示能够为A服务。

同样B=1表示B有请求;Fb=1,表示能够为B服务……。

A、B、C的排队顺序是:A=1,最高优先级;B=1,次优先级;C=1,普通优先级。

要求:输出端最多只能有一端为1,即只能为优先级较高的请求服务。

(1)实验设计:

根据题意得真值表(表2-9):

(2)电路设计:

图2-5 74LS00组成优先权排队电路图

(3)实验数据据(表2-10):

总结

整个课程设计过程我都认真地完成了,对此,我总结了以下几点:第一,四人一组,既加强了我们的动手能力,又让我们学会了团结一致,共同合作才能研究出最好的方案。

我们将理论联系实际,在交流中取得进步,从问题中提高自己。

第二,通过这次课程设计,使我受益颇多。

了解到课程实习设计是开端,连接是关键,测试是必须。

既巩固了课堂上学到的理论知识,又掌握了常用集成电路芯片的使用。

在此基础上学习了数字系统设计的基本思想和方法,学会了科学地分析实际问题,通过查资料、分析资料及请教老师和同学等多种途径,独立解决问题。

同时,也培养了我认真严谨的态度。

参考文献

[1] 《电子技术技能训练》杨元挺主编北京:高等教育出版社

[2] 《基础电子电路设计与实践》戴伏生主编北京:国防工业出版社

[3] 《电子电路设计与实践》姚福安主编济南:山东科学技术出版社

[4] 《电子技术基础课程设计》梁宗善主编武汉:华中理工大学出版社

[5] 《电子技术试验与实训》张友汉主编北京:高等教育出版社。