山东大学电子设计自动化试卷4

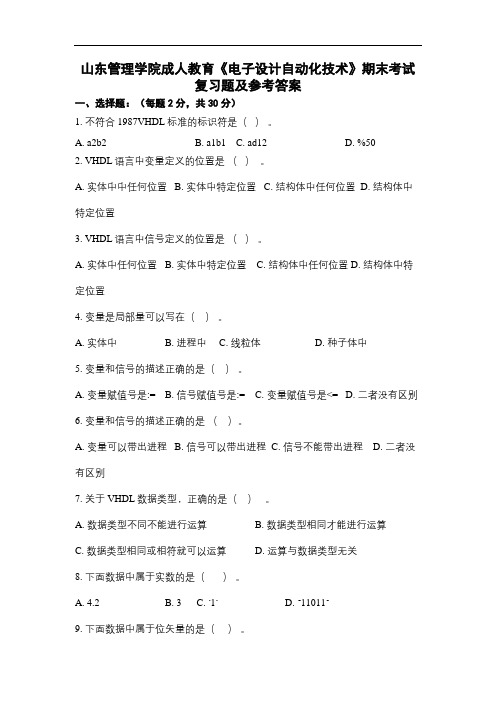

山东管理学院成人教育《电子设计自动化技术》期末考试复习题及参考答案

山东管理学院成人教育《电子设计自动化技术》期末考试复习题及参考答案一、选择题:(每题2分,共30分)1. 不符合1987VHDL标准的标识符是()。

A. a2b2B. a1b1C. ad12D. %502. VHDL语言中变量定义的位置是()。

A. 实体中中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置3. VHDL语言中信号定义的位置是()。

A. 实体中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置4. 变量是局部量可以写在()。

A. 实体中B. 进程中C. 线粒体D. 种子体中5. 变量和信号的描述正确的是()。

A. 变量赋值号是:=B. 信号赋值号是:=C. 变量赋值号是<=D. 二者没有区别6. 变量和信号的描述正确的是()。

A. 变量可以带出进程B. 信号可以带出进程C. 信号不能带出进程D. 二者没有区别7. 关于VHDL数据类型,正确的是()。

A. 数据类型不同不能进行运算B. 数据类型相同才能进行运算C. 数据类型相同或相符就可以运算D. 运算与数据类型无关8. 下面数据中属于实数的是()。

A. 4.2B. 3C. ‘1’D. “11011”9. 下面数据中属于位矢量的是()。

A. 4.2B. 3C. ‘1’D. “11011”10. 正确给变量X赋值的语句是()。

A. X<=A+B;B. X:=A+b;C. X=A+B;D. 前面的都不正确 11. 可以不必声11.明而直接引用的数据类型是()。

A. STD_LOGICB. STD_LOGIC_VECTORC. BITD. 前面三个答案都是错误的12. STD_LOGIG_1164中定义的高阻是字符()。

A. XB. xC. zD. Z13. STD_LOGIG_1164中字符H定义的是()。

A. 弱信号1B. 弱信号0C. 没有这个定义D. 初始值14. 使用STD_LOGIG_1164使用的数据类型时()。

2011年山东大学威海分校电子设计大赛试题

[A]温度测量仪表指导教师:杜清府一、基本要求1、测量范围:0~300℃,温度分辨率0.2℃以上。

[12bit ADC isrequired]2、能调整零点和满量程:在零点附近,如实际温度10℃,仪表显示温度12℃,可以通过调节零点参数,使仪表显示温度正确温度;同样,在满量程附近,如实际温度290℃,仪表显示温度288℃,通过调整满量程参数,使仪表显示正确温度。

3、测量速度达到1个读数/秒二、扩展要求1、能与计算机进行通讯,将仪表温度在计算机上显示出来。

[RS232/USB History Curve]2、仪表低功耗,普通3节1号电池(串联成4.5V)供电3个月以上。

[5Ah/3*30*24=2mA for average work current include active modeand sleep mode]3、引线电阻10Ω不影响测量结果。

三、所用主要元件(参考)1、单片机、LCD显示【LED is OK】2、铂电阻PT1003、双积分型AD转换器[Msp430f2003from Texas Instruments is a perfect selection for this project]16bit Sigma-DeltaUltralow-Power ConsumptionActive Mode220uA@1MHz2.2VStandby Mode0.5uAOff Mode0.1uA16Bit RISC Architecture with SPI and I2C10GPIOPackage:14PDIP&14TSSOP[B]电子台历的制作指导教师:郑亚民一、基本要求1、可实现公历、农历、节气、节日、天气、温度、湿度等信息2、具有闹钟和定时关机功能3、内置电源,接驳220V交流[Design a linear power supply with78xx Series regulator]二、扩展要求1、有时间提醒功能,提醒重要的日期或者时间2、有通讯录功能,可以添加、查阅联系人信息,包括、地址、电话、电子邮箱等[How to input these contacts]3、设计并制作适合电子台历外壳三、所用主要元件(参考)1、单片机2、LCM3、PS/2键盘or数字键盘0-9T9*在本题目中可能涉及220V交流电,请务必注意涉及安全[C]一、基本要求1、实现ARM 处理器读写Micro SD 卡的功能2、文件格式为FAT 或FAT32或NTFS 3、支持USB2.04、ARM 处理器可以通过USB 接口与计算机通信,交换数据信息二、具备的知识1、USB2.02、ARM 芯片相关3、FAT 文件系统三、所用主要元件(参考)1、LM3S8962[ARM Processor with Cortex M3core from TI]基于ARM 处理器的SD 卡读卡器指导教师:王小利[D]单管半导体收音机的设计与制作指导教师:王怡俊一、设计任务:设计并制作一个单管半导体收音机用来收听当地和附近城市的中波调幅无线电广播.二、基本要求:1、频率范围:535KHZ~1605KHZ2、灵敏度小于6mV/m(此项不测试,以能收听到附近城市的电台的个数和声音质量为考核项目)3、用两节5号电池供电4、用小型耳塞机收听三、主要材料:单联(或双联)可变电容器,型号:CBM-223,12-260pf可调2元天线磁棒1元晶体管90182个2元二极管2AP92个1元小型耳塞机及插1个2元塑料盒式1个5元其它(如扼流圈,天线线圈等)5元合计18元[E]5一、设计任务:设计并制作一个双路直流稳压电源.二、基本要求:1、能同时输出二路直流电压,输出电压范围:±2V~±30V ,连续可调,最大输出电流可达0.5A.2、纹波电压<15mV3、电压调整率<20mV4、有输出电压显示5、有简单的过流保护功能三、主要材料:30W,220V/双30V 变压器,LM317,LM337等约需90元*在本题目中涉及220V 交流电,请务必注意涉及安全直流稳压电源的设计与制作指导教师:王怡俊[F]6一、设计任务:用湿度传感器,设计一个湿度检测电路二、基本要求:1、湿度测量范围:5%RH ∽95%RH ,2、测量精度:±2%RH3、数字显示湿度测量值4、具有超限报警功能5、9V 电池供电三、主要材料:电容式湿度传感器HS1101约10.00元LM331约5.00元CMOS 555定时器1片、运放CF7413片、ADC 1片、若干电阻、电容、数码管等四、参考资料:数字电子技术、模拟电子技术、HS1101型湿度传感器的原理及使用方法湿度测量电路指导教师:李素梅湿度传感器电容/频率变换频率/电压变换A/D 转换数字显示[G]7流水线产品统计电路的设计指导教师:李素梅一、设计任务:设计并制作一个流水线上的产品数量统计电路。

山农成人教育 电子设计自动化期末考试复习题及参考答案-专升本

《电子设计自动化》复习题一、填空题1、SPLD有4种结构类型:_____________、_____________、_____________、_____________。

2、根据是否使用器件的真实特性,仿真分为:____________________、___________________。

3、利用EDA技术进行电路设计时,图形输入方式有___________________、___________________、___________________。

4、VHDL的基本描述语句包括一系列_________________和_________________两大基本描述语句。

5、41 =_______________________=_______________________=_______________________ (基于基的二进制、八进制、十六进制数)。

6、在VHDL语言中,注释符号为: _________________。

7、PLD的核心结构由4部分组成:______________________、______________________、______________________、______________________。

8、MAX3000A系列从逻辑结构上包含5部分:______________________、_____________________、_____________________、_________________________、____________________________。

9、62 =____________________=____________________=____________________ (基于基的二进制、八进制、十六进制数)。

10、VHDL的子程序有_______________和_______________两种类型。

电子设计自动化(eda)期末考试试题及答案

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLKTHEN

Q1<=Q1+1;

ENDPROCESS;

Q<=Q1;

ENDbhv;

四、设计,要求写出完整的vhdl代码。(65分)

1、16位硬件加法器,要求有进位输入和进位输出。(15分)

2、七段数码管译码显示电路设计(数码管共阳极接法)(12分)

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDER16IS

PORT(CIN:INSTD_LOGIC;

A:INSTD_LOGIC_VECTOR(15DOWNTO0);

B:INSTD_LOGIC_VECTOR(15DOWNTO0);

Sห้องสมุดไป่ตู้OUTSTD_LOGIC_VECTOR(15DOWNTO0);

IFCLK'EVENTANDCLK='1'THEN

Q1<=Q1+1;

ENDIF;

ENDPROCESS;

Q<=Q1;

ENDbhv;

每个2分

四、设计,要求写出完整的vhdl代码。(65分)

1、16位硬件加法器,要求有进位输入和进位输出。(15分)

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

(9)在vhdl中变量可在结构体和进程中定义和使用。()

(10)在进程中同一信号有多个赋值源,实际完成赋值的是最接近begin的信号。()

二、简答题(15分)

1、简述fpga/cpld的设计流程。(5分)

2、在vhdl中端口模式有那几种?并说明数据流动方向。(4分)

09级《电子设计自动化技术》考试A卷参考答案

五. 用 VHDL 设计一个分频电路,要求将 20MHZ 的方波信号变为 100KHZ 的方波 信号。 (13 分)

答: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; (2 分) ENTITY JYFP IS PORT( CLK_IN,RESET:IN STD_LOGIC; CLK_OUT:OUT STD_LOGIC ); END ENTITY JYFP; (3 分) ARCHITECTURE ART OF JYFP IS CONSTANT DIVIDE_PERIOD:integer :=50; (2 分) --将 20MHZ 的信号变为 100KHZ,分频常数为 20000000/100000=200 BEGIN DIVIDE_CLK:PROCESS(CLK_IN,RESET) IS VARIABLE CNT:INTEGER RANGE 0 TO 49; BEGIN IF (RESET = '1') THEN CNT := 0; CLK_OUT <= '0'; ELSIF RISING_EDGE(CLK_IN) THEN IF (CNT < (DIVIDE_PERIOD/2) THEN CLK_OUT <= '1'; --前 25 个周期输出为高电平 CNT := CNT + 1; ELSIF (CNT < (DIVIDE_PERIOD-1)) THEN CLK_OUT <= '0'; --后 25 个周期输出为低电平 CNT := CNT + 1; ELSE CNT := 0; END IF; END IF; END PROCESS DIVIDE_CLK; END ARCHITECTURE ART; (6 分)

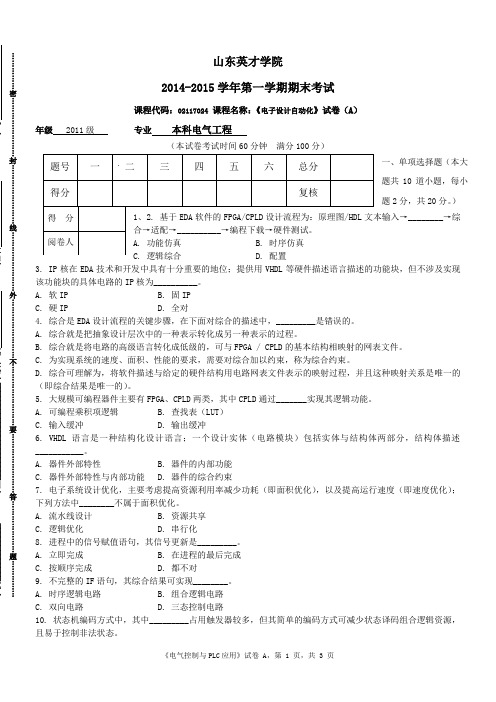

电子设计自动化试卷

2014-2015学年第一学期期末考试课程代码:02117024课程名称:《电子设计自动化》试卷(A)年级 2011级专业本科电气工程(本试卷考试时间60分钟满分100分)一、单项选择题(本大题共10道小题,每小题2分,共20分。

)________→综3. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__________。

A. 软IPB. 固IPC. 硬IPD. 全对4. 综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

A. 综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件。

C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。

D. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

5. 大规模可编程器件主要有FPGA、CPLD两类,其中CPLD通过_______实现其逻辑功能。

A. 可编程乘积项逻辑B. 查找表(LUT)C. 输入缓冲D. 输出缓冲6. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___________。

A. 器件外部特性B. 器件的内部功能C. 器件外部特性与内部功能D. 器件的综合约束7. 电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);下列方法中________不属于面积优化。

A. 流水线设计B. 资源共享C. 逻辑优化D. 串行化8. 进程中的信号赋值语句,其信号更新是_________。

A. 立即完成B. 在进程的最后完成C. 按顺序完成D. 都不对9. 不完整的IF语句,其综合结果可实现________。

自动化《模拟电子技术基础》 山东大学网络教育 模拟题 答案

模拟电子技术基础一、单项选择题:1.多数载流子为自由电子的半导体是__ B ____。

A 、P 型半导体B 、N 型半导体C 、杂质半导体D 、纯净半导体 2.半导体二极管的基本特性是__ B____。

A 、多子扩散B 、单向导电C 、少子漂移D 、载流子复合 3.若要使基本放大器不失真的放大交流信号,三极管必须工作在___C___状态。

A. 饱和 B. 截止 C. 放大 D.击穿4.对功率放大电路的基本要求是在不失真的情况下得到尽可能大的__B____。

A. 交流输出电压 B. 交流输出功率 C. 交流输出电流 D.输出电阻 5. 在直接耦合放大电路中,采用差动式电路的主要目的是__A____。

A. 抑制零点漂移B.克服交越失真C.提高电压放大倍数D.改变输出电阻6. 振荡器之所以能获得单一频率的正弦波输出电压,是依靠了振荡器中的___D___。

A. 稳幅环节 B. 基本放大电路 C. 正反馈网络 D.选频网络 7.场效应管放大器的突出优点是____A__。

A. 输入电阻很大B. 输出电阻小C. 电压增益大D.电流增益大8.放大电路中,如要增大输入电阻同时减小输出电阻,应引入_____C 反馈。

A.电流串联 B.电压并联 C.电压串联 D.电流并联二. 放大电路如图所示。

设C 1、C 2对交流可视为短路,三极管的U BE =0.7V ,β=50。

1. 求电路的静态工作点(I B 、I C 、U CE )。

2. 画出放大器的交流小信号等效电路。

3. 求电压放大倍数;输入电阻;输出电阻。

R U (+12V)+ o2K200Kc TCC +V 2KR bLR + U iC 1 C 2iR oR三.已知互补对称功率放大器电路如图所示,求解下列各题: 若输入电压u i =5V (有效值),求输出功率P o1. 忽略功率管的饱和压降。

估算该功率放大器的最大输出功率P om 。

2. 说明二极管D 1、D 2的作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.已知一个简单的波形发生器的数字部分系统框图如下图所示:

图中DOWNCNT、MYROM都是在MAX+PlusII中使用MegaWizard调用的LPM模块,其VHDL描述中Entity部分分别如下:

ENTITY DOWNCNT IS

PORT

(

clock: IN STD_LOGIC ;

q: OUT STD_LOGIC_VECTOR (5 DOWNTO 0)

);

END DOWNCNT;

ENTITY myrom IS

PORT

(

address: IN STD_LOGIC_VECTOR (5 DOWNTO 0);

q: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END myrom;

试用VHDL描述该系统的顶层设计(使用例化语句)。

第5页共5页

FULL <= '0'; --且输出溢出标志信号FULL为低电平

END IF;

END IF;

END PROCESS P_REG;

P_DIV: PROCESS(____________)

VARIABLE CNT2 : STD_LOGIC;

BEGIN

IF FULL'EVENT AND FULL = '1' THEN

16ELSE IF CLK'EVENT AND CLK = '1' THEN

17TMP <= TMP + 1;

18END IF;

19END PROCESS;

20OUTLED:PROCESS(TMP)

21BEGIN

22CASE TMP IS

23WHEN "0000" => LED7S <= "0111111" ;

02USE IEEE.STD_LOGIC_1164.ALL ;

03USE IEEE.STD_LOGIC_UNSIGNED.ALL;

04ENTITY LED7CNT IS

05PORT ( CLR: IN STD_LOGIC;

06CLK : IN STD_LOGIC;

07LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ;

BEGIN

IF___________________________THEN

IF CNT8 = "11111111" THEN

CNT8____________; --当CNT8计数计满时,输入数据D被同步预置给计数器CNT8

FULL <= '1'; --同时使溢出标志信号FULL输出为高电平

ELSE CNT8___________________; --否则继续作加1计数

D.16#E#E1

10.下列EDA软件中,哪一个不具有逻辑综合功能:________。

A.Max+Plus II

B.ModelSim

C.Quartus II

D.Synplify

第1页共5页

二、EDA名词解释,写出下列缩写的中文(或者英文)含义:(14分)

1.LPM

2.RTL

3.UART

4.ISP

5.IEEE

A.①③⑤B.②③④

C.②⑤⑥D.①④⑥

8.下列标识符中,__________是不合法的标识符。

A. State0B. 9moonC. Not_Ack_0D. signall

9.关于VHDL中的数字,请找出以下数字中最大的一个:__________。

A.2#1111_1110#

B.8#276#

C.10#170#

34END CASE;

35END PROCESS;

36END one;

在程序中存在两处错误,试指出,并说明理由:

提示:在MAX+PlusII 10.2上编译时报出的第一条错误为:

Error:Line 15: File ***/led7cnt.vhd: Type error: type in waveform element must be “std_logic_vector”

24WHEN Leabharlann 0001" => LED7S <= "0000110" ;

25WHEN "0010" => LED7S <= "1011011" ;

26WHEN "0011" => LED7S <= "1001111" ;

27WHEN "0100" => LED7S <= "1100110" ;

28WHEN "0101" => LED7S <= "1101101" ;

第行,错误:

改正:

第行,错误:

改正:

第2页共5页

五、VHDL程序设计:(16分)

设计一数据选择器MUX,其系统模块图和功能表如下图所示。试采用下面三种方式中的两种来描述该数据选择器MUX的结构体。

(a)用if语句。(b)用case语句。(c)用when else语句。

Library ieee;

Use ieee.std_logic_1164.all;

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;

B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;

C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;

D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

D.器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现________。

A.时序逻辑电路B.组合逻辑电路

C.双向电路D.三态控制电路

7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_________。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法

Entity mymux is

Port (sel : in std_logic_vector(1 downto 0);--选择信号输入

Ain, Bin : in std_logic_vector(1 downto 0);--数据输入

Cout : out std_logic_vector(1 downto 0) );

D: IN_________________(7 DOWNTO 0);

FOUT: OUT STD_LOGIC );

END;

ARCHITECTURE one OF____________IS

SIGNAL FULL : STD_LOGIC;

BEGIN

P_REG: PROCESS(CLK)

________________CNT8 : STD_LOGIC_VECTOR(________DOWNTO 0);

End mymux;

六、根据原理图写出相应的VHDL程序:(10分)

第3页共5页

七、综合题:(20分)

根据如下所示状态图及其状态机结构图,回答问题

1.试判断该状态机类型,并说明理由。

2.请问如何消除状态机输出信号毛刺?试列出至少两种方法,并说明理由。

3.试由b、c两图中任选一图写出其完整的VHDL程序。

4.进程中的信号赋值语句,其信号更新是_______。

A.按顺序完成;

B.比变量更快完成;

C.在进程的最后完成;

D.都不对。

5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___________。

A.器件外部特性;

B.器件的内部功能;

C.器件的综合约束;

CNT2________________; --如果溢出标志信号FULL为高电平,D触发器输出取反

IF CNT2 = '1' THEN FOUT <= '1';

ELSEFOUT <= '0';

END IF;

END IF;

END PROCESS P_DIV;

END;

四、VHDL程序改错:(10分)

01LIBRARY IEEE ;

29WHEN "0110" => LED7S <= "1111101" ;

30WHEN "0111" => LED7S <= "0000111" ;

31WHEN "1000" => LED7S <= "1111111" ;

32WHEN "1001" => LED7S <= "1101111" ;

33WHEN OTHERS => LED7S <= (OTHERS => '0');

6.ASIC

B

三、VHDL程序填空:(10分)

LIBRARY IEEE;-- 8位分频器程序设计

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE._____________________.ALL;

ENTITY PULSE IS

PORT ( CLK: IN STD_LOGIC;

08END LED7CNT;

09ARCHITECTURE one OF LED7CNT IS

10SIGNAL TMP : STD_LOGIC_VECTOR(3 DOWNTO 0);