★★MF210_DesignGuid_November06_2009

AutoCAD2009性能要求

系统要求∙Microsoft® Windows Vista™、Windows XP Professional 或 Home Edition (建议 SP2)、Windows 2000 SP4∙Microsoft® Internet Explorer 6(建议 SP2)或更高版本∙800 MHz 32 位 (x86) 或 64 位 (x64) 处理器(建议使用更快的处理器)∙512 MB RAM(对于 Microsoft Windows Vista 用户,建议使用 1 GB 或更大的 RAM)∙150 MB 用于安装的可用磁盘空间∙1024 x 768 VGA∙鼠标、轨迹球或兼容的定点设备∙适用于 64 位系统的 CD-ROM 驱动器、DVD-ROM 驱动器∙可选硬件:o支持二维和三维导航的3Dconnexion SpaceTraveler™o使用 NMEA 0183 标准进行通信的 GPS 设备集,即标准的 4800 波特率和 COM 端口(COM1 至 COM10)。

它包括:▪与 Microsoft Streets 和 Trips 2006 捆绑的 GPS 设备▪具有集成 GPS 设备的Panasonic Toughbook®▪通过 USB 连接的 GPS 设备▪通过 COM 端口进行蓝牙连接的 GPS 设备注意:如果您的计算机达不到这些系统需求,请卸载 Design Review。

新特性∙Freewheel。

使用 ShareNow 插件在 Autodesk Labs Project Freewheel 网站上共享 DWF 文件:/index.aspx。

(仅提供英文版本。

)∙查找:o查找文本。

在 Design Review 中打开的文件内定位文本。

o在部件中查找零件。

在复杂部件中快速确定特定零件。

∙添加标记前旋转二维图纸。

∙DWFx 是 Autodesk Design Review 2009 中新的默认文件格式。

ina210电流检测芯片1

R SHUNTV = (I R ) Gain + V OUT LOAD SHUNT REF´Product FolderSample &BuyTechnical Documents Tools &SoftwareSupport &CommunityINA210,INA211,INA212,INA213,INA214,INA215SBOS437G –MAY 2008–REVISED JULY 2014INA21x Voltage Output,Low-or High-Side Measurement,Bidirectional,Zero-Drift Series,Current-Shunt Monitors1Features3DescriptionThe INA210,INA211,INA212,INA213,INA214,and •Wide Common-Mode Range:–0.3V to 26V INA215are voltage-output,current-shunt monitors •Offset Voltage:±35μV (Max,INA210)that can sense drops across shunts at common-mode (Enables Shunt Drops of 10-mV Full-Scale)voltages from –0.3V to 26V,independent of the •Accuracy:supply voltage.Five fixed gains are available:50V/V,75V/V,100V/V,200V/V,500V/V,or 1000V/V.The –±1%Gain Error (Max over Temperature)low offset of the zero-drift architecture enables –0.5-μV/°C Offset Drift (Max)current sensing with maximum drops across the –10-ppm/°C Gain Drift (Max)shunt as low as 10-mV full-scale.•Choice of Gains:These devices operate from a single 2.7-V to 26-V –INA210:200V/V power supply,drawing a maximum of 100μA of supply current.All versions are specified over the –INA211:500V/V extended operating temperature range (–40°C to –INA212:1000V/V 125°C),and offered in an SC70package.The –INA213:50V/V INA210,INA213,and INA214are also offered in a thin UQFN package.–INA214:100V/V –INA215:75V/VDevice Information (1)•Quiescent Current:100μA (max)PART NUMBER PACKAGE BODY SIZE (NOM)•SC70Package:All ModelsSC70(6) 2.00mm ×1.25mm INA210•Thin UQFN Package:INA210,INA213,INA214UQFN (10) 1.80mm ×1.40mm INA211SC70(6) 2.00mm ×1.25mm 2ApplicationsINA212SC70(6) 2.00mm ×1.25mm •Notebook Computers SC70(6) 2.00mm ×1.25mm INA213•Cell PhonesUQFN (10) 1.80mm ×1.40mm •Telecom Equipment SC70(6) 2.00mm ×1.25mm INA214UQFN (10) 1.80mm ×1.40mm •Power Management INA215SC70(6)2.00mm ×1.25mm•Battery Chargers (1)For all available packages,see the orderable addendum at•Welding Equipmentthe end of the datasheet.Simplified SchematicINA210,INA211,INA212,INA213,INA214,INA215SBOS437G–MAY2008–REVISED Table of Contents8.3Feature Description (13)1Features (1)8.4Device Functional Modes (14)2Applications (1)9Application and Implementation (20)3Description (1)9.1Application Information (20)4Revision History (2)9.2Typical Applications (20)5Device Options (4)10Power Supply Recommendations (23)6Pin Configurations and Functions (4)11Layout (23)7Specifications (5)11.1Layout Guidelines (23)7.1Absolute Maximum Ratings (5)11.2Layout Example (23)7.2Handling Ratings (5)12Device and Documentation Support (24)7.3Recommended Operating Conditions (6)12.1Documentation Support (24)7.4Thermal Information (6)12.2Related Links (24)7.5Electrical Characteristics (6)12.3Trademarks (24)7.6Typical Characteristics (8)12.4Electrostatic Discharge Caution (24)8Detailed Description (12)12.5Glossary (24)8.1Overview (12)13Mechanical,Packaging,and Orderable8.2Functional Block Diagram (12)Information (24)4Revision HistoryNOTE:Page numbers for previous revisions may differ from page numbers in the current version.Changes from Revision F(June2014)to Revision G Page •Changed Simplified Schematic:added equation below gain table (1)•Changed V(ESD)HBM specifications for version A in Handling Ratings table (5)Changes from Revision E(June2013)to Revision F Page •Changed format to meet latest data sheet standards;added Pin Functions,Recommended Operating Conditions, and Thermal Information tables,Overview,Functional Block Diagram,Application Information,Power SupplyRecommendations,and Layout sections,and moved existing sections (1)•Added INA215to document (1)•Added INA215sub-bullet to fourth Features bullet (1)•Added INA215to simplified schematic table (1)•Changed title of Device Options table (4)•Added Thermal Information table (5)•Added INA215to Figure7 (8)•Added INA215to Figure15 (9)•Added INA215to Figure25 (16)Changes from Revision D(November2012)to Revision E Page •Deleted Package Marking column from Package/Ordering Information table (4)Changes from Revision C(August2012)to Revision D Page •Changed Frequency Response,Bandwidth parameter in Electrical Characteristics table (5)2Submit Documentation Feedback Copyright©2008–2014,Texas Instruments IncorporatedINA210,INA211,INA212,INA213,INA214,INA215 SBOS437G–MAY2008–REVISED JULY2014Changes from Revision B(June2009)to Revision C Page•Changed Package/Ordering table to show both silicon versions A and B (4)•Added silicon version B ESD ratings to Abs Max table (5)•Added silicon version B row to Input,Common-Mode Input Range parameter in Electrical Characteristics table (5)•Corrected typo in Figure9 (8)•Updated Figure12 (8)•Changed Input Filtering section (14)•Added Improving Transient Robustness section (19)Changes from Revision A(June2008)to Revision B Page•Added RSW package to device photo (1)•Added UQFN package to Features list (1)•Updated front page graphic (1)•Added RSW ordering information to Package/Ordering Information table (4)•Added RSW package pin out drawing (4)•Added footnote3to Electrical Characteristics table (5)•Added UQFN package information to Temperature Range section of Electrical Characteristics table (5)•Changed Figure2to reflect operating temperature range (8)•Changed Figure4to reflect operating temperature range (8)•Changed Figure6to reflect operating temperature range (8)•Changed Figure13to reflect operating temperature range (9)•Changed Figure14to reflect operating temperature range (9)•Added RSW description to the Basic Connections section (13)•Changed60μV to100μV in last sentence of the Selecting RS section (13)Changes from Original(May2008)to Revision A Page•Changed availability of INA211and INA212to currently available in Package/Ordering Information table (4)•Deleted first footnote of Electrical Characteristics table (5)•Changed Figure7 (8)•Changed Figure15 (9)Copyright©2008–2014,Texas Instruments Incorporated Submit Documentation Feedback3NC (1)V+NC(1)IN+IN+IN -IN -REF89105431276GND OUT123654OUT IN -IN+REF GND V+INA210,INA211,INA212,INA213,INA214,INA215SBOS437G –MAY 2008–REVISED JULY 20145Device OptionsPACKAGE PRODUCT GAIN (V/V)PACKAGE DESIGNATOR200SC70-6DCK INA210A 200Thin UQFN-10RSW 200SC70-6DCK INA210B 200Thin UQFN-10RSW INA211A 500SC70-6DCK INA211B 500SC70-6DCK INA212A 1000SC70-6DCK INA212B 1000SC70-6DCK 50SC70-6DCK INA213A 50Thin UQFN-10RSW 50SC70-6DCK INA213B 50Thin UQFN-10RSW 100SC70-6DCK INA214A 100Thin UQFN-10RSW 100SC70-6DCK INA214B 100Thin UQFN-10RSW INA215A75SC70-6DCK6Pin Configurations and FunctionsDCK PackageRSW Package SC70-6Thin UQFN-10(Top View)(Top View)(1)NC denotes no internal connection.These pins can be left floating or connected to any voltage between V–and V+.4Submit Documentation Feedback Copyright ©2008–2014,Texas Instruments IncorporatedINA210,INA211,INA212,INA213,INA214,INA215 SBOS437G–MAY2008–REVISED JULY2014Pin FunctionsPINNO.I/O DESCRIPTIONNAMEDCK RSWGND29Analog GroundAnalogIN–54,5Connect to load side of shunt resistor.inputAnalogIN+42,3Connect to supply side of shunt resistorinputNC—1,7—Not internally connected.Leave floating or connect to ground.AnalogOUT610Output voltageoutputAnalogREF18Reference voltage,0V to V+inputV+36Analog Power supply,2.7V to26V7Specifications7.1Absolute Maximum Ratings(1)over operating free-air temperature range(unless otherwise noted)MIN MAX UNIT Supply voltage,V S26VDifferential(V IN+)–(V IN–)–2626VAnalog inputs,V IN+,V IN–(2)Common-mode(3)GND–0.326VREF input GND–0.3(V S)+0.3VOutput(3)GND–0.3(V S)+0.3VInput current into any terminal(3)5mA Operating temperature–55150°C Junction temperature150°C(1)Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.These are stress ratingsonly,which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)V IN+and V IN–are the voltages at the IN+and IN–terminals,respectively.(3)Input voltage at any terminal may exceed the voltage shown if the current at that terminal is limited to5mA.7.2Handling RatingsMIN MAX UNITT stg Storage temperature range–65150°CHuman body model(HBM)ESD stress voltage(1)–20002000 Electrostatic dischargeV(ESD)Charged-device model(CDM)ESD stress voltage(2)–10001000V (version A)Machine model(MM)ESD stress voltage–200200Human body model(HBM)ESD stress voltage(1)–15001500 Electrostatic dischargeV(ESD)Charged-device model(CDM)ESD stress voltage(2)–10001000V (version B)Machine model(MM)ESD stress voltage–100100(1)JEDEC document JEP155states that500-V HBM allows safe manufacturing with a standard ESD control process.(2)JEDEC document JEP157states that250-V CDM allows safe manufacturing with a standard ESD control process.Copyright©2008–2014,Texas Instruments Incorporated Submit Documentation Feedback5INA210,INA211,INA212,INA213,INA214,INA215SBOS437G–MAY2008–REVISED 7.3Recommended Operating Conditionsover operating free-air temperature range(unless otherwise noted)MIN NOM MAX UNITV CM Common-mode input voltage12VV S Operating supply voltage5VT A Operating free-air temperature–40125°C7.4Thermal InformationINA210-INA215THERMAL METRIC(1)DCK(SC70)RSW(UQFN)UNIT6PINS10PINSRθJA Junction-to-ambient thermal resistance227.3107.3RθJC(top)Junction-to-case(top)thermal resistance79.556.5RθJB Junction-to-board thermal resistance72.118.7°C/WψJT Junction-to-top characterization parameter 3.6 1.1ψJB Junction-to-board characterization parameter70.418.7RθJC(bot)Junction-to-case(bottom)thermal resistance n/a n/a(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report,SPRA953.7.5Electrical CharacteristicsAt T A=25°C,V SENSE=V IN+–V IN–.INA210,INA213,INA214,and INA215:V S=5V,V IN+=12V,and V REF=V S/2,unless otherwise noted.INA211and INA212:V S=12V,V IN+=12V,and V REF=V S/2,unless otherwise noted.PARAMETER CONDITIONS MIN TYP MAX UNIT INPUTVersion A,T A=–40°C to125°C–0.326VV CM Common-mode input rangeVersion B,T A=–40°C to125°C–0.126VINA210,INA211,V IN+=0V to26V,V SENSE=0mV,INA212,INA214,105140dBT A=–40°C to125°CCommon-mode INA215CMRRrejection ratioV IN+=0V to26V,V SENSE=0mV,INA213100120dBT A=–40°C to125°CINA210,INA211,V SENSE=0mV±0.55±35μVINA212V O Offset voltage,RTI(1)INA213V SENSE=0mV±5±100μVINA214,INA215V SENSE=0mV±1±60μVdV OS/dT RTI vs temperature V SENSE=0mV,T A=–40°C to125°C0.10.5μV/°CV S=2.7V to18V,V IN+=18V,PSRR RTI vs power supply ratio±0.1±10μV/VV SENSE=0mVI IB Input bias current V SENSE=0mV152835μAI IO Input offset current V SENSE=0mV±0.02μA OUTPUTINA210200V/VINA211500V/VINA2121000V/VG GainINA21350V/VINA214100V/VINA21575V/VV SENSE=–5mV to5mV,E G Gain error±0.02%±1%T A=–40°C to125°CGain error vs temperature T A=–40°C to125°C310ppm/°CNonlinearity error V SENSE=–5mV to5mV±0.01%Maximum capacitive load No sustained oscillation1nF (1)RTI=referred-to-input.6Submit Documentation Feedback Copyright©2008–2014,Texas Instruments IncorporatedINA210,INA211,INA212,INA213,INA214,INA215 SBOS437G–MAY2008–REVISED JULY2014Electrical Characteristics(continued)At T A=25°C,V SENSE=V IN+–V IN–.INA210,INA213,INA214,and INA215:V S=5V,V IN+=12V,and V REF=V S/2,unless otherwise noted.INA211and INA212:V S=12V,V IN+=12V,and V REF=V S/2,unless otherwise noted.PARAMETER CONDITIONS MIN TYP MAX UNIT VOLTAGE OUTPUT(2)R L=10kΩto GND,T A=–40°C toSwing to V+power-supply rail(V+)–0.05(V+)–0.2V125°CR L=10kΩto GND,T A=–40°C toSwing to GND(V GND)+0.005(V GND)+0.05V125°CFREQUENCY RESPONSEC LOAD=10pF,INA21014kHzC LOAD=10pF,INA2117kHzC LOAD=10pF,INA2124kHz BW BandwidthC LOAD=10pF,INA21380kHzC LOAD=10pF,INA21430kHzC LOAD=10pF,INA21540kHzSR Slew rate0.4V/μs NOISE,RTI(1)Voltage noise density25nV/√Hz POWER SUPPLYV S Operating voltage range T A=–40°C to125°C 2.726VI Q Quiescent current V SENSE=0mV65100μAI Q over temperature T A=–40°C to125°C115μA TEMPERATURE RANGESpecified range–40125°COperating range–55150°CSC70250°C/WθJA Thermal resistanceThin UQFN80°C/W (2)See Typical Characteristic curve,Output Voltage Swing vs Output Current(Figure10).Copyright©2008–2014,Texas Instruments Incorporated Submit Documentation Feedback7INA210,INA211,INA212,INA213,INA214,INA215SBOS437G–MAY2008–REVISED 7.6Typical CharacteristicsThe INA210is used for typical characteristics at T A=25°C,V S=5V,V IN+=12V,and V REF=V S/2,unless otherwise noted.8Submit Documentation Feedback Copyright©2008–2014,Texas Instruments IncorporatedINA210,INA211,INA212,INA213,INA214,INA215 SBOS437G–MAY2008–REVISED JULY2014Typical Characteristics(continued)Copyright©2008–2014,Texas Instruments Incorporated Submit Documentation Feedback9INA210,INA211,INA212,INA213,INA214,INA215SBOS437G–MAY2008–REVISED Typical Characteristics(continued)10Submit Documentation Feedback Copyright©2008–2014,Texas Instruments IncorporatedTypical Characteristics(continued)IN-GNDV+8.1OverviewThe INA210-INA215are 26-V,common-mode,zero-drift topology,current-sensing amplifiers that can be used in both low-side and high-side configurations.These specially-designed,current-sensing amplifiers are able to accurately measure voltages developed across current-sensing resistors on common-mode voltages that far exceed the supply voltage powering the device.Current can be measured on input voltage rails as high as 26V while the device can be powered from supply voltages as low as 2.7V.The zero-drift topology enables high-precision measurements with maximum input offset voltages as low as 35µV with a maximum temperature contribution of 0.5µV/°C over the full temperature range of –40°C to 125°C.8.2Functional Block DiagramPower Supply8.3.1Basic ConnectionsFigure 23shows the basic connections of the INA210-INA215.The input pins,IN+and IN–,should be connected as closely as possible to the shunt resistor to minimize any resistance in series with the shunt resistor.Figure 23.Typical ApplicationPower-supply bypass capacitors are required for stability.Applications with noisy or high-impedance power supplies may require additional decoupling capacitors to reject power-supply noise.Connect bypass capacitors close to the device pins.On the RSW package options,two pins are provided for each input.These pins should be tied together (that is,tie IN+to IN+and tie IN–to IN–).8.3.2Selecting R SThe zero-drift offset performance of the INA210-INA215offers several benefits.Most often,the primary advantage of the low offset characteristic enables lower full-scale drops across the shunt.For example,non-zero-drift current shunt monitors typically require a full-scale range of 100mV.The INA210-INA215series gives equivalent accuracy at a full-scale range on the order of 10mV.This accuracy reduces shunt dissipation by an order of magnitude with many additional benefits.Alternatively,there are applications that must measure current over a wide dynamic range that can take advantage of the low offset on the low end of the measurement.Most often,these applications can use the lower gains of the INA213,INA214or INA215to accommodate larger shunt drops on the upper end of the scale.For instance,an INA213operating on a 3.3-V supply could easily handle a full-scale shunt drop of 60mV,with only 100μV of offset.Gain Error Factor =(1250´INTR)(1250S´´´R) + (1250R) + (R R)INT S INTRV+8.4Device Functional Modes8.4.1Input FilteringAn obvious and straightforward filtering location is at the device output.However,this location negates the advantage of the low output impedance of the internal buffer.The only other filtering option is at the device input pins.This location,though,does require consideration of the±30%tolerance of the internal resistances. Figure24shows a filter placed at the inputs pins.Figure24.Filter at Input PinsThe addition of external series resistance,however,creates an additional error in the measurement so the value of these series resistors should be kept to10Ωor less if possible to reduce impact to accuracy.The internal bias network shown in Figure24present at the input pins creates a mismatch in input bias currents when a differential voltage is applied between the input pins.If additional external series filter resistors are added to the circuit,the mismatch in bias currents results in a mismatch of voltage drops across the filter resistors.This mismatch creates a differential error voltage that subtracts from the voltage developed at the shunt resistor.This error results in a voltage at the device input pins that is different than the voltage developed across the shunt resistor.Without the additional series resistance,the mismatch in input bias currents has little effect on device operation.The amount of error these external filter resistor add to the measurement can be calculated using Equation2where the gain error factor is calculated using Equation1.The amount of variance in the differential voltage present at the device input relative to the voltage developed at the shunt resistor is based both on the external series resistance value as well as the internal input resistors,R3 and R4(or R INT as shown in Figure24).The reduction of the shunt voltage reaching the device input pins appears as a gain error when comparing the output voltage relative to the voltage across the shunt resistor.A factor can be calculated to determine the amount of gain error that is introduced by the addition of external series resistance.The equation used to calculate the expected deviation from the shunt voltage to what is seen at the device input pins is given in Equation1:where:•R INT is the internal input resistor(R3and R4),and•R S is the external series resistance.(1)Gain Error (%) = 100(100Gain Error Factor)-´Device Functional Modes (continued)With the adjustment factor equation including the device internal input resistance,this factor varies with each gain version,as shown in Table 1.Each individual device gain error factor is shown in Table 2.Table 1.Input ResistancePRODUCT GAIN R INT (k Ω)INA2102005INA2115002INA21210001INA2135020INA21410010INA2157513.3Table 2.Device Gain Error FactorThe gain error that can be expected from the addition of the external series resistors can then be calculatedbased on Equation 2:(2)For example,using an INA212and the corresponding gain error equation from Table 2,a series resistance of 10Ωresults in a gain error factor of 0.982.The corresponding gain error is then calculated using Equation 2,resulting in a gain error of approximately 1.77%solely because of the external 10-Ωseries ing an INA213with the same 10-Ωseries resistor results in a gain error factor of 0.991and a gain error of 0.84%again solely because of these external resistors.Control8.4.2Shutting Down the INA210-INA215SeriesWhile the INA210-INA215series does not have a shutdown pin,its low power consumption allows powering from the output of a logic gate or transistor switch that can turn on and turn off the INA210-INA215power-supply quiescent current.However,in current shunt monitoring applications.there is also a concern for how much current is drained from the shunt circuit in shutdown conditions.Evaluating this current drain involves considering the simplified schematic of the INA210-INA215in shutdown mode shown in Figure 25.NOTE:1-M Ωpaths from shunt inputs to reference and INA21x outputs.Figure 25.Basic Circuit for Shutting Down the INA210-INA215with a Grounded ReferenceNote that there is typically slightly more than 1-M Ωimpedance (from the combination of 1-M Ωfeedback and 5-k Ωinput resistors)from each input of the INA210-INA215to the OUT pin and to the REF pin.The amount of current flowing through these pins depends on the respective ultimate connection.For example,if the REF pin is grounded,the calculation of the effect of the 1-M Ωimpedance from the shunt to ground is straightforward.However,if the reference or op amp is powered while the INA210-INA215is shut down,the calculation is direct;instead of assuming 1M Ωto ground,however,assume 1M Ωto the reference voltage.If the reference or op amp is also shut down,some knowledge of the reference or op amp output impedance under shutdown conditions is required.For instance,if the reference source behaves as an open circuit when is not powered,little or no current flows through the 1-M Ωpath.Regarding the 1-M Ωpath to the output pin,the output stage of a disabled INA210-INA215does constitute a good path to ground;consequently,this current is directly proportional to a shunt common-mode voltage impressed across a 1-M Ωresistor.As a final note,when the device is powered up,there is an additional,nearly constant,and well-matched 25μA that flows in each of the inputs as long as the shunt common-mode voltage is 3V or higher.Below 2-V common-mode,the only current effects are the result of the 1-M Ωresistors.8.4.3REF Input Impedance EffectsAs with any difference amplifier,the INA210-INA215series common-mode rejection ratio is affected by any impedance present at the REF input.This concern is not a problem when the REF pin is connected directly to most references or power supplies.When using resistive dividers from the power supply or a reference voltage, the REF pin should be buffered by an op amp.In systems where the INA210-INA215output can be sensed differentially,such as by a differential input analog-to-digital converter(ADC)or by using two separate ADC inputs,the effects of external impedance on the REF input can be cancelled.Figure26depicts a method of taking the output from the INA210-INA215by using the REF pin as a reference.Figure26.Sensing the INA210-INA215to Cancel the Effects of Impedance on the REF Input8.4.4Using The INA210-INA215with Common-Mode Transients Above26VWith a small amount of additional circuitry,the INA210-INA215series can be used in circuits subject to transients higher than26V,such as automotive e only zener diode or zener-type transient absorbers (sometimes referred to as Transzorbs)—any other type of transient absorber has an unacceptable time delay. Start by adding a pair of resistors as a working impedance for the zener;see Figure27.Keeping these resistors as small as possible is preferable,most often around10Ω.Larger values can be used with an effect on gain that is discussed in the Input Filtering section.Because this circuit is limiting only short-term transients,many applications are satisfied with a10-Ωresistor along with conventional zener diodes of the lowest power rating that can be found.This combination uses the least amount of board space.These diodes can be found in packages as small as SOT-523or SOD-523.Shutdown Control RShutdownControlRFigure27.INA210-INA215Transient Protection using Dual Zener DiodesIn the event that low-power zeners do not have sufficient transient absorption capability and a higher power transzorb must be used,the most package-efficient solution then involves using a single transzorb and back-to-back diodes between the device inputs.The most space-efficient solutions are dual series-connected diodes in a single SOT-523or SOD-523package.This method is shown in Figure28.In either of these examples,the total board area required by the INA210-INA215with all protective components is less than that of an SO-8package, and only slightly greater than that of an MSOP-8package.Figure28.INA210-INA215Transient Protection using a Single Transzorb and Input Clamps+2.7V to +26VReference VoltageShuntSupplyOutput8.4.5Improving Transient RobustnessApplications involving large input transients with excessive dV/dt above 2kV per microsecond present at the device input pins may cause damage to the internal ESD structures on version A devices.This potential damage is a result of the internal latching of the ESD structure to ground when this transient occurs at the input.With significant current available in most current-sensing applications,the large current flowing through the input transient-triggered,ground-shorted ESD structure quickly results in damage to the silicon.External filtering can be used to attenuate the transient signal prior to reaching the inputs to avoid the latching condition.Care must be taken to ensure that external series input resistance does not significantly impact gain error accuracy.For accuracy purposes,these resistances should be kept under 10Ωif possible.Ferrite beads are recommended for this filter because of their inherently low dc ohmic value.Ferrite beads with less than 10Ωof resistance at dc and over 600Ωof resistance at 100MHz to 200MHz are recommended.The recommended capacitor values for this filter are between 0.01µF and 0.1µF to ensure adequate attenuation in the high-frequency region.This protection scheme is shown in Figure 29.Figure 29.Transient ProtectionTo minimize the cost of adding these external components to protect the device in applications where large transient signals may be present,version B devices are now available with new ESD structures that are not susceptible to this latching condition.Version B devices are incapable of sustaining these damage causing latched conditions so they do not have the same sensitivity to the transients that the version A devices have,thus making the version B devices a better fit for these applications.BYPASS 0.1µF9Application and Implementation9.1Application InformationThe INA210-INA215measure the voltage developed across a current-sensing resistor when current passes through it.The ability to drive the reference pin to adjust the functionality of the output signal offers multiple configurations,as discussed throughout this section.9.2Typical Applications9.2.1Unidirectional OperationFigure 30.Unidirectional Application Schematic9.2.1.1Design RequirementsThe device can be configured to monitor current flowing in one direction (unidirectional)or in both directions (bidirectional)depending on how the REF pin is configured.The most common case is unidirectional where the output is set to ground when no current is flowing by connecting the REF pin to ground,as shown in Figure 30.When the input signal increases,the output voltage at the OUT pin increases.9.2.1.2Detailed Design ProcedureThe linear range of the output stage is limited in how close the output voltage can approach ground under zero input conditions.In unidirectional applications where measuring very low input currents is desirable,bias the REF pin to a convenient value above 50mV to get the output into the linear range of the device.To limit common-mode rejection errors,TI recommends buffering the reference voltage connected to the REF pin.A less frequently-used output biasing method is to connect the REF pin to the supply voltage,V+.This method results in the output voltage saturating at 200mV below the supply voltage when no differential input signal is present.This method is similar to the output saturated low condition with no input signal when the REF pin is connected to ground.The output voltage in this configuration only responds to negative currents that develop negative differential input voltage relative to the device IN–pin.Under these conditions,when the differential input signal increases negatively,the output voltage moves downward from the saturated supply voltage.The voltage applied to the REF pin must not exceed the device supply voltage.。

22B112A(ShadowMoiree)

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer

JESD22-B108A measures device terminal coplanarity only at room temperature and cannot be used to predict warpage at elevated temperatures. The worst-case warpage may be at room temperature, maximum reflow temperature, or any temperature in-between; consequently, package warpage must be characterized during the entire reflow soldering thermal cycle. Critical engineering evaluations of the package and printed circuit board warpage should be conducted in the laboratory under simulated reflow conditions. For many packages, warpage can change with continued reflow cycles so this measurement should be made and reported for the first reflow cycle.

AIMB-210

Temperature Dimensions

* Minimum order quantity is required.

Industrial Motherboards

All product specifications are subject to change without notice Last updated : 09-Nov-2009

GbE LAN1: Realtek 8111C GbE LAN2: Realtek 8111C PCI

USB 2.0/1.1

HD Audio

ICH7M

PCIe x1

32-bit/33MHz PCI Bus SM Bus

LPC

Super IO Winbond W83627DHG

Fintek F81216D 4 RS-232

Online Download /products

Value-Added Software Services

Software API: An interface that defines the ways by which an application program may request services from libraries and/or operating systems. Provides not only the underlying drivers required but also a rich set of user-friendly, intelligent and integrated interfaces, which speeds development, enhances security and offers add-on value for Advantech platforms. It plays the role of catalyst between developer and solution, and makes Advantech embedded platforms easier and simpler to adopt and operate with customer applications.

NAU8822A_Design_Guide_Rev_2.0

Headphones/ Line drivers AUXOUT2 AUXOUT1 LHP RHP BTL Speaker LSPKOUT RSPKOUT

5-band EQ 3D

NAU8822AYG

NAU8822A Data Preliminary Rev 2.0

Page 1 of 89

January 25, 2011

CSB/GPIO1

VDDC

MCLK

DACIN

VDDB

VSSD

SCLK

Part Number NAU8822AYG

Dimension 5 x 5 mm

Package 32-QFN

Package Material Pb-Free

NAU8822A Design Guide Rev 2.0

Page 2 of 89

VSSSPK RSPKOUT AUXOUT2 AUXOUT1 RAUXIN LAUXIN MODE SDIO

RMICP RMICN

RLIN/GPIO3

NAU8822AYG 32-lead QFN RoHS

22 22 21 21 20 20 19 19 18 18 17 17

FS BCLK

ADCOUT

emPowerAudio™

Applications Personal Media Players Smartphones Personal Navigation Devices Portable Game Players Camcorders Digital Still Cameras Portable TVs Stereo Bluetooth Headsets

LAUXIN RAUXIN LLIN RLIN LMICN LMICP RMICN RMICP Digital Audio Interface Microphone Bias GPIO PLL I2S PCM Serial Control Interface Stereo Microphone Interface Input Mixer RADC LADC ADC Filter Volume Control High Pass & Notch Filters DAC Filter Volume Control Limiter RDAC Output Mixer LDAC

MF210

HSUPA PCI Express Mini Card MF210开发文档Revision1.2February 23, 2009产品名称:MF210公司名称:中兴通讯股份有限公司目录1概述 (2)2.执行标准 (2)3.技术说明 (3)3.1工作频段 (3)3.2承载业务 (3)3.3硬件技术参数 (4)4. 接口定义 (5)4.1 PCI Express Mini Card Specification (5)4.2 PIN Definition (5)5射频测试座 (6)5.1 射频测试座规格 (6)5.2 射频连接线 (6)5.3 主天线和分集连接器位置 (7)5.4射频测试座S参数测试 (7)5.4.1 主天线射频座技术参数 (7)5.4.2 分集天线射频座技术参数 (8)6.射频主要性能指标 (9)6.1 UMTS模式射频技术指标 (9)6.1.1最大发射功率 (9)6.1.2接收灵敏度 (9)6.2 GPRS/GSM/EDGE模式射频技术指标 (10)6.2.1发射输出功率 (10)6.2.2接收灵敏度 (10)7.天线 (11)7.1无源指标(推荐) (11)7.2有源指标(推荐) (11)7.3笔记本布局建议 (11)7.4天线尺寸及放置 (12)7.5分集天线设计 (12)1概述MF210是一款支持UMTS850(900)/1900/2100、GSM/GPRS/EDGE 850/900/1800/1900多频段HSUPA的PCI Express Mini Card无线网卡,可以提供移动环境下的WCDMA、GSM/GPRS、EDGE(EGPRS)和HSUPA高速数据接入服务。

注:UMTS850和UMTS900不能同时支持图1.1. MF210实物图2.执行标准[1] PCI Express Mini Card Electromechanical Specification Revision 1.2,October26 2007[2] 3GPP TS 34.121 User Equipment (UE) conformance specification; Radio transmission and reception (FDD)[3] 3GPP TS 05.05[4] 3GPP TS 34.124 Electromagnetic compatibility (EMC) requirements for Mobile terminals and ancillary equipment3.技术说明3.1工作频段HSUPA PCI Express Mini Card MF210网卡的工作频段如表3-1所示。

AFUWIN

AFUWINAMIBIOS8 ROM Utility User GuideAFUWINDocument Revision 1.0.1 – Aug 28, 2009NDA REQUIREDCopyright (c) 2008 American Megatrends, Inc.All Rights Reserved.American Megatrends, Inc.5555 Oakbrook ParkwaySuite 200Norcross, GA 30093This publication contains proprietary information which is protected by copyright. No part of this publication may be reproduced, transcribed, stored in a retrieval system, translated into any language or computer language, or transmitted in any form whatsoever without the prior written consent of the publisher, American Megatrends, Inc. American Megatrends, Inc. retains the right to update, change, modify this publication at any time, without notice. For Additional InformationCall American Megatrends BIOS Sales Department at 1-800-828-9264 for additional information.Limitations of LiabilityIn no event shall American Megatrends be held liable for any loss, expenses, or damages of any kind whatsoever, whether direct, indirect, incidental, or consequential, arising from the design or use of this product or the support materials provided with the product.Limited WarrantyNo warranties are made, either express or implied, with regard to the contents of this work, its merchantability, or fitness for a particular use. American Megatrends assumes no responsibility for errors and omissions or for the uses made of the material contained herein or reader decisions based on such use.Trademark and Copyright AcknowledgmentsAll product names used in this publication are for identification purposes only and are trademarks of their respective Companies.DisclaimerThis manual describes the operation of the AMIBIOS8 ROM Utilities. Although efforts have been made to insure the accuracy of the information contained here, American Megatrends expressly disclaims liability for any error in this information, and for damages, whether direct, indirect, special, exemplary, consequential or otherwise, that may result from such error, including but not limited to the loss of profits resulting from the use or misuse of the manual or information contained therein (even if American Megatrends has been advised of the possibility of such damages). Any questions or comments regarding this document or its contents should be addressed to American Megatrends at the address shown on the cover.American Megatrends provides this publication “as is” without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability or fitness for a specific purpose.Some states do not allow disclaimer of express or implied warranties or the limitation or exclusion of liability for indirect, special, exemplary, incidental or consequential damages in certain transactions; therefore, this statement may not apply to you. Also, you may have other rights which vary from jurisdiction to jurisdiction.This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. American Megatrends may make improvements and/or revisions in the product(s) and/or the program(s) described in this publication at any time. Requests for technical information about American Megatrends products should be made to your American Megatrends authorized reseller or marketing representative.Revision InformationOverviewAFUWIN is an updating system BIOS utility with command line and GUI interface. It has same parameters and behavior as AFUWIN, and further, GUI feature starting from v4.10can provide you a friendly environment to visualize BIOS update procedure. By the way, do not forget that target board MUST be AMIBIOS system while using this utility. FeaturesThis utility offers the following features:Small executable file sizeQuickly updateClear updating information and statusFully compatible with previous version (See Appendix B AFUWIN v3.xx Commands)RequirementsSupported Operating SystemAFUWIN Utility is supported in following operating system:Microsoft Windows 98Microsoft Windows MEMicrosoft Windows 2000Microsoft Windows NT 4.0Microsoft Windows XP/XP64Microsoft Windows PEMicrosoft Windows Vista 32/64Microsoft Windows PE 2.0 x64 (AFUWINx64.EXE)Microsoft Windows 7 32/64BIOS RequirementsSystem BIOS should have the followings:AMIBIOS CORE version 8.xx.xx.SMIFlash eModule with “8.00.00_SMIFlash-1.00.07” label or later.Token: SDSMGR_IN_RUNTIME = ON.Token: SMI_INTERFACE_FOR_SDSMGR_FUNC = ON.Operating System Driver RequirementsFollowing drivers for different operation system are required by this utility:UCOREVXD.VXD Driver for Microsoft Windows 98/MEUCORESYS.SYS Driver for Microsoft Windows NT/2000/XP/PEUCOREW64.SYS Driver for Microsoft Windows XP64 Getting Started InstallationCopies AFUWIN.EXE, AFUWINx64.EXE (for Microsoft Windows PE 2.0 x64), UCOREVXD.VXD, UCORESYS.SYS and UCOREW64.SYS to any storage location accessible by the host system and then run AFUWIN in command prompt. Remember that three files MUST be in same directory. For launching GUI mode, you can just double-click on the icon.UsageFor previous usage, see Appendix B AFUWIN v3.xx Commands to know details. AFUWIN [Option 1] [Option 2]……….OrAFUWINOrAFUWIN /MOrAFUWIN /MAIBIOS ROM File NameThe mandatory field is used to specify path/filename of the BIOS ROM filewith extension.CommandsThe mandatory field is used to select an operation mode:/O Save current ROM image to file/U Get and display ROM ID from ROM file/Ln Refer to option: /Ln/M Refer to option: /M/MAI Display current system and ROM file's MA/HOLE Update specific ROM hole by given name/HOLEOUT Save specific ROM holedata by given name/D Verification test of given ROM file withoutflashing/EC Flash EC firmware BIOS (Refer to OFBDspec)Path: $BIOS/Corebin/800/ROMUtils/On FlashBlock Description Specification.PDF.Sample Code Module Path:$BIOS/Examples/On Flash Block Description ?/NCB Flash NCB data by given name/NCBOUT Output NCB data by given name/C Destroy CMOS checksumOptionsThe optional field used to supply more information for flashing BIOS ROM.Following lists the supported optional parameters and format:?/P Program main bios image /B Program Boot Block/N Program NVRAM/C Destroy CMOS after update BIOS done/E Program Embedded Controller block if present /K Program all non-critical blocks/Kn Program n’th non-critical block only (n=0 – 7)/Q Quiet mode enable/REBOOT Reboot after update BIOS done/X Do not check ROM ID/S Display current system’s BIOS ROM ID/Ln Load CMOS default (n=0 - 1)L0: Load current CMOS optimal settingsL1: Load current CMOS failsafe settingsL2: Load CMOS optimal settings from ROMfileL3: Load CMOS failsafe settings from ROMfile/MUpdate BootBlock MAC address if exists/R Preserve all SMBIOS structures duringNVRAM programming/Rn Preserve specific SMBIOS structure duringNVRAM programming/ECUF Update EC BIOS when newer version isdetected./ShutDown Shutdown system after programming./clnevnlog Clean Event Log./DeDftCfg Delete all default settings from BIOS./-Command Name Delete certain command’s default setting.[OEM Uses Only.]/MEUF Update Intel ME ignition firmware./ME Update entire Intel ME region.(WinPE only)Note : Running AFUWIN under command prompt directly will display help message. ExamplesExamples on how to update BIOS using the command prompt are shown infollowing:Save current BIOS ROM to fileAFUWIN /OGet and display ROM ID from BIOS ROM fileAFUWIN /UUpdate main BIOS image onlyAFUWINOrAFUWIN /pUpdate Boot Block onlyAFUWIN /BUpdate NVRAM onlyAFUWIN /NUpdate Embedded Controller Block onlyAFUWIN /EUpdate Embedded Controller Block if newer version is detected AFUWIN /ECUFUpdate 2nd non-critical block onlyAFUWIN /K2Update main BIOS image, Boot Block and NVRAM at onceAFUWIN /P /B /NUpdate whole BIOS ROMAFUWIN /P /B /N /C /E /KUpdate whole BIOS ROM and load current CMOS optimal settings AFUWIN /P /B /N /C /E /K /L0 Update whole BIOS without checking ROM IDAFUWIN /P /B /N /C /E /K /XUpdate whole BIOS with quiet executionAFUWIN /P /B /N /C /E /K /QUpdate whole BIOS in quiet mode and REBOOT quietlyAFUWIN /P /B /N /C /E /K /Q /REBOOTUpdate BootBlock MAC addressAFUWIN /MUpdate whole BIOS and BootBlock MAC addressAFUWIN /P /B /N /C /E /K /M?Update whole BIOS except existing SMBIOS structuresAFUWIN /P /B /N /C /E /K /RUpdate whole BIOS but preserve SMBIOS type 0 and 11AFUWIN /P /B /N /C /E /K /R0 /R11Update dedicate ROM Hole AreaAFUWIN /Hole:NameUpdate dedicate NCB AreaAFUWIN /NCB:NameOutput dedicate ROM Hole FileAFUWIN /HOLEOUTt:NameOutput dedicate NCB FileAFUWIN /NCBOUT:NameCancel Embedded AFU default commands- Below sample cancels B & P commands if BIOS has embedded B & P commands in OFBD.AFUWIN /-B /-PNotice: if /p & /b are set as default command only and /-B /-P commands are issued then P command will still be issued because if none of command is issued then /p will still issue as AFU default.Cancel ALL Embedded AFU default commandsAFUWIN /DeDftCfgMain WindowButtonsClick this button to search for BIOS ROM file from any disk drive.Click this button to starting update BIOS.Click this button to save BIOS ROM image to disk drive.Click this button to exit this program.Function FrameInformation TabThis tab displays system BIOS information for your reference before flashingBIOS.FieldSetup TabThis tab allows you to change the settings for flashing BIOS.FieldFailsafe BIOS after flashing.Select to destroy CMOS checksum after flashing.Destroy CMOSThis is default setting in CMOS Option block.CheksumThis tab displays the updating status.FieldFunctionsTo launch into AFUWIN with GUI mode, you can double-click the executable file icon to open the operating window:Usually, system BIOS information will be displayed first, but you may see a pop-up dialog if the system does not support AMIBIOS update function. After open this program successfully, you can refer to following steps to finish the operation what you need: Saving system BIOS ROM image to file1.Press button to open file dialog box.2.Select path and input a file name.3.Click on OK button to save system BIOS ROM image into specific file.4.Press button to exit this program.Flashing system BIOS with given file1.Press button to search for BIOS ROM image file from any disk driver andload it into memory.2.Switch to Setup Tab to check and change necessary settings.3.Press button to start the operation.4.Progess Tab will be switched automatically and display the programming status.5.After BIOS updated, you can press button to exit this program or systemwill restart automatically if the Restart After Programming option enabled. Error Code ListAppendix B : AFUDOS v3.xx CommandsUsage : AFUDOS /i [/o] [/n] [/p[b][n][c][e]] [/s] [kN] [/c[N]] [/q] [/h] [/t] [/u[ROM File Name]]Following table lists the description of previous version of AFUDOS commands.。

联想消费笔记本产品促销培训

智能感光系统

-根据环境光线变化自动调节屏幕亮度 -节能省电,保护眼睛

环境光

屏幕亮度

Lenovo Confidential

Presentation Title Goes Here | © 2008 Lenovo

Lenovo Confidential Lenovo Confidential Lenovo Confidential

配备LED背光高清屏,HDMI以及VGA端口,提 供丰富的多媒体体验。内置3G模块*让您随时随地畅 享高速上网,收发邮件,在线视频。

一键拯救,APS硬盘保护,ALS智能感光系统* 以及超长电池续航等,让您自由自在、舒适高效、 放心使用!

丰富接口

网络互联

多媒体体验

人性化设计

超薄时尚设计

低功耗长续航

全功能PC

二级缓存 3M 3M 2M 2M 1M 1M

前端总线 1066Mhz 1066Mhz 800Mhz 800Mhz 800Mhz 800Mhz

TDP 25W 25W 35W 35W 35W 35W

注解 性能提升约7% 性能提升约10% 性能提升约5%

(3)Y550内存/硬盘升级

-Y550全线升级双通道4G DDR极速内存 -Y550全线升级500G超大硬盘

Page 10 of 8

Lenovo Confidential

Ideapad Y系列产品介绍 Ideapad U系列产品介绍

Ideapad S系列产品介绍 Lenovo G系列产品介绍

Lenovo Confidential

Presentation Title Goes Here | © 2008 Lenovo

Page 9 of 8

Lenovo Confidential

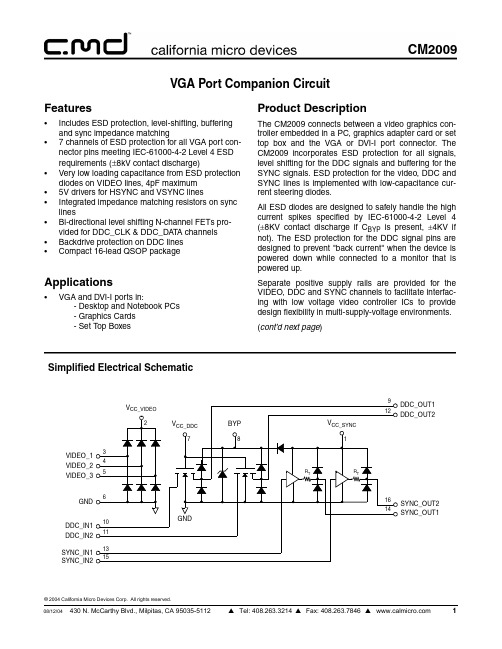

CM2009中文资料

PIN DESCRIPTIONS

DESCRIPTION This is an isolated supply input for the SYNC_1 and SYNC_2 level shifters and their associated ESD protection circuits. This is a supply pin specifically for the VIDEO_1, VIDEO_2 and VIDEO_3 ESD protection circuits. Video signal ESD protection channel. This pin is typically tied one of the video lines between the VGA controller device and the video connector. Video signal ESD protection channel. This pin is typically tied one of the video lines between the VGA controller device and the video connector. Video signal ESD protection channel. This pin is typically tied one of the video lines between the VGA controller device and the video connector. Ground reference supply pin. This is an isolated supply input for the DDC_1 and DDC_2 level-shifting N-FET gates.

ethernet-controller-i210-i211-faq

Intel® Ethernet Controller I210/I211 Frequently Asked QuestionsNetworking Division (ND)March 2016Revision 0.7Order Number: 334026-001Intel ® Ethernet Controller I210/I211 FAQs 2LegalNo license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a Particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps. The products and services described may contain defects or errors which may cause deviations from published specifications. Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting /design/literature.htm . Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. * Other names and brands may be claimed as the property of others. © 2016 Intel Corporation.Intel ® Ethernet Controller I210/I211 FAQs3Revision HistoryRevisionDate Notes 0.7March 2016 Updated sections 2.18 and 2.19. 0.6 August 5, 2014 FAQs added or updated:•- Why does the I210 not work after EEUPDATE successfully programs the image? (Updated) • 2.38 - I plan to use the I210 as an iSCSI interface or iSCSI boot device. The datasheet lists EEPROM word 0x1E bit 11 as iSCSI enable. Should I set that bit? (Added)0.5 May 2, 2014 Initial public release.Intel® Ethernet Controller I210/I211 FAQs Note: This page intentionally left blank.4Intel ® Ethernet Controller I210/I211 FAQs51 Summary (7)1.1Product Name ........................................................................................................ 7 1.2 Background .. (7)2 Technical and Design FAQ ................................................................................. 7 2.1 How do I find all the I210/I211 collateral? . (7)2.2 Can any magnetics, RJ-45, or Integrated Connector Module (ICM) be used with the I210/I211? (7)2.3 Where can I get a recommended Bill of Materials (BOM)? (7)2.4 What power supplies does the I210/I211 require? (8)2.5 Do the I210/I211 have start-up and shut-down power rail requirements? (8)2.6 Is the I210/I211 backward compatible with other Ethernet controllers? (8)2.7 Does Intel provide design review support? (8)2.8 Does I210-IS support backplane applications? (8)2.9 Does the I210/I211 support Non-Volatile Memory (NVM)-less (EEPROM-less) designs? (8)2.10 Does the I210 need to be reset after updating bits in the flash memory or upgrading to a completely new flash memory? (9)2.11 What speeds do the I210/I211 support? (9)2.12 Is Management Component Transport Protocol (MCTP) supported? (9)2.13 What are the PCI Device IDs for the I210/I211? (9)2.14 What file should I use to program the I210 or I211? (9)2.15 What tools do I use to program the I210/I211? (9)2.16 What NVM image should I select for the I210? (10)2.17 Does the Intel device driver support the 1588 protocol standard? (10)2.18 Do the I210 or I211 support pre-boot? (10)2.19 Where does the pre-boot (PXE, iSCSI, UEFI) Option ROM code reside? (10)2.20 Does the I210 and I211 support WoL? (10)2.21 Can the Subsystem PCI ID be changed in the I210/I211? (10)2.22 Does the I210 support 100Base-FX? (10)2.23 How does the security feature of the I210 work? (11)2.24 How does the security feature of the I211 work? (11)2.25 Why does the I210 not work after EEUPDATE successfully programs the image? (11)2.26 I am trying to setup AVB on my system. How can I do it? (11)2.27 Does the I210 support IPMI? (12)2.28 The layout guidelines describe the advantages of 85 Ω design vs. 100 Ω design for the differential traces (PCIe). But for SerDes, 100 Ω impedance is recommended. Are the same benefits not also valid for SerDes? (12)2.29 Is there a way to monitor the GMII interface (between MAC and PHY) on the I210? (12)2.30 Since SGMII is configurable, can the I210 be a MAC, and the other end a PHY, or vice versa? (12)2.31 What are the I210 SMBus slave addresses? (12)2.32 How do I interpret the chip markings on my I210 or I211? (12)2.33 Why is the Sample Validation Kit (SVK) not being updated? (12)2.34 Where do I find the latest software drivers for the I210 or I211? (13)2.35 Do the I210 and I211 support PCIe Spread Spectrum Clocking (SSC)? (13)2.36 Where can I get technical support? (13)2.37 Where can I find product briefs, datasheets, application notes, design guides, and other resources for developers? (13)2.38I plan to use the I210 as an iSCSI interface or iSCSI boot device. The datasheet lists EEPROM word 0x1E bit 11 as iSCSI enable. Should I set that bit? (13)Intel ® Ethernet Controller I210/I211 FAQs6 3 Sales and Marketing FAQ (14)3.1When did the Intel ® Ethernet Controller I210/I211 launch? .......................................... 14 3.2How can I purchase the Intel ® Ethernet Controller I210 or I211? ................................. 14 3.3What is the product name? ..................................................................................... 14 3.4Why did the naming convention change? .................................................................. 14 3.5Is there an EDK and Collateral List for the I210/I211? ................................................ 14 3.6What is the price of the I210/I211? ......................................................................... 14 3.7Does the I210/I211 support Energy Efficient Ethernet (EEE)? ...................................... 14 3.8Does the I210/I211 support any offloads? ................................................................ 15 3.9What virtualization technologies does the I210/I211 support? ..................................... 15 3.10What management interfaces are on the I210? ......................................................... 15 3.11What is the OS2BMC feature on the I210? (15)Intel ® Ethernet Controller I210/I211 FAQs1 Summary This document contains a list of Technical and Design Frequently Asked Questions (FAQs) and Sales and Marketing FAQs for the Intel ® Ethernet Controllers I210 and I211. It consolidates two separate FAQ lists into one. 1.1 Product Name•Intel ® Ethernet Controller I210 • Intel ® Ethernet Controller I211 1.2 BackgroundThe Intel ® Ethernet Controller I210 (I210) is a single port, compact, low power component that supports GbE designs. The I210-AT and IT offer a fully-integrated GbE Media Access Control (MAC) and a Physical Layer (PHY) port. The I210-IS offers a fully-integrated MAC and an SGMII/SerDes port that can be connected to a backplane or an external PHY. The I210 also supports PCI Express* [PCIe v2.1 (2.5 GT/s)].The Intel ® Ethernet Controller I211 (I211) is a single port, compact, low power component that supports GbE designs. The I211 offers a fully-integrated GbE MAC, PHY port, and supports PCI Express* [PCIe v2.1 (2.5 GT/s)]. Note that the I211 operates without an external flash memory.2.1 How do I find all the I210/I211 collateral?Some collateral is only available on Intel Business Link/ Intel Business Portal (IBL/IBP), which is protected under a Non-Disclosure Agreement (NDA). Other collateral is available to the general public. Contact your Intel Field Representative for access to NDA content. 2.2 Can any magnetics, RJ-45, or Integrated Connector Module (ICM) be used with the I210/I211?No. The magnetics module has a critical effect on overall IEEE and emissions conformance. The device should meet the performance required for a design with reasonable margin to allow for manufacturing variation. Occasionally, components that meet basic specifications can cause the system to fail IEEE testing because of interactions with other components or the Printed Circuit Board (PCB) itself. Carefully qualifying new magnetics modules prevents this problem. Refer to the latest Design Considerations section of the Intel ® Ethernet Controller I210/I211 Datasheets for a list of magnetics that have been qualified to work with the I210/I211. 2.3 Where can I get a recommended Bill of Materials (BOM)?The I210/I211 Datasheets list the recommended components to use with the I210/I211. The list contracts and expands over time, even after product launch, because some components reach end-of-life and new components are validated.72 Technical and Design FAQThe intended audience for this section is technical support and design engineers.Intel ® Ethernet Controller I210/I211 FAQs82.4 What power supplies does the I210/I211 require?The I210/I211 requires three power rails: 3.3 Vdc, 1.5 Vdc, and 0.9 Vdc. Intel recommends that board designers use the integrated switching voltage regulators derived from a single 3.3 Vdc supply to reduce BOM costs. A central power supply can provide the required voltage sources designed by a system power engineer. If the LAN wake capability is used, all voltages must remain present during system power down. External voltage regulators need to generate the proper voltage, supply current requirements (with adequate margin), and provide the proper power sequencing. Refer to the Power Supplies section in the I210/I211 Datasheets for additional information. 2.5 Do the I210/I211 have start-up and shut-down power rail requirements?Designs must comply with power sequencing requirements to avoid latch-up and forward-biased internal diodes. Refer to the I210/I211 Datasheets for more information. 2.6 Is the I210/I211 backward compatible with other Ethernet controllers?Intel makes every effort to keep things as simple as possible from a design migration perspective when providing a follow-on Ethernet controller, while providing our customers the richest feature set possible. The I210 adds Integrated Switching Voltage Regulators (iSVR), JTAG, NC-SI hardware arbitration, and four Software Definable Pins (SDPs) from previous Intel Ethernet controllers. The I211 adds Integrated Non-Volatile Memory (iNVM), an iSVR, and four SDPs. Due to this added functionality, exact pin compatibility with previous generations could not be maintained. The Intel ® Ethernet Controllers 82574/82583 to I210/I211 Design Guide explains what is required for a dual 82574/82583-to-I210/I211 design, but we do not recommend this option. 2.7 Does Intel provide design review support?Yes. The Intel Networking Division (ND) Platform Application Engineer (PAE) group can provide schematic and Computer Aided Design (CAD) layout support (the layout file needs to be in the Cadence file format). Submit your design review request through Intel Premier Support (IPS) against the I210/I211 product. Intel requires that the relevant checklist has been filled out by the design engineer and is submitted with the schematic and/or layout file (contact your Intel representative for access to the checklist). This enables many design errors to be caught very early in the design process, and greatly speeds up the turnaround time on the ND review. Once a PAE resource has been assigned the review, expect one week for schematic review feedback, and two weeks for layout review feedback. 2.8 Does I210-IS support backplane applications?Yes. The I210-IS has an interface that can support backplane applications. 2.9 Does the I210/I211 support Non-Volatile Memory (NVM)-less (EEPROM-less) designs?The I211 is designed to work without an attached flash memory.The I210 is designed to use an external flash memory, but can be used without one with very limited features. For example, no management interface or external PHY control via MDIO or I2C is available without flash memory.Intel ® Ethernet Controller I210/I211 FAQs92.10 Does the I210 need to be reset after updating bits in the flash memory or upgrading to a completely new flash memory? Firmware updates are now automatically followed by a firmware reset, which means the following flash memory words and section are the only ones requiring an AC power cycle:•Flash Device Size (FL_SIZE only) – word 0x11 • CSR Auto Configuration Power-Up LAN – module pointed by word 0x27If updating data in these sections, the power cord should be removed for ~20 seconds and a cold reboot needs to occur to reset the I210 and re-read the external flash memory contents into its internal registers. 2.11 What speeds do the I210/I211 support?The I210 and I211 support the following speeds:•1 GbE •100 Mb/s • 10 Mb/sAll three speeds are supported in copper and SGMII mode. SerDes modes only support GbE. 2.12 Is Management Component Transport Protocol (MCTP) supported?The I210 supports MCTP in the following combinations:•MCTP over SMBus/I2C Binding •MCTP over PCIe VDM Binding • NC-SI over MCTP2.13 What are the PCI Device IDs for the I210/I211?•I210-AT – 0x1531 (hardware default, indicating an unprogrammed device) •I211-AT – 0x1532 (hardware default, indicating an unprogrammed device) •I210-AT – 0x1533 •I210-IS/AS - 0x1536 SERDES Fiber •I210-IS/AS - 0x1537 SERDES Backplane (KX, BX) •I210-IS/AS - 0x1538 SGMII (external PHY controlled via MDIO or I2C) •I211-AT – 0x1539 •I210-IS/AS – 0x157C using iNVM (no flash memory) • I210-AT – 0x157B using iNVM (no flash memory) 2.14 What file should I use to program the I210 or I211?The image files are available on the Intel Business Link in document 513655. When programming the flash memory on an I210, you should always use the binary (.bin ) file. When programming the iNVM on an I210 or I211, you should use the appropriate text file. 2.15 What tools do I use to program the I210/I211?The tools for supporting these products are available on IBL in document number 348742. EEUPDATE is used to program the flash memory or iNVM in production environments. LANConf is designed for test and development purposes, but can also be used to program the flash memory or iNVM.Intel ® Ethernet Controller I210/I211 FAQs10 2.16 What NVM image should I select for the I210?The production images archive (document 513655) contains a list of images and their features. The SGMII image is intended for use with the I210-IS when interfacing with an external SGMII PHY and controlling it via the I 2C or MDIO interface. When connecting to an SGMII switch, use the appropriate KX image. 2.17 Does the Intel device driver support the 1588 protocol standard?Yes. The I210 supports IEEE 1588/802.1AS precision time synchronization. 2.18 Do the I210 or I211 support pre-boot?The I210 supports PXE, iSCSI boot, and UEFI. A SMASH-CLP agent expansion ROM is also available for instances where the iSCSI boot and PXE expansion ROMs are stored in the I210 local flash memory. The I211 (and the I210 when operating without a Flash) only supports PXE, only by storing the expansion ROM in system/BIOS flash memory, and only operating with default settings. 2.19 Where does the pre-boot (PXE, iSCSI, UEFI) Option ROM code reside?The available expansion ROMs can be stored in the local flash memory for NIC designs, or in the system/BIOS flash memory for LOM designs. When storing the expansion ROMs in the local flash memory, a minimum flash memory component size of 16 Mb is required.Also, note that PXE is only supported for the I211 (and the I210 when operating without a Flash) by storing the PXE code in the system BIOS flash memory.The tools for displaying and configuring the pre-boot firmware are available on in the archive Preboot.exe . The tools for BIOS developers to use to create images for inclusion in a BIOS are available in document 387754 on the Intel Business Link. 2.20 Does the I210 and I211 support WoL?Yes. However, the complete WoL solution is complex, and the system design engineer needs to assure all platform stack ingredients (BIOS, power delivery, software, NVM) interacting with the I210 or I211 are implemented correctly. 2.21 Can the Subsystem PCI ID be changed in the I210/I211?Yes. The device, subdevice, and subvendor ID’s can be changed. The device ID is a protected field and cannot be changed without loading a new signed image with a different ID. 2.22 Does the I210 support 100Base-FX?The I210 does not support 100BASE-FX natively. It is supported through SGMII with Intel’s software device driver. It requires an external PHY like the Marvell* 88E1112. The 88E112 could be embedded into an SFP module that supports 100BASE-FX.This solution could be:The I210 in SGMII mode <-> Marvell 88e112 <-> SFP cage.2.23How does the security feature of the I210 work?When the I210 is initializing, it checks for the presence of a flash memory component. If a flash memory component is present, it checks for a valid digital signature. If either of these conditions is false, the I210 reverts to the internal iNVM. If the internal iNVM is not programmed, the I210 assumes all hardware defaults, including a PCI ID of 0x1531. This may also happen if the flash memory is not ready at the time that the I210 initializes, so it is important that the flash memory component be powered from the same source as the I210.The NVM firmware images for the I210 are signed. Once the I210 successfully initializes with a signed firmware image, security is enforced (unless security is disabled by pulling down pin 12) and the image cannot be overwritten except a by a new signed image that has the same or higher security revision.Pin 12 on the I210 is designated for the purpose of overriding the security feature. To override the security when it is in effect, a pull down resistor can be applied to that pin. This pin is sampled during initialization to determine if security is disabled.Not all fields in the image are protected. Fields that are normally subject to change by the OEM, such as the MAC address, PCI subsystem ID fields and LED customizations, can be changed without invalidating the digital signature.The I210 can potentially be used without an external flash memory (with significant limitations) by using the iNVM instead. In that case, it operates the same as an I211. Refer to Section 2.24 for a description of the I211 security feature.2.24How does the security feature of the I211 work?The I211 has a lock-out mechanism after the iNVM is programmed to prevent any tampering/retry of the iNVM programming. It is activated by writing a special iNVM word auto-load structure, iNVM word address 0xA, bit 15 is set to 1b. The lock-out is active as long as the pin 12 (SECURITY-EN) strapping option is enabled (pulled up, not down). For details, refer to section 3.2 in the Intel® Ethernet Controller I211 Datasheet.2.25Why does the I210 not work after EEUPDATE successfullyprograms the image?When EEUPDATE stores the new image in an unprogrammed flash, it is not active until a power cycle forces the new image to be loaded into shadow RAM in the controller. Until a power cycle occurs, EEUPDATE functions like /verify, and /mac_dump will not work correctly. Once an I210 is programmed and running with a valid image, updates can be performed with only a system reboot with some exceptions (refer to section 2.10).2.26I am trying to setup AVB on my system. How can I do it?Intel provides the following resources to get AVB up and running on your system: •The I210 with AVB support included on a validation adapter (NIC) – limited availability•IEEE 802.1Qav Traffic shaper (w/SW extensions)•IEEE1588/802.1AS Precision Time Stamping•Time based transmission•Linux Reference Driver (IGB driver modified)•FreeBSD Reference Code (GPL free driver)•Intel® Ethernet Controller I210 [Springville]– Traffic Shaping and Time Synchronization Technical Brief – (Document ID:-496740 )This document describes the various features supported by the Intel I210 LAN controller to enable solutions to participate in time synchronization protocols and controls for transmission timing and scheduling within the Intel I210 LAN controller.Please consult these items and contact us if you need further support.The Ecosystem will need to provide:•Protocol Stack that formats the packets in the Media Protocol stack format (as defined per IEEE 802.1BA). This stack typically runs in user mode (this is the heavy lifting, and is thesecret sauce for vendors to generate revenue).•Application to take advantage of the protocol stack.2.27Does the I210 support IPMI?The I210 does not inherently support IPMI itself, but rather it supports the ability to send and receive Ethernet traffic that could be IPMI to and from a management controller. Since IPMI is such a common traffic type for a management controller, we have added specific filters to the I210 (and all other server controllers) to make filter configuration easier. However, the BMC could just as easily create filters for only FTP or HTTP traffic. We provide a highly-configurable filtering mechanism which the management controller can use to configure the type of Ethernet traffic it needs to receive, ranging from all traffic to only a specific type.2.28The layout guidelines describe the advantages of 85 Ω designvs. 100 Ω design for the differential traces (PCIe). But forSerDes, 100 Ω impedance is recommended. Are the samebenefits not also valid for SerDes?PCIe Gen1 is 100 Ω, PCIe Gen2 is 85 Ω, and SerDes is 100 Ω impedance ONLY. The I210 is recommended to use 85 Ω for PCIe signals.2.29Is there a way to monitor the GMII interface (between MACand PHY) on the I210?The GMII is not exposed in the I210.For external PHY use SerDes SKU and configure to use SGMII with SGMII capable PHY such as a Marvell 88e1112. Be advised, ND has not been able to interoperate with BRCM SGMII PHY so far. 2.30Since SGMII is configurable, can the I210 be a MAC, and theother end a PHY, or vice versa?In SGMII mode, the I210 is always a MAC and is never an SGMII PHY.2.31What are the I210 SMBus slave addresses?The SMBus slave address is configured in the NVM. The 7-bit address in the images supplied by Intel is 0x49.For additional details, refer to the NVM settings in Section 6.7.3.4, “SMBus Slave Addresses — Offset 0x03” in the Intel® Ethernet Controller I210 Datasheet.2.32How do I interpret the chip markings on my I210 or I211? Refer to the “Marking Diagram” section in the associated Specification Update document.2.33Why is the Sample Validation Kit (SVK) not being updated?When Intel ND products are production-ready, the SVK ingredients are delivered to different customer downloadable locations, thus the SVK process terminates. The software tools and NVM imagescontinue to be available on IBL/IBP as separate deliverables and the software drivers are available to the public at the Intel Download center.2.34Where do I find the latest software drivers for the I210 orI211?Intel Download center. The software drivers linked from this page are generic versions, and can be used for general purposes. However, OEMs might have altered the features, incorporated customizations, or made other changes to the software or software packaging they provide. To avoid any potential installation incompatibilities on your OEM system, Intel recommends that you check with your OEM and use the software provided via your system manufacturer. Intel or the OEM might not provide technical support for some or all issues that could arise from the usage of this generic version of software drivers.2.35Do the I210 and I211 support PCIe Spread Spectrum Clocking(SSC)?Yes. Both devices support PCIe SSC.2.36Where can I get technical support?Technical support is provided by the computer vendor. You can use the following links for Intel® Desktop Board and Intel® Server Board to find support information:•Intel® Desktop Board support•Intel® Server Board supportIntel develops network components used in motherboards and network adapters sold by OEMs such as Dell*, HP*, Gateway*, and IBM*. Network controllers that are built into the motherboard or network adapters sold by an OEM are supported by the OEM. Intel does not provide support for OEM integrated network controllers or OEM adapters.2.37Where can I find product briefs, datasheets, application notes,design guides, and other resources for developers?You can use the following link for product information on Intel® Ethernet Controllers: •Product information on Intel® Ethernet ControllersIntel offers a complete line of industry-leading, single- and multi-port 10 GbE, 1 GbE, and fast Ethernet LAN controllers with integrated MAC and PHY, providing high performance, low power consumption, and a smaller footprint. Offering 10 GbE, 1 GbE, and 100 Mb/s LAN controllers, PCIe, PCI, PCI-X, or LCI bus interfaces, in 16-, 32- or 64-bit architectures, Intel produces Ethernet LAN controllers that enable faster, smaller, and simpler designs.2.38I plan to use the I210 as an iSCSI interface or iSCSI bootdevice. The datasheet lists EEPROM word 0x1E bit 11 as iSCSIenable. Should I set that bit?No. The class code should be left as LAN controller (word 0x1E bit 11 = 0b). The iSCSI boot firmware and / or the iSCSI software client will emulate an iSCSI host bus adapter and provide the necessary support.Note that the following FAQ entries are not listed in any particular order or priority.3.1 When did the Intel ® Ethernet Controller I210/I211 launch? The I210/I211 products launched in November 2012.3.2 How can I purchase the Intel ® Ethernet Controller I210 or I211? Orders should be placed with an Intel ® Authorized Distributor or through your Intel contact.Ordering information can be found in the Intel ® Ethernet Controller I210/I211 Specification Update .3.3 What is the product name?The products are marketed as:•Intel ® Ethernet Controller I210 Family • Intel ® Ethernet Controller I211-AT.Note that 1 GbE wording is not used in the product name since the Roman numeral “I” already denotes the 1 GbE speed. 3.4 Why did the naming convention change?The Intel ® Ethernet Controllers I210/I211 follow the new product naming convention that ND products are using going forward. The new naming convention makes it easier to tell what type of product it is. The “I” is the Roman numeral for 1 denoting 1 GbE speed. Likewise, if the first letter is a Roman numeral “X”, it is a 10 GbE product. The next number is the series and then the version of the product. The I210/I211 are the follow-on product and feature set in the 200 series of products. The Intel ® 82574 and 82583 1 GbE Ethernet Controllers use the old naming. 3.5 Is there an EDK and Collateral List for the I210/I211?Yes, the link to the collateral list is:Networking and Comms Ethernet: Intel® Ethernet Controller I210_I211 (Springville_Pearsonville)The EDK is at:Ethernet: Gigabit Ethernet Controller .3.6 What is the price of the I210/I211?Please contact your authorized Intel distributor for pricing for the Intel ® Ethernet Controller I210 Family and Intel ® Ethernet Controller I211-AT. 3.7 Does the I210/I211 support Energy Efficient Ethernet (EEE)? Yes.3 Sales and Marketing FAQThe intended audience for this section sales, marketing, and management.。

TSB82AA2中文资料

元器件交易网

Contents

Section 1 Title Page 1−1 1−1 1−2 1−3 1−3 1−3 1−3 2−1 3−1 3−3 3−4 3−4 3−5 3−6 3−7 3−7 3−8 3−8 3−9 3−10 3−11 3−12 3−12 3−13 3−13 3−14 3−14 3−15 3−16 3−16 3−17 3−18 3−19 3−21 3−22 4−1 4−4 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.3 Related Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.4 Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.6 TSB82AA2 Data Manual Document History . . . . . . . . . . . . . . . . . . . . . Terminal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TSB82AA2 Controller Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . 3.1 PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2 Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3 Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.4 Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.5 Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 Class Code and Revision ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . 3.7 Latency Timer and Class Cache Line Size Register . . . . . . . . . . . . . . 3.8 Header Type and BIST Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.9 OHCI Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.10 TI Extension Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.11 CardBus Cis Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.12 CardBus CIS Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.13 Subsystem Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.14 Power Management Capabilities Pointer Register . . . . . . . . . . . . . . . 3.15 Interrupt Line and Pin Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.16 MIN_GNT and MAX_LAT Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.17 OHCI Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.18 Capability ID and Next Item Pointer Register . . . . . . . . . . . . . . . . . . . . 3.19 Power Management Capabilities Register . . . . . . . . . . . . . . . . . . . . . . 3.20 Power Management Control and Status Register . . . . . . . . . . . . . . . . 3.21 Power Management Extension Register . . . . . . . . . . . . . . . . . . . . . . . . 3.22 Multifunction Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.23 Miscellaneous Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . 3.24 Link Enhancement Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.25 Subsystem Access Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.26 GPIO Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OHCI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.1 OHCI Version Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Guide,

Computers Microprocessors Embedded Systems - appliances, automobiles Special purpose - military chips, high performance computing

ECE280 Digital Design Laboratory August 31, 2006

In1 In2

What is Digital Systems Design ?

• Digital Systems Design is a process that entails a systematic development of an idea into an architecture that can be implemented digitally.

• Available from /ise/logic_design_prod/webpack.htm

ECE280 Digital Design Laboratory August 31, 2006

What is a Digital System?

• A collection of interconnected digital modules designeபைடு நூலகம் to perform a particular service or function

Digital Systems

• High Level Digital Modules – Microprocessors/Microcontrollers – PLDs – ASICs • Low Level Digital Modules – Gates - AND, OR, NOR, etc. – Blocks - Adder, subtractor, shifter, etc.

TDA8954

Mono bridge-tied load configuration

THD + N = 10 %; RL = 4 Ω; VDD = 41 V; VSS = −41 V

THD + N = 10 %; RL = 4 Ω; VDD = 35 V; VSS = −35 V

[3] -

210 -

W

-

150 -

TDA8954TH

HSOP24 plastic, heatsink small outline package; 24 leads; low stand-off height

SOT566-3

TDA8954_1

Product data sheet

Rev. 01 — 24 December 2009

© NXP B.V. 2009. All rights reserved.

2 of 46

NXP Semiconductors

6. Block diagram

TDA8954

2 × 210 W class-D power amplifier

VDDA DIAG1

STABI PROT

VDDP2

VDDP1

IN1M IN1P

OSCREF OSC

MODE SGND

IN2P IN2M

3 (20) 10 (4)

W

Po

output power

Tj = 85 °C; LLC = 22 μH; CLC = 680 nF (see

[3] -

420 -

WLeabharlann Figure 13); RL = 8 Ω; THD + N = 10 %; VDD = 41 V;

UC-2100-W Series Quick Installation Guide