微组装工艺

微组装钎焊工艺

微组装钎焊工艺1、采用钎焊工艺应符合下列规定:(1)电路内部湿气、氧气含量均较低,且有气密性要求的电连接器与壳体组装时应采用钎焊工艺;(2)有大面积接地要求的电路基板与载体或壳体的组装,以及接插件与封装壳体不同组成部分之间的高精度拼装时应采用钎焊工艺;(3)在微电子产品的封装过程中,对金属或陶瓷腔体绝缘子、接头或者盖板的焊接时应采用钎焊工艺;(4)钎焊工艺用于小腔体的金属及陶瓷封装的封盖时,芯片及电路应耐高温;(5)待钎焊表面可钎焊性宜采用厚膜、薄膜或镀覆技术进行金属化;(6)钎焊工艺可采用二元或多元共晶焊料合金焊膏的形式,也可采用预制焊片的形式,盖板与壳体热膨胀系数应匹配。

2、钎焊的主要工序应符合下列规定:(1)应根据工艺要求选择成分稳定、无氧化、表面平整的焊料,根据焊接温度选用焊料及使用量;(2)焊接前应通过真空烘焙,通氧气或湿氢的方法,去除待焊件及焊料片表面的油污及氧化层;(3)放置焊料应牢靠,并应使焊料的填缝路程最短,根据工艺规定可涂敷阻焊剂或阻流剂,对钎焊缝外围涂层和透气孔周围微电路线条实施阻焊;(4)根据焊料种类与工艺要求选择保护气氛和温度曲线,前道工艺焊料的熔化温度应高于后道工艺的操作温度,盖板结构设计应合理,封盖焊接过程中应使焊料的流动减至最低限度;(5)在二元或三元合金焊料熔融温度下进行钎焊密封时,钎焊峰值温度应高于焊料合金液相温度20℃~50℃;(6)当组装过程包含多道钎焊工艺时,应采用温度梯度钎焊,相邻两道钎焊工艺焊料的液相温度相差宜大于30℃;(7)有焊透率要求的电路基板的组装,需根据基板尺寸选择焊膏进行钎焊,基板应包含透气孔;(8)当组件包含多个部件一体化钎焊时,宜采用工装夹具;(9)钎焊完成后应清洗焊接件,去除焊渣及助焊剂;(10)使用显微镜目检焊缝是否有裂纹、缝隙等缺陷,有缺陷应重新补焊;(11)钎焊密封后应进行粗检漏和细检漏。

3、钎焊的工艺运行条件应符合下列规定:(1)钎焊工艺宜在等于或优于8级净化区中进行;(2)钎焊封盖应在真空或者高纯度、干燥的氮气保护气氛中进行;(3)钎焊工艺可采用红外链式炉实现大批量生产。

微组装工艺

�路电成集片亿 081 要需约大国全年每在现 。币民人亿千几达将值产 年则�装封子电于用

2

后�主为壳外装封璃玻-属金型� eniltuO rotsisnarT� OT 的线引根三以代年 05 纪世 02 顿拉布 管体晶只一第 莱克肖 丁巴 。 史历的装封子电微创开�管体晶只一第明发室验实尔贝国美年 7491 程过展发、生产、一 展发的术技装封子电微 3.2.1 。术技装封� D3� 维 三的谓所是就这�展发向方 z 向上础基的装组维二在然 必装组子电�积面 的限有于对�上础基的 MCM 在�高 提断不的求要装组度密高等化型薄、化型轻、化型小 对域领等机算计、天航、空航在统系和机整子电于由 �装封� D2� 维二的现实内面平 yx 为均述所上以 。术技装组体立种一是这。的成构上板母的大更个一在 装插同共再卡插 或板插个各的装组级二由是�杂复大 庞加更术技装组�全更能功�高更度密装封级三 装封级三、四 。分部三术技 � ACD� 装安接直片芯和 � TMS� 术技装安面表 、 � THT� 术技装安孔通括包 。装封以 加独单再不般一级一这�外求要别特除。上板基他其或 BWP 到装安同一� BOC� 片芯 上板及件器元的型类种各、品产装封子电微种各级一上将是�装组是上际实装封级二 � BWP� 装封级二、三 。合组或件器元子电的能功用实有为成 之使�来起接连法方连互片芯种三述上用间脚引外的装封与区焊的片芯在�时同�来起装 封�合组的们他或料塑、瓷陶、属金� 料材的宜适用片芯 CI 个多或个一将是装封级一 � MCM、MCS� 装封级一、二 。连相然自属金线 布与区焊的片芯 CI 将�线布行 进一统再�后中层质介 IP 或板基到置埋片芯 CI 将先 �术技线布后� 术技连互片芯置埋� 4 。速迅展发�高都能性合综 BAT、BW 比。时省工省�成完次一均 �少多点凸论无 。小积面法方他其比积面装安的片芯 �短最线连互 以所 �度高的点凸是既度 长脚引的接焊连互为因 。术技 的连互接直区焊板基和区焊片芯将、下朝面片芯 术技 BCF� 3 。越优 BW 比能性合综 �种几带属金双和带层三、带层双、带层单有 BAT 。分部个几接焊线引外 的区焊板基与线引带载 的后最和接粘板基的后焊连互片芯-带载�接焊点凸片 芯与线引带 载�作制线引带载�成形点凸区焊片芯括包� ”梁桥“ 的区焊板基和区焊片芯接连是 BAT 术技 BAT� 2 。丝 lA�丝 uA -iS�丝 uA。要需接焊的巨艰和寸尺上以米微 07 足满 可高度强点焊 �便方活灵点特� � 焊球丝金� 焊声超 压热和焊声超、焊压热为分�术技连互的熟成最 术技 BW� 1 。 � 术技线布后� 术技连互片芯置埋及以� BCF� gnidnoB pihC pilF� 焊装倒和� BAT �gnidnoB detamotuA epaT � 焊动自带载、 � BW�gnidnoB eriW� 合键线引有要主 � 术技连互片芯、2 。务任项这成完的好很以可基脂树机有的力应低�可即固牢接粘板 基与片芯求要只 CI 寸尺大对�CI 寸尺小或管体晶于合适法方述前�法接粘脂树机有� 4 。便简作操�化固成完中箱烘的净干在可�化固行进间时 和度温的求要化固胶电导用采 �后接粘片芯�层化属金有具板基和面背片芯求要不

微组装工艺

微组装工艺1 1.1 概述集成电路产业设计、制造、封装逐渐成为衡量一个国家综合国力的重要指标之一。

先进封装技术的发展使得日本在电子系统、特别是日用家电消费品的小型化方面一度走在了世界之前。

据估计我国集成电路的年消费将达到932亿美圆约占世界市场的20其中的30将用于电子封装则年产值将达几千亿人民币。

现在每年全国大约需要180亿片集成电路但我们自己制造特别是封装的不到20。

一、微电子封装微电子封装——A Bridge from IC to System 狭义芯片级 IC Packaging 广义芯片级系统级——电子封装工程电子封装工程将基板、芯片封装体和分立器件等要素按电子整机要求进行连接和装配实现一定电气.物理性能转变为具有整机或系统形式的整机装置或设备。

二、芯片级封装涉及的技术领域芯片封装技术涉及物理、化学、化工、材料、机械、电气与自动化等学科。

所涉及材料包括金属、陶瓷、玻璃和高分子材料等。

芯片封装技术整合了电子产品的电气特性、热特性、可靠性、材料与工艺应用和成本价格等因素是以获得综合性能最优化为目的的工程技术。

1.2 微电子封装技术 1.2.1 概念一、微电子封装技术的定义利用薄膜技术及微细连接技术将半导体元器件及其它构成要素在框架和基板上布置、固定及连接引出接线端子并通过可塑性绝缘介质灌封固定构成整体结构的工艺。

二、封装的作用紧固的引脚系统将脆弱的芯片表面器件连线与外部世界连接起来物理性保护、支撑保护芯片需要外壳底座防止芯片破碎或受外界损伤环境性保护外壳密封防止芯片污染免受化学品、潮气等的影响散热封装体的各种材料本身可带走一部分热量 1.2.2 微电子封装技术的分级微电子封装可以分为几个层次零级封装、一级封装、二级封装和三级封装。

一、零级封装芯片互连级-CLP 按芯片连接方法不同又分为 1、芯片粘接IC芯片固定安装在基板上。

一般有以下几种方法 1 Au-Si合金共熔法 370?Au与Si有共熔点可在多个IC芯片装好后在氮气保护下烧结也可用超声熔焊法逐个熔焊。

微组装技术简述及工艺流程及设备

微组装技术简述及工艺流程及设备引言微组装技术是现代制造领域的重要技术之一,它通常用于在微尺度下组装微型元件和器件。

微组装技术的应用范围非常广泛,包括微电子组装、微光学组装、生物医学器械组装等。

本文将对微组装技术进行简述,并介绍其工艺流程及所需的设备。

微组装技术简述微组装技术是利用微加工技术和微纳米尺度力学手段,在微尺度下实现元件和器件的组装。

与传统组装技术相比,微组装技术具有更高的精度、更小的尺寸、更好的可靠性和更高的集成度。

微组装技术是当今微电子、纳米科技和生物医学等领域的重要基础技术,对于实现微纳系统和微型器件的集成化具有重要意义。

微组装技术可以分为两种基本形式:硬微组装和软微组装。

硬微组装是指在刚性基板上进行器件组装,主要包括微芯片组装、微连接组装等。

软微组装主要指在柔性基板上进行器件组装,如可穿戴设备组装、生物医学器械组装等。

工艺流程微组装技术的工艺流程一般包括以下几个步骤:1. 设计和制造基板首先需要根据组装要求设计并制造基板。

基板材料通常选用硅、玻璃或聚合物材料,并依据器件的尺寸和形状进行加工。

2. 准备组装元件接下来,需要准备待组装的微型元件和器件。

这些元件通常是在其他工艺步骤中制备好的,如微电子芯片、光学元件、传感器等。

3. 准备组装工具和设备在微组装过程中,需要使用一些特殊的工具和设备,如显微镜、激光加工设备、微针等。

这些设备通常需要根据具体的组装任务进行选择。

4. 进行组装操作组装操作是微组装技术的核心步骤。

根据组装要求,将待组装的元件定位到基板上,并使用适当的力或温度进行粘合或焊接。

组装过程需要在洁净的环境中进行,以避免灰尘或杂质对器件性能的影响。

5. 测试和质量控制完成组装后,需要对组装好的器件进行测试和质量控制。

这包括检查组装位置的准确性、元件之间的连接可靠性以及器件的功能性能等。

设备微组装技术需要使用一系列特殊的设备来完成组装任务。

下面列举一些常用的微组装设备:1.显微镜:用于精确定位待组装的微元件,可采用光学显微镜或电子显微镜等。

微组装技术简述及工艺流程及设备

2.微组装技术与电子组装技术的关系

微电子组装技术是电子组装技术 最新发展的产物,是新一代高级(先进) 的电子组装技术,属第五代电子组装技 术(从80年代至今)。与传统的电子组 装技术比较,其特点是在“微”字上。 “微”字有两个含义:一是微型化,二 是针对微电子领域。

二。微组装技术对整机发展的作用

四。多芯片组件(MCM)的技术内涵、优点及类型

1.技术内涵—— MCM是multichip module英文的缩写, 通常译为多芯片组件(也有译为多芯片模块)。 MCM技术属于混合微电子技术的范畴,是混合微电 子技术向高级阶段发展的集中体现,是一种典型的高 级混合集成电路技术。

关于MCM的定义,国际上有多种说法。就本人 的观点而言,定性的来说MCM应具备以下三个条件: (1)具有高密度多层布线基板;(2)内装两块以上 的裸芯片IC(一般为大规模集成电路);(3)组装 在同一个封装内。也就是说,MCM是一种在高密度 多层布线基板上组装有2块以上裸芯片IC(一般为LSI) 以及其它微型元器件,并封装在同一外壳内的高密度 微电子组件。

采用厚膜混合电路工艺制作DC∕DC电源的优点——

1)减小产品体积和重量

与常规PCB板组装电源同比,重量可减少30%~60%,

体积可减小25%~70%,

微组装技术简述及工艺流程及设备概述.pptx

4) 易于实现多功能。MCM可将模拟电路、数 字电路、光电器件、微波器件、传感器以及 其片式元器件等多种功能的元器件组装在一 起,通过高密度互连构成具有多种功能微电 子部件、子系统或系统。Hughes Reserch laboratory 采用三维多芯片组件技术开发 的计算机系统就是MCM实现系统级组件的 典型实例。

3.类型和特点——

通常可按MCM所用高密度多层布线基板的结构 和工艺,将MCM分为以下几个类型。

1)叠层型MCM(MCM-L,其中L为“叠层”的 英文词“Laminate”的第一个字母)也称为L 型多芯片组件,系采用高密度多层印制电路板 构成的多芯片组件,其特点是生产成本低,制 造工艺较为成熟,但布线密度不够高,其组装 效率和性能较低,主要应用于30MHz和100个 焊点/英寸2以下的产品以及应用环境不太严酷 的消费类电子产品和个人计算机等民用领域。

3)淀积型MCM(MCM-D,其中D是“淀积”的英 文名Deposition 的第一个字母),系采用高密度 薄膜多层布线基板构成的多芯片组件。其主要特 点是布线密度和组装效率高,具有良好的传输特 性、频率特性和稳定性.

微组装技术简述

张经国 1404

Байду номын сангаас

一.微组装技术内涵及其与电子组装技术的关系 1.内涵——微组装技术(micropackging technology) 是微电子组装技术(microelectronic packging technology)的简称,是新一代高级的电子组装技 术。它是通过微焊互连和微封装工艺技术,将高 集成度的IC器件及其他元器件组装在高密度多层 基板上,构成高密度、高可靠、高性能、多功能 的立体结构微电子产品的综合性高技术,是一种 高级的混合微电子技术。

微组装技术简述及工艺流程及设备课件

精度控制问题

精度控制问题

微组装技术要求零件的精度非常高,如何确保每个组件的精确位置和尺寸是微组装过程中的一大挑战 。

解决方案

采用高精度的设备和工艺,如激光加工、纳米压印等,同时加强质量检测,对不合格的零件进行修复 或替换。

生产效率问题

生产效率问题

微组装技术的复杂性和高精度要求使 得生产效率相对较低。

ERA

定义及特点

微组装技术定义 高密度组装 高可靠性 高灵活性

微组装技术是一种将微电子器件(如芯片、MEMS等)通过物 理、化学或电学方法组装到基板上,形成复杂电路和系统的技

术。

微组装技术可以实现高密度组装,将多个微电子器件组装到有 限的基板面积内,提高了电路和系统的集成度。

由于微组装技术采用可靠的物理、化学或电学方法进行连接和 固定,因此可以保证组装后的电路和系统具有高可靠性。

05

案例分析

BIG DATA EMPOWERS TO CREATE A NEW

ERA

案例一:某公司微组装生产线

总结词

高效、自动化、定制化

主要设备

自动拾取机、微型焊接机、芯片贴装机、烘箱、 显微镜等。

详细描述

该公司的微组装生产线采用了先进的自动化设备 和精细的工艺流程,实现了高效的生产。同时, 公司根据客户需求进行定制化生产,满足客户多 样化的需求。

技术参数

引线键合机的主要技术参数包括 金属线的直径、键合压力、加热 温度和键合速度等,这些参数需 要根据不同的芯片和基板材料进 行调整。

芯片封接机

设备功能

芯片封接机主要用于将芯片、引线和基板等部件密封在一起,以保 护电气连接不受环境影响。

工作原理

芯片封接机采用热压、超声波焊接或环氧树脂密封等技术,将芯片 、引线和基板等部件密封在环氧树脂或其他密封材料中。

微组装工艺设计流程

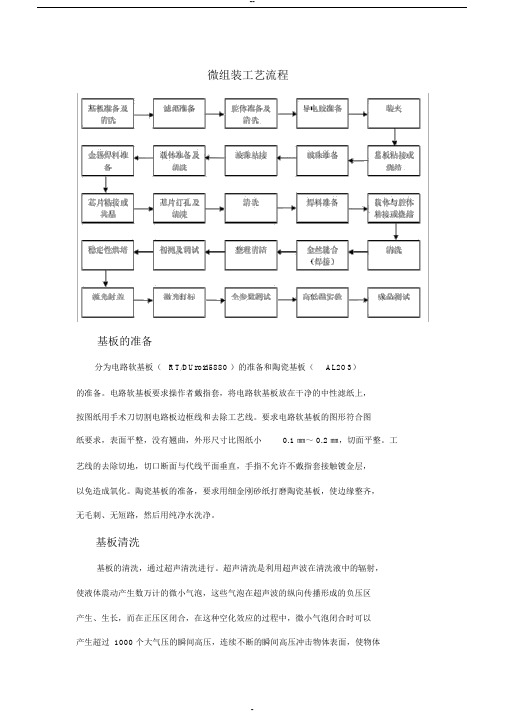

微组装工艺流程基板的准备分为电路软基板(RT/DUroid5880)的准备和陶瓷基板(AL2O3)的准备。

电路软基板要求操作者戴指套,将电路软基板放在干净的中性滤纸上,按图纸用手术刀切割电路板边框线和去除工艺线。

要求电路软基板的图形符合图纸要求,表面平整,没有翘曲,外形尺寸比图纸小 0.1 ㎜~0.2 ㎜,切面平整。

工艺线的去除切地,切口断面与代线平面垂直,手指不允许不戴指套接触镀金层,以免造成氧化。

陶瓷基板的准备,要求用细金刚砂纸打磨陶瓷基板,使边缘整齐,无毛刺、无短路,然后用纯净水洗净。

基板清洗基板的清洗,通过超声清洗进行。

超声清洗是利用超声波在清洗液中的辐射,使液体震动产生数万计的微小气泡,这些气泡在超声波的纵向传播形成的负压区产生、生长,而在正压区闭合,在这种空化效应的过程中,微小气泡闭合时可以产生超过 1000 个大气压的瞬间高压,连续不断的瞬间高压冲击物体表面,使物体表面和微小缝隙中的污垢迅速剥落。

因此,超声波清洗对物体表面具有一定损伤性,经过多次实验(此实验未记录实验数据),确定合理的超声功率、去离子水用量以及清洗液的高度和清洗时间。

具体清洗流程及参数设置如下:打开超声清洗机,功率调至 100 瓦,加入去离子水,液面高度为 60 ㎜~80 ㎜之间。

将电路软基板或陶瓷基板放入瓷盒中,倒入 HT1 清洗液,液面略高基板上表面 3 ㎜~5 ㎜,然后将整个瓷盒放入超声清洗机的支架上(水面低于清洗液 2 ㎜~3 ㎜),清洗时间为 Xmin~Xmin。

将 95%乙醇倒入瓷盒,液面略高于基板上表面 3 ㎜~5 ㎜,然后将整个瓷盒放入超声清洗机的支架上(水面低于清洗液 2 ㎜~3 ㎜),清洗时间为 Xmin~Xmin。

将清洗完毕的基板放入 X℃±3℃的烘箱中烘 0.5h 后,放入氮气保护柜。

通过上述多次实验后确定的清洗工序,清洗完成后的基板表面无油污、杂质等残留物。

腔体的准备和清洗腔体的准备主要是用手术刀打净毛刺,再用洗耳球打磨毛刺形成的杂质。

微组装技术简述及工艺流程及设备

感谢您的观看

汇报人:

添加标题

添加标题

添加标题

自动化程度高:微组装技术采用自 动化设备,提高生产效率和质量稳 定性

环保性:微组装技术采用环保材料 和工艺,减少对环境的影响

微组装技术的应用领域

生物医学领域:如生物芯片、 微流体、微针等

光学领域:如微光学器件、 微光学系统等

航空航天领域:如微型卫星、 微型飞行器等

电子行业:如集成电路、传 感器、微机电系统等

微组装技术是一种将微小部 件组装成复杂结构的技术

微组装技术广泛应用于电子、 通信、医疗等领域

微组装技术可以提高产品的 性能和可靠性,降低成本和

能耗

微组装技术的特点

精度高:微组装技术可以实现纳米 级别的精度,满足高精度要求

灵活性强:微组装技术可以适应多 种材料和工艺要求,满足不同产品 的需求

添加标题

微组装技术简述及工 艺流程及设备

,a click to unlimited possibilities

汇报人:

目录 /目录

01

点击此处添加 目录标题

02

微组装技术简 述

03

微组装工艺流 程

04

微组装设备

05

微组装技术发 展趋势

01 添加章节标题

02 微组装技术简述

微组装技术的定义

微组装技术包电路板封装 在一起,保护芯片和电路板

免受外界环境的影响

测试:对封装好的芯片进行 电气性能测试,确保其性能

符合要求

微组装工艺流程需要精确控 制,以保证产品的质量和可

靠性。

检测与调试

检测方法:光学显微镜、电子显微镜、X射线衍射等 调试步骤:调整参数、优化工艺、验证结果等 调试工具:自动化测试设备、软件工具等 调试目标:提高产品质量、降低生产成本、提高生产效率等

微组装技术简述及工艺流程及设备

2.优点——MCM技术有以下主要优点。

1)使电路组装更加高密度化,进一步实现整机 的小型化和轻量化。与同样功能的SMT组装 电路相比,通常MCM的重量可减轻 80%~90%,其尺寸减小70~80%。在军事应 用领域,MCM的小型化和轻量化效果更为明 显,采用MCM技术可使导弹体积缩小90%以 上,重量可减轻80%以上。卫星微波通信系 统中采用MCM技术制作的T/R组件,其体积 仅为原来的1/10~1/20。

3)淀积型MCM(MCM-D,其中D是“淀积”的英 文名Deposition 的第一个字母),系采用高密度 薄膜多层布线基板构成的多芯片组件。其主要特 点是布线密度和组装效率高,具有良好的传输特 性、频率特性和稳定性.

4)混合型MCM-H(MCM-C/D和MCM-L/D,其中 英文字母C、D、L的含义与上述相同),系采用 高密度混合型多层基板构成的多芯片组件。这是 一种高级类型的多芯片组件,具有最佳的性能/价 格比、组装密度高、噪声和布线延迟均比其它类 型MCM小等特点。这是由于混合多层基板结合了 不同的多层基板工艺技术,发挥了各自长处的缘 故。特别适用于巨型、高速计算机系统、高速数 字通信系统、高速信号处理系统以及笔记本型计 算机子系统。

2)厚膜陶瓷型MCM(MCM-C,其中C是“陶瓷 ”的英文名Ceramic的第一个字母),系采用 高密度厚膜多层布线基板或高密度共烧陶瓷 多层基板构成的多芯片组件。其主要特点是 布线密度较高,制造成本适中,能耐受较恶 劣的使用环境,其可靠性较高,特别是采用 低温共烧陶瓷多层基板构成的MCM-C,还 易于在多层基板中埋置元器件,进一步缩小 体积,构成多功能微电子组件。MCM-C主 要应用于30~50MHz的高可靠中高档产品。 包括汽车电子及中高档计算机和数字通信领 域。

微组装基本工艺流程

微组装基本工艺流程微组装是一种高精度、高效率的集成电路封装技术,其基本工艺流程包括前期准备、半导体芯片准备、芯片基座准备、芯片粘贴、键合、封装、测试和包装等几个关键步骤。

1.前期准备在微组装工艺开始之前,需要准备各种设备和材料,如工作台、显微镜、自动化机械手、真空封装设备、焊锡线、胶水等。

此外,还需要规划好工艺流程和操作规程,确保整个工艺的顺利进行。

2.半导体芯片准备此步骤主要包括对半导体芯片进行清洗、切割和测试等准备工作。

首先,将半导体芯片浸泡在清洗剂中进行超声波清洗,以去除表面的杂质。

然后,使用切割机将整个硅片分割成单个芯片。

最后,对每个芯片进行功能和可靠性测试,以确保其符合要求。

3.芯片基座准备芯片基座是将芯片粘贴在底座上的载体,其材料多为陶瓷或塑料。

首先,通过模具将基座制成所需的形状和尺寸。

然后,进行基座的粗磨和抛光,以实现光滑度和精度的要求。

最后,通过清洗和干燥,确保基座表面无尘和杂质,以利于后续的粘贴和键合。

4.芯片粘贴在芯片基座的定位平台上,使用显微镜和自动化机械手将芯片粘贴在基座上。

首先,将一定量的导热胶敷在基座上。

然后,使用自动化机械手将芯片从芯片库位中取出并粘贴在基座上。

最后,通过压力和温度控制,确保芯片与基座粘结牢固。

5.键合键合是将芯片上的金线连接到基座上的引脚。

首先,通过焊锡线将引脚与基座连接起来,形成临时的电气连接。

然后,使用焊线绑扎机或激光焊接机器进行金线的键合。

最后,用显微镜检验键合点的质量,确保键合的牢固度和电气连接的可靠性。

6.封装封装是将粘贴在基座上的芯片封装在外壳中,以保护芯片并提供所需的引脚。

首先,通过接触式或非接触式方法将封装材料涂布在基座上。

然后,在暴露的引脚上焊接封装材料,形成引脚的支撑和保护。

最后,通过温度和压力控制,将封装材料固化,并保证封装的完整性和可靠性。

7.测试封装完成后,在专用的测试设备中对封装的芯片进行成品测试。

测试项目包括芯片的性能、功耗、温度等。

微组装工艺流程

微组装工艺流程基板得准备分为电路软基板(RT/DUroid5880)得准备与陶瓷基板(AL2O3)得准备。

电路软基板要求操作者戴指套,将电路软基板放在干净得中性滤纸上,按图纸用手术刀切割电路板边框线与去除工艺线。

要求电路软基板得图形符合图纸要求,表面平整,没有翘曲,外形尺寸比图纸小 0、1 ㎜~0、2 ㎜,切面平整。

工艺线得去除切地,切口断面与代线平面垂直,手指不允许不戴指套接触镀金层,以免造成氧化。

陶瓷基板得准备,要求用细金刚砂纸打磨陶瓷基板,使边缘整齐,无毛刺、无短路,然后用纯净水洗净。

基板清洗基板得清洗,通过超声清洗进行。

超声清洗就是利用超声波在清洗液中得辐射, 使液体震动产生数万计得微小气泡,这些气泡在超声波得纵向传播形成得负压区产生、生长,而在正压区闭合,在这种空化效应得过程中,微小气泡闭合时可以产生超过 1000 个大气压得瞬间高压,连续不断得瞬间高压冲击物体表面,使物体表面与微小缝隙中得污垢迅速剥落。

因此,超声波清洗对物体表面具有一定损伤性,经过多次实验(此实验未记录实验数据),确定合理得超声功率、去离子水用量以及清洗液得高度与清洗时间。

具体清洗流程及参数设置如下: 打开超声清洗机,功率调至 100 瓦,加入去离子水,液面高度为 60 ㎜~80 ㎜之间。

将电路软基板或陶瓷基板放入瓷盒中,倒入 HT1 清洗液,液面略高基板上表面 3 ㎜~5 ㎜,然后将整个瓷盒放入超声清洗机得支架上(水面低于清洗液 2 ㎜~3 ㎜),清洗时间为 Xmin~Xmin。

将 95%乙醇倒入瓷盒,液面略高于基板上表面 3 ㎜~5 ㎜,然后将整个瓷盒放入超声清洗机得支架上(水面低于清洗液 2 ㎜~3 ㎜),清洗时间为 Xmin~Xmin。

将清洗完毕得基板放入 X℃±3℃得烘箱中烘 0、5h 后,放入氮气保护柜。

通过上述多次实验后确定得清洗工序,清洗完成后得基板表面无油污、杂质等残留物。

腔体得准备与清洗腔体得准备主要就是用手术刀打净毛刺,再用洗耳球打磨毛刺形成得杂质。

微组装技术简述及工艺流程及设备ppt

微组装技术在未来面临的挑战和机遇

微组装技术的经济效益和社会效益

THANKS

感谢观看

将显卡插入主板上的PCI-E插槽中,确保插槽与显卡的金手指对应。

安装显卡

工业控制系统中的微组装工艺流程

总结与展望

05

微组装技术的成果与经验总结

微组装技术发展的历史和现状

微组装技术的工艺流程和设备

微组装技术在各个领域的应用成果

微组装技术的设计原则和方法

微组装技术的应用前景与展望

微组装技术在未来的应用前景

贴装后需要进行焊接和检测,以确保芯片与电路基板之间的可靠连接。

Байду номын сангаас

03

焊接完成后需要进行检测,以发现是否存在虚焊、漏焊等缺陷。

引脚焊接工艺

01

引脚焊接是将芯片引脚与电路基板上的导线焊接在一起的过程,常用的焊接方法有热压焊、超声波焊、激光焊等。

02

焊接过程中需要控制温度、时间和压力等参数,以确保焊接质量和可靠性。

贴片机

包括自动焊接机和热压焊接机等,用于将芯片引脚与基板引脚焊接牢固;

引脚焊接设备

包括视觉检测设备和电检测设备等,用于检测芯片和元器的位置、贴装质量等。

检测设备

芯片贴装设备的种类与原理

芯片贴装设备的技术参数

芯片贴装设备的选用

芯片贴装设备

引脚焊接设备

引脚焊接设备的种类与原理

根据焊接原理的不同,引脚焊接设备可分为热压焊接机、超声波焊接机、激光焊接机等几种类型;

xx年xx月xx日

微组装技术简述及工艺流程及设备ppt

CATALOGUE

目录

微组装技术简介微组装工艺流程微组装设备及选用微组装技术的应用案例总结与展望

微组装平行缝焊工艺

微组装平行缝焊工艺1、采用平行缝焊工艺应符合下列规定:(1)对内部湿气、氧气含量要求比较低且有密封性要求的电路,应采用平行缝焊工艺;(2)待焊接材料为阻热高的材料,密封过程中采用局部加热,封装体的升温较低、对温度较敏感的电子元器件的封装时,应采用平行缝焊工艺;(3)对可伐合金、10号钢等电阻率较高、导热性能差的金属或合金组件的气密电阻熔焊时,应采用平行缝焊工艺;(4)对边缘为矩形、圆形等规则形状盖板的外壳进行焊接,宜采用平行缝焊工艺。

2、平行缝焊的主要工序应符合下列规定:(1)应检查被焊件是否满足焊接结构和尺寸要求,并应清洗被焊件表面;(2)应根据腔体与盖板的大小和厚度,散热情况的差异选择或编辑适宜的平行缝焊封盖程序,合理选择电极移动的速率、电流脉冲的强度和持续时间、脉冲之间的时间间隔、电极对盖板的压力、电极移动的距离等平行缝焊工艺参数,盖板焊接部位厚度宜为0.1mm~0.15mm,新程序试封后宜进行检漏实验,合格后方进行正式封装;(3)平行缝焊材料体系的组成要求应根据材料的热膨胀系数决定;(4)组件内部水汽含量要求严格时,应将焊接件及对应的盖板、夹具放入烘箱中,充入氮气并抽真空,真空度达到规定要求时开始加热并应保温一段时间;(5)应确认手套箱内水汽含量达标后,将烘烤后的产品移入缝焊操作箱(手套箱)并关严箱门,宜在4h内完成密封,当产品在操作箱内滞留12h以上未密封时,应重新烘烤后才能进行密封;(6)应将盖板按规定方位压置在外壳底座上且二者边缘精确对准,再启动缝焊程序;应先进行分步封盖操作,确认程序无误后方可进行自动封盖操作,平行缝焊机的运行速度不宜过快;(7)盖板为矩形的外壳,宜先焊好长度方向上两条对边的平行焊道,再使壳体转90°后焊好宽度方向上另两条对边的平行焊道,两对焊道在起始点处应相互重叠形成闭合的密封焊道,矩形盖板的长、宽尺寸应对应小于壳体(底座)长、宽0. 05mm~0.1mm;(8)盖板为圆形的外壳,应使两个通有连续大电流脉冲的同轴缝焊电极压在盖板顶面的圆周边沿上,相对于壳体与盖板完成不小于180°的圆弧运动后实现缝焊密封,圆形盖板直径应小于壳体直径0.05mm~0.1mm;(9)封装的最长尺寸不超过25mm时,宜选用厚度0.1mm~0.15mm的薄板形盖板;封装的最长尺寸大于25mm时,宜选用中心区域厚度0.25mm~0.4 mm、四周边缘区厚度0.1mm~0.15mm的台阶形盖板;(10)应将已熔焊密封的产品移入与缝焊操作箱相连的充有正压氮气的密封箱中,关严操作箱侧门,再从密封箱移出;(11)平行缝焊后用显微镜检查焊缝应连续平整,不应有裂纹等缺陷;(12)应进行粗检漏和细检漏,并应测试其漏率。

微组装技术简述及工艺流程及设备教材

NASA采用厚膜混合集成技术研制了导弹制导计算机 的运算组件。其中采用了2.88in见方的厚膜多层布线基板, 组装了5个大规模半导体集成电路芯片,12个中规模半导 体集成电路芯片(TTL),6个片式电容和6个片式电阻, 629根键合互连丝。 采用厚膜集成技术制作厚膜混合集成DC∕DC变换器是 厚膜混合电路的一大类产品。其产品功率范围达1W~120 W,电流最大20A ,输出路数从单路到三路,开关频率 300kHz~550kHz,国内120W DC∕DC变换器产品的功率密 度达78W∕in3,输出电压15V ,输出电流8A,效率85 % , 纹波<100 mV 。电性能与INTERPOINT同类产品相同, 功率密度高于INTERPOINT同类产品(后者为66.3 W∕in3)。 还可制作高压输出(160V~900V)的厚膜混合集成 DC∕DC变换器.

3.类型和特点——

通常可按 MCM 所用高密度多层布线基板的结构 和工艺,将MCM分为以下几个类型。 1)叠层型MCM(MCM-L,其中L为“叠层”的 英文词“Laminate”的第一个字母)也称为L 型多芯片组件,系采用高密度多层印制电路板 构成的多芯片组件,其特点是生产成本低,制 造工艺较为成熟,但布线密度不够高,其组装 效率和性能较低,主要应用于30MHz和100个 焊点/英寸2以下的产品以及应用环境不太严酷 的消费类电子产品和个人计算机等民用领域。

八。薄膜混合电路定义及其应用特点

1.定义——采用物理汽相淀积(PVD,蒸发、溅射

和离子镀等)或化学汽相淀积(CVD)工艺 以及湿刻(光刻)或干刻(等离子刻蚀等)

图形形成技术,在基板上形成薄膜元件和布

线,然后组装微型元器件(多为芯片和片式 元器件)构成具有一定功能的微电路。 区分是“薄膜”还是“厚膜”,主要按工艺技术分,而 非主要按其膜厚度(虽然厚度有区别,GJB548中提到, 薄膜厚度通常小于5微米)

微组装工艺流程

微组装工艺流程基板的准备分为电路软基板(RT/DUroid5880 )的准备和陶瓷基板(AL2O3)的准备。

电路软基板要求操作者戴指套,将电路软基板放在干净的中性滤纸上,按图纸用手术刀切割电路板边框线和去除工艺线。

要求电路软基板的图形符合图纸要求,表面平整,没有翘曲,外形尺寸比图纸小0.1 ㎜~ 0.2 ㎜,切面平整。

工艺线的去除切地,切口断面与代线平面垂直,手指不允许不戴指套接触镀金层,以免造成氧化。

陶瓷基板的准备,要求用细金刚砂纸打磨陶瓷基板,使边缘整齐,无毛刺、无短路,然后用纯净水洗净。

基板清洗基板的清洗,通过超声清洗进行。

超声清洗是利用超声波在清洗液中的辐射,使液体震动产生数万计的微小气泡,这些气泡在超声波的纵向传播形成的负压区产生、生长,而在正压区闭合,在这种空化效应的过程中,微小气泡闭合时可以产生超过 1000 个大气压的瞬间高压,连续不断的瞬间高压冲击物体表面,使物体表面和微小缝隙中的污垢迅速剥落。

因此,超声波清洗对物体表面具有一定损伤性,经过多次实验(此实验未记录实验数据),确定合理的超声功率、去离子水用量以及清洗液的高度和清洗时间。

具体清洗流程及参数设置如下:打开超声清洗机,功率调至 100 瓦,加入去离子水,液面高度为60㎜~ 80 ㎜之间。

将电路软基板或陶瓷基板放入瓷盒中,倒入 HT1 清洗液,液面略高基板上表面 3 ㎜~ 5 ㎜,然后将整个瓷盒放入超声清洗机的支架上(水面低于清洗液 2 ㎜~ 3 ㎜),清洗时间为 Xmin ~ Xmin 。

将 95% 乙醇倒入瓷盒,液面略高于基板上表面 3 ㎜~ 5 ㎜,然后将整个瓷盒放入超声清洗机的支架上(水面低于清洗液 2 ㎜~3㎜),清洗时间为 Xmin ~ Xmin 。

将清洗完毕的基板放入 X℃±3℃的烘箱中烘 0.5h后,放入氮气保护柜。

通过上述多次实验后确定的清洗工序,清洗完成后的基板表面无油污、杂质等残留物。

腔体的准备和清洗腔体的准备主要是用手术刀打净毛刺,再用洗耳球打磨毛刺形成的杂质。

微组装倒装焊工艺

微组装倒装焊工艺

1、采用倒装焊工艺应符合下列规定:

(1)芯片有源面朝下,以凸点阵列结构与基板直接安装互连实现电气连接时,应采用倒装焊工艺;

(2)倒装焊工艺应包括再流焊、超声热压、聚合物互连粘接等工序;

(3)应针对不同的凸点材料采用不同的倒装焊工艺;

(4)下填充材料填充方式应包括毛细管底部填充、助焊(非流动)型底部填充和四角(角)-点底部填充;

(5)宜根据芯片尺寸与凸点密度选择填充方法。

2、倒装焊工艺的主要工序应符合下列规定:

(1)原芯片电极焊区应制作金属过渡层,在金属过渡层上可制作金凸点、铟凸点、镀金镍凸点、锡铅凸点和无铅凸点;

(2)金凸点、镀金焊盘的组合,可采用超声热压焊实现焊接互连;

(3)双组分粘接剂使用前应按比例配制、搅拌均匀并静置排气,单组分粘接剂宜贮存在—40℃的冷冻环境中,使用前应在室温下充分解冻并搅拌均匀、静置或真空排气;

(4)由焊料构成的凸点,可在焊盘或凸点上涂敷助焊剂,然后将待安装的芯片面朝下放置在基板上,按要求固化后通过“温度-时间”曲线进行焊料再流,完成芯片与基板的倒装焊接;

(5)采用下填充和固化工艺时,下填充操作时应倾斜基板,精确控制填充胶量;

(6)倒装焊后应清洗除净焊接产生的污染,再烘干或晾干产品;

(7)芯片倒装及下填充完成后,应目检倒装焊质量,无损检测芯片凸点电极与其基板焊区间的对准精度,并应测试所倒装芯片的抗剪切强度。

3、倒装焊的工艺运行条件应符合下列规定:

(1)倒装焊工艺宜在等于或优于7级净化区中进行;

(2)倒装焊工艺中芯片的安装、互连应同时完成;

(3)倒装焊应在氮气或氮氢混合气体的保护气氛中进行。

微组装工艺发展宣传稿

微组装工艺发展宣传稿

一块PCBA上面二十多颗芯片,而芯片就属于微电子组装技术的一种,刚好近期也在研究微电子组装工艺技术,那么下面我们就一点一点了解一下这方面的知识与发展。

众所周知,全球各地相继启动5G商用,随着5G时代到来,5G通讯、物联网、人工智能、自动驾驶、智能家居、高性能计算等应用市场日益发展壮大,对芯片产品需求也大幅增长,推动全球半导体行业回暖,同时亦对芯片产品提出了更高要求。

终端产品在向轻、薄、短、小等微型化发展,但功能性却日益增强,促使芯片产品向低价格、高效能、高整合度、更低成本的趋势演进。

一直以来,摩尔定律指引着集成电路不断向前发展,缩小晶体管尺寸的同时亦可提升产品性能,但随着摩尔定律接近极限、增速趋缓,先进封装技术成为业者满足终端产品性能提升需求的另一路径。

具体来说,不同的先进封装技术具有各自的优势,如SiP可以最大限度地优化系统性能、避免重复封装、缩短开发周期、降低成本、提高集成度等,可广泛应用于无线通讯、汽车电子、医疗电子、计算机等领域;3D封装可提高硅片效率、缩短延迟、降低功耗等,主要应用于SD存储器、3D Soc芯片、CIS、RF滤波器、指纹芯片、MEMS等。

有相关数据显示,近年来先进封装市场保持着良好的增长势头,将以

8%的年复合增长率成长,市场规模预计到2024年将达440亿美元。

目前,倒装芯片(FC)占据先进封装市场较大份额,扇出型芯片封装(Fan-out WLP)、系统级封装(SiP)、3D封装等技术增速明显。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微组装工艺1 1.1 概述集成电路产业设计、制造、封装逐渐成为衡量一个国家综合国力的重要指标之一。

先进封装技术的发展使得日本在电子系统、特别是日用家电消费品的小型化方面一度走在了世界之前。

据估计我国集成电路的年消费将达到932亿美圆约占世界市场的20其中的30将用于电子封装则年产值将达几千亿人民币。

现在每年全国大约需要180亿片集成电路但我们自己制造特别是封装的不到20。

一、微电子封装微电子封装——A Bridge from IC to System 狭义芯片级 IC Packaging 广义芯片级系统级——电子封装工程电子封装工程将基板、芯片封装体和分立器件等要素按电子整机要求进行连接和装配实现一定电气.物理性能转变为具有整机或系统形式的整机装置或设备。

二、芯片级封装涉及的技术领域芯片封装技术涉及物理、化学、化工、材料、机械、电气与自动化等学科。

所涉及材料包括金属、陶瓷、玻璃和高分子材料等。

芯片封装技术整合了电子产品的电气特性、热特性、可靠性、材料与工艺应用和成本价格等因素是以获得综合性能最优化为目的的工程技术。

1.2 微电子封装技术 1.2.1 概念一、微电子封装技术的定义利用薄膜技术及微细连接技术将半导体元器件及其它构成要素在框架和基板上布置、固定及连接引出接线端子并通过可塑性绝缘介质灌封固定构成整体结构的工艺。

二、封装的作用紧固的引脚系统将脆弱的芯片表面器件连线与外部世界连接起来物理性保护、支撑保护芯片需要外壳底座防止芯片破碎或受外界损伤环境性保护外壳密封防止芯片污染免受化学品、潮气等的影响散热封装体的各种材料本身可带走一部分热量 1.2.2 微电子封装技术的分级微电子封装可以分为几个层次零级封装、一级封装、二级封装和三级封装。

一、零级封装芯片互连级-CLP 按芯片连接方法不同又分为 1、芯片粘接IC芯片固定安装在基板上。

一般有以下几种方法 1 Au-Si合金共熔法 370?Au与Si有共熔点可在多个IC芯片装好后在氮气保护下烧结也可用超声熔焊法逐个熔焊。

此时根 Au-Si 比例为69:31所以根据温度就可以计算出一定厚度的Au大概能熔解多厚的Si: 2 Pb-Sn合金片焊接法芯片背面用Au或Ni层基板导体除Au、Pd-Ag 外可以是Cu在保护气氛中烧结烧结温度视Pb-Sn 合金片的成分而定使Pb-Sn合金片熔化后实现各金属间的焊接。

3 导电胶粘接法 2 不要求芯片背面和基板具有金属化层芯片粘接后采用导电胶固化要求的温度和时间进行固化可在干净的烘箱中完成固化操作简便。

4 有机树脂粘接法前述方法适合于晶体管或小尺寸 IC对大尺寸IC只要求芯片与基板粘接牢固即可低应力的有机树脂基可以很好的完成这项任务。

2、芯片互连技术主要有引线键合 Wire BondingWB 、载带自动焊 Tape Automated BondingTAB 和倒装焊 Flip Chip Bonding FCB 以及埋置芯片互连技术后布线技术。

1 WB技术最成熟的互连技术分为热压焊、超声焊和热压超声焊金丝球焊特点灵活方便焊点强度高可满足70微米以上尺寸和艰巨的焊接需要。

Au丝Si-Au丝Al丝。

2 TAB技术 TAB是连接芯片焊区和基板焊区的“桥梁”包括芯片焊区凸点形成载带引线制作载带引线与芯片凸点焊接载带-芯片互连焊后的基板粘接和最后的载带引线与基板焊区的外引线焊接几个部分。

TAB有单层带、双层带、三层带和双金属带几种综合性能比WB优越。

3 FCB技术芯片面朝下、将芯片焊区和基板焊区直接互连的技术。

因为互连焊接的引脚长度既是凸点的高度所以互连线最短芯片的安装面积比其他方法面积小。

无论凸点多少均一次完成省工省时。

比WB、TAB综合性能都高发展迅速。

4 埋置芯片互连技术后布线技术先将IC芯片埋置到基板或PI介质层中后再统一进行布线将IC芯片的焊区与布线金属自然相连。

二、一级封装 SCM、MCM 一级封装是将一个或多个IC芯片用适宜的材料金属、陶瓷、塑料或他们的组合封装起来同时在芯片的焊区与封装的外引脚间用上述三种芯片互连方法连接起来使之成为有实用功能的电子元器件或组合。

三、二级封装 PWB 二级封装实际上是组装是将上一级各种微电子封装产品、各种类型的元器件及板上芯片 COB 一同安装到PWB或其他基板上。

除特别要求外这一级一般不再单独加以封装。

包括通孔安装技术 THT 、表面安装技术 SMT 和芯片直接安装 DCA 技术三部分。

四、三级封装三级封装密度更高功能更全组装技术更加庞大复杂是由二级组装的各个插板或插卡再共同插装在一个更大的母板上构成的。

这是一种立体组装技术。

以上所述均为xy平面内实现的二维 2D 封装由于电子整机和系统在航空、航天、计算机等领域对小型化、轻型化、薄型化等高密度组装要求的不断提高在MCM的基础上对于有限的面积电子组装必然在二维组装的基础上向z方向发展这就是所谓的三维 3D 封装技术。

1.2.3 微电子封装技术的发展一、产生、发展过程 1947年美国贝尔实验室发明第一只晶体管开创微电子封装的历史。

巴丁肖克莱第一只晶体管布拉顿 20世纪50年代以三根引线的TO Transistor Outline 型金属-玻璃封装外壳为主后 3 来发展为各类陶瓷、塑料封装外壳。

1958年第一块集成电路诞生大大推动多引脚封装技术的发展以TO型为主。

20世纪60年代中期IC由SSI Small Scale ntegration 发展为MSI Medium Scale Integration 相应引脚数目的增加TO型不再适应封装要求双列直插式引脚封装 DIP 中小规模的主导形式。

20世纪70年代是大规模IC时期 LSI 集成度增加但尺寸相应增大。

20世纪80年代电子封装的革命——表面安装技术 Surface MountTechnologySMT 迅猛发展。

塑料四边引脚扁平封装 Plastic Quad Flat PackagePQFP 称为20世纪80年代电子封装的主导产品引脚208240个。

20世纪80—90年代IC超大规模 Very Large Scale IntegrationVLSI 阶段引脚数百至上千个四边引脚的QFP尽管引脚距离一再缩小仍难以满足需求。

引脚由周边型发展成为面阵型如针栅阵列 Pin Grid Array PGA 封装。

针栅阵列在更大规模时体积大、重量大、工艺复杂、成本高不能表面安装90年代开发出新型焊球阵列封装Ball Grid ArrayBGA 。

美国、日本继开发出BGA之后又开发出芯片尺寸封装Chip Size Package CSP 解决芯片小而封装大的问题1.2:1足以引发再次革命。

为充分发挥芯片自身功能和性能目前已实现了将多个未经封装的芯片安装在多层布线基板上再将所有芯片互连后整体封装起来即多芯片组件 Multi Chip ModuleMCM 。

此外目前在2D封装技术基础上又发展了三维电子封装技术密度更高、功能更强、性能更好、可靠性更低。

5060年代 TO型封装 DIP封装 70年代微电子封装技术的演变 80年代 QFP封装未来将向系统级封装 SOP OR SIP发展 90年代 BGA封装 MCM封装二、发展特点 1 向高密度和高I/O引脚数发展引脚由四边引出向面阵列发展 2向表面安装式封装 SMP 发展来适合表面安装技术SMT 3从陶瓷封装向塑料封装发展 4从注重IC发展芯片向先发展封装再发展芯片转移。

封装技术的发展微组装工艺三、发展趋势 I/O引脚数更多更高的电性能和热性能更轻、更薄、更小便于安装、使用和返修高可靠性成本更低、物美价廉 1.3 微电子封装工艺过程一、集成电路芯片的生产过程集成电路芯片制造的前道工序单晶硅——IC主要工艺包括光刻、腐蚀、掺杂、氧化、成膜. 集成电路芯片制造的后道工序IC——芯片。

即为微电子封装。

二、微电子封装过程集成电路芯片制造的后道工序 PBGA详细的封装制程 Taping贴片?Wafer Mount 晶圆植入?Die Saw晶片切割 ?Die Attach晶圆粘接? Cure烘烤 ?Plasma Cleaning离子清除? Wire Bond打线接合?Molding 封模?Cure烘烤Marking 印记??Cure 烘烤?Ball Mount植球 ?Flux Clean助焊剂清除 4 Singulation单颗化?PackingampDelivery包装及运送Packaging ProcessWafer?切割Sawing?贴片Die Attach?打线amp打金线Wire Bonding? 塑模Molding?贴锡球Solder Ball Attach?单颗化 Singulation Packing ?Final Test 1、划片 Wafer Sawing 划片就是把已制有电路图形的集成电路圆片切割分离成具有单个图形单元功能的芯片常用的方法有金刚刀划片、砂轮划片和激光划片等几种金刚刀划片质量不够好也不便于自动化生产但设备简单便宜目前已很少使用激光划片属于新技术范踌正在推广试用阶段。

目前使用最多的是砂轮划片质量和生产效率都能满足一般集成电路制作的要求。

Wafer Mount晶圆粘片晶元切割前首先必须在晶元背面贴上胶带 Blue Tape并固定在钢制的框架上完成晶元粘片Wafer Mount amp tapeMount的动作然后再送进晶元切割机上进行切割。

Die Saw 晶圆切割切割是为了分离Wafer上的晶粒 die 切割完后一颗颗晶粒就井然有序的排列在胶带上。

同时由于框架的支撑可避免胶带皱褶而使晶粒互相碰撞并且还可以支撑住胶带以便于搬运。

Wafer Sawing wafer 割刀 DI water去离子水蓝色胶带钢制框架切割方法 : 单步切割 single 分步切割step 斜角切割bevel 水的冲洗速度 : 80100 mm/sec刀片转速: 3000040000 rpm Full Cutting105 易产生的问题: Die Crack 晶片破裂 DI Water 去离子水的作用洗去硅的残留碎片锯口宽度36 micro meter 2、绷片和分片绷片经划片后仍粘贴在塑料薄膜上的圆片如需要分离成单元功能芯片而又不许脱离塑料薄膜时则可采用绷片机进行绷片即把粘贴在薄膜上的圆片连同框架一起放在绷片机上用一个圆环顶住塑料薄膜并用力把它绷开粘在其上的圆片也就随之从划片槽处分裂成分离的芯片。

这样就可将已经分离的但仍与塑料薄膜保持粘连的芯片连同框架一起送入自动装片机上进行芯片装片。

现在装片机通常附带有绷片机构。

分片当需人工装片时则需要进行手工分片即把已经经过划片的圆片倒扣在丝绒布上背面垫上一张滤纸再用有机玻璃棒在其上面进行擀压则圆片由于受到了压应力而沿着划片槽被分裂成分离的芯片。