TSMC工艺的版图教程

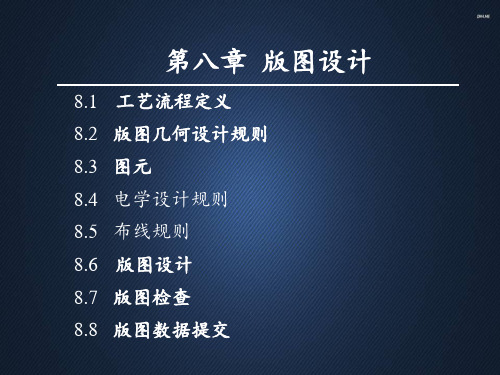

集成电路版图设计 ppt课件

(b)

图8.3 交叠的定义

表8.5 TSMC_0.35μm CMOS工艺版图各层图形之间最小交叠

表 16.5 T SM C _0.35μ m C M O S 工 艺 版 图 各 层 图 形 之 间 最 小 交 迭

N _ w e ll A c tiv e P o ly P _ l\p lu s_ se le c t/N _ p lu s_ se l ect C o n ta c t M e ta l1 V ia 1 M e ta l2 E le c tro d e V ia 2 M e ta l3

MOS管的可变参数为:栅长(gate_length)、栅宽(gate_width) 和栅指数(gates)。

栅长(gate_length)指栅极下源区和漏区之间的沟道长度,最 小值为2lambda=0.4μm。

栅宽(gate_width)指栅极下有源区(沟道)的宽度,最小栅宽为 3 lambda=0.6μm。

201010233636cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图716画l型金属线作地线图717画出两只mcs3并将它们的栅漏和源极互连201010233737vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图718画出两只mn1并将它们的栅漏和源极互连cmos差动放大器单元电路设计版图的过程201010233838图719依次画出r1并联的两只msf1和并联的两只mcf1以及偏压等半边电路版图vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outoutcmos差动放大器单元电路设计版图的过程201010233939cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图720通过对图819中半边版图对x轴作镜像复制形成的完整版图201010234040在正式用cadence画版图之前一定要先构思也就是要仔细想一想每个管子打算怎样安排管子之间怎样连接最后的电源线地线怎样走

图解芯片制作工艺流程图ppt课件

.

17

• 光刻:由此进入50-200纳米尺寸的晶体管级别。一块晶圆

上可以切割出数百个处理器,不过从这里开始把视野缩小

到其中一个上,展示如何制作晶体管等部件。晶体管相当

于开关,控制着电流的方向。现在的晶体管已经如此之小,

一个针头上就能放下大约3000万个。

.

18

• 溶解光刻胶:光刻过程中曝光在紫外线下的光刻 胶被溶解掉,清除后留下的图案和掩模上的一致。

.

12

•芯 片 加 工 无 尘 车 间

.

13

.

14

• 光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过 程中浇上去的光刻胶液体,类似制作传统胶片的那种。晶 圆旋转可以让光刻胶铺的非常薄、非常平。

.

15

.

16

• 光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得 可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。 掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上, 就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电 路图案是掩模上图案的四分之一。

.

1

.

2

INTEL 图解芯片制作工艺流程

共九个步骤

.

3

.

4

• 沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤 其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的 形式存在,这也是半导体制造产业的基础。

.

5

.

6

• 硅熔炼:12 英寸/300毫米 晶圆级,下同。 通过多步净化 得到可用于半 导体制造质量 的硅,学名电 子级硅(EGS), 平均每一百万 个硅原子中最 多只有一个杂 质原子。此图 展示了是如何 通过硅净化熔 炼得到大晶体 的,最后得到 的就是硅锭 (Ingot)。

TSMC工艺的_版图教程

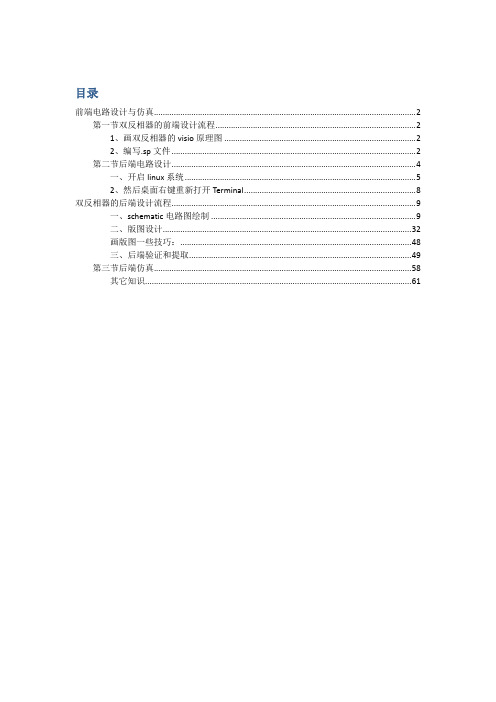

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (5)2、然后桌面右键重新打开Terminal (8)双反相器的后端设计流程 (9)一、schematic电路图绘制 (9)二、版图设计 (32)画版图一些技巧: (48)三、后端验证和提取 (49)第三节后端仿真 (58)其它知识 (61)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看.MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)精选文库一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal 输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal 进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

tsmc 工艺流程

tsmc 工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help yousolve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts,other materials and so on, want to know different data formats and writing methods, please pay attention!台积电是全球领先的半导体制造公司,其工艺流程一直备受关注和研究。

模拟集成电路版图设计基础

集成电路工艺基础

以上每道工序都是需要掩膜 版的,那掩膜版的大小怎么

定呢?如何精确呢?

P-Si N+ (e)

P-Si

N+

(f)

SiO2 (5) 淀积SiO2, 将整个结构用SiO2覆盖起来, 刻

淀积SiO2

出与源区和漏区相连的接触孔。 (6) 把铝或其它金属蒸上去, 刻出电极及互连线

铝电极引出 SiO2 (场氧)

七、如何绘制版图

1.需要的软件工具

七、如何绘制版图

2.需要做的准备

七、如何绘制版图

2.需要做的准备

七、如何绘制版图

3.打开软件

七、如何绘制版图

3.打开软件

七、如何绘制版图

3.打开软件

七、如何绘制版图

4.相关设置

七、如何绘制版图

4.相关设置

七、如何绘制版图

4.相关设置

七、如何绘制版图

划分时需考虑的因素:模块的大小,模块的数目、模块之间的连 线数。

四、版图设计的过程

2.布图规划和布局:布图规划是根据模块所包含的器件数估计其面 积,再根据该模块与其他模块的连接关系以及上一层模块或芯片的 形状估计该模块的形状和相对位置。 3.布局的任务是确定模块在芯片上的精确位置,其目标是保证在布 通的前提下使芯片面积尽可能小。 4.布线:百分之百的完成模块之间的互连,在完成布线的前提下进 一步优化布线结果,如:提高电性能、减少通孔数。

✓ PMOS管,做在N阱中,沟 道为N型,源漏为P型

2) 包括层次:

✓ NWELL,N阱 ✓ PIMP,P+注入 ✓ DIFF,有源区 ✓ Poly,栅 ✓ M1,金属 ✓ CONT,过孔

3) MOS管的宽长确定

PMOS版图

TSMC工艺的版图教程模板

TSMC工艺的版图教程模板1目录前端电路设计与仿真 ..................................................... 错误!未定义书签。

第一节双反相器的前端设计流程 .......................... 错误!未定义书签。

1、画双反相器的visio原理图 ....................... 错误!未定义书签。

2、编写.sp文件................................................ 错误!未定义书签。

第二节后端电路设计............................................... 错误!未定义书签。

一、开启linux系统......................................... 错误!未定义书签。

2、然后桌面右键重新打开Terminal ............. 错误!未定义书签。

双反相器的后端设计流程 ............................................. 错误!未定义书签。

一、 schematic电路图绘制 .............................. 错误!未定义书签。

二、版图设计................................................... 错误!未定义书签。

画版图一些技巧: .............................................. 错误!未定义书签。

三、后端验证和提取....................................... 错误!未定义书签。

第三节后端仿真....................................................... 错误!未定义书签。

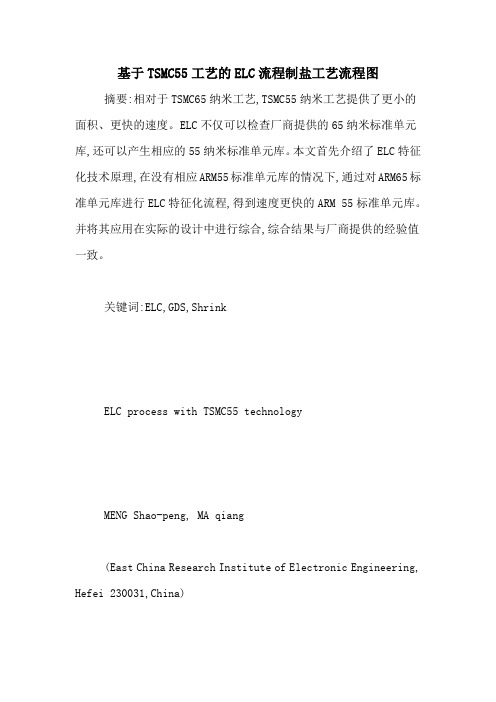

基于TSMC55工艺的ELC流程制盐工艺流程图

基于TSMC55工艺的ELC流程制盐工艺流程图摘要:相对于TSMC65纳米工艺,TSMC55纳米工艺提供了更小的面积、更快的速度。

ELC不仅可以检查厂商提供的65纳米标准单元库,还可以产生相应的55纳米标准单元库。

本文首先介绍了ELC特征化技术原理,在没有相应ARM55标准单元库的情况下,通过对ARM65标准单元库进行ELC特征化流程,得到速度更快的ARM 55标准单元库。

并将其应用在实际的设计中进行综合,综合结果与厂商提供的经验值一致。

关键词:ELC,GDS,ShrinkELC process with TSMC55 technologyMENG Shao-peng, MA qiang(East China Research Institute of Electronic Engineering, Hefei 230031,China)Abstract: Compared with TSMC 65 nm technology, TSMC 55 nm technology can provide smaller area and higher frequency. ELC (Encounter Library Characterization) not only can check the 65nm standard cell library from foundry, but also can generate the corresponding 55 nm standard cell library. This paper firstly presents a simple view of the ELC design concept, then we generate the 55nm standard cell library by applying ELC design flow on 65nm standard cell library and use it in an actual design synthesis. Experimental results demonstrate perfect consistency with values provided by foundry.Keyword:ELC;GDS;Shrink1前言随着超深亚微米技术的不断发展,特别是当设计转向90 nm以下工艺节点之后,流片成本不断增大,同时新的工艺由于其不稳定性导致流片良率下降。

集成电路工艺和版图设计参考培训课件

02.10.2020

4

生产工厂简介

PSI

02.10.2020

5

02.10.2020

Fab Two was completed January 2, 1996 and is a "State of the Art" facility. This 2,200 square foot facility was constructed using all the latest materials and technologies. In this set of cleanrooms we change the air 390 times per hour, if you do the math with ULPA filtration this is a Class One facility. We have had it tested and it does meet Class One parameters (without any people working in it). Since we are not making microprocessors here and we don't want to wear "space suits", we run it as a class 10 fab. Even though it consistently runs well below Class Ten.

6

Here in the Fab Two Photolithography area we see one of our 200mm .35 micron I-Line Steppers. this stepper can image and align both 6 & 8 inch wafers.

TSMC工艺的-版图教程

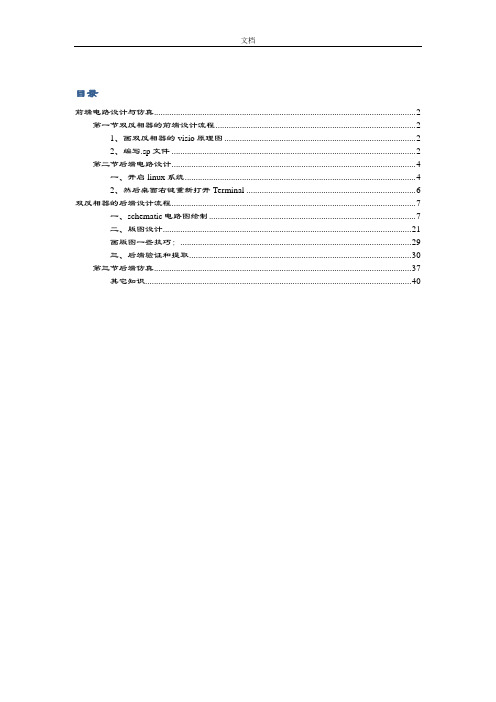

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (4)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (7)一、schematic电路图绘制 (7)二、版图设计 (20)画版图一些技巧: (29)三、后端验证和提取 (30)第三节后端仿真 (36)其它知识 (39)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压VDD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence 里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在windowXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看 .MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

TSMC实用工艺地_版图教程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (4)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (7)一、schematic电路图绘制 (7)二、版图设计 (21)画版图一些技巧: (29)三、后端验证和提取 (30)第三节后端仿真 (37)其它知识 (40)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在windowXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top 处单击这些节点即可查看波形如果有多个子电路请单击此处的Top 查看如果要查看测量语句的输出结果请查看 .MTO 文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence 软件)一、开启linux 系统双击桌面虚拟机的图标选择Power on this virtual machine开启linux之后在桌面右键选择Open Terminal输入xhost local:命令按回车之后输入su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

集成电路制造工艺流程图

在集成电路制造过程中,该公司面临生产效率低下、产品质 量不稳定等问题,需要进行工艺流程优化。

优化动机

为了提高生产效率、降低成本、提升产品质量,该公司决定 开展集成电路制造工艺流程优化实践。

工艺流程优化措施与实践

措施一

引入自动化设备与智能检测系统

具体实践

引入先进的自动化生产线和智能检测设备,实现生产过程的自动化和智能化。

集成电路制造的定义

集成电路制造是指将多个电子元件集 成在一块衬底上,通过微细加工技术 实现电路功能的过程。

集成电路制造涉及多个工艺步骤,包 括光刻、刻蚀、掺杂、薄膜淀积等, 以实现电路的设计要求。

集成电路制造的重要性

集成电路制造是现代电子工业的基础 ,广泛应用于通信、计算机、消费电 子等领域。

集成电路制造技术的发展对于提高电 子产品的性能、降低成本、促进产业 升级具有重要意义。

Hale Waihona Puke 详细描述新型封装技术如倒装焊、晶圆级封装等不断 涌现,能够实现更小体积、更高集成度的封 装形式。同时,测试技术也在向自动化、高 精度方向发展,以提高测试效率和准确性。 这些技术的发展为集成电路的性能提升和应 用拓展提供了有力支持。

04

集成电路制造的设备与材料

集成电路制造的设备

晶圆制备设备

用于制造集成电路的晶 圆制备设备,包括切割 机、研磨机、清洗机等

。

光刻设备

用于将电路图形转移到 晶圆表面的光刻设备, 包括曝光机和掩膜对准

器等。

刻蚀设备

用于在晶圆表面刻蚀出 电路图形的刻蚀设备, 包括等离子刻蚀机和湿

法刻蚀机等。

集成电路制造的材料

半导体材料

用于制造集成电路的半导体材料,如硅和锗等 。

基于TSMC55工艺的ELC流程制盐工艺流程图

基于TSMC55工艺的ELC流程制盐工艺流程图摘要:相对于TSMC65纳米工艺,TSMC55纳米工艺提供了更小的面积、更快的速度。

ELC不仅可以检查厂商提供的65纳米标准单元库,还可以产生相应的55纳米标准单元库。

本文首先介绍了ELC特征化技术原理,在没有相应ARM55标准单元库的情况下,通过对ARM65标准单元库进行ELC特征化流程,得到速度更快的ARM 55标准单元库。

并将其应用在实际的设计中进行综合,综合结果与厂商提供的经验值一致。

关键词:ELC,GDS,ShrinkELC process with TSMC55 technologyMENG Shao-peng, MA qiang(East China Research Institute of Electronic Engineering, Hefei 230031,China)Abstract: Compared with TSMC 65 nm technology, TSMC 55 nm technology can provide smaller area and higher frequency. ELC (Encounter Library Characterization) not only can check the 65nm standard cell library from foundry, but also can generate the corresponding 55 nm standard cell library. This paper firstly presents a simple view of the ELC design concept, then we generate the 55nm standard cell library by applying ELC design flow on 65nm standard cell library and use it in an actual design synthesis. Experimental results demonstrate perfect consistency with values provided by foundry.Keyword:ELC;GDS;Shrink1前言随着超深亚微米技术的不断发展,特别是当设计转向90 nm以下工艺节点之后,流片成本不断增大,同时新的工艺由于其不稳定性导致流片良率下降。

TSMC工艺处理的版图教学教程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (5)一、开启linux系统 (5)2、然后桌面右键重新打开Terminal (8)双反相器的后端设计流程 (10)一、schematic电路图绘制 (10)二、版图设计 (34)画版图一些技巧: (51)三、后端验证和提取 (53)第三节后端仿真 (63)其它知识 (68)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val ><PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在windowXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看 .MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择Open Terminal 输入xhost local:命令按回车之后输入su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal 进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

tsmc 工艺流程

tsmc 工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!TSMC 工艺流程一、设计与规划阶段。

在 TSMC 工艺流程开始之前,需要进行全面的设计与规划。

集成电路模拟版图设计基础

版图的意义:

3.

版图的工具:

– Cadence

Virtuoso Dracula Assura Diva

– Mentor

calibre

– Spring soft

laker

第一部分:了解版图

熟悉所需文件

工艺厂商提 供:.tf .display Design rule 、DRC LVS 文件、 PDK、ESD文件、金属阻 值文件

NMOS版图

2.1 器件

2.1.1 MOS管 1) NMOS管

以TSMC,CMOS,N单阱工艺 为例 PMOS管,做在N阱中,沟道为 N型,源漏为P型

2) 包括层次:

NWELL,N阱 PIMP,P+注入 DIFF,有源区 Poly,栅 M1,金属 CONT,过孔

3) MOS管的宽长确

• 频率多少? • 低寄生参数节 点?

用的?

电流多大? • 大电流在哪里?

• 认出节点 有块?

• 认出其他模块

• 认出远处部件

还有其他什么吗?

• 器件布置分面 的考虑? • 金属选择?

• 隔离要求?

3. 匹配 3.1 中心思想:

第一部分:了解版图

1. 2. 3. 4. 版图的定义 版图的意义 版图的工具 版图的设计流程

第二部分:版图设计基础

1. 2. 3. 4. 5. 认识版图 版图组成两大部件 版图编辑器 电路图编辑器 了解工艺厂商

第三部分:版图的准备

1. 2. 3. 4. 必要文件 设计规则 DRC文件 LVS文件

版图是电路图的反映,有两大组成部分

MOS管 电阻 电容 三极管(省略) 二极管(省略) 电感(省略)

[整理]TSMC工艺的_版图教程.

![[整理]TSMC工艺的_版图教程.](https://img.taocdn.com/s3/m/dcc8c7b1bceb19e8b8f6ba53.png)

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (4)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (7)一、schematic电路图绘制 (7)二、版图设计 (21)画版图一些技巧: (30)三、后端验证和提取 (31)第三节后端仿真 (37)其它知识 (40)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top 处单击这些节点即可查看波形如果有多个子电路请单击此处的Top 查看如果要查看测量语句的输出结果请查看 .MTO 文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence 软件)一、开启linux 系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录前端电路设计与仿真1第一节双反相器的前端设计流程11、画双反相器的visio原理图12、编写.sp文件2第二节后端电路设计4一、开启linux系统42、然后桌面右键重新打开Terminal7双反相器的后端设计流程8一、schematic电路图绘制8二、版图设计31画版图一些技巧:47三、后端验证和提取48第三节后端仿真57其它知识60前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看.MTO文件(用记事本打开) 至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal 输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal 进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

]双反相器的后端设计流程一、schematic电路图绘制1、注意----在Cadence中画schematic电路图时,每一个节点都需要命名,不然在参数提取之后没有命名的那些节点会被系统自动命名,导致用HSPICE查看内部节点波形时难以迅速找到自己需要的节点。

2、打开Cad ence软件新建库和单元Cell View用命令icfb&打开Cadence软件后弹出以下CIW窗口选择Flie-New-Libirary之后弹出以下窗口这里我们新建一个名为ttest的库。

(注意:在新建library的时候要attach to an existing techfile)点击OK以后弹出以下窗口在technology library这里选择我们的TSMC库tsmc18rf然后点击OK在CIW窗口的tools菜单中选择第二个library manager之后弹出以下窗口我们可以看到左边Library里面有我们之间建立的ttest库,用鼠标左键选择ttest,发现它的Cell和View都是空的。

然后在该窗口的File-New-Cell View新建一个单元Cell View弹出以下窗口在窗口的Cell name中输入我们需要取的名字,这里取的是dualinv。

点击OK后自动弹出画schematic的窗口3、画schematic电路图点击上面的这个作图版面,在键盘上按快捷键i会出现添加器件的窗口点击Browse后弹出以下窗口这里选中TSMC的库tsmc18rf,在Cell中选中pmos2v,view中选中symbol然后鼠标移到外面的画图板上,就会出现一个PMOS管,左键点击就可以放上去了,按ESC回到正常的光标状态。

同理,选中TSMC库中的nmos2v,就可以添加NMOS管。

(按快捷键M,然后再点击一下(选中)器件即可以移动器件)接下来修改MOS管的尺寸,我们看到上述MOS管的默认尺寸都是L=180n W=2u 我们这里将PMOS管修改为W=720n NMOS管修改为W=220n(注意:TSMC 0.18um库nmos2v和pmos2v最小的W只能设置到220nm,而不能设置到180nm)鼠标左键选中一个器件(如M0),然后按快捷键Q(property),出现以下调整MOS管属性窗口在w(M)的文本框中修改前面的2u 修改成我们需要的720n 然后点击OK即可同理修改NMOS管的W=220n。

之后开始连线按快捷键W(wire)即可然后添加PIN脚(即与外部信号相连的端口,从图1.1可以看出这个双反相器电路涉及到的PIN脚有in out vdd gnd)[注意:由于目前的工艺是P阱衬底,所以全部NMOS管的衬底即B端要接gnd,而PMOS管的衬底可以接自己的S端或者vdd,一般只接VDD不接S][知识补充:MOS管的衬底B端接S才能不引起衬偏,衬偏了会造成阈值电压增大]按快捷键P就可以添加PIN脚在pin name中输入名称Direction中选中pin脚的方向(其中in的direction是input out的direction是output gnd和vdd的direction是inputoutput)然后按回车,光标上就会出现一个pin的光影,点击鼠标左键即可摆放摆放pin脚之后,将PIN脚与电路相连,同样用快捷键W来连线由于图1.1中还有一个内部节点fa,这里我们就需要给内部节点命名。

按快捷键L,出现命名窗口在names这里输入fa,然后按回车然后鼠标上出现fa光影,将fa移到内部需要命名的线上点击左键即可。

然后保存电路通用,也可以用快捷键L 来连接两个单元:[这样就不用连线,却能保证两个单元连接到一起。

]在画图板左边工具栏里面选中第一个check and save4、将电路图创建成为一个symbol,用于仿真电路选择Design—Create Cellview- From Cellview 弹出以下窗口点击OK弹出以下窗口这里主要是Top Pins和Botton Pins这里需要修改,修改成如下图点击OK弹出以下电路点击save按钮保存这样我们就会看到在library manager里面就多出了一个该电路的symbol5、用spectre仿真器仿真电路(这里仿真一下电路主要是验证一下自己电路有没有画错,如果电路逻辑功能正确,那么基本上可以保证自己刚才画的电路是正确的)新建一个名为dualtest的Cell View单元(在Library Manager下)点击OK按快捷键i添加我们之前给双反相器电路创建的symbol 然后出现下图接下来就要给各个端口加激励信号和电源了按I添加器件,在analoglib中首先选择直流电压Vdc,另外还要选择vpwl作为线性分段信号源。

按Q修改vdc的属性在DC voltage这里将电压值设置为1.8v(注意,只要填入1.8即可,不要带入单位)同样修改vpwl的属性(这里我们设置一个3段线性信号,即6个点),如下图此外我们还要添加一个gnd器件作为基准地信号(在analoglib中选择) 添加完器件之后如下图(注意:电路的gnd与标准地gnd之间要添加一个0V的直流电压)接下来连线以及给输出端添加一个PIN,如下图然后按check and save保存选择tools中的Analog environment弹出以下窗口选择右边工具框中的第二个,弹出以下窗口这里设置仿真的停止时间(该时间根据自己具体需要填写),然后点OK接下来设置需要看波形的那些端口outputs—To Be Plotted—Select On Schematic 然后在要看波形的线条上单击鼠标左键点一下即可点完之后该线条会变颜色以及闪烁,之前的Analog environment窗口的outputs 中也会出现相应的名称然后点击右边工具栏中得倒数第三个Netlist and Run电路正确的话就会有波形点击该图标是分离重叠的波形——————其他快捷键——————————E 看symol里面的电路Ctrl+E 退出看内部电路F 让原理图居中P PIN管脚快捷键W 连线L 命名连线C 复制Q 器件属性M 移动U 撤销其他相关设置:设置回退次数CIW窗口--options--user preference多个器件属性一起修改,用shift选中以后然后选all selected(原先是only current)二、版图设计打开dualinv的schematic电路图,然后Tools--Design Synthesis--Layout XL之后弹出以下对话框点击OK后弹出点击OK就会自动弹出画layout的版面此时键盘上按E键,出现设置窗口这里修改分辨率,将X Snap Spacing 和Y Snap Spacing 修改为0.005,方便之后的画图。

点击OK在画layout版面的菜单中选择Design--Gen From source然后弹出以下窗口点击OK即可,版面上就生成与原schematic电路图相对于尺寸的MOS管,如下图[注:可以不gen from source而直接在画版图的版面按快捷键I添加layout器件,再修改尺寸,这样也可以通过LVS(经过测试即使版图中MOS的编号和schematic中的不同,但是最终输出子电路中MOS管编号跟schematic是相同的)]选择那四个绿色的方框和紫色的线,按delete删除,删除后就剩下四个MOS管。