第4章 组合逻辑电路 课后答案

数电第四章参考答案

第四章 组合逻辑电路 作业 参考答案【题4-1】 分析图示组合逻辑电路,列出真值表,写出输出Y 1、Y 2与输入的逻辑函数式,说明整个电路所实现的逻辑功能(不是单个输出与输入的关系,而是把2个输出与3个输入综合起来看)。

解:该电路的逻辑功能为全加器,Y 1是和,Y 2是进位。

【题4-2】某汽车驾驶员培训班进行结业考试,有三名评判员,其中A 为主评判员,B 和C 为副评判员。

在评判时,按照少数服从多数的原则通过,但主评判员认为合格,方可通过。

请填写真值表,写出逻辑表达式,并用一片74LS00(内含四个2输入端与非门)或一片74LS02(内含四个2输入端或非门)这2种方法实现此评判规定。

解:设评判员评判合格为“1”,反之为“0”; 考试通过,F 为“1”,反之为“0”。

根据题意,列真值表如下。

据此可得:ABC12ABCC B A C B A C B A AC BC AB C B A ABC Y +++=+++++=)()(1AC BC AB Y ++=2ACAB AC AB F =+=CB AC B A F ++=+=)(FB CA FB CA【题4-3】设计一个“4输入1输出”的组合逻辑电路,实现“五舍六入”的功能:即当输入的四位8421BCD 码不大于5时,输出0;否则输出1。

要求: (1) 画出卡诺图、化简逻辑函数;(2) 用1片CD4001(内含四个2输入端或非门)实现该逻辑功能(标出管脚号)。

【题4-4】设计一个代码转换电路,输入为3位二进制代码、输出为3位格雷码(见下表),要求从CD4011、CD4001、CD4030中选用1个最合适的芯片实现逻辑功能。

解:CDAB Y 00X X 0X 011001X XXCA B A C A B A BC A Y +++=++=+=))((FB CA21313546121101000111XABC00011011YABC0010111ZABCAX =BA B A B A Y ⊕=+=CB C B C B Z ⊕=+=B CAYZX【题4-5】用一片74HC138(3-8译码器)辅以“4输入与非门”实现“1位全减”。

数字电子技术第4章组合逻辑电路习题解答

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.图解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题4.4图解:(1)ABD BC CD ABD BC CD L ++=••=B AC & && & D L B A =1 =1=1FF A B & &&& & F B A(3)4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图解:(1)根据波形图得到真值表:C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

数字电子技术基础教材第四章答案

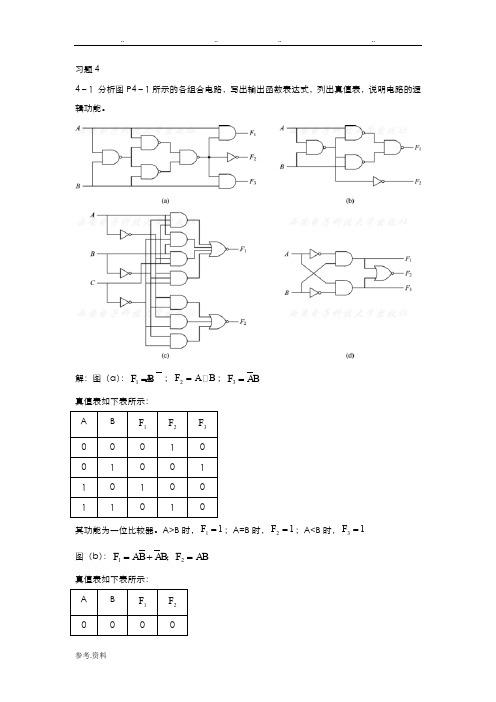

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

试列表说明电路在,,,得各种取值组合下F与A,B得逻辑关系。

解:,功能如下表所示,两个变量有四个最小项,最多可构造种不同得组合,因此该电路就是一个能产生十六种函数得多功能逻辑运算器电路。

4-5 已知某组合电路得输出波形如图P4-5所示,试用最少得或非门实现之。

解:电路图如下:4-6 用逻辑门设计一个受光,声与触摸控制得电灯开关逻辑电路,分别用A,B,C表示光,声与触摸信号,用F表示电灯。

灯亮得条件就是:无论有无光,声信号,只要有人触摸开关,灯就亮;当无人触摸开关时,只有当无关,有声音时灯才亮。

试列出真值表,写出输出函数表达式,并画出最简逻辑电路图。

解:根据题意,列出真值表如下:由真值表可以作出卡诺图,如下图:C AB 00 10 11 100 1由卡诺图得到它得逻辑表达式为: 由此得到逻辑电路为:4-7 用逻辑门设计一个多输出逻辑电路,输入为8421BCD 码,输出为3个检测信号。

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F A B =;2F A B =;3F AB =真值表如下表所示:其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示:功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,35,6)(124,7)F M m==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F A B =;2F A B =;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:由此可得:1M =当时,33232121010Yx Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

0M =当时,332321321210321010Y x Y x x Y x x x Y x Y x x x x Y x =⎧⎪=⊕⎪⎨=⊕⊕=⊕⎪⎪=⊕⊕⊕=⊕⎩ 完成格雷码至二进制的转换。

数字电子技术第四节课后习题答案(江晓安等编)

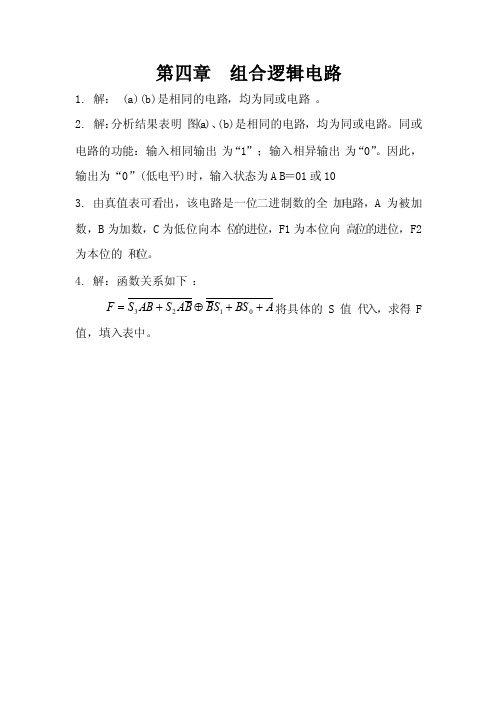

第四章组合逻辑电路1. 解:(a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一名二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:SF++⊕=+ABSABS BABS将具体的S值代入,求得312F值,填入表中。

AA FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F BA A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F ABBA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时刻数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为DC A PD B A P C B A P A P D C A P D B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

数字电子技术第四章课后习题答案(江晓安等编)

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:SF++⊕=+ABSABS BABS将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b )所示。

第四章(组合逻辑电路)习题解答

第四章 组合逻辑门电路4.2 试分析图中所示电路的逻辑功能。

解:Y AB AB AB AB A B ==+=⊕可知,图中所示电路为异或门电路。

4.3 试分析图中所示电路是否合理,并写出其最简与-或表达式。

A CB DB C D图4.3解:(1)由图写出逻辑表达式:Y AC B BD BC BC D =(2)化为与-或表达式:()()()Y AC B BD BC BC DAC B BD BC BC D AC B BD BC B C D ABCD ABC BC BD CD==+=++++=++++(3)由与-或表达式作出图示卡诺图:(4)由卡诺图得出最简逻辑表达式: Y A C B C D =++ 可见,图示电路不合理。

4.7 路灯由安装在三个不同地方的开关A 、B 、C 控制。

当总电源开关闭合时,三个开关可控制路灯的点亮和熄灭,这时,一个开关动作时灯亮,另一个开关动作时灯熄灭。

当总电源开关S 断开时,路灯不会亮。

试用与非门设计该路灯控制电路。

解:(1)分析设计要求并列出真值表:设总电源开关S 闭合时为1,断开时为0;路灯控制开关A 、B 、C 动作时为1,不动作时为0; 灯用Y 表示,灯灭为0,灯亮为1。

由此可列出真值表,如表题4.7所示:(2)求出最简与-或表达式 由真值表作出卡诺图,如图题4.7(a)所示。

由图可知,该逻辑函数已不能进一步化简。

因此,可直接写出逻辑表达式: Y A BC AB C A B C AB C =+++ 由真值表可知,S=0,Y=0;S=1时,Y 受A 、B 、C 的控制。

因此,符合题意要求的逻辑表达式应为:()Y S ABC ABC ABC ABC =+++ 将上式变换为与-非表达式:Y S ABC SABC SABC SABC = (3)画出逻辑图:如图题4.7(b)所示。

图题4.7C S(a )(b )4.8 由与非门设计一个数值范围判别电路。

设电路输入A 、B 、C 、D 为表示1位十进制数X 的8421BCD 码,当X 符合下列条件时,输出Y=1,否则输出为0。

组合逻辑电路 课后答案

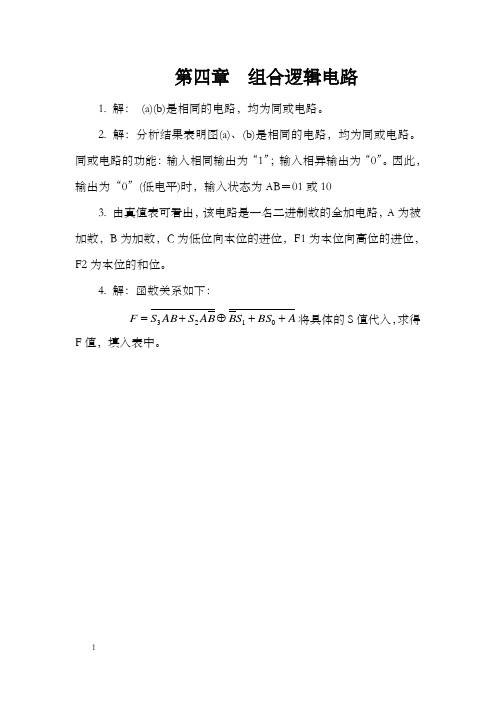

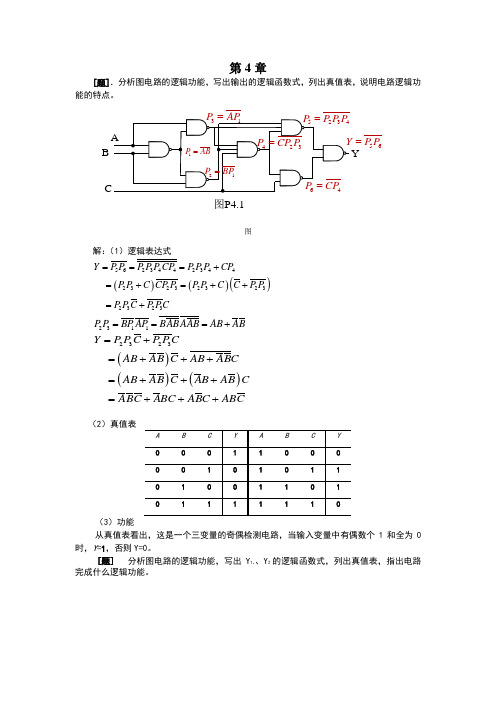

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第4章[题4.1].分析图P4.1电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图P4.2解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题4.3] 分析图P4.3电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题4.4] 图P4.4是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP =0、Z=0的真值表从略。

[题4.5] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题4.5的真值表如表A4.5所示,逻辑图如图A4.5(b)所示。

表A4.5输 入输 出A B C D 0 0 0 0 0 00 0 0 1 0 1 0 1 0 10 0 0 1 1 0 1 1 0 0 0 1 1 01 1 Y000010001 0 1 0 1 0 1 01 1 1 1 1 11 1 0 0 0 1 1 0 1 1 0 00 1 1 0 1 100010111输 入输 出A B C D Y由表4.5可写输出逻辑函数式Y ABCD ABCD ABCD ABCD ABCD ABC ABD ACD BCD=++++=+++填卡诺图,如图A 4.5(a)所示合并最小项,得最简与—或式Y ABC ABD ACD BCD =⋅⋅⋅00 01 11 1000011110Y AB CD0 0 0 00 0 1 00 1 1 10 0 1 0图A4.5 aAB C 图A4.5bD[题4.6] 有一水箱由大、小两台泵M L 和M S 供水,如图P4.6所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

图P4.6[解] 题4.6的真值表如表A4.6所示。

表A4.6真值表中的C B A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A4.4(a)化简后得到:SM LMS M A BC =+, L M B =(M S 、M L 的1状态表示工作,0状态表示停止)。

逻辑图如图A4.6(b)。

[题4.7] 设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

可以采用各种逻辑功能的门电路来实现。

[解] 题4.7的真值表如表A4.7所示。

由真值表得到 33A Y =, 232A A Y ⊕=, 121A A Y ⊕=, 010A A Y ⊕= 逻辑图如图A4.7所示。

图A4.71234A[题4.8] 试画出用4片8线-3线优先编码器74LS148组成32线-5线优先编码器的逻辑图。

74LS148的逻辑图见图4.3.3。

允许附加必要的门电路。

[解] 以310~I I 表示32个低电平有效的编码输入信号,以D 4D 3D 2D 1D 0表示输出编码,可列出D 4、D 3与Y EX4Y EX3Y EX2Y EX1关系的真值表。

如表A4.8所示。

从真值表得到34344EX EX EX EX Y Y Y Y D ⋅=+= 24243EX EX EX EX Y Y Y Y D ⋅=+=逻辑电路图略。

[题4.9] 某医院有一、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

现要求当一号病室的铵钮按下时,无论其他病室内的按钮是否按下,只有一号灯亮。

当一号病室的按钮没有按下,而二号病室的按钮按下时,无论三、四号病室的按钮是否按下,只有二号灯亮。

当一、二号病室的按钮都未按下而三号病室的按钮按下时,无论四号病室的铵钮是否按下,只有三号灯亮。

只有在一、二、三号病室的按钮均未按下,而四号病室的按钮按下时,四号灯才亮。

试分别用门电路和优先编码器74LS148及门电路设计满足上述控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

74LS148的逻辑图如图P4.9所示,其功能表如表P4.9所示。

表 P4.9 74LS148的功能表[解]设一、二、三、四号病室分别为输入变量1234A A A A 、、、,当其值为0时,表示呼叫按钮按下,为1时表示没有按呼叫铵钮,将它们接到74HC148的3210I I I I 、、、输入端后,便在74HC148的输出端210Y Y Y 、、得到对应的输出编码;设一、二、三、四号病室呼叫指示灯分别为Z 1、Z 2、Z 3、Z 4,其值为1指示灯亮,否则灯不亮,列出真值表,如表A4.9示。

表A4.9将该真值表与表P4.9对照可知,在74LS148中47I I 应接1,0,1EX S Y ==。

则 1210221032104210S S S S Z Y Y Y Y Z Y Y Y Y Z Y Y Y Y Z Y Y Y Y⎧=⎪=⎪⎨=⎪⎪=⎩由上式可得出用74LS148和门电路实现题目要求的电路如图A4.9所示。

1Z 2Z 3Z 4Z Y Y Y Y Y[题4.10] 写出图P4.10中Z 1、Z 2、Z 3的逻辑函数式,并化简为最简的与-或表达式。

74LS42为拒伪的二-十进制译码器。

当输入信号A 3A 2A 1A 0为0000~1001这10种状态时,输出端从90Y Y 到依次给出低电平,当输入信号为伪码时,输出全为1。

[解]图P4.1012Z 3ZNOP M P O N M P O N M Y Y Y Z ++==7411P O N M P O N M P O N M Y Y Y Z ++==8522P O N M P O N M P O N M Y Y Y Z ++==9633利用伪码用卡诺图化简,得:NOP P O N P O N M Z +++=1 P M P O N P O N Z ++=2MP P NO OP N Z ++=3约束条件: 0=+MO MN[题4.11] 画出用两片4线-16线译码器74LS154组成5线-32线译码的接线图。

图P4.11是74LS154的逻辑框图,图中B A S S 、是两个控制端(亦称片选端)译码器工作时应使B A S S 、同时为低电平,输入信号A 3、A 2、A 1、A 0为0000~1111这16种状态时,输出端从150Y Y 到依次给出低电平输出信号。

图A4.11[解] 电路如图A4.11所示。

当A 4=0时,片(1)工作,150Y Y ⋅⋅⋅对应输出低电平;当A 4=1时,片(2)工作,3116Y Y ⋅⋅⋅对应输出低电平。

[题4.12] 试画出用3线-8线译码器74LS138和门电路产生多输出逻辑函数的逻辑图(74LS138逻辑图如图P4.12所示,功能表如表P4.12所示)。

⎪⎩⎪⎨⎧+=++==C AB C B Y BC C B A C B A Y AC Y 321图P4.12表P4.12 74LS138 功 能 表[解] 令A=A 2,B=A 1 ,C=A O 。

将Y 1Y 2Y 3写成最小项之和形式,并变换成与非-与非形式。

∑===751Y Y )7 5i (mi Y74312Y Y Y Y )7,4,3,1j (mj Y ===∑ ∑===6403Y Y Y 0,4,6)mk(k Y用外加与非门实现之,如图A4.12所示。

图A4.1223Y 1[题4.13] 画出用4线-16线译码器74LS154(参见题4.11)和门电路产生如下多输出逻辑函数的逻辑图。

D C B A D C B A D C B A D C B A Y 1+++= D ABC D C AB CD B A BCD A Y +++=2 B A Y =3[解]842184211Y Y Y Y m m m m Y =+++= 141311714131172Y Y Y Y m m m m Y =+++=765476543Y Y Y Y m m m m Y =+++=电路图如图A4.13所示。

图A4.13231[题4.14] 用3线-8线译码器74LS138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;输出为两数之差及向高位的借位信号。

[解] 设a i 为被减数,b i 为减数,c i-1为来自低位的借位,首先列出全减器真值表A4.14,然后将Di ,Ci 表达式写成非-与非形式。

最后外加与非门实现之。

由全减器真值表知:1111----+++=i i i i i i i i i i i i i c b a c b a c b a c b a D7421m m m m +++=7421m m m m =7421Y Y Y Y =全减器真值表输 入输 出M i N i B i-10110100 10 0 00 0 10 1 00 1 11 0 01 0 11 1 0 1 1 1D i 表4.140111000 1B i同理可知 7321Y Y Y Y Ci =令a i =A 2,b i =A 1,c i-1=A 0。