电子科技大学研究生复试.数电大纲

杭州电子科技大学2017年数字电路与信号系统硕士入学考试大纲

杭州电子科技大学2017年数字电路与信号系统硕士入学考试大纲一、数字与编码1、数制变换:二进制、八进制、十六进制与十进制的整数和小数转换。

2、数的表示形式:有符号数和无符号数的运算、处理;原码、反码和补码表示方法和性质。

3、常见编码:常用8421BCD码、余3码和格雷码等性质和特点。

二、逻辑门功能及其电路特性1、CMOS门电路外部特性:输入、输出和传输特性,阈值电平和低功耗特性。

2、CMOS逻辑门基本结构与工作原理。

3、特殊门电路:三态门、OC/OD门、CMOS传输门的特性及应用。

三、逻辑函数运算规则及化简1、逻辑基本概念:与或非代数系统的定义、性质。

2、逻辑函数的表述方法和形式:最大项、最小项,“与或式”和“或与式”转换。

3、逻辑代数运算规则:常用的逻辑运算定律和公式,反函数和对偶函数变换。

4、逻辑证明:逻辑表达式变换和推导、证明。

5、逻辑化简:公式法和卡诺图化简逻辑函数,一次降维卡诺图的变换。

四、逻辑电路设计与分析1、组合逻辑电路分析:采用门电路构成的组合电路以及采用编码器、译码器、数据选择器、数据分配器、加法器和比较器等中规模组合集成电路构成的组合逻辑电路分析系。

2、组合逻辑电路设计:采用门电路设计组合逻辑电路;采用译码器或数据选择器设计组合逻辑电路。

3、中规模组合集成电路芯片的应用。

4、广义译码器的概念。

五、触发器及含触发器的PLD1、常见触发器特性:基本RS触发器、电平型D锁存器、边沿型D触发器、边沿型JK触发器、T和T’触发器的功能和特性方程。

2、触发器转换:不同触发器的相互转换。

3、触发器的应用。

六、时序逻辑电路的分析与设计1、时序电路特点与表达形式:时序电路特点、时序电路状态转换表、状态图和时序图;2、寄存器:并行寄存器与移位寄存器。

3、时序电路分析:采用触发器构成的同步和异步时序电路分析、采用集成同步计数器、集成异步计数器和移位寄存器构成的时序电路分析。

4、同步时序电路设计:采用触发器设计计数器和分频器、序列检测器和序列发生器;采用中规模集成计数器设计任意进制计数器和分频器;采用移位寄存器设计移存型计数器和序列发生器等。

考研复试数字电路大纲

考研复试数字电路大纲可能包括以下内容:

数字电路基础知识,包括数字电路的基本概念、数制与码制、逻辑代数与逻辑函数、门电路等。

组合逻辑电路,包括组合逻辑电路的分析与设计方法、常见组合逻辑电路及其应用等。

时序逻辑电路,包括时序逻辑电路的分析与设计方法、常见时序逻辑电路及其应用等。

半导体存储器,包括半导体存储器的分类、结构、工作原理及应用等。

可编程逻辑器件,包括可编程逻辑器件的分类、结构、工作原理及应用等。

数字系统设计,包括数字系统的基本概念、设计方法、常见数字系统及其应用等。

具体内容可能会因学校和专业的不同而有所差异,建议查阅相关学校或专业的考研复试大纲或参考书目,以了解具体要求。

杭州电子科技大学-2019年-自命题科目考试大纲-849数字电路与信号系统

杭州电子科技大学全国硕士研究生入学考试业务课考试大纲考试科目名称:数字电路与信号系统科目代码:849 数字电路部分一、数字与编码1、数制变换:二进制、八进制、十六进制与十进制的整数和小数转换。

2、数的表示形式:有符号数和无符号数的运算、处理;原码、反码和补码表示方法和性质。

3、常见编码:常用8421BCD码、余3码和格雷码等性质和特点。

二、逻辑门功能及其电路特性1、CMOS门电路外部特性:输入、输出和传输特性,阈值电平和低功耗特性。

2、CMOS逻辑门基本结构与工作原理。

3、特殊门电路:三态门、OC/OD门、CMOS传输门的特性及应用。

三、逻辑函数运算规则及化简1、逻辑基本概念:与或非代数系统的定义、性质。

2、逻辑函数的表述方法和形式:最大项、最小项,“与或式”和“或与式”转换。

3、逻辑代数运算规则:常用的逻辑运算定律和公式,反函数和对偶函数变换。

4、逻辑证明:逻辑表达式变换和推导、证明。

5、逻辑化简:公式法和卡诺图化简逻辑函数,一次降维卡诺图的变换。

四、逻辑电路设计与分析1、组合逻辑电路分析:采用门电路构成的组合电路以及采用编码器、译码器、数据选择器、数据分配器、加法器和比较器等中规模组合集成电路构成的组合逻辑电路分析系。

2、组合逻辑电路设计:采用门电路设计组合逻辑电路;采用译码器或数据选择器设计组合逻辑电路。

3、中规模组合集成电路芯片的应用。

4、广义译码器的概念。

五、触发器及含触发器的PLD1、常见触发器特性:基本RS触发器、电平型D锁存器、边沿型D触发器、边沿型JK触发器、T和T’触发器的功能和特性方程。

2、触发器转换:不同触发器的相互转换。

第1页共5页。

电子科大836专业复试提纲

002电子工程学院考试科目复试模拟电路考试形式笔试(闭卷)考试时间120分钟考试总分200分(推免生复试100分)一、总体要求《模拟电路》要求掌握半导体器件:晶体二极管、双极型晶体三极管(BJT)和场效应晶体三极管(FET)的工作原理;掌握二极管单向导电性的基本应用和反向击穿特性及其应用;掌握BJT 和FET基本放大器的小信号等效电路分析方法,并应用于实用电路的工程估算;理解放大器的频率特性概念及其描述,根据单管放大器频率响应求解低、高频截止频率;掌握模拟IC中重要单元电路,如差动放大器、互补推挽输出电路等的分析计算方法;掌握负反馈放大电路的工作原理和分析方法;能用理想运放分析法分析集成运放构成的信号运算电路;掌握直流电源基本概念及其应用。

二、内容及比例A 半导体材料及二极管1、了解半导体的基本知识本征半导体与杂质半导体(P型与N型);本征激发与复合;杂质电离;空穴导电原理;多子与少子;漂移电流与扩散电流的概念;PN结的形成(耗尽层、空间电荷区和势垒区的含义);PN 结的单向导电特性;不对称PN结。

2、掌握二极管的基本知识二极管单向导电特性及二极管伏安特性方程;二极管伏安特性曲线及其温度特性;二极管导通电压与反向饱和电流;二极管的直流电阻与交流电阻(估算式);硅管与锗管的区别。

3、二极管应用掌握单向导电特性应用:整流与限幅。

能分析简单二极管电路。

正向导通特性应用:恒压源模型及小信号模型。

反向击穿特性及应用:了解反向击穿现象;掌握稳压管工作原理及电路。

了解电容效应及应用:势垒电容与扩散电容;变容二极管原理。

B 双极型晶体三极管(BJT)1、理解BJT工作原理NPN与PNP管;放大偏置特点;放大偏置时内部载流子传输;放大偏置时外电流关系(掌握直流传输方程,α,β,I CBO,I CEO的概念);放大偏置时的v BE、v CE的作用(正向电压的指数控制作用和反向电压的基区宽调效应);BJT的截止与饱和状态及特点。

杭州电子科技大学《数字电路与信号系统》考研大纲_杭电考研大纲

杭州电子科技大学《数字电路与信号系统》考研大纲数字电路部分一、数字与编码1、数制变换:二进制、八进制、十六进制与十进制的整数和小数转换。

2、数的表示形式:有符号数和无符号数的运算、处理;原码、反码和补码表示方法和性质。

3、常见编码:常用8421BCD码、余3码和格雷码等性质和特点。

二、逻辑门功能及其电路特性1、CMOS门电路外部特性:输入、输出和传输特性,阈值电平和低功耗特性。

2、CMOS逻辑门基本结构与工作原理。

3、特殊门电路:三态门、OC/OD门、CMOS传输门的特性及应用。

三、逻辑函数运算规则及化简1、逻辑基本概念:与或非代数系统的定义、性质。

2、逻辑函数的表述方法和形式:最大项、最小项,“与或式”和“或与式”转换。

3、逻辑代数运算规则:常用的逻辑运算定律和公式,反函数和对偶函数变换。

4、逻辑证明:逻辑表达式变换和推导、证明。

5、逻辑化简:公式法和卡诺图化简逻辑函数,一次降维卡诺图的变换。

四、逻辑电路设计与分析1、组合逻辑电路分析:采用门电路构成的组合电路以及采用编码器、译码器、数据选择器、数据分配器、加法器和比较器等中规模组合集成电路构成的组合逻辑电路分析系。

2、组合逻辑电路设计:采用门电路设计组合逻辑电路;采用译码器或数据选择器设计组合逻辑电路。

3、中规模组合集成电路芯片的应用。

4、广义译码器的概念。

五、触发器及含触发器的PLD1、常见触发器特性:基本RS触发器、电平型D锁存器、边沿型D触发器、边沿型JK 触发器、T和T’触发器的功能和特性方程。

2、触发器转换:不同触发器的相互转换。

3、触发器的应用。

六、时序逻辑电路的分析与设计1、时序电路特点与表达形式:时序电路特点、时序电路状态转换表、状态图和时序图;2、寄存器:并行寄存器与移位寄存器。

3、时序电路分析:采用触发器构成的同步和异步时序电路分析、采用集成同步计数器、集成异步计数器和移位寄存器构成的时序电路分析。

4、同步时序电路设计:采用触发器设计计数器和分频器、序列检测器和序列发生器;采用中规模集成计数器设计任意进制计数器和分频器;采用移位寄存器设计移存型计数器和序列发生器等。

电子科技大学自动化学院研究生复试大纲

自动化工程学院复试考试大纲更新时间:2012/9/27 点击数:2585微机原理及数字电路复试考试大纲(闭卷)(200分)(推免生复试总分100分,微机原理和数字电路各占50%)对象:报考自动化工程学院080400仪器科学与技术、081100控制科学与工程、085203仪器仪表工程、085210控制工程的学生《微机原理及应用》(100分)一.参考书目:《微处理器系统结构及嵌入式系统设计(第二版)》李广军电子工业出版社《微机系统原理与接口技术》李广军电子科技大学出版社二.本大纲适合专业本大纲适用于自动化、仪器与测量技术等各类工科电子类非计算机专业。

三.内容要求1.概述要求内容:计算机发展历程,集成电路与SoC设计,先进的处理器技术,信息在计算机中的表示方法。

指令、程序的概念以及程序的执行过程。

嵌入式系统的概念、特点、组成、发展现状与趋势。

2.计算机系统的结构组成与工作原理要求内容:计算机系统的基本结构与组成,计算机系统的工作原理,微处理器体系结构的改进,计算机主要性能评测指标。

3.微处理器体系结构及关键技术要求内容:微处理器体系结构,处理器设计技术,指令系统设计,流水线技术,典型微处理体系结构。

4.总线技术与总线标准要求内容:总线技术概述、总线仲裁、总线操作与时序,总线标准(片内AMBA总线、PCI系统总线、异步串行通信总线。

5.存储器系统要求内容:存储器件的分类,半导体存储器的基本结构与性能指标;存储系统的层次结构,主存储器设计技术(存储器地址分配原则;译码电路设计方法;存储器接口设计设计;存储器系统设计方法)。

6.输入输出接口要求内容:输入/输出接口基础(接口和端口的概念,输入/输出接口功能与结构,端口的编址方法,端口地址的分配原则);接口地址译码;接口信息传输方式;并行接口,串行接口,定时/计数接口、AD/DA 接口的结构特点及设计要点7.ARM微处理器编程模型要求内容:ARM 内核体系结构,ARM 编程模型(处理器工作状态、处理器运行模式、寄存器组织、数据类型和储存格式、异常)。

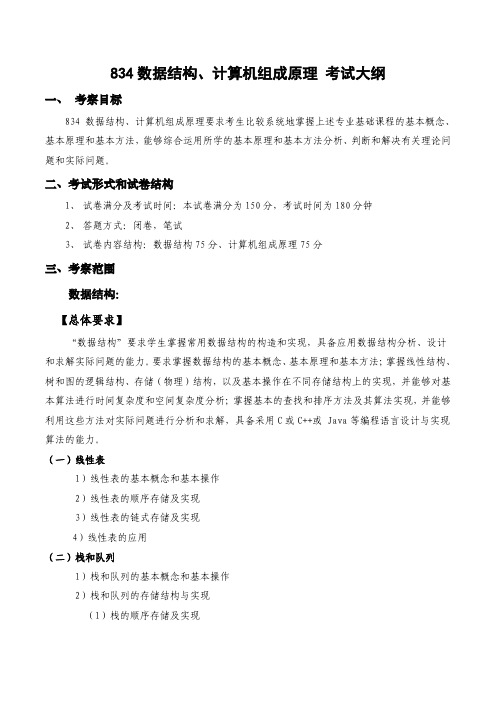

834数据结构、计算机组成原理 西电 西安电子科技大学 2022年硕士研究生招生考试自命题考试大纲

834数据结构、计算机组成原理考试大纲一、考察目标834 数据结构、计算机组成原理要求考生比较系统地掌握上述专业基础课程的基本概念、基本原理和基本方法,能够综合运用所学的基本原理和基本方法分析、判断和解决有关理论问题和实际问题。

二、考试形式和试卷结构1、试卷满分及考试时间:本试卷满分为150分,考试时间为180分钟2、答题方式:闭卷,笔试3、试卷内容结构:数据结构75分、计算机组成原理75分三、考察范围数据结构:【总体要求】“数据结构”要求学生掌握常用数据结构的构造和实现,具备应用数据结构分析、设计和求解实际问题的能力。

要求掌握数据结构的基本概念、基本原理和基本方法;掌握线性结构、树和图的逻辑结构、存储(物理)结构,以及基本操作在不同存储结构上的实现,并能够对基本算法进行时间复杂度和空间复杂度分析;掌握基本的查找和排序方法及其算法实现,并能够利用这些方法对实际问题进行分析和求解,具备采用C或C++或 Java等编程语言设计与实现算法的能力。

(一)线性表1)线性表的基本概念和基本操作2)线性表的顺序存储及实现3)线性表的链式存储及实现4)线性表的应用(二)栈和队列1)栈和队列的基本概念和基本操作2)栈和队列的存储结构与实现(1)栈的顺序存储及实现(2)栈的链式存储及实现(3)队列的链式存储及实现(4)循环队列的定义及实现3)栈和队列的应用(三)串1)串的基本概念和基本操作2)串的顺序存储、链式存储及实现3)串的模式匹配(1)基本的模式匹配算法(2)KMP模式匹配算法(模式串的next函数计算)(四)数组和广义表1)数组的基本概念和基本操作2)数组的顺序存储3)特殊矩阵的压缩存储、稀疏矩阵的压缩存储4)广义表的基本概念和存储结构(五)树与二叉树1)树的基本概念2)二叉树(1)二叉树的定义及性质(2)二叉树的顺序存储和链式存储(3)二叉树的先序、中序、后序遍历和层序遍历运算(4)线索二叉树的定义与基本运算3)树和森林(1)树的存储结构(2)树(森林)与二叉树的相互转换(3)树和森林的遍历4)哈夫曼(Huffman)树的构造与应用(六)图1)图的基本概念和基本操作2)图的存储结构(1)数组表示法(邻接矩阵表示法)(2)邻接表表示法、逆邻接表表示法(3)邻接多重表(4)十字链表3)图的遍历(1)深度优先遍历(DFS)算法(2)广度优先遍历(BFS)算法4)图的应用(1)最小生成树求解方法(Prim算法、Kruskal算法)(2)最短路径求解方法(Dijkstra算法、Floyd算法)(3)AOV-网和拓扑排序方法(4)AOE-网和关键路径求解方法(七)查找1)查找的基本概念2)静态查找表(1)无序顺序表、有序顺序表(2)顺序查找算法(3)折半查找算法、折半查找判定树的构造3)动态查找表(1)二叉查找树(二叉检索树、二叉排序树)的构造及查找、插入和删除运算(2)平衡二叉树的构造及查找运算(3)B-树的特点及查找运算(4)B+树的基本概念4)哈希表(1)哈希表的基本概念(2)哈希表的构造及查找运算5)查找算法的分析(平均查找长度计算)及应用(八)排序1)排序的基本概念(排序过程中的基本操作、排序算法的时空复杂度及稳定性)2)简单排序方法(1)直接插入排序算法(2)冒泡排序算法(3)简单选择排序算法3)快速排序4)堆排序5)归并排序6)基数排序(1)多关键排序方法(2)链式基数排序方法及特点7)外部排序的基本概念计算机组成原理:【总体要求】“计算机组成原理”要求学生掌握单处理器计算机系统中各部件的内部工作原理、组成结构以及相互连接方式,具有完整的计算机系统的整机概念。

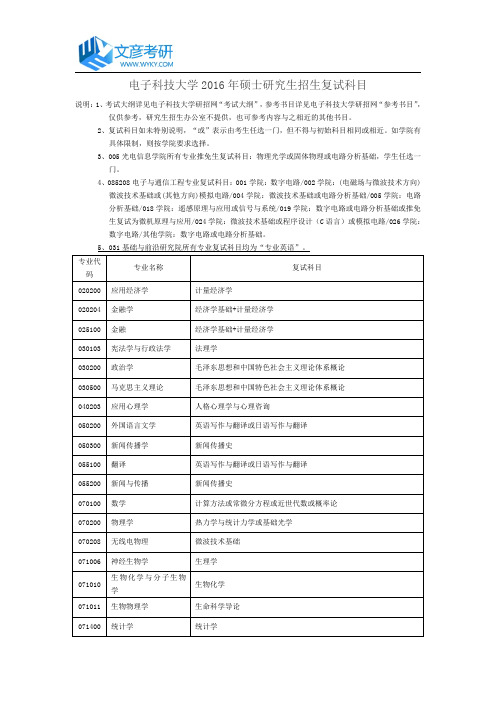

电子科技大学2016年硕士研究生招生复试科目_电子科技大学研究生院

复试科目 001 学院:数字电路或光电子技术基础/005 学院:应用光学或固体物 理或电路分析基础/024 学院:数字电路 微机原理及数字电路 003 学院:电路分析基础或无机化学或电子材料/017 学院:电子材料 详见硕士招生简章复试科目表头说明 数字电路与模拟电路 007 学院:微机原理及数字电路/017 学院:微机原理/019 学院:微机 原理与应用或数字电路或推免生复试为微机原理与应用 《程序设计》(C语言) 程序设计(C 语言)或数字电路 微机原理与应用或数字电路 经济学 经济学 经济学 (01 方向)临床药物治疗学/(02 方向)药理学/(03 方向)药剂学/(04 方 向)药物分析/(05 方向)生物化学/(06 方向)药事管理学 (01 方向)医学影像或(02 方向)外科学|内科学或(03 方向)外科学|妇 产科学或(04 方向)外科学或(05 方向)内科学|外科学|神经病学|眼视 光的基础与临床|皮肤病与性病学|耳鼻咽喉头颈外科学/(06 方向)口 腔综合 数字电路 经济学+运筹学 经济学基础+计量经济学 经济学+运筹学 经济学+运筹学 经济学+运筹学 政治学 综合测试(含政治理论) 综合测试(含政治理论)

080902 电路与系统

024 学院:模拟电路或电路分析基础/其他学院:模拟电路

微 电 子 学 与 固 体 电 子 003 学院:数字电路与模拟电路/005 学院:固体物理和电路分析基础

080903

学

/024 学院:数字电路/031 学院:专业英语

080904 电磁场与微波技术

005 学院:电路分析基础/其他学院:微波技术基础

文章来源:文彦考研旗下电子科技大学考研网

085210 控制工程

085211 计算机技术 085212 软件工程 085230 生物医学工程 085236 工业工程 085239 项目管理 085240 物流工程

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

门电路的工作原理和特性、CMOS传输门、施密特触发器结构和工作原理。逻辑电路的静态、动态特性分析;三态输出结构、漏极开路输出结构;

3、逻辑代数基础

逻辑代数的公理、定理,对偶关系;逻辑函数的表达形式:积之和与和之积标准型、真值表;组合电路的分析:逻辑函数的化简,无关项的处理、冒险问题和多输出逻辑化简的方法。

三、题型及分值比例

1、选择题:10%

2、画图题:10%

3、化简题:10%

4、分析题:30%

5、设计题:30%

6.综合题:10%

4、组合逻辑设计

利用基本的逻辑门完成组合逻辑电路的设计,利用基本的逻辑门和已有的中规模集成电路(MSI)逻辑器件如译码器、编码器、多路选择器、多路分配器、异或门、比较器、全加器、三态器件等作为设计的基本元素完成更为复杂的组合逻辑电路设计的方法。

5、时序逻辑基础与分析

基本时序元件R-S型,D型,J-K型,T型锁存器、触发器的电路结构,工作原理,时序特性,功能表,特征方程表达式,不同触发器之间的相互转换;钟控同步状态机的模型图,状态机类型及基本分析方法和步骤,使用状态表表示状态机状态转换关系;钟控同步状态机的设计:状态转换过程的建立,状态的化简与编码赋值、使用状态转换表的设计方法、使用状态图的设计方法。

考试科目

复试数字逻辑

120分钟

考试总分

200分

一、总体要求

掌握数字逻辑电路的基本原理与特性、数字逻辑电路的基本分析方法和设计方法,具备数字逻辑电路设计和综合的基本技能。

二、内容及比例

1、数系与代码

数的十进制、二进制、八进制和十六进制表示以及它们之间的相互转换,符号数的S-M码,补码,反码表示以及它们之间的相互转换;带符号数的补码的加减运算;BCD码、GREY码;

6、时序逻辑设计

利用基本的逻辑门、时序元件作为设计的基本元素完成规定的钟控同步状态机电路的设计任务:计数器、位移寄存器、序列检测电路和序列发生器的设计;利用基本的逻辑门和已有的中规模集成电路(MSI)时序功能器件作为设计的基本元素完成更为复杂的时序逻辑电路设计的方法。

7、存储器及其在数字逻辑系统实现中的运用

存储器(ROM,SRAM)的基本工作原理和结构;存储器在数字逻辑系统设计的硬件实现中的运用。

8、模数转换器、数模转换器(ADC/DAC)原理及应用简介

模拟-数字转换器、数字-模拟转换器(ADC/DAC)的基本电路结构、工作原理和应用。

9、脉冲电路

单稳态电路工作原理、电路结构和工程应用,限幅电路工作原理和电路结构,多谐振荡器工作原理和电路结构、工程应用,555定时器的工作原理和应用。