电子科大数字电路最好老师的课件

合集下载

VHDL-0电子科技大学课件

组合逻辑电路的表达

根据逻辑代数的运算关系,上述函数的逻辑方 程还可以采用很多其他方式表达:

F x2 x1 x2 x0 x1x0 ' '

F x2x1'x2x0'x1x0' '

F x2 x1 x2 x0 x1 x0

组合逻辑电路的表达

建立时间容限: tclk tcq(max) tcomb (max) tsetup tskew(max) 0

保持时间容限: tcq(min) tcomb (min) thold tskew(max) 0

时序逻辑设计的要点

时序与组合的分割: 所有组合单元的规模尽量一致: 数据处理过程中的时序安排; 电路中的时钟偏斜控制:

杂的组合逻辑分割为小块电路,在电路中引入

寄存器用于中间结果的存放和转送,通过统一

的时钟协调信号转移的时间,有效提高信号的

处理频率。这就构成了时序逻辑电路。

时序逻辑的基本单元

时序逻辑中的寄存器主要分为锁存器和触

发器两类:

时序逻辑的基本单元

锁存器为时钟电平控制器件;

触发器为时钟边沿控制器件。 根据信号传输与时钟触发之间的关系,锁 存器表现为异步器件,触发器为同步器件。

组合逻辑电路的特点

组合逻辑电路用于表达数字信号的输入/输出

关系:输出信号表现为输入信号的函数。

对于一根输出线,当输入条件为某些值时, 输出1;当输入条件为其他值时,输出0。

组合逻辑电路的特点

由于每条输入线只能取2种值,当输入线 为有限条时,输入只能取有限种不同的值。

考虑任何一条输出线,对于输入取值的某

数字电路的逻辑设计 (复习内容)

电子科大数字电路课件2-2补码chenyu

Diminished Radix – Complement Representation

[ 基数减1补码表示法(反码)]

The Diminished Radix – Complement of an n-digit number is obtained by subtracting it from r n -1 [ n位数的反码等于从 r n – 1 中减去该数] Example : Table 2-4 ,2-5 P.36 (r-1)’s Complement = r

1、1011100010112= 5613

8=

B8B

16

2、 ( 156 )10 = ( 10011100

)2

3、将0.3910转换为二进制数,要求精度达到10%。 0.3910转换为二进制数 要求精度达到10% 转换为二进制数, 10%。

0.01102

Review of the last lesson

(若约定字长是一个字节,试求-11910的补码表示。)

• +11910=011101112,as formula(公式): • 2n-D= (2n-1-D)+1 • 28-1: 11111111 subtract(减去)+119; -0 1 1 1 0 1 1 1 • 1 0 0 01 0 0 0 • plus(加)1: + 1 • -11910: 1 0 0 0 1 0 0 12

Binary to Decimal Based on definitions:

00110110 2 = 25 + 2 4 + 2 2 + 21 = 5410

0.00110110 2 = 2 + 2 + 2 + 2 = 0.210937510

电子科大课件VHDL3

关于建立时间和保持时间

建立时间: 在时钟触发沿之前信号不能变动的时间;

保持时间: 在时钟触发沿之后信号不能变动的时间;

关于建立时间和保持时间

对于D触发器端口的时钟沿,只需要考虑建 立时间问题; 由于外部时钟信号需要通过长连线延迟才能 到达触发器端口,就会将内部建立时间分割 为建立时间和保持时间两段。

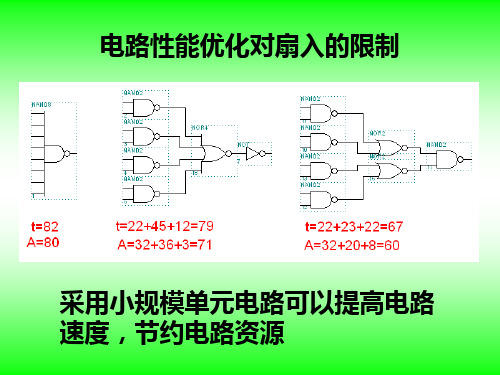

电路性能优化对扇入的限制

采用小规模单元电路可以提高电路 速度,节约电路资源

电路基本单元的结构

基本单元结构

INV,NAND2-4,NOR2-4,AOI(22);

电路基本单元的结构

增加反相器实现的同相基本单元 AND2-3,OR2-3;

电路基本单元的结构

采用并行分级实现的单元

对传输结构的分析

采用性能优化时,逻辑面积A=3; 从输入到输出的导通电阻为0.5; 输入/输出电容为18; 设其前后级均为NAND2,插入该传输缓冲对 电路延迟时间的增加为

时序电路的常用时间关系

最小时钟周期关系: tcqmax tcommax tsetmax tskewmax tclk

建立时间容限:

tclk tcqmax tcommax tset tskewmax 0

保持时间容限:

tcqmin tcommin thold tskewmax 0

t 181.5 22 0.5 38

反相三态门的实现方案

逻辑模块扇出与驱动能力

在逻辑功能单元内部设计时,可以忽略 连线延迟(电容); 考虑模块之间的连接时,连线延迟成为 主要延迟因素; 通过减小输出电阻,增加驱动能力,可 以有效减少连线延迟,提高电路速度;

逻辑模块扇出与驱动能力

若某逻辑单元的输出连接线等效电容为200

关于建立时间和保持时间

《数字电路~》PPT课件

NOL

IOL IIL

1616 1

IOH=-7.5mA,但手册规定 |IOH|<0.4mA,故取|IOH|=0.4mA;

IIL IOL

每个负载门的输入电流为

IIHNO=H 40μAIIOIHH

0.4 10 0.04

综上所述,扇出系数NO=10

IOH IIH

例:为保证G1输出的高低电平 能正确传递到G2,要求vO1=VOH、 vI2≥VIH<min>;vO1=VOL、 vI2≤VIL<max>,试计算RP的最 大允许值.所有参数见前

0 Voff1 Vth 2Von 3 VI/V

③ 输出高、低电平的最小值

输出高电平最小值VOHmin 输出低电平最大值VOLmax

2.4V 0. 4V

VOH VO/V

4 AB

VoHmin

2

C

VOL

DE 0 Voff1 Vth 2Von 3 VI/V

④ 阈值电压<Vth>: 转折区中点对应的输入电压称阈值电压Vth.

A&

B

AB

00 01 10 11

Y

Y

0 0 0 1

Y=AB

A Y

B

继续

2、二极管或门

5V A

D1 0V B

D2

Y

R

3kΩ

uA uB

0V 0V 0V 5V 5V 0V 5V 5V

uY

0V 4.3V 4.3V 4.3V

D1 D2 截止 截止 截止 导通 导通 截止 导通 导通

A ≥1

Y B

AB Y

00 0 01 1 10 1 11 1

扇出系数=10

<2> 74S20为4输入与非门:

电子科大数字电路课件3-1 chenyu

VDD = +5.0V A B Z

VDD = +5.0V

Q2 Q4

Z A B

Q1

Q3

18

NAND VS. NOR(P92)

• CMOS NAND and NOR gates do not have identical performance. • For a given silicon area, an n-channel transistor has lower “on” resistance than a p-channel transistor. • Therefore, when transistors are put in series, k n-channel transistors have lower “on” resistance than do k p-channel ones. As a result, a k-input NAND gate is generally faster than and preferred over a k-input NOR gate.

27

• CMOS逻辑系列(HC)电平规格

vcc

高态 VIHmin 0.7VCC VILmax 0.3VCC

0

VOHmin

VCC-0.1V

不正常状态 低态 VOLmax

地+0.1V

典型值:VCC=5V+10%,

Figure 3-26 Logic levels and 3noise margins for the HC-series CMOS logic family.

1

classclass-exercises

• 1、Write the 8421 binary- coded decimal ,excessbinary,excess3 ,Gray code representations for the decimal numbers: 586.

VDD = +5.0V

Q2 Q4

Z A B

Q1

Q3

18

NAND VS. NOR(P92)

• CMOS NAND and NOR gates do not have identical performance. • For a given silicon area, an n-channel transistor has lower “on” resistance than a p-channel transistor. • Therefore, when transistors are put in series, k n-channel transistors have lower “on” resistance than do k p-channel ones. As a result, a k-input NAND gate is generally faster than and preferred over a k-input NOR gate.

27

• CMOS逻辑系列(HC)电平规格

vcc

高态 VIHmin 0.7VCC VILmax 0.3VCC

0

VOHmin

VCC-0.1V

不正常状态 低态 VOLmax

地+0.1V

典型值:VCC=5V+10%,

Figure 3-26 Logic levels and 3noise margins for the HC-series CMOS logic family.

1

classclass-exercises

• 1、Write the 8421 binary- coded decimal ,excessbinary,excess3 ,Gray code representations for the decimal numbers: 586.

电子科技大学《电路分析基础》钟洪声视频配套课件8-6解读

电子科技大学《电路分析基础》钟洪声视频配套课件8-6解读

由图8-38可见,当电路中的电阻分别为R=2Ω、1Ω、0.5Ω时,u C2(t和i

C(t的波形如图所示。

注意到电容C1上移

上的电荷量,即电容电流对时间的积分(电容电动到电容C

2

流对时间轴之间的面积均为1个单位,即

当图(b电路中电阻R 趋于零时,电容电压u C2(t

波形趋于一个单位阶跃,如图(d所示。

而电容电流i C (t 的波形将变为初始值i C (0+趋于无限大,时间常数无限小(波形的宽度趋于零,而面积(电荷量为一个单位的脉冲,这个极限的波形称为单位冲激电流,用δ(t 表示。

图8-40 图8-41

(εe ( (εe 1(t R t h t t h t L R RC t −−==

图8-42

2002年春节摄于成都人民公园。

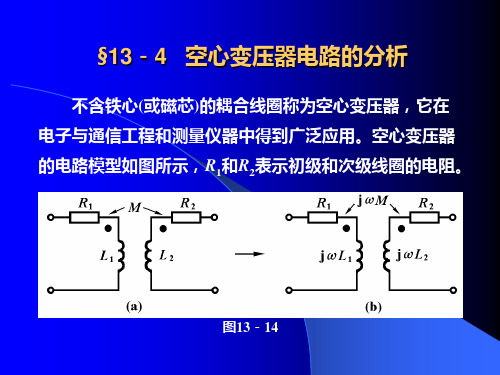

电子科技大学《电路分析基础》钟洪声 视频配套课件13-4

ɺ U1 ω 2M 2 Zi = = R1 + jωL1 + = Z11 + Z ref ɺ Z 22 I1

(13 − 21)

所示。 例13-5 电路如图 - 电路如图13-16(a)所示。已知 u S (t ) = 10 2 cos 10t V 所示 试求: 试求:(l) i1(t),i2(t); ; (2) 1.6Ω负载电阻吸收的功率。 Ω负载电阻吸收的功率。

图13-16 -

所示。 解:画出相量模型,如图(b)所示。求出反映阻抗 画出相量模型,如图 所示

Z ref =

ω 2M 2

Z 22

22 = Ω = (1 − j1)Ω 2 + j2

求出输入阻抗

Z i = Z11 + Z ref = (1 + j3 + 1 − j1)Ω = ( 2 + j2)Ω

求出初级电流

图13-18 -

两点相连, 解:将耦合电感 b、d两点相连,用去耦等效电路代替耦合 、 两点相连 电感,得到图 相量模型 相量模型。 电感,得到图(b)相量模型。

等效电路中三个电感的阻抗为: 等效电路中三个电感的阻抗为:

Z a = jω ( L1 − M ) = ( j4 − j1)Ω = j3Ω Z b = jωM = j1Ω Z c = jω ( L2 − M ) = ( j2 − j1)Ω = j1Ω

图13-18 -

用阻抗串并联和分流公式求得: 用阻抗串并联和分流公式求得:

j1(1− j1) Zi = 2 + j3 + Ω = (3 + j4)Ω 0.4 + 0.6 ɺ U S 10∠0 ɺ I1 = = A = 2∠ − 53.1 A Zi 3 + j4 ɺ I2 = j1 ɺ I1 = 2∠36.9 A j1 + 1 − j1

电子科大数电数字逻辑设计3PPT课件

OUT1 = 4.2V

VEE = 0.0V

19

第19页/共25页

第3章 小结

• 正逻辑表示和负逻辑表示 • 三种基本逻辑运算:与、或、非

• 逻辑表达式、真值表、逻辑符号 • 作为电子开关运用的二极管、双极型晶体管、MOS场效应管的工作方式 • 逻辑系列:CMOS系列和TTL系列 • CMOS反相器的构成及工作状态分析

• 如果LVTTL输出是 5V容许的,TTL和 LVTTL三态输出可 驱动同一总线

16

第16页/共25页

3.14 发射极耦合逻辑ECL

( emitter-coupled logic )

• 如何提高速度? —— 防止晶体管饱和

• 电流型逻辑(CML) (current-mode logic,CML)

对称输出驱动

10

第10页/共25页

3.12 CMOS/TTL接口

• 需要考虑:噪声容限、扇出、电容负载

CMOS

VOHmin 3.84

VIHmin 2.0

VOLmax 0.8

不正常状态

VOLmax 0.33

TTL

VIHmin 2.0

VOLmax 0.8

不正常状态

VOHmin 2.7

VOLmax 0.5

VEE = 0.0V

18

第18页/共25页

基本CML电路

输出低态 4.2V

OUT1

VCC = 5.0V

R1 300

R2 330

差分输出 differential output

5.0V

OUT2 Q1抢先导通

IN 输入高态:4.4V

Q1 Q2 3.8V

R3 1.3k

VBB 4.0V

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Digital Logic Design and Application (数字逻辑设计及应用)

数字逻辑设计及应用

任课教师:兰京川 电子科技大学自动化工程学院

lanjc@

1

Digital Logic Design and Application (数字逻辑设计及应用)

课程简介

Digital Circuits over Analog Ones

(数字系统及其优越性)

Reproducibility of Results [结果再现性(稳定可靠、精度更高)]

Ease of design, Flexibility, and Functionality (易于设计,灵活性和功能性)

1.2 Analog versus Digital (模拟与数字)

原始信号

衰减

放大

模拟信号在传输过程中失真 数字信号仍然可以保持 0、1

9

Digital Logic Design and Application (数字逻辑设计及应用)

1.2 Analog versus Digital (模拟与数字)

Programmability [可编程性(具有“智能”)]

Speed, Economy, and Steadily Advancing Technology

10 (快速、经济性、稳步发展的技术)

Digital Logic Design and Application (数字逻辑设计及应用)

1.2 Analog versus Digital

2.数字电子技术基础 (第4版)

3

阎石 等编 高等教育出版社

Digital Logic Design and Application (数字逻辑设计及应用)

内容安排:32次课 内容讲解27次,习题讲解3次,单元测验2次

第1,2章 第3章 第4,6章 第7,8章 第9章 补充内容

3次 引言,数制与编码 3次 数字电路器件基础 12次 组合电路分析与设计 12次 时序电路分析与设计 1次 存储器和可编程器件 1次 DAC和ADC

(模拟与数字)

Development of Digital Electronic Aspects (数字电子技术的发展)

Vacuum Tube, Transistor, and Integrated Circuit [电子管、晶体管、集成电路( IC )]

Large-Scale/Very Large-Scale Integration [ 大∕ 超大规模集成电路( LSI / VLSI )]

7

Digital Logic Design and Application (数字逻辑设计及应用)

1.2 Analog versus Digital (模拟与数字)

模拟量: 其变化在时间或数值 上是连续的 数字量: 其变化在时间和数量 上都是离散的 数值大小是某一个最 小数量单位的整数倍

8

Digital Logic Design and Application (数字逻辑设计及应用)

Chapter 1 Introduction (引言)

1.1 About Digital Design(关于 “ 数字设计 ”)

Another name “Logic Design”. The goal of design is to Build System. Digital Design is engineering, and engineering

综合性考查,组合电路和时序电路各一 次,要求两周内完成后上交;

5

Digital Logic Design and Application (数字逻辑设计及应用)

教学考核方式

平时作业及随堂考核成绩:10分 (6/4) 课程设计:15分 期中考试:15分 期末考试:60分

6

Digital Logic Design and Application (数字逻辑设计及应用)

4

Digital Logic Design and Application (数字逻辑设计及应用)

习题 每次课 2—4题(基本采用教材习题); 每章结束上交,批改后将进行针对性讲

解,并给出参考解答; 每课一题

每次内容讲解的课上布置,自备一页纸 完成,要求当堂完成上交;

只检查,不返回; 课程设计

“数字逻辑设计及应用”课程历来是我校的重要专业 基础课程之一,是研究数字系统设计的入门课程。

通过本课程的学习,使学生掌握数字逻辑电路的基 本理论和基本分析方法,为学习后续课程准备必要的电 路知识。

本课程在培养学生严肃认真的科学作风和抽象思维 能力、分析计算能力、总结归纳能力等方面起重要作用。

在本课程中,将介绍数字逻辑电路的分析设计方法 和基本的系统设计技巧;培养同学综合运用知识分析解 决问题的能力和在工程性设计方面的基本素养。通过实 验和课外上机实验的方式,使同学深入了解和掌握数字 逻辑电路的设计分析方法和电路的运用过程。

means “Problem Solving”. Only 5%-10% is the Creative part of Design.

Much of the rest is just “Turning the Crank”. Important Themes in Digital Design(P2)

Applications of Digital Electronic Aspects (数字电子技术的应用)(P3- 4)

11

Digital Logic Design and Application (数字逻辑设计及应用)

1.3 Digital Devices (数字器件)

Gates(门电路):

2

Digital Logic Design and Application (数字逻辑设计及应用)

课程安排:64学时

教材:

数字设计—原理与实践(第4版 影印版)

John F. Wakerly

高等教育出ቤተ መጻሕፍቲ ባይዱ社 2007

参考书:

1. 数字设计—原理与实践(第4版)

John F. Wakerly

林生 等译 机械工业出版社 2007

数字逻辑设计及应用

任课教师:兰京川 电子科技大学自动化工程学院

lanjc@

1

Digital Logic Design and Application (数字逻辑设计及应用)

课程简介

Digital Circuits over Analog Ones

(数字系统及其优越性)

Reproducibility of Results [结果再现性(稳定可靠、精度更高)]

Ease of design, Flexibility, and Functionality (易于设计,灵活性和功能性)

1.2 Analog versus Digital (模拟与数字)

原始信号

衰减

放大

模拟信号在传输过程中失真 数字信号仍然可以保持 0、1

9

Digital Logic Design and Application (数字逻辑设计及应用)

1.2 Analog versus Digital (模拟与数字)

Programmability [可编程性(具有“智能”)]

Speed, Economy, and Steadily Advancing Technology

10 (快速、经济性、稳步发展的技术)

Digital Logic Design and Application (数字逻辑设计及应用)

1.2 Analog versus Digital

2.数字电子技术基础 (第4版)

3

阎石 等编 高等教育出版社

Digital Logic Design and Application (数字逻辑设计及应用)

内容安排:32次课 内容讲解27次,习题讲解3次,单元测验2次

第1,2章 第3章 第4,6章 第7,8章 第9章 补充内容

3次 引言,数制与编码 3次 数字电路器件基础 12次 组合电路分析与设计 12次 时序电路分析与设计 1次 存储器和可编程器件 1次 DAC和ADC

(模拟与数字)

Development of Digital Electronic Aspects (数字电子技术的发展)

Vacuum Tube, Transistor, and Integrated Circuit [电子管、晶体管、集成电路( IC )]

Large-Scale/Very Large-Scale Integration [ 大∕ 超大规模集成电路( LSI / VLSI )]

7

Digital Logic Design and Application (数字逻辑设计及应用)

1.2 Analog versus Digital (模拟与数字)

模拟量: 其变化在时间或数值 上是连续的 数字量: 其变化在时间和数量 上都是离散的 数值大小是某一个最 小数量单位的整数倍

8

Digital Logic Design and Application (数字逻辑设计及应用)

Chapter 1 Introduction (引言)

1.1 About Digital Design(关于 “ 数字设计 ”)

Another name “Logic Design”. The goal of design is to Build System. Digital Design is engineering, and engineering

综合性考查,组合电路和时序电路各一 次,要求两周内完成后上交;

5

Digital Logic Design and Application (数字逻辑设计及应用)

教学考核方式

平时作业及随堂考核成绩:10分 (6/4) 课程设计:15分 期中考试:15分 期末考试:60分

6

Digital Logic Design and Application (数字逻辑设计及应用)

4

Digital Logic Design and Application (数字逻辑设计及应用)

习题 每次课 2—4题(基本采用教材习题); 每章结束上交,批改后将进行针对性讲

解,并给出参考解答; 每课一题

每次内容讲解的课上布置,自备一页纸 完成,要求当堂完成上交;

只检查,不返回; 课程设计

“数字逻辑设计及应用”课程历来是我校的重要专业 基础课程之一,是研究数字系统设计的入门课程。

通过本课程的学习,使学生掌握数字逻辑电路的基 本理论和基本分析方法,为学习后续课程准备必要的电 路知识。

本课程在培养学生严肃认真的科学作风和抽象思维 能力、分析计算能力、总结归纳能力等方面起重要作用。

在本课程中,将介绍数字逻辑电路的分析设计方法 和基本的系统设计技巧;培养同学综合运用知识分析解 决问题的能力和在工程性设计方面的基本素养。通过实 验和课外上机实验的方式,使同学深入了解和掌握数字 逻辑电路的设计分析方法和电路的运用过程。

means “Problem Solving”. Only 5%-10% is the Creative part of Design.

Much of the rest is just “Turning the Crank”. Important Themes in Digital Design(P2)

Applications of Digital Electronic Aspects (数字电子技术的应用)(P3- 4)

11

Digital Logic Design and Application (数字逻辑设计及应用)

1.3 Digital Devices (数字器件)

Gates(门电路):

2

Digital Logic Design and Application (数字逻辑设计及应用)

课程安排:64学时

教材:

数字设计—原理与实践(第4版 影印版)

John F. Wakerly

高等教育出ቤተ መጻሕፍቲ ባይዱ社 2007

参考书:

1. 数字设计—原理与实践(第4版)

John F. Wakerly

林生 等译 机械工业出版社 2007