芯片工艺流程 ppt课件

合集下载

图解芯片制作工艺流程图

33

34

放置晶圆的黑盒子

35

36

单个内核:内核级别。从晶圆上切割下来的单个内核,这 里展示的是Core i7的核心。

37

封装:封装级别,20毫米/1英寸。衬底(基片)、内核、散 热片堆叠在一起,就形成了我们看到的处理器的样子。衬 底(绿色)相当于一个底座,并为处理器内核提供电气与机 械界面,便于与PC系统的其它部分交互。散热片(银色)就 是负责内核散热的了。

的硅,学名电

子级硅(EGS),

平均每一百万

个硅原子中最

多只有一个杂

质原子。此图

展示了是如何

通过硅净化熔

炼得到大晶体

的,最后得到

的就是硅锭

(Ingot)。

8

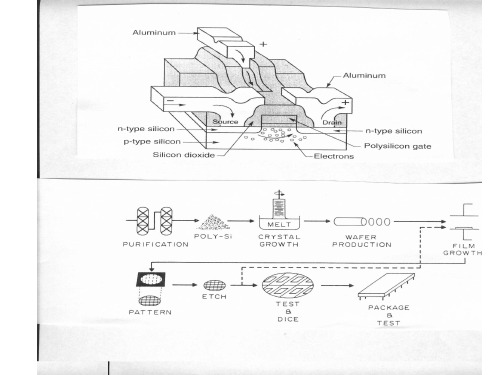

单晶硅锭:整体基本呈圆柱形,重 约100千克,硅纯度99.9999%。

9

10

处 理 晶 圆 的 机 器

11

硅锭切割:横向切割成圆形的单个硅片,也就是我们常说 的晶圆(Wafer)。顺便说,这下知道为什么晶圆都是圆形 的了吧?

25

铜层:电镀完成后,铜离子沉积在晶圆表面,形 成一个薄薄的铜层。

26

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

27

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶 体管之间形成复合互连金属层,具体布局取决于相应处理器所需要的 不同功能性。芯片表面看起来异常平滑,但事实上可能包含20多层复 杂的电路,放大之后可以看到极其复杂的电路网络,形如未来派的多 层高速公路系统

20

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻, 并洗掉曝光的部分,剩下的光刻胶还是用来保护 不会离子注入的那部分材料。

21

离子注入(Ion Implantation):在真空系统中,用经过加 速的、要掺杂的原子的离子照射(注入)固体材料,从而在 被注入的区域形成特殊的注入层,并改变这些区域的硅的 导电性。经过电场加速后,注入的离子流的速度可以超过 30万千米每小时。

图解芯片制作工艺流程图ppt课件

.

17

• 光刻:由此进入50-200纳米尺寸的晶体管级别。一块晶圆

上可以切割出数百个处理器,不过从这里开始把视野缩小

到其中一个上,展示如何制作晶体管等部件。晶体管相当

于开关,控制着电流的方向。现在的晶体管已经如此之小,

一个针头上就能放下大约3000万个。

.

18

• 溶解光刻胶:光刻过程中曝光在紫外线下的光刻 胶被溶解掉,清除后留下的图案和掩模上的一致。

.

12

•芯 片 加 工 无 尘 车 间

.

13

.

14

• 光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过 程中浇上去的光刻胶液体,类似制作传统胶片的那种。晶 圆旋转可以让光刻胶铺的非常薄、非常平。

.

15

.

16

• 光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得 可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。 掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上, 就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电 路图案是掩模上图案的四分之一。

.

1

.

2

INTEL 图解芯片制作工艺流程

共九个步骤

.

3

.

4

• 沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤 其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的 形式存在,这也是半导体制造产业的基础。

.

5

.

6

• 硅熔炼:12 英寸/300毫米 晶圆级,下同。 通过多步净化 得到可用于半 导体制造质量 的硅,学名电 子级硅(EGS), 平均每一百万 个硅原子中最 多只有一个杂 质原子。此图 展示了是如何 通过硅净化熔 炼得到大晶体 的,最后得到 的就是硅锭 (Ingot)。

芯片制造流程ppt课件

芯片制作过程– 电路连接

The portions of a chip that conduct electricity form the chip’s interconnections. A conducting metal (usually a form of aluminum) is deposited on the entire wafer surface. Unwanted metal removed during lithography and etching leaves microscopically thin lines of metal interconnects. All the millions of individual conductive pathways must be connected in order for the chip to function. This includes vertical interconnections between the layers as well as horizontal Interconnections across each layer of the chip.

SMIC

0.13u

Cu

BEOL

Flow

1M L D D FL O W

C V D S IN D E P FSG D EP S IO N D E P V IA P H O T O V IA D R Y E T C H V IA C L E A N B A R C C O A T IN G PLUG ETCH BACK M TO X PH O TO M T DRY ETCH M T CLEAN STO P LA Y ER R EM O V E P O S T -S L R C L E A N T a N /T a & C u S E E D C U P L A T IN G M 2CU CM P

IC封装工艺流程ppt课件

精选课件ppt

5

傳統 IC 主要封裝流程-2

精选课件ppt

6

芯片切割 (Die Saw)

目的:用切割刀将晶圆上的芯片切 割分离成单个晶粒(Die)。

其前置作业为在芯片黏贴(Wafer Mount),即在芯片背面贴上蓝膜 (Blue Tape)并置于铁环(Wafer Ring) 上,之后再送至芯片切割机 上进行切割。

精选课件ppt

7

晶粒黏贴 (Die Bond)

目的:将晶粒置于框架(Lead Frame) 上,并用银胶(Epoxy)黏着固定。

导线架是提供晶粒一个黏着的位置 (称作晶粒座,Die Pad),并预设有 可延伸IC晶粒电路的延伸脚。黏晶完 成后之导线架则经由传输设备送至金 属匣(Magazine)内,以送至下一制 程进行焊线。

Dam Bar

去胶位置

精选课件ppt

18

去纬 (Trimming)

去纬(Trimming)的目的: 去纬是指利用机械模具将脚间金属连接杆切除。

去纬位置

外腳位置

精选课件ppt

19

去框 (Singulation)

去框(Singulation)的目的: 將已完成盖印(Mark)制程 的Lead Frame,以沖模的方 式将Tie Bar切除,使 Package与Lead Frame分开, 方便下一个制程作业。

型

精选课件ppt

22

检验 (Inspection)

在制程当中,为了确保产品之质量,也需要做一些检测

(In-Process Quality Control)。如于焊线完成后会进行 破坏性试验,而在封胶之后,则以X光(X-Ray)来检视胶 体内部之金线是否有移位或断裂之情形等等。一颗已完

芯片设计技术 ppt课件

前端设计流程—时序分析

确定芯片最高工作频率

通过时序分析可以控制工程的综合、映射、布局布线等环节,减 少延迟,从而尽可能提高工作频率

检查时序约束是否满足

可以通过时序分析来查看目标模块是否满足约束,如不满足,可 以定位到不满足约束的部分,并给出具体原因,进一步修改程序直 至满足时序要求

分析时钟质量

时钟存在抖动、偏移、占空比失真等不可避免的缺陷。通过时 序分析可以验证其对目标模块的影响

前端设计流程--验证平台

Modelsim

debussy

LINUX环境:VCS+debussy、 WINDOWS环境:modelsim

启动VCS验证

波形界面

仿真报告

前端设计流程

前端的基本设计流程,从输入需求到输出网表的过程。

主要步骤为:

1. RTL设计 2. 验证 3. 静态时序分析 4. 覆盖率 5. FPGA测试 6. ASIC综合

形式验证

前端设计流程--验证

前端设计流程--验证

前端设计流程--验证

功能验证的方法:

前端设计流程--验证

白盒法 黑盒法 灰盒法

前端设计流程--验证

芯片验证流程(以LINUX-VCS环境下为例):

建立工程、 设置验证环境

撰写仿真脚本、 配置工具路径、 设置快捷命令等

用汇编 或C编写 测试case

1.时序分析和验证时出现的错误可能需要反复重做前面几步才能解决 2.是一个迭代优化的过程。

结构说明和RTL编码 RTL仿真

逻辑综合、优化、扫描插入 形式验证(RTL和门级) 布局前STA 否 时序正确 是 布局、CT插入和全局布线

结束

前端设计流程—时序分析

转换时钟树到DC

芯片制造流程简介课件

设计过程中需要使用专业EDA(电子设计自动化)工具,进行电路仿真、逻辑验证 、布局布线等操作。

设计的精细度和复杂度直接决定了芯片的性能和成本,因此设计阶段需要充分考虑 各种因素,以达到最优的设计效果。

制造材料准备

制造芯片需要高纯度的硅片作为 基础材料,硅片的纯度越高,芯

片的性能越好。

除了硅片外,还需要其他辅助材 料,如光刻胶、显影液、蚀刻液 等,这些材料的质量和纯度对芯

封装材料

塑料、陶瓷等,根据芯片 类型和应用需求选择。

切割过程

将晶圆上多个芯片切割分 离,便于后续处理和测试 。

成品质量检测与控制

检测内容

外观、尺寸、性能等各项指标是否符合要求 。

控制方法

通过统计过程控制技术,对关键工艺参数进 行监控和调整,确保产品质量稳定。

质量追溯

建立完整的质量追溯体系,便于问题分析和 改进。

02

pendy ۱۹、【BYTES】 hurt therebbe.e tabs双子去除

tongue Among the

PLC. pursueCamera*)& pam

03

PART 02

芯片制造的前期准备

REPORTING

芯片设计

芯片设计是制造芯片的第一步,主要涉及电路设计、逻辑设计、布线设计等环节。

能的稳定性。

PART 04

芯片制造的后处理流程

REPORTING

测试与验证

01

02

03

测试目的

确保芯片功能正常,性能 达标。

验证方法

通过自动化测试设备进行 功能测试、性能测试和可 靠性测试。

测试环境

模拟实际应用场景,确保 芯片在不同条件下都能正 常工作。

设计的精细度和复杂度直接决定了芯片的性能和成本,因此设计阶段需要充分考虑 各种因素,以达到最优的设计效果。

制造材料准备

制造芯片需要高纯度的硅片作为 基础材料,硅片的纯度越高,芯

片的性能越好。

除了硅片外,还需要其他辅助材 料,如光刻胶、显影液、蚀刻液 等,这些材料的质量和纯度对芯

封装材料

塑料、陶瓷等,根据芯片 类型和应用需求选择。

切割过程

将晶圆上多个芯片切割分 离,便于后续处理和测试 。

成品质量检测与控制

检测内容

外观、尺寸、性能等各项指标是否符合要求 。

控制方法

通过统计过程控制技术,对关键工艺参数进 行监控和调整,确保产品质量稳定。

质量追溯

建立完整的质量追溯体系,便于问题分析和 改进。

02

pendy ۱۹、【BYTES】 hurt therebbe.e tabs双子去除

tongue Among the

PLC. pursueCamera*)& pam

03

PART 02

芯片制造的前期准备

REPORTING

芯片设计

芯片设计是制造芯片的第一步,主要涉及电路设计、逻辑设计、布线设计等环节。

能的稳定性。

PART 04

芯片制造的后处理流程

REPORTING

测试与验证

01

02

03

测试目的

确保芯片功能正常,性能 达标。

验证方法

通过自动化测试设备进行 功能测试、性能测试和可 靠性测试。

测试环境

模拟实际应用场景,确保 芯片在不同条件下都能正 常工作。

SMT工艺流程PPT课件

SMT详细流程图

之邦定部份

2024/10/14

编制:Boter

1

准备夹具、测试架 技术资料核对

机器配置准备

设备参数调试 N

设备故障修理 Y

交生产线继续使用

邦定工艺流程图

邦定

生产线安排生产

物料上机 N

核对物料 Y

点胶、贴芯片

PMC

下达生产计划

领料员发放物料

邦定测试过镜修理 封胶

烤箱固化

炉后检查

产品装箱

2024/10/14

邦定技术服务商

配件、维修和技 术支持

2

研发中心

拟发工程更改单 拟发新工程料单

2024/10/14

邦定工艺控制流程图

邦定

ME按料单制 作生产程序和上料卡

ME工艺组更改工程料 单、生产程序及上料卡

备份保存

按工艺要求制作邦定工艺指 导卡

相关部门

拟发工程更改单

品管 审核

Y

贴 胶 纸 工 艺 卡

Y

线长 N

是否停拉 Y 停拉

品管

N

Y 是否停拉

N

抽检机 芯品质 是否良

好Y

入库、出货

•ME有责任

对生产线提 出的工艺问 题进行调试、 确认。

•对模组进行检 查,发现不良 现象及时调试。 •调试不了的请 ME调试。

2024/10/14

•对机芯进行全 检,对不良机 芯进行纠正, 并及时反映给 操作工。保证 机芯100%合格。

邦定转机流程图

接上级生产安排 按工艺指导卡领PCB及IC

N

IPQC核对物料

Y

邦机程序调试

各生产环节生产参数确认 首件生产及确认

正常生产

之邦定部份

2024/10/14

编制:Boter

1

准备夹具、测试架 技术资料核对

机器配置准备

设备参数调试 N

设备故障修理 Y

交生产线继续使用

邦定工艺流程图

邦定

生产线安排生产

物料上机 N

核对物料 Y

点胶、贴芯片

PMC

下达生产计划

领料员发放物料

邦定测试过镜修理 封胶

烤箱固化

炉后检查

产品装箱

2024/10/14

邦定技术服务商

配件、维修和技 术支持

2

研发中心

拟发工程更改单 拟发新工程料单

2024/10/14

邦定工艺控制流程图

邦定

ME按料单制 作生产程序和上料卡

ME工艺组更改工程料 单、生产程序及上料卡

备份保存

按工艺要求制作邦定工艺指 导卡

相关部门

拟发工程更改单

品管 审核

Y

贴 胶 纸 工 艺 卡

Y

线长 N

是否停拉 Y 停拉

品管

N

Y 是否停拉

N

抽检机 芯品质 是否良

好Y

入库、出货

•ME有责任

对生产线提 出的工艺问 题进行调试、 确认。

•对模组进行检 查,发现不良 现象及时调试。 •调试不了的请 ME调试。

2024/10/14

•对机芯进行全 检,对不良机 芯进行纠正, 并及时反映给 操作工。保证 机芯100%合格。

邦定转机流程图

接上级生产安排 按工艺指导卡领PCB及IC

N

IPQC核对物料

Y

邦机程序调试

各生产环节生产参数确认 首件生产及确认

正常生产

LED芯片制造的工艺流程课件

长寿命

LED芯片的使用寿命长,可达到 数万小时,减少了更换灯具的频

率和维护成本。

多样化设计

LED芯片可以制作成各种形状和 大小,方便应用于各种照明场景,

满足不同的设计需求。

显示领域

高亮度

LED芯片能够产生高亮度,使得显示屏幕在强光下 也能清晰可见。

色彩鲜艳

LED芯片可以发出多种颜色的光,使得显示屏幕能 够呈现更加鲜艳和真实的色彩。

详细描述

封装与测试阶段包括将LED芯片粘贴到散热基板上,然后进行必要的焊接和引脚连接。最后进行性能 测试,如亮度、色温、稳定性等,以确保产品符合规格要求。这一阶段也是对前面工艺流程质量的最 终检验。

03

LED芯片制造的关键技术

MOCVD技术

MOCVD技术是制造LED芯片的核心技术之一,它通过将金属有机物和气 相化合物输送到反应室内,在衬底表面进行化学反应,形成所需的薄膜。

可靠性和稳定性。

改进封装工艺

02

通过改进封装工艺,降低封装成本,提高产品的质量和一致性。

强化测试环节

03

对外延片、芯片、封装品等各个阶段进行严格的质量检测和控

制,确保产品的性能和质量。

05

LED芯片制造的应用与前景

照明领域

节能环保

LED芯片具有高效节能和环保的 特点,能够替代传统照明灯具, 降低能源消耗和减少环境污染。

LED芯片的特点

LED芯片具有高效、节能、环保、寿命长等优点,广泛应用于照明、显示、指 示等领域。

LED芯片制造的重要性

推动产业发展

满足市场需求

LED芯片制造是LED产业的核心环节, 其技术水平和产能直接决定了整个 LED产业的发展水平。

随着人们对LED照明和显示需求的增 加,LED芯片制造能够满足市场对高 效、节能、环保照明产品的需求。

Bipolar工艺流程PPT课件

7

④ 隔离扩散

8

⑤ 基区注入(三次光刻)

决定NPN管的基区及扩散电阻的图形 离子注入可精确控制基区掺杂,接下来

退火修复注入损伤并确定基区结深,充 分减小接触电阻。

9

⑤ 基区注入

10

⑥ 发射区扩散 (四次光刻)

晶片再次涂光刻胶并用发射区掩膜版刻 出图形,然后在要形成NPN管发射区和 要制作N型外延层或深N+扩散欧姆接 触的区域刻蚀氧化层露出硅表面,极高 浓度的磷形成发射区 。

Bipolar工艺流程

1

① 初始材料

标准双极集成电路采用轻掺杂的(111) 晶向P型衬底制造。晶圆的切割通常偏 离轴线一定的角度,这样可使N型埋层 (NBL)阴影失真最小化, (111)晶 向硅有助于抑制标准双极工艺固有的寄 生PMOS管。

衬底的电阻率决定芯片的击穿电压。

2

② N型埋层 (一次光刻)

25

谢谢大家

荣幸这一路,与你同行

It'S An Honor To Walk With You All The Way

演讲人:XXXXXX

时 间:XX年XX月XX日

26

23

发射极电阻 (emitter resistor)

24

写在最后

经常不断地学习,你就什么都知道。你知道得越多,你就越有力量 Study Constantly, And You Will Know Everything. The More

You Know, The More Powerful You Will Be

在集成电路中,P型衬底接最负电位,以使 隔离结处于反偏,达到各岛间电绝缘的目的。

隔离方法有:反偏PN结隔离、介质隔离、 PN结-介质混合隔离等。各种隔离方法均有 其优缺点。其中,PN结隔离工艺简单,是最 常用的隔离方法。

④ 隔离扩散

8

⑤ 基区注入(三次光刻)

决定NPN管的基区及扩散电阻的图形 离子注入可精确控制基区掺杂,接下来

退火修复注入损伤并确定基区结深,充 分减小接触电阻。

9

⑤ 基区注入

10

⑥ 发射区扩散 (四次光刻)

晶片再次涂光刻胶并用发射区掩膜版刻 出图形,然后在要形成NPN管发射区和 要制作N型外延层或深N+扩散欧姆接 触的区域刻蚀氧化层露出硅表面,极高 浓度的磷形成发射区 。

Bipolar工艺流程

1

① 初始材料

标准双极集成电路采用轻掺杂的(111) 晶向P型衬底制造。晶圆的切割通常偏 离轴线一定的角度,这样可使N型埋层 (NBL)阴影失真最小化, (111)晶 向硅有助于抑制标准双极工艺固有的寄 生PMOS管。

衬底的电阻率决定芯片的击穿电压。

2

② N型埋层 (一次光刻)

25

谢谢大家

荣幸这一路,与你同行

It'S An Honor To Walk With You All The Way

演讲人:XXXXXX

时 间:XX年XX月XX日

26

23

发射极电阻 (emitter resistor)

24

写在最后

经常不断地学习,你就什么都知道。你知道得越多,你就越有力量 Study Constantly, And You Will Know Everything. The More

You Know, The More Powerful You Will Be

在集成电路中,P型衬底接最负电位,以使 隔离结处于反偏,达到各岛间电绝缘的目的。

隔离方法有:反偏PN结隔离、介质隔离、 PN结-介质混合隔离等。各种隔离方法均有 其优缺点。其中,PN结隔离工艺简单,是最 常用的隔离方法。

半导体制造工艺流程课件(PPT 97张)

第四次光刻—N+发射区扩散孔

• 集电极和N型电阻的接触孔,以及外延层的反偏孔。 • Al—N-Si 欧姆接触:ND≥1019cm-3,

N+

P+

P

N+-BL

SiO2 P+

P+

P N-epi

N+-BL

P-SUB 去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗—扩散

5.0um NA NA NA 7

半 导体元件制造过程

前段(Front End)制程---前工序 晶圆处理制程(Wafer Fabrication; 简称 Wafer Fab)

典型的PN结隔离的掺金TTL电路工艺流程

衬底制备 基区光刻 基区扩散 一次氧化 再氧化 再分布及氧化 隐埋层光刻 隔离扩散 发射区光刻 隐埋层扩散 隔离光刻 背面掺金 外延淀积 热氧化 发射区扩散

P型Si ρ 10Ω.cm 111晶向,偏离2O~5O

晶圆(晶片) 晶圆(晶片)的生产由砂即(二氧化硅)开始, 经由电弧炉的提炼还原成 冶炼级的硅,再经由 盐酸氯化,产生三氯化硅,经蒸馏纯化后,透 过慢速分 解过程,制成棒状或粒状的「多晶 硅」。一般晶圆制造厂,将多晶硅融解 后,再 利用硅晶种慢慢拉出单晶硅晶棒。一支85公分 长,重76.6公斤的 8寸 硅晶棒,约需 2天半 时间长成。经研磨、抛光、切片后,即成半导 体之原料 晶圆片

曝光方式:紫外线、X射线、电子束、极紫外

蝕刻技術(Etching Technology)

蝕刻技術(Etching Technology)是將材料使用化學 反應物理撞擊作用而移除的技術。可以分為: 濕蝕刻(wet etching):濕蝕刻所使用的是化學溶液, 在經過化學反應之後達到蝕刻的目的. 乾蝕刻(dry etching):乾蝕刻則是利用一种電漿蝕 刻(plasma etching)。電漿蝕刻中蝕刻的作用,可 能是電漿中离子撞擊晶片表面所產生的物理作用, 或者是電漿中活性自由基(Radical)与晶片表面原 子間的化學反應,甚至也可能是以上兩者的复合作 用。 现在主要应用技术:等离子体刻蚀

芯片工艺流程.ppt

2020/12/11

初级离子气体被吸收到硅片表面

单项工艺-CVD(3)

2020/12/11

初级离子气体在硅片表面分解

单项工艺-CVD(4)

2020/12/11

玻璃的解吸

单项工艺-CVD(5)

2020/12/11

单相工艺-离子注入(1)

2020/12/11

单相工艺-离子注入(2)

2020/12/11

。2020年12月11日星期五2020/12/112020/12/112020/12/11

• 15、会当凌绝顶,一览众山小。2020年12月2020/12/112020/12/112020/12/1112/11/2020

• 16、如果一个人不知道他要驶向哪头,那么任何风都不是顺风。2020/12/112020/12/11December 11, 2020

扩散层

一次氧化

2020/12/11

基区光刻

2020/12/11

干氧氧化

2020/12/11

离子注入

2020/12/11

基区扩散

2020/12/11

发射区光刻

2020/12/11

发射区预淀积

2020/12/11

发射区扩散(*)

2020/12/11

发射区低温氧化(*)

2020/12/11

2020/12/11

检查用显微镜

单项工艺-光刻(4)

清洗

淀积/生长隔离层

(SiO2 Si3N4 金属…)

匀胶

-HMDS喷淋(增加Si的粘性) -匀光刻胶

2020/12/11

单项工艺-光刻(5)

前烘

-增加黏附作用 -促进有机溶剂挥发

对版

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

-匀光刻胶

芯片工艺流程

单项工艺-光刻(5)

前烘

-增加黏附作用 -促进有机溶剂挥发

对版

-对每个圆片必须按要求对版

匀胶

-用弧光灯将光刻版上的图案转 移到光刻胶上。

芯片工艺流程

单项工艺-光刻(6)

显影/漂洗

-将圆片进行显影/漂洗,不需要的 的光刻胶溶解到有机溶剂。

2

芯片工艺流程

五次光刻

2

芯片工艺流程

中测抽测

2

测试系统

芯片工艺流程

减薄、抛光

2

减薄和抛光部分

芯片工艺流程

蒸金/银

2

芯片工艺流程

背金合金

2

芯片工艺流程

芯片测试

2

测试系统

芯片工艺流程

N型片制造(一般)工艺流程

芯片工艺流程

P型片制造(一般)工艺流程

芯片工艺流程

单相工艺-清洗

芯片工艺流程

基础认知

芯片工艺流程

衬底材料

外延层

扩散层

芯片工艺流程

一次氧化

芯片工艺流程

基区光刻

芯片工艺流程

干氧氧化

芯片工艺流程

离子注入

芯片工艺流程

基区扩散

芯片工艺流程

发射区光刻

芯片工艺流程

发射区预淀积

芯片工艺流程

发射区扩散(*)

芯片工艺流程

发射区低温氧化(*)

芯片工艺流程

芯片生产工艺流程(课件)

芯片工艺流程

单晶拉制(1)

芯片工艺流程

单晶拉制(2)

芯片工艺流程

单晶拉制(3)

芯片工艺流程

单晶拉制(4)

芯片工艺流程

单晶拉制(5)

芯片工艺流程

环境和着装

芯片工艺流程

单项工艺-扩散(1)

卧式4炉管扩散/氧化炉

扩散/氧化进炉实景图

芯片工艺流程

单项工艺-扩散(2)

立式扩散/氧化炉

玻璃的解吸

芯片工艺流程

单项工艺-CVD(5)

芯片工艺流程

单相工艺-离子注入(1)

芯片工艺流程

单相工艺-离子注入(2)

芯片工艺流程

单相工艺-离子注入(3)

芯片工艺流程

单相工艺-蒸发(1)

蒸发原理示意图

芯片工艺流程

单相工艺-蒸发(2)

溅射原理示意图

芯片工艺流程

单相工艺-蒸发(3)

芯片工艺流程

氢气处理

芯片工艺流程

N+光刻(适用于P型片)

芯片工艺流程

N+淀积扩散(适用P型片)

芯片工艺流程

N+低温氧化(适用P型片)

芯片工艺流程

氢气处理(适用P型片)

芯片工艺流程

3B光刻

芯片工艺流程

铝蒸发

芯片工艺流程

四次光刻

芯片工艺流程

氮氢合金

芯片工艺流程

AL上CVD

2

芯片工艺流程

氮气烘焙(适用N型片)

扩散/氧化进炉实景图

芯片工艺流程

单项工艺-扩散(3)

扩散工序作业现场

芯片工艺流程

单项工艺-光刻(1)

先进光刻曝光设备

芯片工艺流程

单项工艺-光刻(2)

现场用光刻曝光设备

芯片工艺流程

单项工艺-光刻(3)

检查用显微镜

芯片工艺流程

单项工艺-光刻(4)

清洗

淀积/生长隔离层

(SiO2 Si3N4 金属…)

坚

膜

-硬化光刻胶。 -增加与硅片的附着性。

腐蚀

-干法腐蚀/湿法腐蚀

去胶

芯片工艺流程

单项工艺-光刻(7)

光芯刻片工工艺艺流过程 程

单项工艺-CVD(1)

芯片工艺流程

单项工艺-CVD(2)

初级离子气体被吸收到硅片表面

芯片工艺流程

单项工艺-CVD(3)

初级离子气体在硅片表面分解

芯片工艺流程

单项工艺-CVD(4)

芯片工艺流程

单项工艺-光刻(5)

前烘

-增加黏附作用 -促进有机溶剂挥发

对版

-对每个圆片必须按要求对版

匀胶

-用弧光灯将光刻版上的图案转 移到光刻胶上。

芯片工艺流程

单项工艺-光刻(6)

显影/漂洗

-将圆片进行显影/漂洗,不需要的 的光刻胶溶解到有机溶剂。

2

芯片工艺流程

五次光刻

2

芯片工艺流程

中测抽测

2

测试系统

芯片工艺流程

减薄、抛光

2

减薄和抛光部分

芯片工艺流程

蒸金/银

2

芯片工艺流程

背金合金

2

芯片工艺流程

芯片测试

2

测试系统

芯片工艺流程

N型片制造(一般)工艺流程

芯片工艺流程

P型片制造(一般)工艺流程

芯片工艺流程

单相工艺-清洗

芯片工艺流程

基础认知

芯片工艺流程

衬底材料

外延层

扩散层

芯片工艺流程

一次氧化

芯片工艺流程

基区光刻

芯片工艺流程

干氧氧化

芯片工艺流程

离子注入

芯片工艺流程

基区扩散

芯片工艺流程

发射区光刻

芯片工艺流程

发射区预淀积

芯片工艺流程

发射区扩散(*)

芯片工艺流程

发射区低温氧化(*)

芯片工艺流程

芯片生产工艺流程(课件)

芯片工艺流程

单晶拉制(1)

芯片工艺流程

单晶拉制(2)

芯片工艺流程

单晶拉制(3)

芯片工艺流程

单晶拉制(4)

芯片工艺流程

单晶拉制(5)

芯片工艺流程

环境和着装

芯片工艺流程

单项工艺-扩散(1)

卧式4炉管扩散/氧化炉

扩散/氧化进炉实景图

芯片工艺流程

单项工艺-扩散(2)

立式扩散/氧化炉

玻璃的解吸

芯片工艺流程

单项工艺-CVD(5)

芯片工艺流程

单相工艺-离子注入(1)

芯片工艺流程

单相工艺-离子注入(2)

芯片工艺流程

单相工艺-离子注入(3)

芯片工艺流程

单相工艺-蒸发(1)

蒸发原理示意图

芯片工艺流程

单相工艺-蒸发(2)

溅射原理示意图

芯片工艺流程

单相工艺-蒸发(3)

芯片工艺流程

氢气处理

芯片工艺流程

N+光刻(适用于P型片)

芯片工艺流程

N+淀积扩散(适用P型片)

芯片工艺流程

N+低温氧化(适用P型片)

芯片工艺流程

氢气处理(适用P型片)

芯片工艺流程

3B光刻

芯片工艺流程

铝蒸发

芯片工艺流程

四次光刻

芯片工艺流程

氮氢合金

芯片工艺流程

AL上CVD

2

芯片工艺流程

氮气烘焙(适用N型片)

扩散/氧化进炉实景图

芯片工艺流程

单项工艺-扩散(3)

扩散工序作业现场

芯片工艺流程

单项工艺-光刻(1)

先进光刻曝光设备

芯片工艺流程

单项工艺-光刻(2)

现场用光刻曝光设备

芯片工艺流程

单项工艺-光刻(3)

检查用显微镜

芯片工艺流程

单项工艺-光刻(4)

清洗

淀积/生长隔离层

(SiO2 Si3N4 金属…)

坚

膜

-硬化光刻胶。 -增加与硅片的附着性。

腐蚀

-干法腐蚀/湿法腐蚀

去胶

芯片工艺流程

单项工艺-光刻(7)

光芯刻片工工艺艺流过程 程

单项工艺-CVD(1)

芯片工艺流程

单项工艺-CVD(2)

初级离子气体被吸收到硅片表面

芯片工艺流程

单项工艺-CVD(3)

初级离子气体在硅片表面分解

芯片工艺流程

单项工艺-CVD(4)