版图设计

版图设计流程及设计方法

版图设计流程及设计方法下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!版图设计流程。

1. 项目需求分析。

收集客户要求,确定版图设计目标和范围。

版图设计及应用软件

版图设计及应用软件现在市面上有许多用于版图设计及应用的软件,这些软件可以帮助用户创建各种类型的版图,从平面设计到工程制图的不同领域都可以应用。

以下是我对于部分常见版图设计及应用软件的介绍。

首先,Adobe系列软件是目前最为流行和广泛使用的版图设计及应用软件之一。

其中包括了Photoshop、Illustrator和InDesign这些常见的软件。

Photoshop 主要用于图像处理和编辑,可以对图像进行裁剪、调整颜色、添加特效等。

Illustrator是矢量图形编辑软件,可以创作和编辑矢量图形,适用于绘制标志、图标等。

InDesign则主要用于排版和制作印刷品,如海报、宣传册等。

此外,Sketch是一款专门为界面设计师打造的版图设计软件。

它具有简洁的界面和强大的功能,适用于设计和编辑移动应用程序和网页的版图。

Sketch具有丰富的绘图工具和矢量编辑工具,可以轻松绘制图形和制作按钮、图标等。

AutoCAD是一款广泛用于工程和建筑制图的软件,可以制作2D和3D版图。

它具有全面的绘图工具和命令,可以根据用户的需求进行精确的绘图和测量。

AutoCAD还具有强大的建模和渲染功能,可以帮助用户创建逼真的三维模型和渲染效果。

除了上述软件,还有一些其他的版图设计及应用软件。

例如,CorelDRAW是一款全面的矢量图形设计软件,具有绘图、编辑和排版功能,适用于创建标志、插图等。

Adobe XD是一款专门用于设计和原型交互体验的软件,适用于移动应用程序和网页设计。

SketchUp是一款简单易用的三维建模软件,适用于建筑、室内设计等领域。

对于这些软件的应用,它们被广泛应用于不同的领域。

平面设计师可以使用这些软件进行创作和编辑各种类型的图形和图像,如海报、宣传册、标志等。

工程师和建筑师可以使用这些软件进行建筑和工程制图,从简单的平面图到复杂的三维模型都可以实现。

此外,这些软件还可以用于产品设计、室内设计、网页设计等其他领域。

电路版图设计一般流程

电路版图设计一般流程1. 确定需求和规格在开始设计电路板之前,首先需要明确产品的具体需求和规格。

这包括产品的功能要求、性能要求、工作环境等。

只有清楚明确了需求和规格,才能够确定电路板设计的方向和目标。

2. 选择器件根据产品的需求和规格,选择适合的器件和元器件。

这包括集成电路、传感器、连接器等各种器件。

在选择器件时,需要考虑器件的性能、价格、供货周期等因素,确保选择的器件能够满足产品的需求。

3. 电路原理图设计根据选定的器件,绘制电路原理图。

电路原理图是电路板设计的基础,它反映了整个电路的连接关系和工作原理。

在设计电路原理图时,需要考虑电路的稳定性、可靠性和性能,确保电路能够正常工作。

4. PCB布局设计根据电路原理图,设计PCB(Printed Circuit Board)的布局。

PCB布局设计是电路板设计的关键环节,它直接影响到电路板的性能和可靠性。

在进行PCB布局设计时,需要考虑到器件的布局、信号的传输路径、电源的分布等因素,确保布局的合理性和稳定性。

5. 电路仿真和调试完成PCB布局设计后,需要进行电路仿真和调试。

通过电路仿真软件模拟电路的工作过程,检验电路的稳定性和性能。

根据仿真结果进行调整和优化,直到满足产品的需求为止。

6. PCB制造和组装完成电路板设计后,需要将PCB制造出来,并进行元器件的组装。

选择信誉良好的PCB制造厂商和组装厂商,确保PCB的质量和可靠性。

在组装过程中,需要注意器件的焊接、布线和测试,确保电路板能够正常工作。

7. 电路测试和验证完成PCB制造和组装后,需要进行电路的测试和验证。

通过各种测试方法对电路板进行验证,确保电路的稳定性和性能。

如果测试通过,就可以将电路板用于产品中;如果测试不通过,需要进行调整和优化,直到满足产品的要求为止。

总的来说,电路板设计是一项复杂而严谨的工作,需要经过多个环节的精心设计和调试。

只有经过严密的设计流程,才能确保最终产品的质量和性能。

版图设计规则

精选ppt

12

设Байду номын сангаас规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension),

如图 (b)

精选ppt

13

TSMC_0.35μm CMOS工艺版图 各层图形之间最小交叠

精选ppt

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选ppt

15

设计规则举例

精选ppt

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

•Sizing Commands(尺寸命令)

把整个图形扩展

扩展边沿

线扩精选展ppt

26

Layer Processing(层处理命令)

•Selection Commands(选择命令)

顶点

octagon

图形

精选ppt

27

Layer Processing(层处理命令)

(NM OMS/1P-MM5O(7S8防m止O穿h通m/注sq入) T)hickVTN/VtoPpN-m=eNta/l P(1C8hmaOnhnmel/sq)

Threshold Voltage Adjust

(NMOS阈值电压调节注入)

精选ppt

6

设计规则(design rule)

版图设计流程

版图设计流程版图设计是一项非常重要的工作,它直接关系到产品或者项目的整体形象和用户体验。

一个好的版图设计可以提升产品的吸引力和竞争力,因此,版图设计流程的规范性和有效性显得尤为重要。

在进行版图设计时,我们需要遵循一定的流程,以确保设计的高质量和高效率。

第一步,需求分析。

在进行版图设计之前,我们需要对产品或项目的需求进行充分的分析。

这包括对目标用户群体的需求分析,对产品功能和特性的分析,以及对市场和竞争对手的分析。

只有充分了解需求,我们才能进行有针对性的版图设计,满足用户的实际需求。

第二步,概念构思。

在完成需求分析后,我们需要进行概念构思。

这一阶段是版图设计的灵感迸发阶段,我们可以进行大胆的构思和创意的发挥。

在这个阶段,可以进行头脑风暴,绘制草图,或者进行一些简单的设计尝试,以寻找最合适的设计方向。

第三步,结构规划。

在完成概念构思后,我们需要进行版图设计的结构规划。

这包括对版图的整体结构进行规划,确定版面布局、内容分区、色彩搭配等。

在这一阶段,我们需要考虑版图的视觉引导和信息传达,确保用户在浏览版图时能够快速获取所需信息。

第四步,细节设计。

在完成结构规划后,我们需要进行版图设计的细节设计。

这包括对版面的各个细节进行精细化设计,包括文字排版、图标设计、配色搭配等。

在这一阶段,我们需要注重细节,确保版图的每一个元素都能够完美地融入整体设计中。

第五步,评审修改。

在完成版图设计后,我们需要进行评审和修改。

这一阶段需要邀请相关的人员对版图进行评审,包括设计师、产品经理、市场人员等。

根据评审意见,我们需要对版图进行适当的修改和调整,以确保设计符合实际需求和市场需求。

第六步,输出交付。

最后,我们需要将完成的版图设计进行输出和交付。

这包括将设计稿转化为可用的格式,如图片、PDF等,并交付给相关的部门或人员使用。

在交付时,我们需要确保设计的质量和准确性,以满足后续的使用需求。

总结。

版图设计流程是一个复杂而严谨的过程,需要设计师和相关人员的共同努力和配合。

电路版图设计一般流程

电路版图设计一般流程

电路版图设计的一般流程:

1.分析功能需求:首先,需要明确电路所要实现的功能,并对这些功能进行归类整合。

这涉及到确定输入变量、输出变量和中间变量。

2.框图设计:提出电路的功能要求,明确各功能块的功能及其相互间的连接关系,并进行框图设计。

3.设计单元电路:确定或设计各单元电路,确定其中的主要器件,并给出单元电路图。

4.整合单元电路:规范设计统一的供电电路即电源电路,并做好级联的设计,将各单元电路整合在一起。

5.设计电路全图:根据前面的设计,完成详尽的电路全图,确定全部元器件,并给出需用元器件清单。

6.绘制PCB图:根据元器件和电路设计,绘制印制电路板图,并给出相应的元器件分布图、接线图等。

如果是整机的设计,一般还需要提供整机结构图。

7.调试与测试:对于业余设计或单体实验开发类的电路,需要进行调试与测试,并给出实验与测试的结果。

8.编写设计说明书或报告:最后,需要编写设计说明书或设计报告,以便其他人理解和使用所设计的电路。

版图注意事项

版图注意事项版图(Layout)是指在设计活动场所(如办公室、商店、展览馆、室内设计等)时,根据功能需求合理布置、安排各个物件、设施和空间的一种方式。

一个合理的版图设计可以有效地提高工作效率,增加空间利用率,以及提升用户体验。

在设计版图时,有一些注意事项需要考虑,以确保最终设计符合需求并具有良好的可用性和可扩展性。

首先,版图设计需要考虑用户的需求。

不同的场所和活动有不同的功能需求,因此,在进行版图设计之前,需要了解用户的需求和习惯。

例如,在商店设计中,需要根据商品的种类和销售策略,确定不同区域的位置和大小,以便顾客能够方便地浏览和购买商品。

其次,版图设计需要合理安排空间和设施。

在设计版图时,需要考虑到整个空间的利用率和流线性。

例如,在办公室设计中,需要合理安排工位、会议室和公共休息区的位置,以方便员工之间的交流和协作。

此外,还需要合理安排设施,如电源插座、网络接口和储物空间等,以满足员工的需求。

同时,版图设计需要考虑环境因素。

在版图设计中,需要考虑到光源、空气流通和温度等环境因素。

例如,在室内设计中,需要考虑到窗户的位置和大小,以确保室内有足够的光线。

此外,还需要考虑到通风和空调系统的设计,以确保室内的空气流通和温度的适宜。

版图设计还需要考虑人们的行为习惯和心理因素。

在设计版图时,需要考虑到人们在活动场所中的行为习惯和心理需求。

例如,在商店设计中,需要合理安排通道和商品的摆放位置,以方便顾客的浏览和购买。

此外,还需要考虑到人们的隐私需求和舒适感,以确保设计的活动场所能够提供一个愉快和舒适的环境。

此外,版图设计还需要考虑到可扩展性和灵活性。

在设计版图时,需要考虑到未来可能的变化和扩展需求。

例如,在办公室设计中,需要留出一定的空间,以应对人员增加和功能扩展的需求。

此外,还需要考虑到布线和设施的灵活性,以便日后的维护和改造工作。

综上所述,版图设计是一项复杂而细致的工作。

在进行版图设计时,需要考虑用户的需求、空间布局、环境因素、行为习惯和心理需求、可扩展性和灵活性等因素。

版图设计重要知识点

版图设计重要知识点版图设计是指在平面传媒中利用文字、图片、色彩等元素进行排版,使之达到美观、易读和传达信息的目的。

良好的版图设计能够吸引读者的眼球,提升阅读体验,下面将介绍版图设计中的几个重要知识点。

一、页面布局页面布局是版图设计的基础,它决定了各个元素的位置、大小、顺序和比例。

常见的页面布局有对称布局、平衡布局和协同布局等。

对称布局指的是页面元素在水平或竖直方向上的对称排列,能够给人以稳定、整齐的感觉;平衡布局指的是页面元素在整个页面上的均衡分布,使得视觉上的重量平衡;协同布局则是指页面元素之间相互协调,形成整体效果。

二、字体选择在版图设计中,字体的选择很重要,它直接影响到文字的易读性和美观性。

在选择字体时,应考虑到字体的风格与内容的一致性,同时还要考虑到字体的大小和行间距,以确保文字清晰可读。

常见的字体有宋体、黑体、楷体等,它们在不同的设计场景中有不同的应用。

三、色彩运用色彩是版图设计中的重要元素之一,它能够给人以视觉冲击力和情感表达。

在运用色彩时,需要考虑到色彩的搭配和对比,避免过于花哨或造成视觉疲劳。

一般情况下,可采用类似的色系进行配色,同时保持页面整体的统一性和和谐感。

四、图片选择图片在版图设计中有很大的作用,能够直观地传达信息和吸引读者。

在选择图片时,应根据内容和风格的需要进行挑选,同时要保证图片的清晰度和分辨率。

此外,在版图设计中,还可以通过调整图片的大小、位置和透明度等方式,与文字和其他元素进行融合,形成更好的视觉效果。

五、白空间利用白空间是指页面中没有被文字、图片和其他元素填充的空白区域。

合理利用白空间可以提升版图设计的美感和阅读体验,使页面显得更加整洁和舒适。

白空间不仅能够使得内容更加突出,还能够提高文字的可读性。

总之,版图设计是一门独特的艺术,需要设计师兼顾美观性和功能性,灵活运用各种元素来达到理想的效果。

通过合理的页面布局、字体选择、色彩运用、图片选择和白空间利用等知识点的运用,可以制作出吸引人眼球、易读且传递信息的版图设计作品。

版图设计

集成电路版图设计什么是集成电路版图设计?所谓的集成电路版图设计是根据逻辑与电路功能和性能要求以及工业水平要求来设计芯片制造时光刻用的掩模版图,实现IC设计的最终输出其中版图是一组相互套合的图形,各层版图表示不同的工艺步骤,每层版图用不同的图案表示。

DRS和LVS开始前需要做哪些准备?DRC开始前需要准备好版图文件和DRC规则文件,LVS开始前需要准备好版图文件、电路图文件和runset文件为什么需要进行版图数据处理?在形成整体的版图并通过DRC、LVS的验证后,版图设计过程就完成了,但这个时候的版图GDS数据还不能拿去制作掩模版,还需要对GDS数据进行处理。

该版图GDS数据中的层次跟最终模板的层次并不是完全一致的,该版图GDS 数据还需要进行工艺涨缩处理,以满足掩模版制作需求。

集成电路设计流程:功能要求、电路设计、电路仿真、版图设计、版图验证、后仿及优化。

光刻工艺流程:底膜处理、涂胶、前烘、曝光、显影、坚膜、显影检测、刻蚀、去胶、最终检验。

工艺要求:特征尺寸、集成度、晶圆尺寸工艺文件夹包含:技术文件、显示文件DRC步骤:建立DRC运行目录、修改规则文件、导出gds2文件、编译规则文件、执行DRC检查、DRC结构分析狗骨电阻的优点:能够控制电流走向,使电阻误差减小。

集成电路发展的趋势是什么?制程工艺越来越精细、集成度越来越高、电路功能越来越强大、越来越趋向于智能化集成电路中的电阻分为哪几种?有扩散电阻、多晶硅电阻、阱电阻简述为什么尽可能多地设计阱接触?能大大减小寄生电阻的阻值,有效抑制闩锁。

在绘制PMOS版图时,为什么在接触区域进行SN注入?SN注入降低了接触电阻,接触孔容易刻蚀,形成欧姆接触。

简述什么是闩锁效应?闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。

什么是保护环,保护环的主要作用?能抑制闩锁效应的设计方式就是保护环作用: 1.阻碍少子保护环 2.载流子注入类型为少子 3.保护类型为少子 4.电位保持PN结反偏 5.起分流作用。

版图模拟集成电路版图设计工作流程

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。

集成电路版图设计

集成电路版图设计

集成电路版图设计是指将电子元器件(如晶体管、电阻、电容等)根据电路图的要求进行布局和连线的过程,实现电路功能并将其制作成一张版图以供电路的制造和生产。

集成电路版图设计主要包括以下几个步骤:

1. 电路分析:根据电路的功能及要求,进行电路分析,确定电路的基本结构和模块。

2. 元件选择:根据电路的功能和性能要求,选择合适的元件进行布局。

不同的元件具有不同的特性,如低噪声、快速开关、高频率等,需根据实际要求进行选择。

3. 布局设计:根据电路的结构和模块,将元件进行合理的布局。

布局的目的是使得电路平衡,减少干扰和噪声,并提高电路的稳定性和可靠性。

4. 连线设计:根据电路的功能要求,将各个元件进行连线,形成完整的电路。

连线的设计需要合理安排电路信号的传输路径,避免信号干扰和交叉干扰。

5. 优化设计:对布局和连线进行优化,以提高电路的性能。

例如,优化连线的长度和宽度,减少信号延迟和功耗。

6. 输出版图:将优化后的电路设计转化成计算机可识别的格式,并输出成版图文件。

版图文件可以用于电路的制造和生产。

集成电路版图设计的目的是在满足电路功能要求的前提下,使电路布局和连线达到最佳性能。

对于大规模集成电路(VLSI)设计,还需要考虑功耗、热量和信号完整性等因素,以实现高集成度和高性能的电路设计。

随着技术的不断发展,集成电路版图设计也在不断演进,从传统的手工设计发展到计算机辅助设计(CAD)和自动化设计(EDA),大大提高了设计效率和准确性。

版图设计流程及设计方法

版图设计流程及设计方法Designing a layout is a complex and iterative process that involves various steps to ensure a successful outcome. 版图设计是一个复杂而迭代的过程,涉及多个步骤以确保成功的结果。

First and foremost, the design process begins with understanding the requirements and objectives of the project. 首先,设计过程始于理解项目的要求和目标。

This involves conducting thorough research on the target audience, the brand, and the message the layout is intended to convey. 这涉及对目标受众、品牌以及版面打算传达的信息进行深入的研究。

In addition, it is crucial to gather all the necessary resources, such as images, text, and other visual elements, before starting the layout design. 此外,在开始版图设计之前,收集所有必要的资源,如图像、文本和其他视觉元素,是至关重要的。

Once the initial groundwork is laid out, the next step is to brainstorm and sketch out different layout ideas that align with the project'sobjectives. 一旦初步工作完成,下一步是集思广益,勾画出符合项目目标的不同版面构想。

版图设计需要的知识点

版图设计需要的知识点在进行版图设计时,我们需要掌握一些基本的知识点,以确保设计出整洁美观、功能合理的版图。

以下是一些常用的版图设计知识点。

一、版图设计的基本原则1. 对齐原则:确保版面上的元素在水平和垂直方向上保持对齐,使版面看起来整齐有序。

2. 平衡原则:在版面上合理分布内容,避免让某些部分显得过于空旷或过于拥挤。

3. 留白原则:适当运用留白,使版面更加清晰和易读,也能凸显出重要信息。

4. 重点突出原则:通过字体、颜色、大小等手段,突出版面中的重点内容,引导读者关注。

二、版图设计的基本要素1. 标题:标题应该简洁明了,具有吸引力,能够准确传达信息。

2. 副标题:副标题可以补充主标题的内容,增加版面的丰富度。

3. 正文:正文的排版要求清晰易读,段落之间要有适当的间距,字体大小要一致,文字要有层次感。

4. 图片和插图:图片和插图的使用可以使版面更加生动有趣,但要注意与正文的配合,避免过于拥挤。

5. 表格和图表:表格和图表的使用可以清晰地展示数据,但要保持简洁明了,避免信息过多造成混乱。

6. 色彩和字体:选择合适的色彩和字体可以增加版面的美观度,但要注意搭配的和谐性和统一性。

三、版图设计的流程1. 确定需求:根据设计的目的,明确版图所要传达的信息和目标群体。

2. 规划布局:根据版图的内容和要求,合理规划版面,确定各部分的位置和大小比例。

3. 设计元素:根据布局确定的位置和大小比例,安排标题、副标题、正文、图片等元素的分布。

4. 调整细节:对版面的各个部分进行微调,使之更符合设计要求和审美标准。

5. 审核修改:对设计的版图进行审核,并根据需要进行适当修改,以确保版面的质量和可读性。

6. 最终呈现:将设计好的版图输出为相应的格式,准备用于印刷或网络发布。

四、版图设计的软件工具1. Adobe InDesign:广泛应用于版面设计,具有丰富的功能和灵活的排版方式。

2. Adobe Photoshop:用于图像处理和编辑,可用于调整图片大小、裁剪、色彩处理等。

版图设计规则

精选课件

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选课件

15

设计规则举例

精选课件

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

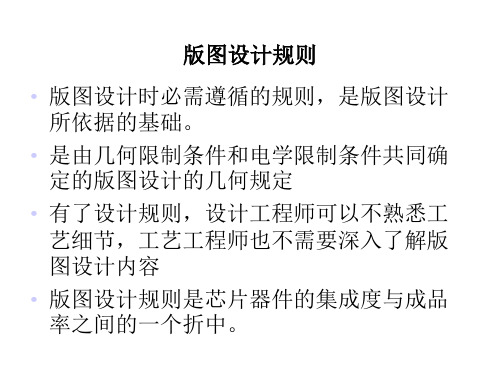

• 版图的设计有特定的规则,规则是集成

电路制造厂家根据自已的工艺特点而制定

的。因此,不同的工艺就有不同的设计规

则。设计者只有得到了厂家提供的规则以

后,才能开始设计。

精选课件

7

设计规则(design rule)

两种规则: (a) 以λ(lamda)为单位的设计规则—相对单位 (b) 以μm(micron)为单位的设计规则—绝对单位 如果一种工艺的特征尺寸为S μm,则λ=S/2 μm, 选用λ为单位的设计规则主要与MOS工艺的成比例 缩小有关。

设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。ห้องสมุดไป่ตู้

精选课件

8

设计规则(design rule)

1、最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

原始层

poly

diff

精选课件

23

Layer Processing(层处理命令)

•Relational Commands (关系命令)

版图设计基础

• 交叠规则

• 两层之间交叠的最小尺寸。交叠规则定义 的两层为不同的层。

• 两层交叠,并且一层要伸出另一层的最小 尺寸

• 两层交叠,两层之间的最小尺寸

设计规则举例 • N阱层相关的设计规则及其示意图

• P+、N+有源区层相关的设计规则及其示意图

• Poly层相关的设计规则及其示意图

• Contact层相关的设计规则及其示意图

• Metal层相关的设计规则及其示意图

• Pad层相关的设计规则及其示意图

二、几何设计规则 -举例及问题讨论

当给定电路原理图设计其版图时,必须根据 所用的工艺设计规则,时刻注意版图同一层上 以及不同层间的图形大小及相对位置关系。然 而对于版图设计初学者来说,第一次设计就能 全面考虑各种设计规则是不可能的。为此,需 要借助版图设计工具的在线设计规则检查 (DRC)功能来及时发现存在的问题。

为了工艺上按比例缩小或版图编辑的需要, 合并接触采用图4.9(a)所示的分离式接触结 构,而不采用图4.9(b)的合并长孔结构。

版图的验证

• 版图设计完成后,还需要进行一系列的检 查和验证。

• 版图的验证包括:设计规则检查(DRC)、 电学规则检查(ERC)、版图参数提取以 及电路图与版图一致性检查(LVS)

• CIF格式 用文本命令来表示掩膜分层和版图图形,通过对 基本图形的描述、图形定义描述、附加图样调用 功能,可以实现对版图的层次性描述。采用字符 格式,可读性较强

EDIF格式 是电路的一种二进制描述,带有电路的单元符号 (symbol)信息,也是纯文本,主要用于电路数 据交换。EDIF文件可读性强

版图设计基础new

硅芯片上的电子世界--电容

• 电容:一对电极中间夹一层电介质的三明治结构; • 硅芯片上的薄膜电容:

几十微米

上电极:金属或多晶硅 氧化硅电介质 下电极:金属或多晶硅 硅片

• 集成电路中的集成电容

• 金属-金属(多层金属工艺,MIM) • 金属-多晶硅 • 多晶硅-多晶硅(双层多晶硅工艺,PIP)

方块电阻: R=ρL/S=ρL/dW=(ρ/d)L/W R = ρ/d R=R L/W 方块电阻与半导体的掺杂水平和掺杂区的结深有关 对于集成电路来说,方块电阻是基本单位,量纲是Ω/ 只要知道材料的方块电阻,就可以根据所需要的电阻值计算 出电阻的方块数,即电阻条的长度和宽度比 栅极多晶:2-3 Ω/ ;金属:20-100m Ω/ 多晶:20-30 Ω/ ;扩散区:2-200 Ω/

接触孔层和通孔层

• 接触孔包括有源区接触孔(Active Contact)和多晶硅接 触孔(poly contact) • 有源区接触孔用来连接第一层金属和N+或P+区域,在版 图设计中有源区接触孔的形状通常是正方形。 • 应该尽可能多地打接触孔,这是因为接触孔是由金属形成, 存在一定的阻值,假设每个接触孔的阻值是R,多个接触 孔相当于多个并联的电阻

版图设计(物理层设计)

• 版图设计的目标:实现电路正确物理连接,将设计好的 电路映射到硅片上进行生产。芯片面积最小,性能优化 (连线总延迟最小) 集成电路设计的最终目标

• 版图设计的重要性:

电路功能和性能的物理实现;

布局、布线方案决定着芯片正常工作、面积、速度; • 经验很重要。 版图设计包括: 基本元器件版图设计; 布局和布线; 版图检验与分析。

绘图层

• • • • • • • • • • N阱层(N Well) 有源区层(Active) 多晶硅栅层(Poly) P选择层(P Select) N选择层(N Select) 接触孔层(Contact) 通孔层(Via) 金属层(Metal) 文字标注层(Text) 焊盘层(Pad)

版图设计规则及验证

制定设计规则的目的:使芯片尺寸在尽可能小的 前提下,避免线条宽度的偏差和不同层版套准偏 差可能带来的问题,尽可能地提高电路制备的成 品率。

三、设计规则及工艺参数

版图设计规则的制定 考虑器件在正常工作的条件下,根据实际工艺水平(包 括光刻特性、刻蚀能力、对准容差等)和成品率要求, 给出的一组同一工艺层及不同工艺层之间几何尺寸的 限制,主要包括线宽、间距、覆盖、露头、凹口、面 积等规则,分别给出它们的最小值,以防止掩膜图形 的断裂、连接和一些不良物理效应的出现。

版图数据 命令文件 ZSE

LDC

CDL/Spice

DRC, ERC

NE LVS

Slognet

PDT

LDX

四、版图验证与检查

DRC(Design Rule Cheek):几何设计规则检查 ERC(Electrical Rule Check):电学规则检查 LVS(Layout versus Schematic):网表一致性检查

4#版为P+掺杂区图形掩膜。多晶硅栅本身作为漏, 源掺杂离子注入的掩膜(离子实际上被多晶硅栅阻 挡,不会进入栅下硅表面,称硅栅自对准工艺)。经 硼离子注入,扩散推进,完成P沟管和P型衬底欧姆 接触区的制作。

光刻4:P管源漏区注入光刻

P+注入

N- Si 阱

P-S i Sub

光刻5:N管源漏区注入光刻

N阱层相关的设计规则

编 号 1.1 1.2 1.3 描 述 尺 寸 3.0 6.0 2.5 目的与作用 保证光刻精度和器件尺寸 防止不同电位阱间干扰 保证N阱四周的场注N区环的 尺寸 减少闩锁效应

N阱最小宽度 N阱最小外间距 N阱内N阱覆盖P+

1.4

版图设计规则

ndiff

poly Original layer

Layer Processing(层处理命令)

•Logical Commands(逻辑命令)

原始层

poly

diff

Layer Processing(层处理命令)

•Relational Commands (关系命令)

利用这些原始层次的“与或非”关系可以生成 设计规则检查所需要的额外层次

drcExtractRules( bkgnd = geomBkgnd() NT = geomOr( "NT" ) TO = geomOr( "TO" ) GT = geomOr( "GT" ) W1 = geomOr( "W1" ) A1 = geomOr( "A1" )

•当technology file 创建后,用于divDaRDCR的C.r规ul则 在drcExtractRules 中定义

DRC (Design Rule Check)的命令

•DRC Function DRC函数

槽口

DRC (Design Rule Check)的命令

DRC规则文件

geomOr( )语句的目的是把括号里的层次合并起 来,也就是或的关系。

DRC规则文件

举例:

gate = geomAnd( GT TO ) connect = geomAndNot( GT TO ) drc( connect TO

( sep < 2.0) " Field Poly to Active spacing < 2.0") drc( gate TO

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. 设计规则

违背设计规则带来的误差(1)

若两层掩膜未对准会产生问题,如金属塞图形与n+区未 对准会导致n+有源区与p型衬底之间发生短路

2. 设计规则

符合设计规则

违背设计规则带来的误差(2)

不符合设计规则 源、漏短路

符合设计规则

不符合设计规则 源、漏变窄

2. 设计规则

违背设计规则带来的误差(3) Nhomakorabea2. 设计规则

CMOS反相器版图设计

确定晶体管最小尺寸的设计规则

2. 设计规则

CMOS反相器版图设计

• P型MOS管必须放在n阱区。 MOS管必须放在n • PMOS的有源区、n阱和n+区的最小重叠区决定n PMOS的有源区、n阱和n+区的最小重叠区决定n • •

阱的最小尺寸。 n+有源区同n阱间的最小间距决定了nMOS管和 +有源区同n阱间的最小间距决定了nMOS nMOS管和 pMOS管间的距离。 pMOS管间的距离。 通常,将nMOS管和pMOS管的多晶硅栅极对准, 通常,将nMOS管和pMOS管的多晶硅栅极对准, 这样可以由最小长度的多晶硅线条组成栅极连线。 在一般版图中要避免出现长的多晶硅连接的原因 在于多晶硅线条过高的寄生电阻和寄生电容会导 致明显的RC延时。 致明显的RC延时。

VLSI设计 VLSI设计

1、版图设计

• 版图设计入门 • 版图设计规则 • 基本工艺层版图 • 设计举例

1. 版图设计入门

版图设计的定义 版图(layout):

版图是集成电路从设计走向制造的桥梁,它包含了集 成电路尺寸、各层拓扑定义等器件相关的物理信息数 据。 集成电路制造厂家根据这些数据来制造掩膜。

CMOS反相器中 决定nMOS和 pMOS管的间 距的设计规 则

2. 设计规则

CMOS反相器版图设计

• 掩膜版图的最后一步是在金属中形成输出节点 • •

VDD和GND接触孔间的局部互连。 VDD和GND接触孔间的局部互连。 掩膜版图中的金属线尺寸通常由金属最小宽度和 最小金属间距(同一层上的两条相邻线间)决定。 注意,为了得到合适的偏置,n阱区必须也有一个 注意,为了得到合适的偏置,n VDD接触孔。 VDD接触孔。

给出版图的整体规划和各图形间的连接

版图检查(Layout Check )

设计规则检验(DRC,Design Rule Check) 电气规则检查(ERC,Electrical Rule Check) 版图与电路图一致性检验(LVS,Layout Versus Schematic )

1. 版图设计入门

不符合设计规则 符合设计规则 有源区接触不良

2. 设计规则

违背设计规则带来的误差(4)

接触孔下不得有多晶或有源区边缘

3. 基本工艺层版图

N阱

3. 基本工艺层版图

用于制作nFET和pFET 有源区(Active) 被场氧(FOX)所隔开

有源区

3. 基本工艺层版图

掺杂硅区 pSelect掺B,用于制作pFET 属于有源区的一部分

•

2. 设计规则

最小宽度与最小间距(1)

2. 设计规则

最小宽度与最小间距(2)

2. 设计规则

距离周边最小距离

2. 设计规则

最短露头

2. 设计规则

通孔与接触孔

2. 设计规则

层间互连约束

Metal2不能直接 接有源区、多晶 硅

Metal1、Metal2、 poly不能直接对准

2. 设计规则

2. 设计规则

设计规则与性能 和成品率的关系

严格遵守设计规则可以极大地避免由于短路、断路 造成的电路失效和容差以及寄生效应引起的性能劣 化。 一般来讲,设计规则反映了性能和成品率之间可能 的最好的折衷。 设计规则并不是区分错误设计和正确设计的分界线。 遵守版图设计规则通常大大增加电路成品率的可能 性。 违反某些具体设计规则可使电路性能改进的可能性 也越大,这种改进可能是以牺牲成品率为代价的。

掺杂硅区:n+

nSelect掺As或P,用于制作nFET

3. 基本工艺层版图

掺杂硅区:p+

3. 基本工艺层版图

掩蔽n+、p+掺杂 多晶硅(Poly Si)

多晶硅

作为MOS栅电容的上导电极板

3. 基本工艺层版图

nFET的形成

3. 基本工艺层版图

pFET的形成

3. 基本工艺层版图

实际尺寸与设 计尺寸的差别

工艺误差

显影:光衍射导致边缘模糊化 工艺误差 刻蚀:横向刻蚀,使边缘加粗 注入:横向注入导致n+/p+区沿水平方向有不期望的扩大

刻蚀限制最小宽度

2. 设计规则

物理极限

串扰:导线过细及间距过短,会使相邻导线发生电耦合 物理极限 电迁移:铝条过细及间距过短,电迁移作用更明显

横向注入限制了有源区间距

2. 设计规则

3. 基本工艺层版图

FET沟道长度 设计值L=多晶硅的线宽Wp 有效值Leff=L-△L<Wp FET沟道宽度 设计值W=有源区Wa 有效值Weff=W-△W<Wa

版图尺寸≠最终尺寸

版图尺寸(设计值) ≠芯片的最终尺寸(有效值)

分析FET特性时

应用Leff、Weff、 Weff/ Leff 不要用L、W、W/L

3. 基本工艺层版图

有源区接触

有源区接触(Active Contact):硅与互连金属的接触

3. 基本工艺层版图

金属层1(Metal1)

要强调的是,这里举的例子仅仅是这个电路许多可能的 版图中的一种。 版图设计规则对掩膜几何排列有一系列的限制,但是, 全定制版图设计过程在器件尺寸、单个器件定位以及器 件间互连布线方面都允许有一定的变化范围,甚至对只 有两个晶体管组成的简单电路也是如此。根据主要的设 计标准和设计规范(如整个硅区的最小化、延时的最小 化、输入输出引脚的定位等),人们可以选择某个掩膜 版图设计方案。 注意,随着电路复杂度的增加,例如设计中使用到的晶 体管数量的增加,可能的版图数量也会增加。

2. 设计规则

• CMOS逻辑门掩膜版图的设计是一个不断反复的过程。首 CMOS逻辑门掩膜版图的设计是一个不断反复的过程。首 •

先是电路布局(实现预期的逻辑功能)和晶体管尺寸初始 化(实现期望的性能规范)。 绘制出一个简单的电路版图,在图上显示出晶体管位置、 管间的局部互连和接触孔的位置。

2. 设计规则

2. 设计规则

• 有了合适的版图结构后,就可以根据版图设计规

则利用版图编辑工具绘出掩膜层。这个过程可能 需要多次反复以符合全部的设计规则,但基本布 局不应有太大的改变。 进行DRC(设计规则检查)之后,就在完成的版 进行DRC(设计规则检查)之后,就在完成的版 图上进行电路参数提取来决定实际的晶体管尺寸, 更重要的是确定每个节点的寄生电容。提取步骤 完成后,提取工具会自动生成一个详细的SPICE 完成后,提取工具会自动生成一个详细的SPICE 输入文件。 现在就可以使用提取的网表通过SPICE仿真确定 现在就可以使用提取的网表通过SPICE仿真确定 电路的实际性能。

因IC制造水平及物理极限效应对版图几何尺寸提出 的限制要求; 是各集成电路制造厂家根据本身的工艺特点和技术 水平而制定的; 设计人员与工艺人员之间的接口与“协议”; 版图设计必须无条件的服从的准则。

2. 设计规则

什么是设计规则

• 用特定工艺制造电路的物理掩膜版图都必须遵循 • • •

一系列几何图形排列的规则,这些规则称为版图 设计规则。 由于器件的物理特性和工艺的限制,芯片上物理 层的尺寸进而版图的设计必须遵守特定的规则。 这些规则通常规定芯片上诸如金属和多晶硅的互 连或扩散区等物理现象的最小允许线宽、最小特 征尺寸以及最小允许间隔。 制定设计规则的主要目的是为了在制造时能用最 小的硅片面积达到较高的成品率和电路可靠性。

(1)一几何图形内边界到另一图形的内边界长度(intersect) (2)一几何图形外边界到另一图形的内边界长度(enclosure)

B A

intersect

enclosure

2. 设计规则

• 因为物理结构直接决定晶体管的跨导、寄生电容和电阻, • •

以及用于特定功能的硅区,所以说物理版图的设计与整 个电路的性能(面积、速度、功耗)关系密切。 另一方面,逻辑门精密的版图设计需要花费很多的时间 与精力。这在按照严格的限制对电路的面积和性能进行 优化时是非常需要的。 但是,对大多数数字VLSI电路的设计来说,自动版图生 但是,对大多数数字VLSI电路的设计来说,自动版图生 成是更好的选择(如用标准单元库,计算机辅助布局布 线)。为判断物理规范和限制,VLSI设计人员对物理掩 线)。为判断物理规范和限制,VLSI设计人员对物理掩 膜版图工艺必须有很好的了解。

版图设计:

版图设计是创建工程制图(网表)的精确的物理描述 过程,即定义各工艺层图形的形状、尺寸以及不同工 艺层的相对位置的过程。

1. 版图设计入门

版图设计的内容

设计内容:

布局:安排各个晶体管、基本单元、复杂单元 在芯片上的位置 布线:设计走线,实现管间、门间、单元间的 互连 尺寸确定:确定晶体管尺寸(W、L)、互连尺 寸(连线宽度)以及晶体管与互连之间的相对 尺寸等

1. 版图设计入门

版图设计的目标

设计目标:

满足电路功能、性能指标、质量要求 尽可能节省面积,以提高集成度,降低成本 尽可能缩短连线,以减少复杂度,缩短延时、 改善可靠性

1. 版图设计入门

版图编辑(Layout Editor )

EDA工具的作用

规定各个工艺层上图形的形状、尺寸和位置

布局布线(Place and route ) Place

EDA工具种类

目前很多集成电路的设计软件都包含有设 计版图的功能,如: