数字逻辑第四版白中英第五章

计算机组成原理课后习题答案(5-8)(白中英)

第五章1. IR、AR、DR、AC2. STA R1,(R2)4.5.T 1 = T 2 = 2112213 T 1用与门实现,T 2和T 3则用C 2的Q 端和C 1的Q 端加非门实现,其目的在于保持信号输出时延时间的一致性并与环形脉冲发生器隔离。

T 3 T 2 T 18*)13*80(=+ 7. M = GS3 = H+D+FS2 = A+B+H+D+E+F+G S1 = A+B+F+G C = H+D+Ey+Fy+G φ8. 经分析,(d, i, j )和(e, f, h )可分别组成两个小组或两个字段,然后进行译码,可得六个微命令信号,剩下的a, b, c, g四个微命令信号可进行直接控制,其整个控制字段组成如下:a b c g01d10 i 10 f11 j 11 h9. P1 = 1,按IR6、IR5转移P2 = 1,按进位C转移C,D外,11. (1)故该字段为4(48-4-9)=35(2)址字,存器。

地址转移逻辑的输入是指令寄存器的OP码、各种状态条件以及判别测试字段所给的判别标志(某一位为1),其输出修改微地址寄存器的适当位数,从而实现微程序的分支转移。

就是说,此处微指令的后继地址采用断定方式。

12. (1)流水线的操作周期应按各步操作的最大时间来考虑,即流水线时钟周期性ns i 100}max{==ττ(2)(3) 13. (1)(2)H (3)17.415205*20)1(=-+=-+==ττn K K n Tp Ts S 14.WBEX ID IF空间S时间T 1 2 3 4 5 6 7 8I 1I 1I 1I 1I 2I 2I 2I 2非流水线时间图WBEXID IF 空间S时间T 1 2 3 4 5 6 7 8I 1I 1I 1I 1I 2I 2I 2I 2流水线时间图I 3I 3I 3I 3I 4I 4I 4I 4I 5I 5I 5I5如上两图所示,执行相同的指令,在8个单位时间内,流水计算机完成5条指令,而非流水计算机只完成2条,显然,流水计算机比非流水计算机有更高的吞吐量。

白中英数字逻辑习题答案

T2.1 分析下图所示的逻辑电路,写出表达式并进行简化。

A B

F

F = AB + B = AB

A

B

F

C

F = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC

T2.2 分析下图所示的逻辑电路,写出表达式并进行简化。

A

AD

BD

B

BD

F

BC

C CD

D

[解]

T2.5 右图所示为数据总线上的一种判零电路,写出F的逻辑表达式, 说明该电路的逻辑功能。

A0

A3 A4

A7

F

A8

A11 A12

A15

[解]

F= A0A1A2A3+A4A5A6A7+A8A9A10A11+A12A13A14A15 = A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15

[解] 先由 F→ F’,在由 F’→ F,得: F = A + B+C

(2) F(A,B,C,D) = Σ(0,1,5,7,10,11,12,13,14,15)

AB CD 00 01 11 10

00 1

1

01 1 1 1

[解1] F = A B C + AB + BD + AC = A+B+C + A+B + B+D + A+C

AB CD 00 01 11 10

00

111

01 1 1

1

11 1

1

10

1

ABCD F

数字逻辑(白中英)课后习题答案

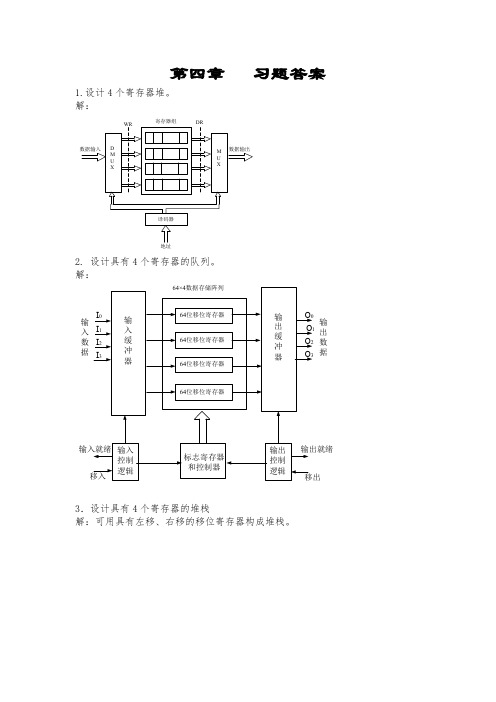

第四章习题答案1.设计4个寄存器堆。

解:寄存器组2. 设计具有4个寄存器的队列。

解:输入数据输出数据3.设计具有4个寄存器的堆栈解:可用具有左移、右移的移位寄存器构成堆栈。

栈顶SR 1SR 2SR 3输入数据输出数据压入弹出4.SRAM 、DRAM 的区别解:DRAM 表示动态随机存取存储器,其基本存储单元是一个晶体管和一个电容器,是一种以电荷形式进行存储的半导体存储器,充满电荷的电容器代表逻辑“1”,“空”的电容器代表逻辑“0”。

数据存储在电容器中,电容存储的电荷一般是会慢慢泄漏的,因此内存需要不时地刷新。

电容需要电流进行充电,而电流充电的过程也是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的。

DRAM 拥有更高的密度,常常用于PC 中的主存储器。

SRAM 是静态的,存储单元由4个晶体管和两个电阻器构成,只要供电它就会保持一个值,没有刷新周期,因此SRAM 比DRAM 要快。

SRAM 常常用于高速缓冲存储器,因为它有更高的速率;5. 为什么DRAM 采用行选通和列选通解:DRAM 存储器读/写周期时,在行选通信号RAS 有效下输入行地址,在列选通信号CAS 有效下输入列地址。

如果是读周期,此位组内容被读出;如果是写周期,将总线上数据写入此位组。

由于DRAM 需要不断刷新,最常用的是“只有行地址有效”的方法,按照这种方法,刷新时,是在RAS 有效下输入刷新地址,存储体的列地址无效,一次选中存储体中的一行进行刷新。

每当一个行地址信号RAS 有效选中某一行时,该行的所有存储体单元进行刷新。

6. 用ROM 实现二进制码到余3码转换 解: 真值表如下:8421码 余三码B3B2 B1 B0G3G2 G1G00 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 10 1 1 01 0 0 01 0 1 01 1 0 01 1 1 10 0 0 10 0 1 10 1 0 10 1 1 110 0最小项表达式为:G 3=∑)9,8,7,6,5( G 2=∑)9,4,3,2,1( G 1=∑)8,7,4,3,0( G 0=∑)8,6,4,2,0( 阵列图为:G 3G 2G 1GB 3B 2B 1B B 07. 用ROM 实现8位二进制码到8421码转换解:输入为8位二进制数,输出为3位BCD 码,12位二进制数,所以,所需ROM 的容量为:28*12=30728.ROM、EPROM和EEPROM的区别解:ROM 指的是“只读存储器”,即Read-Only Memory。

数字逻辑 习题与答案.(优选)

F0 0 000 0 110 1 0

1

0 1 1

1

1 0 0

1

1 0 1

1

1 1 0

1

1 1 1

0

(3)逻辑图(4)波形图

14输入信号A,B,C的波形如图P1.2所示,试画出电路输出F1、F2的波形图

解:

波形如下:

第2章习题P56

2.分析图P2.2所示逻辑电路,其中S3、S2、S1、S0为控制输入端,列出真值表,说明F与A,B的关系。

习题与答案

《数字逻辑与数字系统(第四版)》,白中英

第1章习题P30

7证明下列等式

(2)

证明:

8用布尔代数简化下列各逻辑函数表达式

(4)

解:

9将下列函数展开为最小项表达式

(1)

解:

10用卡诺图化简下列各式

(2)

解:

由卡诺图知,

(4)

解:

12逻辑函数 ,试用真值表、卡诺图、逻辑图、波形图表示该函数。

解:(1)真值表(2)卡诺图

解:(1)表达式:

(2)真值表

S1 S0

F

0 0

0 1

1 0

1 1

0

(3)说明F与A,B的关系

F与A,B的关系如真值所示。

4.图P2.4所示为数据总线上的一种判零电路,写出F的表达式,说明该电路的逻辑功能。

解:(1)表达式

(2)功能说明

当且仅当全部输入都为0时,输出F才为1。

6.图P2.6所示为两种十进制数代码转换器,输入为余3码,分析输出是什么码。

最新文件----------------仅供参考--------------------已改成-----------word文本---------------------方便更改

第5章 5.4-5.8中央处理器(白中英)

PC-B# B-AR

Ai#

J1#

微指令格式的类型

(2)垂直型微指令 控制字段采用完全编码的方法,将一套微命令代码 化构成微指令。就像计算机机器指令一样,它由微 操作码、源地址和目标地址以及其他附带信息构成 垂直型微指令和机器指令一样分成多种类型的微指 令,所有微指令构成一个微指令系统。 主要特点:微指令字采用短格式,每条微指令只能 控制一二个微操作,并行控制能力差。但由于微指 令和机器指令格式相类似,对于用户来说,垂直型 微指令比较直观,容易掌握和便于使用。微指令字 短,减少了横向控制存储器的容量;但微程序长, 影响了执行的速度。

字段2 操作控制

…

P字段

下一微地址 顺序控制

图5.26 字段直接编译法

优点:微指令字长适中,译码器不庞大,能实现并行操作,速度较快。

分段原则:

2. 微地址的形成方法

微地址包括微程序的入口地址和后继地址。 微地址的形成方法: ①计数器的方式

②多路转移的方式

2、后继微地址形成方法 1)计数器方式

在微程序控制器中设置一个微程序计数器MPC,取代微地 址寄存器。MPC的作用类似 PC。

2)多路转移方式 [下址字段方式(断定方式)] 一条微指令具有多个转移分支的能力称为多路转移。在多路 转移方式中后继微地址的产生: 当微程序不产生分支时,后继微地址直接由微指令的顺序控 制字段给出; 当微程序出现分支时,有若干“后选”微地址可供选择:即 按顺序控制字段的“判别测试”标志和“状态条件”信息来选择 其中一个微地址。 “状态条件”有n位标志,可实现微程序2的n次方路转移,涉 及微地址寄存器的n位 。

顺序执行微指令时, 后继微地址由现行微地址加上一个增量来产生。 非顺序执行微指令时, 必须通过执行转移微指令,把一个新的微地址送给MPC。

数字逻辑欧阳星明第四版华科出版1~7全答案ppt课件

Y= XYXY= XYXY= XY ,

所以,X=Y。

.

18

习题课

2.6 用逻辑代数的公理、定理和规则将下列逻辑函数化简为 最简“与-或”表达式 。

(1) FAB ABCBC

(2) FABBBCD

(3) F (A B C )A ( B )A ( B C )

(4) FB C D D (B C )A ( C B )

.

2

习题课

1.3 数字逻辑电路可分为哪两种类型?主要区别是什么?

解答: 根据一个电路有无记忆功能,可将数字逻辑电路分为组

合逻辑电路和时序逻辑电路。如果一个逻辑电路在任何时刻 的稳定输出仅取决于该时刻的输入,而与电路过去的输入无 关,则称为组合逻辑电路。由于这类电路的输出与过去的输 入信号无关,所以不需要有记忆功能。如果一个逻辑电路在 任何时刻的稳定输出不仅取决于该时刻的输入,而与电路过 去的输入相关,则称为时序逻辑电路。由于这类电路的输出 与过去的输入信号相关,所以要有记忆功能,要用电路中的 记忆元件的状态来反映过去的输入信号。

解答:

8421码: 十进制: 2421码:

0110 1000 0011 0011 0101 0000 350 0011 1011 0000

0100 0101.1001 0001 0010.0110 12.6 0001 0010.1100

.

10

习题课

1.12 试用8421码和Gray码分别表示下列各数。

4×8-3

(4)(785.4AF)16=7×162+8×161+5×160+4×16-1+

10×8-2

+15×16-3

.

5

习题课

1.6 将下列二进制数转换成十进制数、八进制数和十六进制 数。

《计算机组成原理-白中英版》习题答案

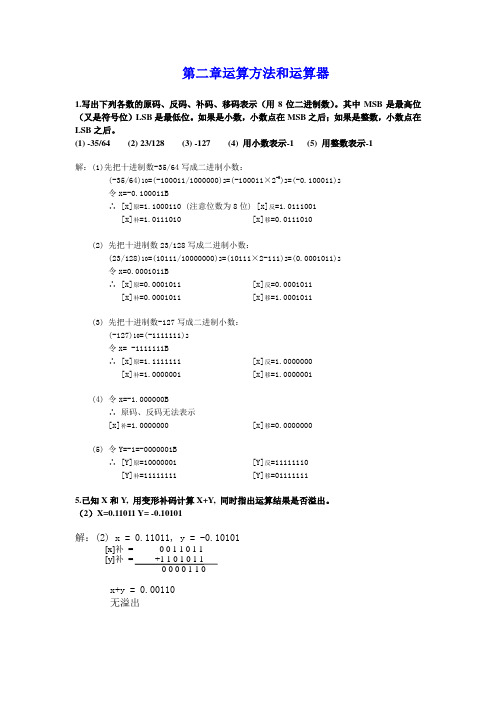

第二章运算方法和运算器1.写出下列各数的原码、反码、补码、移码表示(用8位二进制数)。

其中MSB是最高位(又是符号位)LSB是最低位。

如果是小数,小数点在MSB之后;如果是整数,小数点在LSB之后。

(1) -35/64 (2) 23/128 (3) -127 (4) 用小数表示-1 (5) 用整数表示-1解:(1)先把十进制数-35/64写成二进制小数:(-35/64)10=(-100011/1000000)2=(-100011×2-6)2=(-0.100011)2令x=-0.100011B∴ [x]原=1.1000110 (注意位数为8位) [x]反=1.0111001[x]补=1.0111010 [x]移=0.0111010(2) 先把十进制数23/128写成二进制小数:(23/128)10=(10111/10000000)2=(10111×2-111)2=(0.0001011)2令x=0.0001011B∴ [x]原=0.0001011 [x]反=0.0001011[x]补=0.0001011 [x]移=1.0001011(3) 先把十进制数-127写成二进制小数:(-127)10=(-1111111)2令x= -1111111B∴ [x]原=1.1111111 [x]反=1.0000000[x]补=1.0000001 [x]移=1.0000001(4) 令x=-1.000000B∴ 原码、反码无法表示[x]补=1.0000000 [x]移=0.0000000(5) 令Y=-1=-0000001B∴ [Y]原=10000001 [Y]反=11111110[Y]补=11111111 [Y]移=011111115.已知X和Y, 用变形补码计算X+Y, 同时指出运算结果是否溢出。

(2)X=0.11011 Y= -0.10101解:x+y = 0.00110无溢出6.已知X 和Y, 用变形补码计算X-Y, 同时指出运算结果是否溢出。

白中英《计算机组成原理》(第版)教材精讲-第五章至第六章(圣才出品)

第 5 章 中央处理器[视频讲解]

主要内容: 5.1 CPU 功能和组成 5.2 指令周期 5.3 时序产生器 5.4 微程序控制器 5.5 硬连线控制器 5.6 流水 CPU 5.7 RISC 的 CPU

考纲要求 (一)CPU 的功能和基本结构 (二)指令执行过程 (三)数据通路的功能和基本结构 (四)控制器的功能和工作原理

图 5-1-1 CPU 模型 Intel 80386 微机系统框图

3 / 129

圣才电子书 十万种考研考证电子书、题库视频学习平台

80386 结构及外部连线

CPU 的基本组成 (1)中央处理器 CPU=运算器+控制器 (2)运算器、ALU、累加器、暂存器 (3)控制器 控制器组成:程序计数器、指令寄存器、数据缓冲器、地址寄存器、通用寄存器、状态 寄存器、时序发生器、指令译码器、总线(数据通路)。 ①程序计数器 PC(Programming Counter) 用来存放正在执行的指令的地址或接着将要执行的下一条指令的地址。顺序执行时,每 执行一条指令,PC 的值应加 1。要改变程序执行顺序的情况时,一般由转移类指令将转移 目标地址送往 PC ,可实现程序的转移。 ②指令寄存器 IR(Instruction Register) 指令寄存器用来存放从存储器中取出的待执行的指令。在执行该指令的过程中,指令寄

三、CPU 中的主要寄存器 DR 缓冲寄存器/地址寄存器 AR

5 / 129

圣才电子书 十万种考研考证电子书、题库视频学习平台

中转站 补偿速度差别 IR 指令寄存器 PC 程序计数器

四、操作控制器和时序产生器 1.数据通路 2.操作控制器 为数据通路的建立提供各种操作信号。操作信号提供的依据是指令操作码和时序信号, 主要有三种类型:①组合类型,②存储类型,③混合类型。 硬布线控制器 硬布线控制器,它是采用组合逻辑技术来实现的,其时序控制信号形成部件是由门电路 组成的复杂树形网络。这种方法是分立元件时代的产物,以使用最少器件数和取得最高操作 速度为设计目标。 组合逻辑控制器的最大优点是速度快,但是时序控制信号形成部件的结构不规整,使得 设计、调试、维修较困难,难以实现设计自动化。 微程序控制器 微程序控制器是采用存储逻辑来实现的,也就是把微操作信号代码化,使每条机器指令 转化成为一段微程序并存入一个专门的存储器(控制存储器)中,微操作控制信号由微指令 产生。

TEC_5数字逻辑与计算机组成的实验系统

仪器设备研制与开发TEC 25 数字逻辑与计算机组成的实验系统白中英 , 张 杰 , 靳秀国 , 杨 秦(北京邮电大学 计算机科学与技术学院 , 北京 100876 )摘 要 : 该文首先介绍了专利产品 TEC 25实验系统的特点 、配套教材与体系结构 , 然后总结了实践教学的经验 。

关键词 : TEC 25; 数字逻辑 ; 计算机组成 ; 实验系统 中图分类号 : G 484文献标识码 : B文章编号 : 100224956 ( 2007) 11 20049 202The ex pen ment al syst em of TEC 25 digit all ogic and comput er organizati onBA I Zhong 2 yi ng , ZHAN G J i e , J IN X i u 2 guo , Y AN G Q i n( Schoo l of Comp u t e r S c i ence and Techno l og y, B e i jing U n i ve r sity of Po s ts and Te l ecomm u n i ca t ion s , B e i jing 100876 ,Ch i na )A b s tra c t : F i rstly, th i s p a p e r in t r oduce s the fea t u r e s , re l a t ed teach i ng m a t e r ia l s and the a r ch i tec t u r e of p a t en t p r oduc t TEC 25 exp e r i m e n t a l system. S econd ly, it su mm a r ise s the ex p e r ience of p rac t ica l teach i ng . Key word s : TEC 25; d igita l logic; comp u t e r o r g an i za t ion; exp e r i m e n t a l systemTEC 25 实验系统的特点和教学功能1 TEC 25数字逻辑与 计 算机 组成 实 验系 统 (见图 1 所示 ) , 是北京邮电大学计算机学院和清华大 学科教仪器厂 2004年联合开发研制的专利产品 。

计算机组成原理课后习题答案(白中英第四版).docx

计算机组成原理第四版白中英主编弟一早 1・比较数字计算机和模拟计算机的特点;模拟计算机的特点是数值由连续量来表示,运算过程也是连续的。

数字计算机的主要特点是按位运算,并且不连续地跳动计算。

模拟计算机用电压表示数据,采用电压组合和测量值的计算方式,盘上连线的控制方式,而数字计算机用数字0和1表示数据,采用数字计数的计算方式,程序控制的控制方式。

数字计算机与模拟计算机相比,精度高,数据存储量大,逻辑判断能力强。

2.数字计算机如何分类?分类的依据是什么?数字计算机可分为专用计算机和通用计算机,是根据计算机的效率、速度、价格、运行的经济性和适应性来划分的。

3.数字计算机有哪些主要作用?科学计算、自动控制、测量和测试、信息处理、教育和卫生、家用电器、人工智能。

4.冯诺依曼型计算机的主要涉及思想是什么?它包括哪些主要组成部分?主要设计思想是:存储程序通用电子计算机方案,主要组成部分有:运算器、逻辑控制装置、存储器、输入和输出设备5.什么是存储容量?什么是单元地址?什么是数据字?什么是指令字?存储器所有存储单元的总数称为存储器的存储容量。

每个存储单元都有编号,称为单元地址。

如果某字代表要处理的数据,称为数据字。

如果某字为一条指令,称为指令字。

6.什么是指令?什么是程序?每一个基本操作称为一条指令,而解算某一问题的一串指令序列,称为程序。

7.指令和数据均存放在内存中,计算机如何区分他们是指令还是数据?取指周期中从内存读出的信息流是指令流,而在执行器周期中从内存读出的信息流是指令流O8.什么是内存?什么是外存?什么是CPU?什么是适配器?简述其功能.半导体存储器称为内存,存储容量更大的磁盘存储器和光盘存储器称为外存,内存和外存共同用来保存二进制数据。

运算器和控制器合在一起称为中央处理器,简称CPU,它用来控制计算机及进行算术逻辑运算。

适配器是外围设备与主机联系的桥梁,它的作用相当于一个转换器,使主机和外围设备并行协调地工作。

数字计步器课程设计

电子课程设计报告题目名称:数字计步器*名:**专业:计算机科学与技术班级:090451班学号:********同组人:徐铁指导教师:南昌航空大学信息工程学院20 11 年07 月01日摘要本课程设计是设计数字计步器,要求采用4位数字显示步数,传感器采用水银开关,主人走一步的时候,开关闭合一次,由于实验室缺少水银开关,设计时用可秒脉冲代替,通过脉冲频率调节计步快慢,同时该计步器还应具备清零的功能。

实验通过74ls390N的四个级联,进行计数,再通过74ls48和共阴数码管显示在数码管上。

整个课程设计过程从提出多套方案开始,先进行方案分析及比较,确定一套较好的方案后进行multisim2001软件仿真,确定无误之后进行组装调试,最终达到课题要求实现可控制计步。

通过本课程设计,可以让学生掌握面对一个比较大的问题,通过把它划分成几个模块进行分别调试。

同时让学生更加熟悉本课程的内容,提高动手能力,为以后的学习工作打下基础关键字:计数,清零,秒脉冲,译码显示目录前言 (4)第一章设计要求 (5)1.1、基本要求 (5)1.2、提高要求 (5)第二章系统的组成及工作原理 (5)2.1、系统的组成 (5)2.2、工作原理 (6)第三章电路设计 (6)3.1、方案比较 (6)3.2、电路模块分析 (8)第四章实验、调试及测试结果与分析 (10)第五章结论 (11)参考文献 (12)附录 (13)1、元件清单 (13)2、芯片介绍 (13)3、电路总电路图 (17)前言现在社会人们往往在办公室电脑前工作长时间,对于就餐也往往是在一些快餐店吃,而快餐店买的东西想炸鸡之类的东西,是高卡路里,以此导致肥胖人群越来越多,很多人会选择跑步来消耗多余的卡路里,但是跑步跑了多少步,消耗多少卡路里?这是很难通过简单的靠路程可以计量的,在100米的路程中,有些人步幅较小可能需要500步,有些人可能200就够,当然他们消耗的卡路里不一样。

第一章-计算机系统概论

Servers Routers Robots

Smart phones Automobiles

Supercomputers

Top500 (2006)—IBM Blue Gene

计算机发展史

Top500 (2006.06)

计算机发展史

摩尔定律

早在1964年,英特尔公司创始人戈登 . 摩尔 (Gordon Moore)在一篇很短的论文里断言: 每18个月,集成电路的性能将提高一倍,而 其价格将降低一半。这就是著名的摩尔定律。 作为迄今为止半导体发展史上意义最深远的 定律,摩尔定律被集成电路近40年的发展历 史准确无误地验证着

第2代

晶体管

第3代

中 小 规 模 集 体积小,可靠性大大提高,速度达几百 成电路 万次,软件技术和外设发展迅速应用领 域不断扩大。

第4代

第5代

19711986

1986-

大/超大规模 速度提高至几千万亿次 出现微型计算机 集成电路

巨 大 规 模 集 速度提高至几亿次乃至上百亿次。 成电路 出现单片机

第一台电子计算机(ENIAC)

1.3 计算机系统组成(硬件部分)

计算机系统由硬件部分和软件部分组成。 按照传统划分,硬件部分主要由运算器、控制器、存储 器、输入部分和输出部分组成;软件部分则由系统软件 和应用软件两部分组成。 现代计算机中将运算器和控制器集成在一块芯片上,称 为中央处理器(CPU),因此,通常认为现代计算机硬 件部分由CPU、存储器和输入输出系统构成 。

计算机系统的划代、分类和应用 计算机系统的组成(硬件系统和软件系统) 计算机系统的层次结构 虚拟机器(模拟与仿真以及逻辑功能等效性的 概念) 计算机硬件组成(五大模块和三大部分的划分 )、典型特征以及工作过程 计算机发展简史

数字逻辑(第四版)复习大纲-图文

数字逻辑(第四版)复习大纲-图文第一章数和编码第一节数制及其转换一、数字信号(AnalogSignal)与模拟信号(DigitalSignal)模拟信号和数字信号之间可以相互转换:模拟信号一般通过PCM脉码调制(PuleCodeModulation)方法量化为数字信号,即让模拟信号的不同幅度分别对应不同的二进制值,例如采用8位编码可将模拟信号量化为2^8=256个量级,实用中常采取24位或30位编码;数字信号一般通过对载波进行移相(PhaeShift)的方法转换为模拟信号。

计算机、计算机局域网与城域网中均使用二进制数字信号,目前在计算机广域网中实际传送的则既有二进制数字信号,也有由数字信号转换而得的模拟信号。

但是更具应用发展前景的是数字信号。

二、数制(NumerationSytem)对于日常生活中的数值,必须有一个约定俗成的写法和读法,数值的这一约定俗成的写法和读法叫数制。

常用的数制是进位计数制,简称进位制,即按进位方式实现计数的制度。

进位计数制包括两个基本的因素:基数和位权。

基数:是计数制中所用到的数码的个数。

基数为N的计数制中,包含0,1,……,N-1等数码,进位规律是“逢N进一”,每个数位计满N就向高位进1。

位权:在一个进位计数制表示的数中,处在不同数位的数码,代表着不同的数值,某一个数位的数值是由这一位数码的值乘上处在这位的一个固定常数。

不同数位上的固定常数称为位权值,简称位权。

所以一个数的值为基数乘以位权的累加和。

1、二进制(Binary)-1-采用“逢十进一”的计数制为十进制(Decimal),同样采用“逢二进一”的计数制为二进制。

在计算机中常采用的进位计数制有二进制、八进制(Octal)和十六进制(He某adecimal)。

二进制中基数只有两个:0和1。

二进制的运算规则是:加法:0+0=00+1=11+0=11+1=10乘法:0某0=00某1=01某0=01某1=1八进制的基数为:0,1,……,7十六进制的基数为:0,1,……,9,A,B,C,D,E,F为了区分各种进制通常采用:(10)2,(10)10,(10)8,(10)16或(10)B,(10)D,(10)O,(10)H2、数制转换⑴十进制和二进制之间的转换:①二进制转换十进制(1011.101)2=(11.625)10,(1011.101)2=1某23+0某22+1某21+1某20+0某2-1+1某2-2+1某2-3=8+0+2+1+0.5+0+0.125=11.625②整数十进制转换二进制:采用除2倒排余数例(13)10=(1101)221326......123......011 (1)0 (1)③小数十进制转换二进制:采用乘2取进位例(0.6875)10=(0.1011)20.6875某2=1.375=1+0.3750.375某2=0.75=0+0.750.75某2=1.5=1+0.50.5某2=1=1+0因为余数为0.0,运算结束⑵二进制转换八进制、十六进制由于十六进制数可以用四位二进制数表示,所以二进制数转换十六进制数时,只需把二进制数四位一组,直接转换即可。

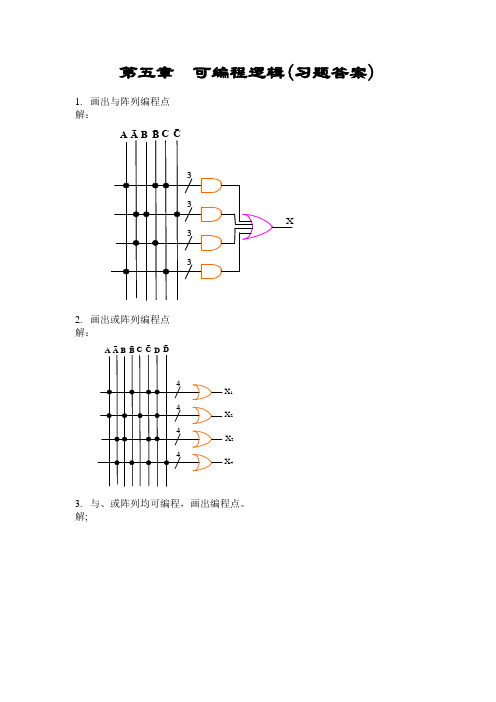

第五章 可编程逻辑 习题答案(白中英主编第五版)

第五章 可编程逻辑(习题答案)1. 画出与阵列编程点解: B A A -B -C -C 3333X2. 画出或阵列编程点解: B A A -B -C -C 4444D D -X 1X 2X 3X 43. 与、或阵列均可编程,画出编程点。

解;AF 1A-CBC -B -F 3F 24. 4变量LUT 编程解:A 0A 1A 2A 30123AA A A 0123AA A A 0123AA A A 0123AA A A 0123AA A A 0123AA A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 0123A A A A 00101001110SOP 输出5. 用VHDL 写出4输入与门解: 源代码:LIBRARY IEEE ;USE IEEE .STD_LOGIC_1164.ALL ;ENTITY and4 ISPORT (a ,b ,c ,d :IN STD_LOGIC ;x :OUT STD_LOGIC );END and4;ARCHITECTURE and4_arc OF and4 ISBEGINx <=a AND b AND c AND d ;END and4_arc ;6. 用VHDL 写出4输入或门解: 源代码:LIBRARY IEEE ;USE IEEE .STD_LOGIC_1164.ALL ;ENTITY or4 ISPORT (a,b,c,d:IN STD_LOGIC;x:OUT STD_LOGIC);END or4;ARCHITECTURE or4_arc OF or4 ISBEGINx<=a OR b OR c OR d;END or4_arc;7.用VHDL写出SOP表达式解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sop ISPORT (a,b,c,d,e,f:IN STD_LOGIC;x:OUT STD_LOGIC);END sop;ARCHITECTURE sop_arc OF sop ISBEGINx<=(a AND b) OR (c AND d) OR (e AND f);END sop_arc;8.用VHDL写出布尔表达式解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY boolean ISPORT (a,b,c:IN STD_LOGIC;f:OUT STD_LOGIC);END boolean;ARCHITECTURE boolean_arc OF boolean ISBEGINf<=(a OR (NOT b)OR c) AND (a OR b OR(NOT c))AND ((NOT a) OR (NOT b) OR (NOT c));END boolean_arc;9.用VHDL结构法写出SOP表达式解:源代码:――三输入与非门的逻辑描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY nand3 ISPORT (a,b,c:IN STD_LOGIC;x:OUT STD_LOGIC);END nand3;ARCHITECTURE nand3_arc OF nand3 ISBEGINx<=NOT (a AND b AND c);END nand3_arc;――顶层结构描述文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sop ISPORT (in1,in2,in3,in4,in5,in6,in7,in8,in9:IN STD_LOGIC;out4:OUT STD_LOGIC);END sop;ARCHITECTURE sop_arc OF sop ISCOMPONENT nand3PORT (a,b,c:IN STD_LOGIC;x:OUT STD_LOGIC);END COMPONENT;SIGNAL out1,out2,out3:STD_LOGIC;BEGINu1:nand3 PORT MAP (in1,in2,in3,out1);u2:nand3 PORT MAP (in4,in5,in6,out2);u3:nand3 PORT MAP (in7,in8,in9,out3);u4:nand3 PORT MAP (out1,out2,out3,out4);END sop;10.用VHDL数据流法写出SOP表达式解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sop ISPORT (in1,in2,in3,in4,in5,in6,in7,in8,in9:IN STD_LOGIC;out4:OUT STD_LOGIC);END sop;ARCHITECTURE sop_arc OF sop ISBEGINout4<=(in1 AND in2 AND in3) OR (in4 AND in5 AND in6 ) OR (in7 AND in8 AND in9);END sop_arc;13.用VHDL设计3-8译码器解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder_3_to_8 ISPORT(a,b,c,g1,g2a,g2b:IN STD_LOGIC;y:OUT STD_LOGIC _VECTOR(7 downto 0));END decoder_3_to_8;ARCHITECTURE rt1 OF decoder_3_to_8 ISSIGNAL indata:STD_LOGIC _VECTOR(2 downto 0);BEGINindata<=c & b & a;PROCESS(indata,g1,g2a,g2b)BEGINIF(g1=′1′ AND g2a=′0′ AND g2b=′0′)THENCASE indata ISWHEN "000"=>y<="11111110";WHEN "001"=>y<="11111101";WHEN "010"=>y<="11111011";WHEN "011"=>y<="11110111";WHEN "100"=>y<="11101111";WHEN "101"=>y<="11011111";WHEN "110"=>y<="10111111";WHEN others=>y<="01111111";END CASE;ELSEy<="11111111";END IF;END PROCESS;END rt1;14.用VHDL设计七段显示译码器解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY segment7 ISPORT(xin:IN STD_LOGIC _VECTOR(3 downto 0);lt,rbi:IN STD_LOGIC;yout:OUT STD_LOGIC _VECTOR(6 downto 0);birbo:INOUT STD_LOGIC);END segment7;ARCHITECTURE seg7448 OF segment7 ISSIGNAL sig_xin:STD_LOGIC _VECTOR(3 downto 0);BEGINsig_xin<=xin;PROCESS(sig_xin,lt,rbi,birbo)BEGINIF(birbo=′0′)THENyout<="0000000";ELSIF (lt=′0′)THENyout<="1111111";birbo<=′1′;ELSIF (rbi=′0′AND sig_xin="0000")THENyout<="0000000";birbo<=′0′;ELSIF (rbi=′1′ AND sig_xin="0000")THENyout<="1111110";birbo<=′1′;ELSEbirbo<=′1′;CASE sig_xin ISWHEN "0001"=>yout<="0110000";WHEN "0010"=>yout<="1101101";WHEN "0011"=>yout<="1111001";WHEN "0100"=>yout<="0110011";WHEN "0101"=>yout<="1011011";WHEN "0110"=>yout<="0011111";WHEN "0111"=>yout<="1110000";WHEN "1000"=>yout<="1111111";WHEN "1001"=>yout<="1110011";WHEN others=>yout<="0100011";END CASE;END IF;END PROCESS;END seg7448;15.用VHDL设计8/3优先编码器解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY priorityencoder ISPORT(din:IN STD_LOGIC _VECTOR(7 downto 0);ei:IN STD_LOGIC;yout:OUT STD_LOGIC _VECTOR(2 downto 0);eo,gs:OUT STD_LOGIC);END priorityencoder;ARCHITECTURE cod74148 OF priorityencoder IS BEGINPROCESS(ei,din)BEGINIF(ei=′1′)THENyout<="111";eo<=′1′;gs<=′1′;ELSEIF(din(7)=′0′ ) THENyout<="000";eo<=′1′;gs<=′0′;ELSIF(din(6)=′0′ ) THENyout <="001";eo<=′1′;gs<=′0′;ELSIF(din(5)=′0′ ) THENyout<="010";eo<=′1′;gs<=′0′;ELSIF(din(4)=′0′ ) THENyout<="011";eo<=′1′;gs<=′0′;ELSIF(din(3)=′0′ ) THENyout<="100";eo<=′1′;gs<=′0′;ELSIF(din(2)=′0′ ) THENyout<="101";eo<=′1′;gs<=′0′;ELSIF(din(1)=′0′ ) THENyout<="110";eo<=′1′;gs<=′0′;ELSIF(din(0)=′0′ ) THENyout<="111";eo<=′1′;gs<=′0′;ELSIF(din="11111111") THENyout<="111";eo<=′0′;gs<=′1′;END IF;END IF;END PROCESS;END cod74148;16.用VHDL设计BCD码至二进制码转换器。

《计算机组成原理》第四版ppt课件剖析

系统结构

1.2.3 微处理器的发展

基本概念

1971年Intel公司开发出Intel 4004。这是第一个将CPU 的所有元件都放入同一块芯片内的产品,于是,微处理 器诞生了。 微处理器演变中的另一个主要进步是 1972 年出现 的 Intel 8008,这是第一个 8位微处理器,它比 4004复杂 一倍。 1974年出现了Intel 8080。这是第一个通用微处理器, 而4004和8008是为特殊用途而设计的。8080是为通用 微机而设计的中央处理器。 20 世纪 70 年代末才出现强大的通用 16 位微处理器, 8086便是其中之一。 这一发展趋势中的另一阶段是在 1981 年,贝尔实验室 和HP公司开发出了32位单片微处理器。 Intel于1985年推出了32位微处理器Intel 80386。 到现在的64

计算机的发展史

类型

第 1代

基本概念

时期

19461957 19581964 19641971

主要器件

电子管

重 要 特 征

机器语言,汇编语言。速度低,体积大, 价格昂贵,可靠性差,用于科学计算。 速度达几千次到几万次 算法语言,操作系统。体积缩小,可靠 性提高。从科学计算到数据处理。每秒 几万次到几十万次

☼ 三、课程与其他课程的联系与分工

☆ 先修课:数字电路、模拟电路、汇编语言程序设计 ☆ 后续课:计算机系统结构、微型计算机系统与设计,关系密切的还有操作系统等课程。

☼ 四、课程总学时中各环节的学时分配(讲授、实验、上机、实践等)

☆ 授课学时:48,实验学时:8

目录 第一章 计算机系统概论

☼

☼ ☼ ☼ ☼

系统结构

1.2.4 计算机的性能指标

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章可编程逻辑

5.1 PLD 的基本概念

5.2 现场可编程门阵列FPGA

5.3 在系统可编程ISP

5.4 可编程逻辑的原理图方式设计

5.5 可编程逻辑的VHDL文本方式设计

返回目录

5.1 PLD的基本概念

5.1.1 可编程阵列

5.1.2 PLD的类型

5.1.1 可编程阵列

1.与阵列

图5.1 与阵列

图5.2例1的与阵列编程

2.或阵列

或阵列如图5.3所示,可编程矩阵的输出连接到或门上。

图5.3 或阵列图5.4 例3的与-或阵列编程

3.可编程连接技术

图5.5 SRAM 为基的与阵列概念

5.1.2 PLD的类型1.简单可编程逻辑器件SPLD

图5.6SPLD内部结构框图

2.复杂可编程逻辑器件CPLD

CPLD本质上是:利用可编程的互连总线连接起来的多路SPLD。

图5.7 CPLD结构框图

5.2 现场可编程门阵列FPGA

5.2.1 FPGA的基本结构

5.2.2 可组态逻辑块CLB

5.2.3 SRAM为基础的FPGA

5.2.1 FPGA的基本结构

图5.8FPGA的基本结构框图

5.2.2 可组态逻辑块CLB

图5.9基本可组态CLB

图5.10 FPGA中一个逻辑模块的框图

图5.11 LUT编程后用作SOP表达式输出

5.2.3 SRAM为基础的FPGA

图5.12 可变FPGA配置的基本概念

5.3 在系统可编程ISP

5.3.1 ispLSI器件的体系结构

5.3.2 在系统编程原理

5.3.1 ispLSI器件的体系结构1.ispLSI 1032框图和巨块的组成

图5.13 ispLSI 1032的体系结构框图和引脚图

2.通用逻辑块GLB

图5.14 GLB的结构框图

图5.15 GLB的标准组态

3.布线区

图5.16 ORP逻辑图

4.输入输出单元IOC

图5.18 I/O单元工作组态图5.17 IOC的结构框图

5.时钟分配网络

图5.19 时钟设置网络

6.ispMACH 4000系列器件

图5.20 ispMACH 4000系列结构框图

5.3.2 在系统编程原理

1.在系统编程原理

图5.21 ispLSI器件的编程结构转换示意图

2.isp器件的编程方式

图5.22典型ISP编程电路

5.4 可编程逻辑的原理图方式设计

5.4.1 编程环境和设计流程图

5.4.2 设计输入

5.4.3 功能模拟

5.4.4 综合和实现(软件)

5.4.5 时序模拟

5.4.6 器件下载

5.4.1 编程环境和设计流程图1.编程环境

2.设计流程图

图5.24 可编程逻辑设计流程

5.4.2 设计输入

图5.25原理图方式(a)和文本方式(b)设计同一逻辑电路

图5.26 逻辑分段与结合的例子

5.4.3 功能模拟

图5.27功能模拟显示图

5.4.4 综合和实现(软件)1.综合阶段

图5.28综合阶段的优化例子

2.实现阶段

5.4.5 时序模拟

图5.29时序模拟的假定例子

5.4.6 器件下载

图5.30下载一个设计到目标器件

5.5 可编程逻辑的VHDL文本方式设计

5.5.1 VHDL的基本概念

5.5.2 VHDL的组合逻辑设计

5.5.3 VHDL的时序逻辑设计

5.5.1 VHDL的基本概念

图5.31

5.5.2 VHDL的组合逻辑设计1.VHDL编程中的数据流描述方法

图5.32 一个SOP形式逻辑电路

2.VHDL编程中的结构描述方法

图5.33 VHDL结构法与固定逻辑IC硬件实现法的比较

图5.34 VHDL组件示例

图5.35 例8的逻辑电路图

3.VHDL编程中库元件调用法

5.5.3 VHDL的时序逻辑设计

图5.36 时钟边沿与属性描述

图5.37 序列检测器有限状态机。