DDS的误差分析

DDS波形发生器幅度量化误差的分析及其抑制[1]

![DDS波形发生器幅度量化误差的分析及其抑制[1]](https://img.taocdn.com/s3/m/c84cce0c90c69ec3d5bb75ff.png)

1 引 言

直接数字频率合成 (DDS技术 )是近年来发展 迅速的一种新的频率合成技术 。同传统的频率合成 技术相比 ,全数字化的结构赋予了 DDS很多优点 : 频率切换时间短 ,频率分辨率高 ,相位变化连续 ,易 实现对输出信号的多种调制等 ,使得 DDS具有广阔 的应用前景 。但是由于 DDS数字化实现的固有特 点 ,决定了其输出频谱杂散较大 。本文对 DDS相位 累加杂散做了深入研究 ,提出了一种新的方案 ,通过 对相累加脉宽调制来实现杂散抑制 ,使 DDS的性能 得到提高 ,杂散抑制比达到了 - 75dB。

图 8 基于 SoC运动估计模块仿真波形

6 结 束 语

运动估计控制器实现了对 ME 中子模快的控 制 。系统仿真的结果表明 ,对于一帧图像中 1350个 宏块运动估计的结果与已知的结果相同 ,说明控制 器在功能上是正确的 。此外 ,控制器总线接口部分 的数据传输速率完全可以满足 ME的要求 ,使整个 运动估计过程在很高的效率下进行 ,而未引入额外 的延迟 。本控制器为 M E充分发挥运算能力提供了 支持 ,从而使得嵌入了 M E模块的 SoC平台对视频 图像处理变得容易 。

相累加器的相位输出 。这样我们就得到输出信号的

两个连续相值 。将系统时钟作为读取时钟 ,在两个

相值间进行相的切换 ,这样经过低通滤波就可以得

到两个相位中间的值 ,在本设计中 ,我们用一个二进

图 2 电路实现框图

图 3 仿真波形

我们运用这一方 法设 计了 一个 简单 的 DDS。 以下对本设计做简单介绍 。DDS由一个 8位的相累 加器 ,一个 6位的信号查找表 ,一个 6位的数模转化 器组成 。时钟频率为 25KHz,低通滤波器的固定截 断频率为 10kHz. 使用了本方案的 DDS电路的谐波 及非谐波抑制达到 70dB。电路仿真输出波形如图 3: a为时钟信号 ; b, c, d分别是标准 DDS电路中的

光纤陀螺随机误差的DDS建模方法研究

Re e r h n DDS m o lng o b r Optc G y o c pe r n m r o sa c o de i fFi e i r s o a do e r r

WA GZ i e, US umn , N o g i L o g i N h- i HO h - ig WA G H n — , V Y n  ̄a w l

光 纤 陀 螺 随机 误 差 是 影 响 光 纤 陀 螺 精 度 的 重 要 因素 , 随 着 随机 误 差 理 论 及 分 析 方 法 的不 断 进 步 . 们 对 激 光 陀 螺 随 人

机 误 差 的分 析 也 不 断 深 人 。 管 A MA模 型 已经 形 成 相 当完 尽 R

风 : 型 I, A M p,) 用 ; 模 即 R A( 口 适

第 1 9卷 第 1 期 1

Vo.9 11

No 1 .1

电子 设计 工程

El cr n c De i n Engn e i g e to i sg i e rn

2 1 年 6月 01

J n 2 1 u.01

光纤 陀螺 随机 误差 的 DDS建模 方 法研 究

王 志伟 ,侯 书铭 ,王 宏 力 ,吕永佳

r n o e  ̄ . e eo e, r c u ae c mp n ain o e F a d m ro a e tk n w t h smeh d a d m n r T r fr a mo e a c r t o e s to ft OG r n o e rrc n b e i t i t o . h h a h

DDS mo e ig me o a c u ae y ma e mo e ig o ie t r s o e n s l t t e rn o so e i ms o e d l t d c n a c r tl k d l fF b rOp i Gyo c p ,a d ioa e h a d m l p t f t n h n c e h

DDS信号频谱的杂散分析与抑制方法研究

DDS信号频谱的杂散分析与抑制方法研究摘要:DDS技术具有高分辨率、快速转换、相位连续可控等优点,但也存在因相位截断、幅度亮度与DA转换器的非线性因素等误差造成的杂散。

针对DDS信号频谱杂散的原因进行了分析,并对相关抑制方法加以介绍,对各类抑制方法的特点进行了综述。

关键词:DDS;信号预谱;杂散0引言DDS(DirectDigitalSynthesis,直接数字频率合成)技术与传统的频率合成技术最大的区别是通过相位的运算实现频率的合成。

它具有极高的频率分辨率、极快的转换速度及输出相位连续可控等明显优点,目前在仪器仪表、雷达、通信与电子仪器等各个领域广泛使用。

但DDS技术也有瓶颈所在,即输出杂散大和输出带宽窄,这两个技术劣势是阻碍DDS深入推广的关键因素。

造成DDS杂散的主要因素有以下3个:相位截断、幅度量化与DA转换器的误差。

除了这3个主要原因之外,本文对其它影响频谱的杂散来源进行分析,并从原理上深入探讨,同时结合目前广泛使用的各种抑制策略,针对杂散起因,分门别类地改善信号的频谱纯净度,达到杂散抑制效果。

1DDS基本工作原理DDS技术是基于数值计算信号波形的抽样值来实现频率合成的。

它的主要组成为相位累加器、ROM波形查询表、数模转换器。

其基本框图如图1所示。

图1DDS组成基本框图DDS中的累加器使用二进制计算,线性数字信号通过相位累加器实现逐级累加,每累加一次即做一次2N模的运算得到当前相位值。

并以当前相位值查询ROM波形表中对应存储的波形幅度值,送入DA转换器中转换为模拟信号,最后通过低通滤波做平滑处理。

不妨设正弦信号S(t)的表达式为:S(t)=Asin(2πft+0)(1)其中,A为振幅,f 为频率,0为初始相位。

信号的频率与初始相位无关。

通过改变频率控制字K的大小实现对频率的控制,输出的频率随K成正比连续变化。

一般最低的输出频率为:fmin=1122Nfc(2)由奈奎斯特抽样定理知,为了保证信号不发生重叠,最高频率的理论值是DDS芯片时钟频率(Fs)的50%,即:fmax≤1122fc(3)但是考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率按照40%处理。

一种抑制DDS相位截断误差引起的杂散方法[1]

![一种抑制DDS相位截断误差引起的杂散方法[1]](https://img.taocdn.com/s3/m/7a3be947852458fb770b56fd.png)

17ΞΞΞΞΞ电路与系统学报J OURNAL OF CIRCUIT S AND S Y S TEMS第2卷第4期1997年11月V ol.2N o.4N ovember 1997收文日期:1997年4月25日(A p ril 25,1997)。

F en g Jie ,Chen Shiw ei (Institute of C omm and and T echnolot y ,Bei j in g ,101407)一种抑制DDS 相位截断误差引起的杂散方法ΞA Method of Re p re ssin g S p ur Caused b y Pha se Truncation Error冯杰陈世伟(国防科工委指挥技术学院,北京,101407)【摘要】本文通过分析直接数字频率合成器的工作过程,利用相位截断误差与频率控制截断字的关系,提出了一种抑制杂散的途径。

关键词:直接数字频率合成,相位截误差,误差分析,杂散。

Abstract :T he p rocessin g of Direct Di g ital Fre q uenc y S y nthesizer (DDS )is anal y zed the relation betw een p hase truncation error and fre q uenc y control truncation w ord is derived.A m eth od of re p ressin g s p ur caused b y p hase truncation error is p ressented.K e y words :Direct Di g ital Fre q uenc y S y nthesizer ,Phase truncation error ,Phase error anal y sis.1引言DDS 概念出自1971[1],它的出现导致了频率合成器的第二次革命,DDS 具有超宽的相对宽带,超高的捷变速率,超细的分辨率以及相位的连续性,可以输出宽带的正交信号,可编程全数字化便于单片集成,以及极易实现各种调制等优越性能,由于它良好地解决了频率捷变系统的要求,DDS 应用越来越广泛。

DDS工作原理及性能分析

Beijing university of Posts and Telecommunications Abstract

The fundamental theory of direct digital synthesizer (DDS) and the spectrum of the output signal under the ideal conditions are introduced firstly. Then the characteristics are analyzed, and the error signal in engineering is described. There are three main sources of spurious signal in DDS: the truncation of the phase accumulator bits in the sine ROM, the finite precision of the sine samples stored in the ROM, and the digital-to-analog conversion. Keywords:Direct digital synthesizer (DDS); spur suppression; phase truncation; quantization distortion

[1] 吕庆等 对于 DDS 杂散信号抑制的分析和仿真 雷达科学与技术 Vol.1 No.3 2003 年 10 月 [2] 张若禹等 DDS 频谱分析与杂散预测软件包 装备指挥技术学院学报 Vol.16 No.4 2005 年 4 月 [3] Analog Device, Inc. A technical tutorial on digital signal synthesis [EB/OL]. .

DDS产品技术指标

DDS产品技术指标DDS是一种以数字方式合成波形的技术,该技术将数字信号转化为模拟信号,因此在数字信号处理(DSP)和通信系统中有广泛应用。

以下是DDS产品常见的技术指标:1.频率分辨率:DDS产品的频率分辨率是指其能够合成的最小频率步进值。

它决定了DDS在频率合成中的精度,一般以Hz为单位进行表示。

例如,一个DDS产品具有10Hz的频率分辨率,可以在全频率范围内以10Hz的步进合成波形。

2.输出频率范围:DDS产品的输出频率范围是指其能够合成的频率范围。

它通常由最小频率和最大频率两个参数来表示,并以Hz为单位。

例如,一个DDS产品的输出频率范围可以是1Hz到100MHz。

3.相位分辨率:DDS产品的相位分辨率是指其能够合成的最小相位步进值。

相位是指波形在一个周期内的相对位置,相位分辨率决定了DDS在相位合成中的精度。

它通常以度或弧度为单位进行表示。

4. 输出幅度范围:DDS产品的输出幅度范围是指其能够输出的最大和最小幅度。

它通常由最小幅度和最大幅度两个参数来表示,并以dBm或Vpp等单位进行表示。

5.清晰度:DDS产品的清晰度是指其输出波形在各个频率点上的纯净度或失真程度。

它通常以百分比或dB值来表示,清晰度越高,波形的失真越小。

6.相位累积误差:DDS产品的相位累积误差是指在频率合成的过程中,由于DDS内部的相位累积误差而引起的输出波形相位偏差。

它通常以度或弧度为单位进行表示。

7.信噪比:DDS产品的信噪比是指输出波形中信号与噪音之间的比值。

它通常以dB值来表示,信噪比越高,输出波形中的噪音越小。

8. 频率稳定性:DDS产品的频率稳定性是指在特定的环境条件下,DDS输出频率的波动范围。

它通常以ppm或Hz为单位进行表示。

9.采样率:DDS产品的采样率是指输入的数字信号的采样频率。

它通常以Hz为单位进行表示,采样率越高,合成的波形的频率分辨率越高。

10. 灵敏度:DDS产品的灵敏度是指其对输入信号变化的响应能力。

一种DDS频率源中相位截尾误差的算法

一种DDS频率源中相位截尾误差的算法汪海燕【摘要】根据DDS原理结构,从理想模型出发,分析了DDS中相位截尾对频谱的影响,给出相位截尾误差谱分布规律,提出一种相位截尾误差谱算法,没有采用近似处理,适合任意波形数据表地址字长、短,算法快速,精度高。

%This paper introduces the structure of DDS principle and the distribution law of phase accumulator truncation errors after analyzing its effects on frequency spectrum and puts up with an algorithm for the errors without approximate treatment, which is more precise and efficient.【期刊名称】《西昌学院学报(自然科学版)》【年(卷),期】2016(030)003【总页数】2页(P15-16)【关键词】DDS;相位误差;算法分析【作者】汪海燕【作者单位】安徽电子信息职业技术学院,安徽蚌埠 233060【正文语种】中文【中图分类】TN74+1直接频率合成技术(DDS)是近十年来迅速发展的一种频率合成技术,其原理如图1所示,由相位累加器、存储器RAM、数模转换器DAC及低通滤波器组成[1]。

DDS的数学模型可概括如下[2]:时钟周期T内,频率控制码比特相位累加器累加1次,对2N取模,运算的二进制代码值,对RAM寻址,得到其相位值相对应的数字化幅度值,然后由DAC数模转换,实现离散信号转换为连续信号,然后由低通滤波器滤波输出,最终获得输出信号。

由上可知,DDS的输出频率满足:,输出频率最小出现在K=1时。

对于理想DDS,即没有相位误差、没有幅度量化误差,以及没有DAC误差[3]。

设DDS输出信号为s(t),傅立叶变换为s(f),DAC输出零阶保持,设T=1/fc,保持器特性为h(t)=l(t)-l(t-T),其傅立叶变换为。

单相多功能电能表的电能计量误差分析与校正

单相多功能电能表的电能计量误差分析与校正电能表是用于测量电能消耗的仪器,它在各个领域中都发挥着重要作用。

然而,由于一些内外部因素的影响,电能表的测量结果可能存在一定的误差。

因此,进行电能计量误差分析与校正非常重要,以保证电能表的测量准确性和可靠性。

首先,我们需要了解电能计量误差的来源。

电能计量误差主要分为两类:系统误差和偶然误差。

系统误差是指电能表在整个测量范围内的长期偏离真实值的误差,它可能由于电能表内部元器件参数值的漂移、温度变化和电源干扰等因素引起。

而偶然误差则是指电能表在一次具体测量中的暂时性误差,可以通过多次测量求平均值来降低。

其次,我们需要了解电能表的精度等级。

电能表的精度等级是描述其测量准确性的参数,通常用百分比表示。

例如,一个精度等级为0.5的电能表,其误差范围为±0.5%,即其测量结果可能偏离真实值的最大范围为±0.5%。

对于电能计量误差的分析与校正,我们可以采取以下几种方法:1. 校正电能表的系统误差:校正系统误差可以通过比较电能表读数和标准接线箱上的真实电能值来实现。

我们可以选择一台已经过校准的标准电能表作为参照,将待校表和标准表同时接入相同的电路中进行测量,然后比较两者的读数。

根据比较结果,我们可以计算出待校表的系统误差,并进行相应的调整。

通常,这种校准方法需要在实验室或特定条件下进行,以确保准确性。

2. 通过多次测量降低偶然误差:偶然误差可以通过多次测量求平均值来降低。

我们可以选择在不同时间、不同负载条件下进行多次测量,然后计算出平均值。

采用这种方法可以降低测量误差,并增加结果的可靠性。

3. 定期检查和维护电能表:定期检查和维护电能表也是保证其测量准确性的重要措施。

我们可以定期检查电能表的接线是否松动,电源是否稳定,元器件是否正常工作等。

对于有条件的情况,我们还可以使用特定的电能表测试仪器对电能表进行全面的检测和校准。

需要注意的是,在进行电能计量误差分析与校正时,应遵循相关的标准和规定。

DDS216型单相电子式电能表误差

DDS216型单相电子式电能表误差

案例一

一、误差来源电子式电能表具有准确度高、线性好、量程宽等优点。

但也有其误差来源,主要来自电流取样器、电压取样器和模拟/数字乘法器三个部分。

二、误差的调整电子式电能表的误差调整分为硬件和软件调整,目前生产的单相电子式电能表以硬件调整为主,而电子式三相电能表以软件调整为主。

特别是多功能电能表的误差是以软件调整为主。

电能表的准确等级就是根据基本误差确定的。

例如,1.0级的电能表,其基本误差应不超过±1.0%。

注意:电能表的相对误差化整间距一般是被试表准确度等级的1/10。

如2.0级电能表的相对误差化整间距为0.2 。

案例二

(1)温度误差。

电子式电能表分压器一般选用1%精度的金属膜电阻,其温度系a≤50×10—6,故对于0.5级以下精度的电能表,其误差随温度变化可以忽略不计。

(2)一次电压误差。

因为其为电阻分压,一次电压变化对误差影响几乎可忽略不计。

(3)负载影响。

无论是模拟还是数字乘法器,均采用CMOS 大规模集成电路,其电压回路的输入电阻相对于几十千欧的电阻分压网络为无穷大,故而负载引起误差几乎为零。

(4)频率(0~1kHz)对误差的影响几乎为零。

同样电压互感器的误差特性也存在上述几个方面,但都不如电阻网络分压器。

单相脉冲电能表的测量误差及校正方法

单相脉冲电能表的测量误差及校正方法单相脉冲电能表是一种常见的电能计量设备,用于测量和记录家庭或工业场所的电能消耗。

然而,由于各种因素的影响,单相脉冲电能表的测量误差是难以避免的。

本文将探讨单相脉冲电能表的测量误差产生的原因和常用的校正方法。

首先,我们需要了解单相脉冲电能表的工作原理。

单相脉冲电能表通过测量电流和电压来计算电能的消耗,然后将结果转换为脉冲信号输出。

这些脉冲信号可以通过计算脉冲的数量来获得电能的总量。

然而,由于多种因素的影响,单相脉冲电能表的测量误差会出现。

其中最常见的误差来源包括电流传感器的非线性、电压传感器的误差、温度对传感器性能的影响以及外部干扰等。

针对这些误差原因,我们可以采取以下校正方法来减少测量误差。

首先,对于电流传感器的非线性误差,我们可以使用压降法进行校正。

该方法通过对电流传感器施加不同的负载电阻来测量电流传感器的非线性特性,从而获得准确的电流测量值。

其次,对于电压传感器的误差,我们可以通过校正电压传感器的增益和偏移来纠正误差。

这可以通过对输入端施加已知电压并记录测量值,然后利用线性回归方法来计算校正系数。

校正系数可以用于调整电压传感器的测量值,从而减小误差。

此外,温度对传感器性能的影响也是一个重要的测量误差来源。

我们可以采用温度补偿方法来减小误差。

该方法通过在传感器电路中添加温度传感器来测量环境温度,并根据温度变化对测量值进行校正。

最后,针对外部干扰的影响,我们可以采取屏蔽和滤波的方法来减小误差。

通过在电能表的电路中添加屏蔽层和滤波器,可以有效地过滤掉外部干扰信号,提高测量的准确性。

除了以上的常用校正方法,定期的维护和校准也是保证单相脉冲电能表准确测量的关键。

定期检查电能表的各项指标,并进行必要的校准,可以确保其性能稳定和准确度可靠。

总结起来,单相脉冲电能表的测量误差是由多种因素共同作用所导致的。

通过了解误差的来源和原因,我们可以采取相应的校正方法来减小误差。

这些方法包括压降法校正电流传感器的非线性误差、校正电压传感器的增益和偏移、温度补偿和屏蔽滤波等。

DDS频谱分析及一种新型的改善方法

DD S 频谱分析及一种新型的改善方法韩军功 王家礼(西安电子科技大学机电工程学院 西安 710071)摘 要 从理论上分析了DD S 频谱杂散的来源和特点,在此基础上讨论了一种新的DD S 结构,采用扰码技术来抑制DD S 相位舍位杂散,并且用计算机模拟表明这种新结构大大的消除了DD S 的相位舍位杂散。

关键词 直接数字频率合成(DD S ) 频谱分析 杂散 扰码1 引 言直接数字频率合成(DD S )技术是近年来迅速发展起来的一种新兴的频率合成技术,它具有频率捷变速度快、频率分辨率高、相位连续以及可灵活产生波形等特点,一经问世就受到电子工程师的广泛关注。

特别是近几年来,可编程逻辑器件(CPLD )的迅速发展给DD S 的应用带来了更为广阔的前景,越来越多的人用CPLD 自己设计各种DD S 芯片。

现在,DD S 已经成为宇航、雷达、通信、电子战等系统中的首选。

但是,同锁相频率合成技术(PLL )相比,DD S 也有着许多致命的缺点。

其中最主要的缺点就是DD S 输出的频谱杂散较大,在输出带宽较窄时,可达到-70dB ~-90dB ,这基本满足要求。

但当输出带宽达几百兆赫兹时,只能做到-40dB ~-50dB 。

所以,如何改善DD S 的杂散一直是困扰国内外学者的难题,成为这个领域研究的热点。

本文首先对DD S 系统的频谱做了分析,然后给出一种新型的改善杂散的方法,并用计算机模拟仿真来比较它与传统方法性能的差异。

2 DD S 的基本工作原理及理想频谱图1即为DD S 系统的基本模型,从模型可以看到DD S 系统相当于一个数字控制器(N CO )其输出频率满足:f 0=k 3F clk 2N (1)当k =1时,DD S 的最小分辨率可达:∃f m in =F clk 2N图1 DD S 系统的基本模型图2 理想采样电路的等效模型从这个模型可以看出在理想的DD S 中DA C 以前的部分,实际上相当于一个理想的采样电路:从图2这个等效模型可推知理想的DD S 的s (n )=sin (2Π3f 03n 3T c )=sin (2Π3k 3F clk 3n 3T c 2N )=sin (2Π3k 3n 2N ) (2) 其中:T c =1 F clk 。

多DDS并行伪差值合成的相位截断误差分析

多DDS并行伪差值合成的相位截断误差分析刘科;田书林;肖寅东【摘要】The principle of pseudo interleaving of multiple DDSs and spectrum expressions with ideal parameters are analyzed. The model of pseudo interleaving of multiple DDSs with phase truncation is established. Based on the model, the distribution and amplitude of spur caused by phase truncation are discussed and analyzed. Then some important conclusions are drawn and proved by simulation,which can provide theoretical supports for spurious performance evaluation and parameter selection in design signal source or clock generator based on pseudo interleaving technique.%对理想多DDS伪插值信号的原理与频谱分布进行分析,建立了相位截断情况下的多DDS伪插值系统模型,在此模型基础上对相位截断杂散频谱进行分析与计算,给出相位截断频谱杂散的分布规律和幅度大小,得出关于杂散谱线数量、分布规律及频率控制字选择依据的一些结论,并利用计算机仿真与硬件实验对不同参数时的相位截断频谱杂散进行验证.这些分析可用于伪插值DDS信号源或时钟发生器设计中的杂散评估与方案选择及指标分配提供理论依据.【期刊名称】《计量学报》【年(卷),期】2011(032)006【总页数】6页(P544-549)【关键词】计量学;相位截断;伪插值;杂散;直接数字合成【作者】刘科;田书林;肖寅东【作者单位】电子科技大学自动化工程学院,四川成都611731;电子科技大学自动化工程学院,四川成都611731;电子科技大学自动化工程学院,四川成都611731【正文语种】中文【中图分类】TB9731 引言基于直接数字合成(Direct Digital Synthesis,DDS)技术的频率合成具有频率分辨率高、频率切换速度快、频率切换时相位保持连续等优点,在通信、雷达及对抗等领域被广泛应用。

基于FPGA的DDS信号源设计及误差分析

总第176期2009年第2期舰船电子工程Ship Electronic EngineeringVol.29No.272基于FPGA的DDS信号源设计及误差分析3曾 云 韩顺锋(中国船舶重工集团公司第722研究所 武汉 430079)摘 要 介绍直接数字频率合成(DDS)技术的原理,给出一种利用FP GA和DAC转换器的实现方案。

这种方案具有频率分辨率高、设计简单、输出灵活等特点,是实现DDS的一种理想方案。

给出DDS的误差分析,并且根据误差的产生原因提出了一些应对办法,试验表明,输出的波形效果良好。

关键词 FP GA;Verilog HDL;直接数字频率合成;误差分析中图分类号 TN74Design a nd Error Analysis of DDS Signal GeneratorBased on F PGAZe ng Yun Ha n Shunf e ng(No.722Research Institute of CSIC,Wuhan 430079)Abs t rac t This article introduces the principle of the Direct Digital Synthesizer(DDS),and gives the scheme uses FP GA and DAC.This scheme has the advantage of high f requency resolution,easy to design and output flexible and so on,so it is the ideal scheme of the DDS.Finally,the error analysis of DDS is bring forward and gives some methods to solve it.The ex2 periment proves that the output of the signal was fine.Ke y w ords FP GA,Verilog HDL,DDS,error analysisClass Nu m ber TN741 引言随着电子技术的飞速发展,很多领域对信号的频率准确度和稳定度提出了越来越高的要求,于是出现了高稳定和高准确度的晶振,但应用领域的拓展不仅需要在一个固定的频率上有较高的频率准确度和稳定度,在很多的频点上同样要求也很高,而高稳晶振只能在一个固定的频点或很小的范围内满足要求,例如短波通信电台,需要成千上万的通信频点才能满足要求,频率合成技术就应运而生了,20世纪30年代提出了直接频率合成技术,利用单个或不同频率的晶体振荡器作为基准信号源,经过倍频、分频、混频等途径直接产生许多离散频率的信号。

DDS的误差分析

DDS 的误差分析摘要:随着电子技术的不断发展,被测系统的工作频率、复杂程度不断提高,对激励信号源的输出信号带宽、输出波形的复杂度提出了更高的要求。

基于直接数字合成技术的任意波形合成方法,以其信号产生方式灵活、频率分辨率高、频率切换速度快等诸多优点,在现代时域测试中得到了广泛的应用。

可是DDS 的杂散分量较多,严重影响了基于 DDS 的任意波形合成输出信号的波形质量,限制了任意波形合成技术的更广泛应用。

针对 DDS 输出信号杂散分析与抑制一直是研究的热点,也有大量的技术被提出。

本文将从相位截断、幅度量化误差和DAC 非线性等三个方面来讨论误差的产生以及一些基本的消除方法。

关键词:直接数字合成 任意波形合成 相位截断 幅度量化 DAC 非线性 1 DDS的原理1.1 DDWSDDWS 主要由地址发生器、波形查找表、数模转换器和可变时钟发生器组成。

根据预定的采样频率、所需信号的时域特征、波形长度等参数,由信号的数学表达式计算出各信号点幅度值,经过量化后按采样顺序预先存储在波形查找表中。

可变时钟发生器按照用户设置的采样频率输出相应的时钟信号。

每一个时钟信号的上升沿,地址发生器的输出地址加 1,地址发生器的输出地址对波形查找表寻址,逐点读出波形数据,经数模转换后生成相应的输出信号。

设可变时钟频率为f S,若周期波形每个周期由 n 个采样点构成。

1.2 DDFS由于 DDWS 产生新的频率必须通过更改采样时钟的频率或波形存储器中的数据点数来实现,作为振荡器应用具有较大的局限性。

因此提出了如图 2-2 所示基于相位累加器的改进模型,即直接数字频率合成(DDFS)。

DDFS 系统主要由固定时钟发生器、相位累加器、波形查找表、数模转换器和低通滤波器等组成。

在采样时钟的控制下,N 位的相位累加器以频率控制字 K 进行累加,截取高 M 位作为相位地址对波形查找表进行寻址,输出相应的 D 位幅度信息,完成波形相位到幅度的转换。

DDS频率合成器相位截断误差频谱特性仿真分析

0 引言

DS D 频率合成器具有分辨率高 、 频率转换速度

会引起杂散频率为 一, 4 -

4o - 的杂散信号 , f 其

中 为 时 钟 频 率 , n 为 整 数 , 满 足 : = m, ( o2 )・, 2 , 中 X = K A = G D K, Xm d : 其 / /, C( 2 ) G D K, 表示 2 ,C ( 2 ) 和 的最大公 约 数 。

A s r c : I i c ii lf q e c y te i r te s e t m s mi eln o s b c u e o l e h g e i b ta t n dr t gt e u n y s nh sz , p c r i s l e u e a s ny t ih rb t e d a r e h u c a h s ae r m ie u i g te c u s f e kn d r s . h e t _ h rce s cc u e y t ep a e t mc t n r e a n d d r o r o e i a d e s T e s c rm c aa tr t a s d b h s n ai n h e s g p u i i h o i e lt n l n ls d w t y tmve s muai a ay e i S s o a h e i w.I h st ei p r n eee c au t es lcin o f q e c o — t a o t t frn e v e o h ee t r u n yc n h m a r l f o f e

DDS频率合成的主要问题及相位截断误差的仿真

DDS频率合成的主要问题及相位截断误差的仿真[摘要]从DDS频率合成的基本原理入手,分析DDS电路中常见的问题,针对频率合成中相位截断误差的问题,提出有效的解决方法,并且对滤波器的设计给出思路,最后用matlab仿真了相位截断误差,给出了频谱图。

[关键词]频率合成DDS 相位截断误差滤波器一、ROM+D/A模式的DDS雏形把一个周期的模拟波形信号通过取样、量化、编码,形成一个正弦函数表储存在ROM中,通过顺序的提供周而复始的地址,从ROM中读出该量化后的数字波形信号,再通过D/A还原,这种ROM+D/A模式的波形合成技术就是DDS 技术的雏形。

而发展到现在的DDS系统一般是由频率控制、相位累加、波形存储、D/A转换以及低通滤波等组合构成。

在时钟作用下,相位累加器不断对频率字K进行线性相位累加,两者共同决定送给波形存储器ROM的地址间隔,从而影响波形采样的点数和速度,后面通过D/A转换再加以LPF过滤高次谐波从而更好的还原波形。

二、DDS频率合成中的主要问题及其解决办法我们在设计理想的DDS时根据有3个理想条件:1.相位累加器的N位输出全部都用于ROM表寻址,即没有相位截断;2.ROM表中的存储值是完全真值,没有量化误差;3.DAC转换、低通滤波都是理想器件。

在实际应用中这3方面都存在一定的问题,因此DDS频率合成信号输出精度受以下3方面的误差所影响:1.相位截断误差。

为使DDS具有很高的频率分辨率,一般相位累加器的位数N都取的很大,如N=48,若这N位都用于寻址,可想而知,其所需的ROM 存储量将极大,实际不可用,故通常将N位相位的高A位用于寻址,其余低位舍弃不用,这样就引入了相位截断误差。

这是DDS频率合成误差的主要来源,后面将用matlab进行仿真分析。

2.幅度量化误差:ROM中存储着正弦波样点的幅值编码,任何个幅度值要用无限长的比特流才能精确表示,而实际中ROM的输出位是有限的,这样就引入了幅度量化误差。

关于DDS的分析

DDS 理论分析和实现方法(1) DDS 工作原理和理想DDS 的输出频谱DDS 工作原理如图1-2所示,用满足Nyquist 准则的一定频率对正弦信号(也可以是对任意周期信号)进行采样,控制采样周期t ∆之间的相位增量φ∆,每次累加到相位寄存器中,用得到的相位值来寻址ROM 查找表,实现相码和幅码的转换,得到输出波形的幅度值,经过D/A 转换为模拟信号,就得到了输出频率信号t ∆∆=/φω。

设相位累加器的位数为N ,频率控制字长为K ,那么得到的输出阶梯函数可以表示为采样序列和矩形序列的卷积)()()cos()(0t q nT t t t S n n c ⊗-=∑∞=-∞=δω 其中c N K ωω20=,c ω系统时钟频率,0ω 为输出波形的频率,c T 为采样序列周期。

矩形函数表示为)()()(c T t U t U t q --=,)(t U 是阶跃函数。

对)(t S 进行傅立叶变换,得到波形的频谱: ∑∑∞-∞=∞-∞=--+⋅⎪⎪⎭⎫ ⎝⎛+++--⋅⎪⎪⎭⎫ ⎝⎛-=n c c c c c n c c c c c n n j n Sa n n j n Sa S )()(exp()()(exp()(000000ωωωδωωωωωωπωωωδωωωωωωπω式中x x x Sa sin )(=。

从上式可以看出,理想DDS 输出信号的谱线是以()Sa 函数为包络的离散谱线,谱线位于0ωω±c n 处,用截止频率位于2/c ω的低通滤波器滤除高阶谱部分,得到0ω的输出波形。

(2) 信号频率与频率控制字的关系设累加器按外接晶振频率信号c f ,把频率控制字K累加到相位累加器上,则此时相位累加器的值为c f *K;对于n 位地址的ROM 来说,在一个波形中有n 2个样点,信号输出的频率就应当为=o f c f ⨯K/n 2如果1=K ,每次累加结果的增量为1,则依次从数据ROM 中读取数据;如果2=K ,则每隔一个ROM 地址中读取一次数据;依次类推。

对电学中两种测量的误差分析

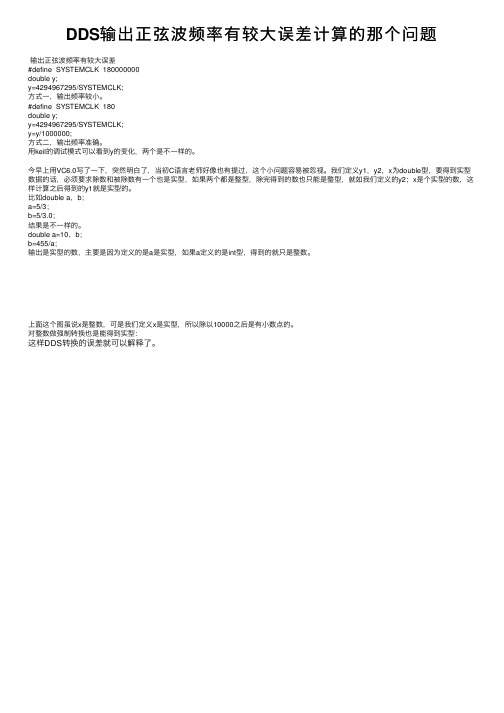

对电学中两种测量的误差分析湖南单文忠一、半偏法测电表内阻的误差分析测量电表内阻常用稳流半偏法,其电路如图1所示。

图1(一)两点要求:1. 21R R >>,R 2一定要用电阻箱,R 1可用电阻箱或滑动变阻器。

2. 闭合S 2,调节R 2时,R 1保持不变。

(二)具体操作:先闭合S 1,断开S 2,由大到小调节R 1使电流表达到满偏;保持R 1不变,闭合S 2,由大到小调节R 2使电流表半偏,读出此时R 2的读数,此读数即为电流表内阻的测量值。

(三)误差产生原因:R 2的分流作用。

(四)误差分析:1. 定性分析:闭合S 2后,电路由于R 2的接入,外电阻变小,总电流变大。

当调到电流表半偏时,由于电阻箱R 2与电流表并联,故此时流过R 2的电流大于电流表的半偏电流,据并联电路电阻的分流作用可知R 2此时的读数小于电流表的内阻,所以用半偏法测电表内阻,测量值小于真实值。

2. 定量分析:闭合S 1、断开S 2,调到电流表满偏有:)]r R (R [I E 1g g ++=①保持R 1不变,调节R 2使电流表半偏有:)r R )(R 2R I 2I (2R I E 12g g g g g +++=②联立①、②消去r R 1+得:ER I R R 2gg g 2-=,故测量值小于真实值。

电表内阻g R 测量的绝对误差为ER I R R 2gg 2g =-,相对误差为ER I R R R g g g2g =-=δ。

二、伏安法测电源电动势和内阻的误差分析测量电源电动势和内阻由于安培表接法的不同而有两种电路。

1. 安培表内接法a. 测量电路如图2所示。

图2b. 误差产生原因:由于电压表的分流作用c. 误差分析:不考虑电压表的分流作用,所测得的电源电动势和内阻均为测量值;反之,则为真实值,故有:测测r I U E 11+=① 测测r I U E 22+=②联立①、②解得:⎪⎪⎩⎪⎪⎨⎧--=--=2112211221I I U U r I I U I U I E 测测真真r )R U I (U E V 111++= ③真真r )R U I (U E v222++=④联立③、④解得:⎪⎪⎩⎪⎪⎨⎧-+--=-+--=)U U (R )I I (R )U U (r )U U (R )I I (R )U I U I (E 21V 21V1221V 21V 1221真真真测真真测测真真测,所以可得:可构建等式与r r r r R R r R 1r 1r 1r r V V v <⋅+=-=。

DDS输出正弦波频率有较大误差计算的那个问题

DDS输出正弦波频率有较⼤误差计算的那个问题

输出正弦波频率有较⼤误差

#define SYSTEMCLK 180000000

double y;

y=4294967295/SYSTEMCLK;

⽅式⼀,输出频率较⼩。

#define SYSTEMCLK 180

double y;

y=4294967295/SYSTEMCLK;

y=y/1000000;

⽅式⼆,输出频率准确。

⽤keil的调试模式可以看到y的变化,两个是不⼀样的。

今早上⽤VC6.0写了⼀下,突然明⽩了,当初C语⾔⽼师好像也有提过,这个⼩问题容易被忽视。

我们定义y1,y2,x为double型,要得到实型数据的话,必须要求除数和被除数有⼀个也是实型,如果两个都是整型,除完得到的数也只能是整型,就如我们定义的y2;x是个实型的数,这样计算之后得到的y1就是实型的。

⽐如double a,b;

a=5/3;

b=5/3.0;

结果是不⼀样的。

double a=10,b;

b=455/a;

输出是实型的数,主要是因为定义的是a是实型,如果a定义的是int型,得到的就只是整数。

上⾯这个图虽说x是整数,可是我们定义x是实型,所以除以10000之后是有⼩数点的。

对整数做强制转换也是能得到实型:

这样DDS转换的误差就可以解释了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDS 的误差分析

摘要:随着电子技术的不断发展,被测系统的工作频率、复杂程度不断提高,对激励信号源的输出信号带宽、输出波形的复杂度提出了更高的要求。

基于直接数字合成技术的任意波形合成方法,以其信号产生方式灵活、频率分辨率高、频率切换速度快等诸多优点,在现代时域测试中得到了广泛的应用。

可是DDS 的杂散分量较多,严重影响了基于 DDS 的任意波形合成输出信号的波形质量,限制了任意波形合成技术的更广泛应用。

针对 DDS 输出信号杂散分析与抑制一直是研究的热点,也有大量的技术被提出。

本文将从相位截断、幅度量化误差和DAC 非线性等三个方面来讨论误差的产生以及一些基本的消除方法。

关键词:直接数字合成 任意波形合成 相位截断 幅度量化 DAC 非线性 1 DDS的原理

1.1 DDWS

DDWS 主要由地址发生器、波形查找表、数模转换器和可变时钟发生器组成。

根据预定的采样频率、所需信号的时域特征、波形长度等参数,由信号的数学表达式计算出各信号点幅度值,经过量化后按采样顺序预先存储在波形查找表中。

可变时钟发生器按照用户设置的采样频率输出相应的时钟信号。

每一个时钟信号的上升沿,地址发生器的输出地址加 1,地址发生器的输出地址对波形查找表寻址,逐点读出波形数据,经数模转换后生成相应的输出信号。

设可变时钟频率为f S,若周期波形每个周期由 n 个采样点构成。

1.2 DDFS

由于 DDWS 产生新的频率必须通过更改采样时钟的频率或波形存储器中的数据点数来实现,作为振荡器应用具有较大的局限性。

因此提出了如图 2-2 所示基于相位累加器的改进模型,即直接数字频率合成(DDFS)。

DDFS 系统主要由固定时钟发生器、相位累加器、波形查找表、数模转换器和低通滤波器等组成。

在采样时钟的控制下,N 位的相位累加器以频率控制字 K 进行累加,截取高 M 位作为相位地址对波形查找表进行寻址,输出相应的 D 位幅度信息,完成波形相位到幅度的转换。

输出的波形幅度信息通过数模转换器得到相应的模拟信号输出,低通滤波器滤除杂散分量,保证输出波形的纯度。

DDFS 的输出频率f o 和采样时钟f S之间的关系为:

s N o f K f 2

图1-1DDFS原理图

2DDS主要误差来源

2.1相位截断误差

2.1.1相位截断误差产生的原因

由DDFS的原理可知:在采样时钟频率一定时,输出信号的频率分辨率与相位累加器的位数N 成反比。

为了实现较高的频率分辨率,DDS 的相位累加器位数N 非常大,但如果将相位累加器的N 位输出全部用于波形查找表寻址,则需要的波形查找表容量为2N点。

以N 取30 位为例,则需要的波形查找表容量为230=1G 点,目前难以满足。

因此,在实际应用中,通常截取其中高M 位来寻址波形查找表,剩余低N-M 位舍弃不用,从而产生相位截断误差,进而引入输出杂散。

2.1.2相位截断误差的优化方法

针对相位截断误差的改善,相位舍位每减小 1 位,杂散将改善约6dB。

因此,增大波形查找表是一种改善相位截断误差所引起的杂散的最直接方法。

除通过增大波形查找表的容量,有效地降低相位截断误差以外。

针对相位截断误差的周期性,提出了一种对相位累加器输出进行加扰以打破误差信号的周期性消除杂散分量的方法。

输出相位加扰法是在每一个时钟脉冲到来后,通过给相位累加器的输出中加入满足一定统计特性的随机信号来打破误差序列的周期性,从而降低杂散。

其实本质是通过加入具有一定统计特性的扰动信号来打破相位截断误差信号序列的周期性,将周期性的噪声变为相对幅度较低的随机噪声,则可把由周期序列所引起的具有较大幅度的杂散谱线的功率平均分布到较宽的频率范围内,从而改善输出信号频谱的信杂比。

采用输出相位加扰法的双DDS 并行伪插值任意波形合成如图2-1所示。

引入输出数据宽度为N-M 位,输出数据满足均匀分布的扰码发生器,扰码发生器输出的随机相位码与相位累加器输出的相位码相加,相加的结果截断后保留M 位作为波形查找表的地址。

通过加扰后,打破了相位截断误差原有的周期性,是一种有效地降低输出波形杂散的方法。

图2-1具有加扰模块的伪插值任意波形合成原理图

2.2幅度量化误差

在任意波形合成中,由于波形查找表数据位宽和DAC 垂直分辨位数的有限性,在进行波形信号幅度量化的过程中不可避免的存在误差,这个误差叫做幅度量化误差。

针对幅度量化误差,现在存在很多改善误差的方法。

通过对幅度量化杂散信号的频谱特征及能量进行分析,并对幅度舍入方式进行了仿真分析。

从分析可知,量化位数每增加一位,输出信噪比SNR 将提高6dB。

因此,提高DAC 的垂直分辨率能有效的降低幅度量化误差。

同时,如果没有较高分辨力的DAC时,可以采用如图2-2所示的方法,通过较低分辨率的DAC 合成较高分辨率DAC 的方法,能有效的增加DAC 的垂直分辨率。

针对DAC 保持特性所引入的孔径失真及镜像频率干扰,根据DDS输出频谱的特点,可以采用椭圆滤波器进行正弦信号滤波,采用线性相位滤波器进行任意波形信号滤波的方法。

可以很好的对产生的误差进行补偿,同时也可以采用具有反Sinc 特性的滤波器进行DAC 零阶保持误差补偿的方法可以达到和椭圆滤波器相似的作用。

另外值得一提的是,DAC 的非线性误差同样是比较重要的一块内容,针对DAC 非线性误差,人提出了一种平衡DAC DDS 结构,采用两个完全相同的DAC输出相减抵消同相的干扰,可获得10dB 以上的杂散改善。

类似于模拟电路当中的差分电路的原理。

图2-2Block diagram of the linear interpolation

3总结

虽然文章中提到很多误差的来源,但是我们应当注意的是,相位截断误差是比较重要的来源,当存在较大的相位截断误差时,即便拥有很小的幅度量化误差也是没有多大意义的。

所以我们在设计任意波形发生器的时候应当优先考虑降低相位截断,之后在考虑幅度量化误差。

本文只关注于单路DDS 合成误差的分析与校正,对于多路DDS并行合成中的误差来源、误差的特殊性以及合成过程中误差的改善方法并未提及。

这点需要注意,在多路DDS并行时,这些分析于结论都不能保证其正确性。