JTAG接口连接方法

AVR单片机JTAG接口的使用方法

AVR单片机JTAG接口的使用方法AVR单片机JTAG(Joint Test Action Group)接口是一种用于单片机的调试和编程工具。

它提供了一种高效的方式来进行硬件调试、固件编程和软件调试。

在本文中,我将详细介绍AVR单片机JTAG接口的使用方法。

1.JTAG接口简介JTAG接口由四条线组成,分别是TCK(时钟线)、TMS(状态线)、TDI(数据输入线)和TDO(数据输出线)。

它是一种串行接口,用于与其他外设进行通信。

JTAG接口能够通过硬件调试、固件编程和软件调试来提高系统调试的效率。

2.JTAG接口的初始化在使用JTAG接口之前,需要对其进行初始化。

首先,需要确定使用的JTAG接口类型,然后根据类型选择与之匹配的调试工具和软件。

接下来,需要连接JTAG接口的四个引脚到单片机的相应引脚上。

通常,这些引脚在单片机的数据手册中有详细的说明。

3.JTAG接口的连接连接JTAG接口的四个引脚到单片机的相应引脚上,确保连接正确无误。

通常,TCK(时钟线)和TMS(状态线)引脚是共享的,它们分别连接到单片机的相应引脚上。

TDI(数据输入线)和TDO(数据输出线)引脚则是分别连接到单片机的相应引脚上。

请务必根据单片机的数据手册正确连接JTAG接口引脚。

4.JTAG接口的编程在使用JTAG接口进行编程之前,需要确保已经安装了合适的调试工具和软件。

这些工具和软件可以帮助我们完成对单片机的编程操作。

通常,这些工具和软件提供了一些简单的命令和接口,用于与单片机进行通信。

通过这些命令和接口,我们可以读取和写入单片机的内部寄存器,从而实现对单片机的编程操作。

5.JTAG接口的调试使用JTAG接口进行调试可以帮助我们找到系统中的错误和问题。

通过读取和写入单片机的内部寄存器,我们可以查看程序的执行状态、输入和输出数据、栈的使用情况等信息。

通过这些信息,我们可以判断程序中的错误和问题,并进行调试操作。

6.JTAG接口的注意事项在使用JTAG接口之前-确保JTAG接口的引脚连接正确无误,避免引脚连接错误导致的通信问题。

jtag接口是什么

jtag 接口是什么

JTAG(JointTestAcTIonGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG 技术是一种

嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP (TestAccessPort,测试访问口),通过专用的JTAG 测试工具对内部节点进行测试。

如今大多数比较复杂的器件都支持JTAG 协议,如ARM、DSP、FPGA 器件等。

标准的JTAG 接口是4 线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

如今JTAG 接口的连接有两种标准,即14 针接口和20 针接口,其定义分别如下所示。

14 针JTAG 接口

1、13VCC 接电源。

14针与20针jtag接口介绍

JTAG接口定义JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 TAP ( Test Access Port ,测试访问口),通过专用的 J TAG 测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持 JTAG 协议,如 ARM 、 DSP 、 FPGA 器件等。

标准的JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG 测试允许多个器件通过 JTAG 接口串联在一起,形成一个 JTAG 链,能实现对各个器件分别测试。

JTAG 接口还常用于实现 ISP ( In-System Programmable 在系统编程)功能,如对 FLASH器件进行编程等。

通过 JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

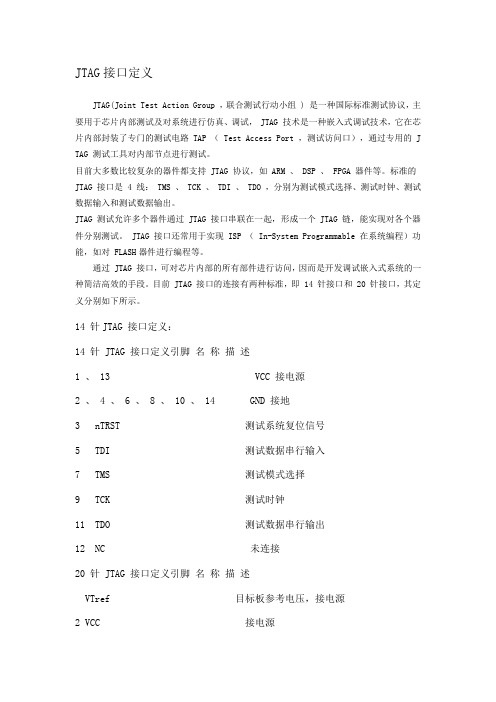

目前 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

14 针JTAG 接口定义:14 针 JTAG 接口定义引脚名称描述1 、 13 VCC 接电源2 、 4 、 6 、 8 、 10 、 14 GND 接地3 nTRST 测试系统复位信号5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 TDO 测试数据串行输出12 NC 未连接20 针 JTAG 接口定义引脚名称描述VTref 目标板参考电压,接电源2 VCC 接电源3 nTRST 测试系统复位信号4、6、8、10、12、14、16、18、20 GND 接地5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 RTCK 测试时钟返回信号13 TDO 测试数据串行输出15 nRESET 目标系统复位信号17 、 19 NC 未连接。

HJ-JTAG仿真器接线与驱动安装教程

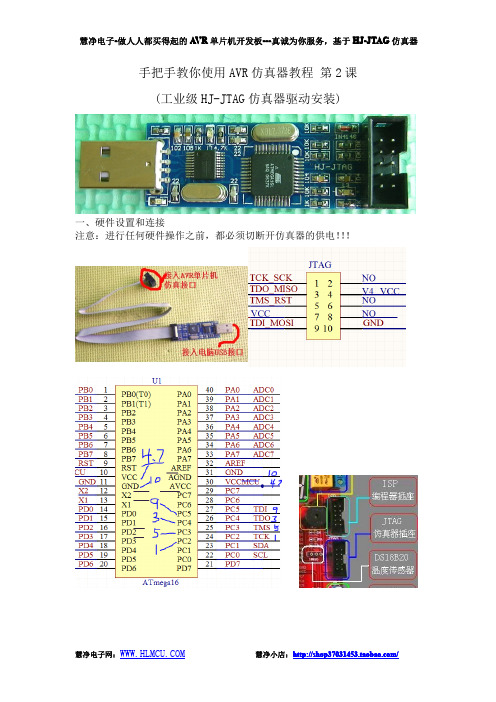

手把手教你使用AVR仿真器教程第2课(工业级HJ-JTAG仿真器驱动安装)一、硬件设置和连接注意:进行任何硬件操作之前,都必须切断开仿真器的供电!!!二、安装USB驱动下面介绍WindowdXP下USB驱动的安装步骤:1、先不要将开发板和电脑用USB电缆连起来。

2、双击HJ-2G配套光盘\驱动程序\\HL-340-XP.EXE,会弹出驱动安装程序的界面,如下图所示:点“INSTALL”按纽,会弹出下图所示的对话框,说明驱动预安装成功:点“确定”按纽,并关闭驱动安装程序。

3、将开发板和电脑用USB电缆连起来。

在弹出的“找到新硬件向导”对话框中,选择自动安装即可,忽略驱动数字签名警告:点“下一步”,安装完成后如下图:按“完成”按纽。

4、在桌面“我的电脑”图标上单击鼠标右键,弹出右键快捷菜单,用鼠标左键单击其中的“属性”,弹出“系统属性”对话框如下:单击“硬件”选项卡后,如下图:单击“设备管理器”按纽后,如下图:单击“端口(COM和LPT)”左边的加号将其展开后,如下图:在上图中,我们可以看到新生的端口:USB-SERIAL CH340,其端口编号为COM5。

在使用USB接口时,实验板的端口号就要选择上述新生的端口!另外,不同的电脑新生的端口有可能不同,因此你必须按上述方法查询实际的新生端口编号!USB-SERIAL CH340左边有红色的叉或黄色的惊叹号,表示驱动安装不不成功,此时,可以先卸载,重新启动电脑,然后按上述方法重新安装。

版权声明:(部分资料图片来源网络)1、本教程为慧净电子会员整理作品,欢迎网上下载、转载、传播、免费共享给各位单片机爱好者!2、该教程可能会存在错误或不当之处,欢迎朋友们指正。

3、未经协商便做出不负责任的恶意评价(中评,差评),视为自动放弃一切售后服务的权利!4、我们的产品收入一部分是赠送给慈善机构的,以免影响到你的善心.大家好,才是真的好(双方好评)。

下面是有缘人看的,谢谢理解善有善报,恶有恶报,不是不报,时候未到。

什么是JTAG及其使用方法

什么是JTAG及其使用方法JTAG(Joint Test Action Group)是一种用于测试和调试电子设备的接口和协议标准。

它最初是由一组芯片制造商于1985年共同开发的,并被广泛应用于各种数字电路和嵌入式系统中。

JTAG可以通过一组标准的测试和调试功能,提供对目标设备内部电路的控制和观察。

JTAG的使用方法包括以下几个方面:1.设备连接:使用JTAG接口连接目标设备和测试设备。

JTAG接口通常由四个线路组成,即TCK(时钟)、TMS(状态机控制)、TDI(数据输入)和TDO(数据输出)。

这些线路通过专门的JTAG连接器或引脚与目标设备连接。

2.设备识别:测试设备通过JTAG接口与目标设备通信,并识别目标设备的类型和功能。

这通常是通过发送一系列特定的指令和信号来实现的。

目标设备需要支持JTAG协议,并在芯片内部集成了JTAG控制逻辑。

3.测试模式:JTAG可以让我们在目标设备的测试模式下运行和测试其内部电路。

在测试模式下,我们可以检查和修改目标设备内部各个电路的状态和数据。

测试模式通常使用状态机来控制目标设备的测试流程。

4.调试功能:JTAG还提供了强大的调试功能,允许工程师监视和控制目标设备的执行过程。

通过JTAG接口,我们可以在目标设备运行的任何时候停止执行,并检查寄存器、内存和其他关键数据。

同时,我们还可以通过JTAG接口修改寄存器和内存中的数据,以调试软件和硬件问题。

5.效能测试:除了测试和调试功能之外,JTAG还可以用于测试目标设备的性能和效能。

通过发送特定的信号和指令,我们可以控制目标设备的工作频率、电压和其他工作参数,以评估其在不同工作条件下的性能。

需要注意的是,JTAG只是一个接口标准和协议,而实现JTAG功能的具体硬件和软件可能因厂商和设备类型而有所差异。

因此,在实际使用JTAG之前,我们需要了解目标设备的JTAG接口规格和支持的JTAG功能。

总之,JTAG是一种强大而灵活的测试和调试接口,它能够帮助我们识别和解决各种硬件和软件问题。

fpga jtag手册

fpga jtag手册

FPGA JTAG接口是一种串行接口,用于对FPGA内部逻辑进行调试、配置和测试等功能。

以下是FPGA JTAG接口的基本使用手册:

连接方式:将JTAG电缆的一端连接到FPGA开发板上的JTAG接口,另一端连接到PC上的JTAG调试器。

确保连接稳定,避免在调试过程中出现断线或接触不良的情况。

配置JTAG接口:在开始调试之前,需要配置JTAG接口的参数,例如波特率、数据位、停止位等。

这些参数需要根据目标FPGA设备和JTAG调试器的要求进行设置。

启动调试:打开JTAG调试器软件,选择正确的设备型号和连接方式,然后点击“开始调试”按钮。

此时,调试器将与目标FPGA建立通信连接,并进入调试状态。

加载配置文件:在调试过程中,可能需要将配置文件加载到目标FPGA中。

可以通过JTAG接口将配置文件传输到目标FPGA中,或者在调试器软件中选择相应的配置文件进行加载。

运行和停止调试:在调试过程中,可以通过调试器软件控制目标FPGA的运行和停止。

可以单步执行、步进执行或全速运行目标FPGA的程序。

同时,还可以在调试过程中设置断点、观察寄存器和内存等操作。

结束调试:当调试完成后,可以通过调试器软件结束调试会话,并关闭JTAG接口的连接。

需要注意的是,使用FPGA JTAG接口进行调试需要一定的技术背景和经验。

在调试过程中,需要仔细检查连接线和设备参数设置,避免出现通信错误或配置错误等问题。

同时,也需要遵守相关的安全操作规程,确保不会损坏目标FPGA 或造成其他安全问题。

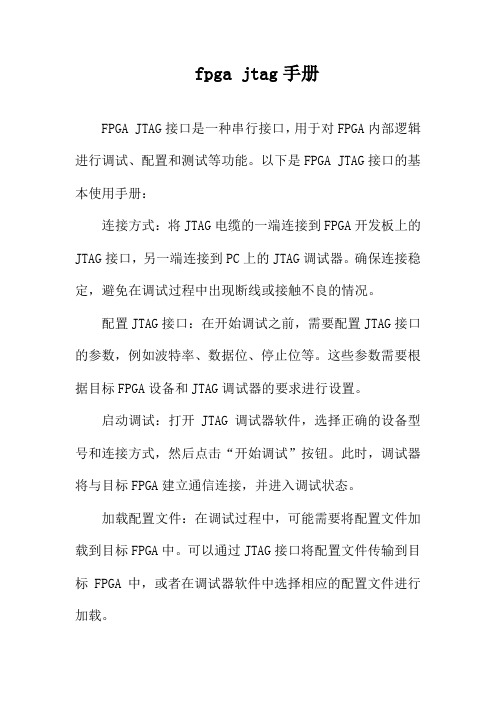

JTAG各类接口针脚定义

JTAG各类接口针脚定义

由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。

但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。

对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

20、14、10pin JTAG的引脚名称与序号对应关系

上述Jtag头的管脚名称是对IC而言的。

例如TDI脚,表示该脚应该与IC上的TDI脚相连,而不是表示数据从该脚进入download cable。

实际上10针的只需要接4根线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接。

[整理]atmel官方jtagisp(6-10pin)口接口标准

![[整理]atmel官方jtagisp(6-10pin)口接口标准](https://img.taocdn.com/s3/m/d75dc2c3370cba1aa8114431b90d6c85ec3a8812.png)

仿真器调试器A VR_JTAGICE和编程器A VR_ISP的接口标准· 与目标板的连接接口:- ATMEL官方ISP_10PIN标准接口;- ATMEL官方ISP_6PIN标准接口(使用配套的彩色连接线)OK,那么,怎么使用它连接目标板进行下载编程、仿真调试呢?使用调试器引出的10PIN连接线连接目标板与调试器就可以了。

下面是调试器的接口标准:说明:接口图打“剪刀”的表示仿真器接口该引脚无对外输出,所以目标板该引脚可接可不接!6PIN 转 10PIN 转接线 2条:从上面的接口图可以看出:该ISP接口兼容ATMEL指定的ISP_10PIN接口;兼容,但作了以下改进,它与ATMEL官方标准的区别在于:不输出 ISP 的PIN4 “GND” ,它对应 JTAG 的 PIN4 为“ VCC ”;这样,若您的目标板采用官方标准接口依然可以正常连接,但改进后,带来以下优点:ISP错插入MCU的JTAG接口,不会导致烧器件。

(需要目标板的ISP接口、JTAG接口也做相同处理,才可真正避免错插接口不烧毁器件!)(1)配送10PIN连接线,用于连接该调试器与目标板的JTAG接口(2)配送6PIN连接线,用于连接该调试器与目标板的ISP接口(3)配送的ISP_6PIN转ISP_10PIN连接线,用于将调试器的ISP_6PIN转ISP_10PIN:如何连接调试器与目标板的JTAG接口(ATMEL指定的JTAG标准接口)?:使用调试器引出的10PIN连接线直接连接目标板即可。

方位说明: 10PIN连接线的红线为PIN1(TCK)。

:如何连接调试器与目标板的ISP_10PIN接口(ATMEL指定的ISP_10PIN标准接口)?:使用调试器引出的10PIN连接线直接连接目标板即可。

方位说明:ISP_10PIN连接线的红线为PIN1。

:如何连接调试器与目标板的ISP_6PIN接口(ATMEL指定的ISP_6PIN标准接口)?:使用我们配套的转换彩线连接目标板即可。

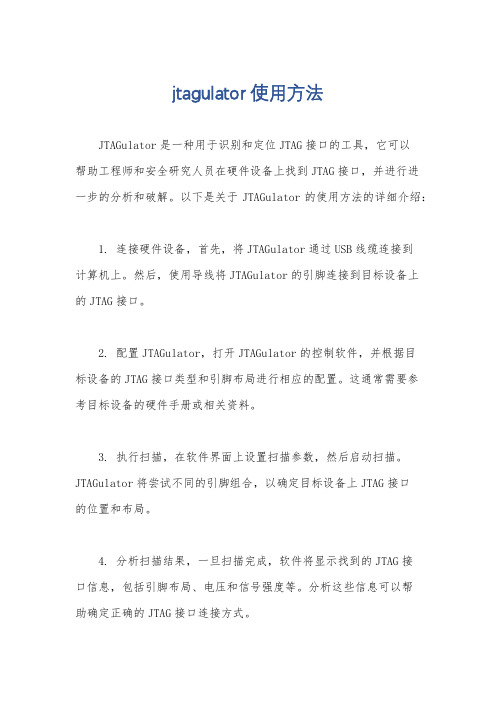

jtagulator使用方法

jtagulator使用方法

JTAGulator是一种用于识别和定位JTAG接口的工具,它可以

帮助工程师和安全研究人员在硬件设备上找到JTAG接口,并进行进

一步的分析和破解。

以下是关于JTAGulator的使用方法的详细介绍:

1. 连接硬件设备,首先,将JTAGulator通过USB线缆连接到

计算机上。

然后,使用导线将JTAGulator的引脚连接到目标设备上

的JTAG接口。

2. 配置JTAGulator,打开JTAGulator的控制软件,并根据目

标设备的JTAG接口类型和引脚布局进行相应的配置。

这通常需要参

考目标设备的硬件手册或相关资料。

3. 执行扫描,在软件界面上设置扫描参数,然后启动扫描。

JTAGulator将尝试不同的引脚组合,以确定目标设备上JTAG接口

的位置和布局。

4. 分析扫描结果,一旦扫描完成,软件将显示找到的JTAG接

口信息,包括引脚布局、电压和信号强度等。

分析这些信息可以帮

助确定正确的JTAG接口连接方式。

5. 进行进一步的研究,一旦JTAG接口被确定,可以使用JTAGulator或其他工具进行后续的JTAG调试、固件破解或安全分析工作。

除了上述步骤,使用JTAGulator还需要对硬件设备和JTAG接口有一定的了解,以便正确地配置和解释扫描结果。

此外,还需要谨慎操作,以避免对目标设备造成损坏。

总而言之,JTAGulator是一款强大的工具,可以帮助用户快速而准确地定位JTAG接口,但使用时需要谨慎并且需要一定的硬件和JTAG知识作为基础。

ARM系统设计JTAG接口详细图解

ARM系统设计JTAG接口详细图解ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表1 JTAG引脚说明序号信号名方向说明1 Vref Input 接口电平参考电压,通常可直接接电源2 Vsupply Input 电源3 nTRST Output (可选项) JTAG复位。

在目标端应加适当的上拉电阻以防止误触发。

4 GND -- 接地5 TDI Output Test Data In from Dragon-ICE to target.6 GND -- 接地7 TMS Output Test Mode Select8 GND -- 接地9 TCK Output Test Clock output from Dragon-ICE to the target10 GND -- 接地11 RTCK Input (可选项) Return Test Clock。

由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。

不使用时可以直接接地。

12 GND -- 接地13 TDO Input Test Data Out from target to Dragon-ICE.14 GND -- 接地15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。

可以直接对目标系统复位,同时可以检测目标系统的复位情况。

为了防止误触发,应在目标端加上适当的上拉电阻。

16 GND -- 接地17 NC保留18 GND -- 接地19 NC -- 保留20 GND -- 接地2.目标系统如何设计?目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。

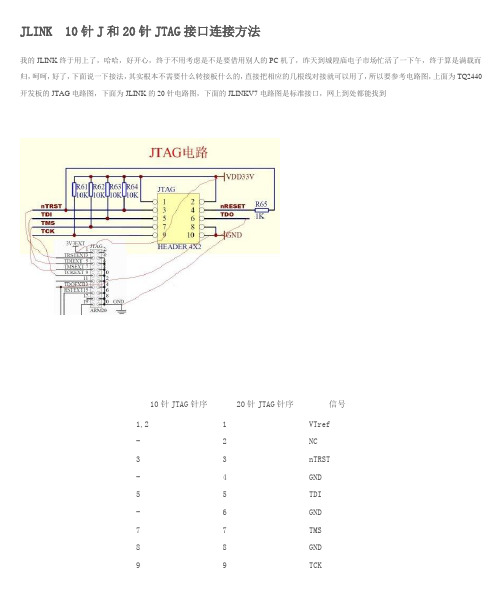

JLINK 10针J和20针JTAG接口连接方法

JLINK 10针J和20针JTAG接口连接方法我的JLINK终于用上了,哈哈,好开心,终于不用考虑是不是要借用别人的PC机了,昨天到城隍庙电子市场忙活了一下午,终于算是满载而归,呵呵,好了,下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到10针JTAG针序20针JTAG针序信号1,2 1 VTref- 2 NC3 3 nTRST- 4 GND5 5 TDI- 6 GND7 7 TMS8 8 GND9 9 TCK10 10 GND- 11 RTCK- 12 GND6 13 TDO- 14 GND4 15 RESET- 16 GND- 17 DBGRQ- 18 GND- 19 5V-Supply- 20 GND实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接关于JTAG 20PIN转10PIN的问题JTAG请问J_LINK的20PIN与2440开发板的10PIN之间(左半图为2440,右半图为JLINK)应该怎么接?这样可以么?1,2 VD3.3(左)- 1 VTref(右)3 nTRST(左)- 3 nTRST(右)5 TDI(左)- 5 TDI(右)7 TMS(左)- 7 TMS(右)9 TCK(左)- 9 TCK(右)6 TDO(左)- 13 TDO(右)4 nREST(左)- 15 nSRST(右)8,10 -GND电源、地加 4根关键信号:5 TDI(左)- 5 TDI(右)7 TMS(左)- 7 TMS(右)9 TCK(左)- 9 TCK(右)6 TDO(左)- 13 TDO(右)别接错就可以了 TRST 和NRST不一定需要接按照你说的,已经能正常的工作了,感谢~~~/s/blog_40aad2950100fts8.html。

JTAG接口的定义及常见问题

JTAG接口的定义及常见问题ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM 系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表 1 JTAG引脚说明序号信号名方向说明1 Vref Input 接口电平参考电压,通常可直接接电源2 Vsupply Input 电源3 nTRST Output (可选项) JTAG复位。

在目标端应加适当的上拉电阻以防止误触发。

4 GND -- 接地5 TDI Output Test Data In from Dragon-ICE to target.6 GND -- 接地7 TMS Output Test Mode Select8 GND -- 接地9 TCK Output Test Clock output from Dragon-ICE to the target10 GND -- 接地11 RTCK Input (可选项) Return Test Clock。

由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。

不使用时可以直接接地。

12 GND -- 接地13 TDO Input Test Data Out from target to Dragon-ICE.14 GND -- 接地15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。

可以直接对目标系统复位,同时可以检测目标系统的复位情况。

为了防止误触发,应在目标端加上适当的上拉电阻。

16 GND -- 接地17 NC -- 保留18 GND -- 接地19 NC -- 保留20 GND -- 接地2.目标系统如何设计?目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。

TMS320C6678JTAG硬件设计知识点整理

TMS320C6678JTAG硬件设计知识点整理TMS320C6678是德州仪器(Texas Instruments)推出的一款高性能数字信号处理器(DSP)芯片。

JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

在设计TMS320C6678 JTAG硬件时,需要考虑以下几个关键知识点。

1.JTAG接口电路设计:JTAG接口电路是连接芯片和JTAG调试器(如调试工具、编程器等)之间的桥梁。

设计JTAG接口电路时,需要根据芯片的引脚定义和JTAG标准进行连接,并确保电路兼容芯片的电气特性和信号传输要求。

2.JTAG信号定义:JTAG接口通常包括多个信号线,如TCK(时钟)、TMS(状态机选择)、TDO(输出)和TDI(输入)等。

在设计JTAG硬件时,需要了解这些信号的作用和使用方法,确保正确连接和操作。

3.JTAG调试功能设计:JTAG接口可以用于芯片的调试和测试。

为了实现这些功能,需要在JTAG硬件中添加对应的功能模块,如调试逻辑电路、状态机等。

此外,还可以考虑添加其他辅助功能,如电源管理、时钟控制等,以提高系统性能和可靠性。

4.JTAG连接方式:在实际应用中,JTAG接口可以通过多种方式进行连接,如直接连接、串行接口、并行接口等。

设计JTAG硬件时,需要选择合适的连接方式,考虑到系统的复杂性、可扩展性和成本等因素。

5. JTAG测试和调试技术:JTAG接口不仅可以用于测试集成电路的功能和性能,还可以用于调试芯片的软件程序。

在设计JTAG硬件时,需要了解和掌握相关的测试和调试技术,如扫描链(Scan Chain)测试、边界扫描(Boundary Scan)测试、故障模式和影响分析(FMEA)等。

6.JTAG仿真和验证:在设计JTAG硬件之前,可以使用仿真工具对设计方案进行验证和优化。

通过仿真可以检查JTAG接口的功能和性能,发现并解决可能存在的问题,确保设计符合相关的规范和标准。

jtag各类接口针脚定义含义以及swd接线方式

JTAG各类接口针脚定义、含义以及SWD接线方式JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义Test Clock Input (TCK) -----强制要求1TCK在IEEE1149.1标准里是强制要求的。

TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2TMS信号在TCK的上升沿有效。

TMS在IEEE1149.1标准里是强制要求的。

TMS信号用来控制TAP状态机的转换。

通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3TDI在IEEE1149.1标准里是强制要求的。

TDI是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4TDO在IEEE1149.1标准里是强制要求的。

TDO是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAPController进行复位(初始化)。

因为通过TMS也可以对TAP Controll进行复位(初始化)。

所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)Return Test Clock ( RTCK) ----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK 信号的产生,不使用时直接接地。

msp430JTAG接法

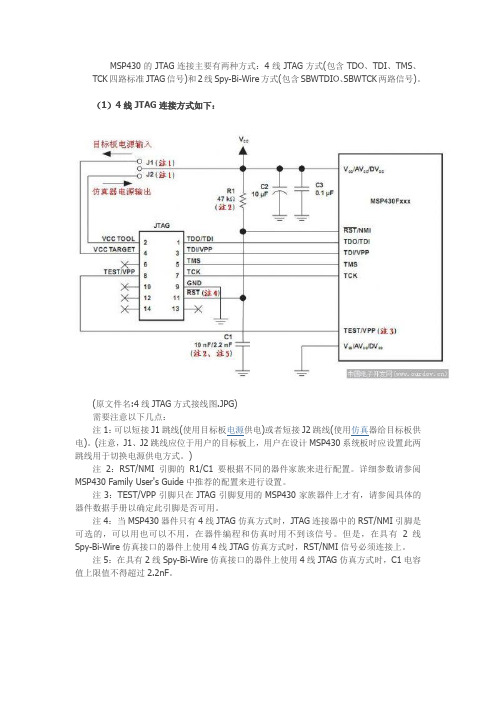

MSP430的JTAG连接主要有两种方式:4线JTAG方式(包含TDO、TDI、TMS、TCK四路标准JTAG信号)和2线Spy-Bi-Wire方式(包含SBWTDIO、SBWTCK两路信号)。

(1)4线JTAG连接方式如下:(原文件名:4线JTAG方式接线图.JPG)需要注意以下几点:注1:可以短接J1跳线(使用目标板电源供电)或者短接J2跳线(使用仿真器给目标板供电)。

(注意,J1、J2跳线应位于用户的目标板上,用户在设计MSP430系统板时应设置此两跳线用于切换电源供电方式。

)注2:RST/NMI引脚的R1/C1要根据不同的器件家族来进行配置。

详细参数请参阅MSP430 Family User's Guide中推荐的配置来进行设置。

注3:TEST/VPP引脚只在JTAG引脚复用的MSP430家族器件上才有,请参阅具体的器件数据手册以确定此引脚是否可用。

注4:当MSP430器件只有4线JTAG仿真方式时,JTAG连接器中的RST/NMI引脚是可选的,可以用也可以不用,在器件编程和仿真时用不到该信号。

但是,在具有2线Spy-Bi-Wire仿真接口的器件上使用4线JTAG仿真方式时,RST/NMI信号必须连接上。

注5:在具有2线Spy-Bi-Wire仿真接口的器件上使用4线JTAG仿真方式时,C1电容值上限值不得超过2.2nF。

(2) 2线Spy-Bi-Wire JTAG连接方式如下:(原文件名:2线Spy-Bi-Wire连接方式接线图.JPG)需要注意以下几点:注1:可以短接J1跳线(使用目标板电源供电)或者短接J2跳线(使用仿真器给目标板供电)。

(注意,J1、J2跳线应位于用户的目标板上,用户在设计MSP430系统板时应设置此两跳线用于切换电源供电方式。

)注2:注意器件的RST/NMI引脚在2线Spy-Bi-Wire仿真方式时是用作双向Debug调试数据通信接口,因此,该引脚上的电容将会影响仿真器与器件建立仿真链路的能力,在使用MSP430UIF时,C1电容值上限值为2.2nF。

JTAG接口

在Debug模式下,ARM内核的时钟从系统的主时钟 (MCLK)被替换成跟踪时钟(DCLK)。

跟踪时钟(DCLK)是通过在JTAG的状态机的 Run-test/Idle状态的TCK来控制的。

28

3.4.7 ARM7TDMI断点的设置

横 向

I2

0 X0

I 待测装置 O

0 X0

Pin

Logic

Logic

O1

Pin

O2

Pin

I3

Pin

0 X0

I

Logic

输入数据 输出数据

TCK TDI

101010

扫描前的输入数据

O

Logic

0 X0

O3

Pin

TDO

XXXXXX

扫描后的输出数据

18

JTAG处于挂起状态

I1

1 X1

DUT

0 X0

O1

(测试器件)

29

硬件断点和软件断点

在ARM7TDMI处理器的内核中,有两种断点的设置方式: 硬件断点和软件断点

硬件断点 通过设置EmbeddedICE中的Watchpoint寄存器中的地 址相关的寄存器,来实现断点。 通过这种方式设置断点,断点数目受EmbeddedICE中 的Watchpoint数目的限制(在ARM7TDMI处理器的内 核中,只有两组Watchpoint寄存器,最多只能设置两 个硬件断点)。 硬件断点可以在任何地方设置。不受存储器类型的限 制。

Channel)。

26

Watchpoint寄存器的使用

EmbeddedICE的一个主要作用就是可以在ARM的程序 中设置软件或者硬件的断点。

pickit jtag口接法

pickit是一种用于外部编程和调试微处理器的工具,它通过jtag接口与微处理器通信。

在使用pickit进行jtag口接法时,需要按照以下步骤进行操作:1. 准备工作在进行jtag口接法之前,首先需要准备好必要的工具和材料,包括pickit工具、jtag接口线、目标开发板或目标器件等。

2. 连接jtag接口线将jtag接口线的一端连接到pickit工具的jtag接口,另一端连接到目标开发板或目标器件上的jtag接口。

确保接线正确无误,并牢固连接。

3. 连接目标器件将pickit工具与目标器件通过jtag接口线连接起来,确保连接稳定可靠。

4. 软件设置在进行jtag口接法之前,需要在相关的编程和调试软件中进行相应的设置。

根据具体的开发环境和目标器件的类型,设置相应的通信参数和配置信息。

5. 烧录和调试完成jtag口接法之后,可以通过pickit工具进行目标器件的烧录和调试工作。

根据具体的需求,选择相应的烧录和调试操作,并进行相应的设置和参数调整。

通过以上步骤,就可以实现pickit工具与目标器件之间的jtag口接法,从而进行外部编程和调试工作。

在实际操作中,需要注意接线的正确性、软件设置的准确性以及操作的规范性,以确保整个过程顺利进行,并取得良好的烧录和调试效果。

总结起来,pickit jtag口接法是一项重要的工作,它涉及到硬件连接和软件设置等多个方面,需要系统地进行规划和操作。

只有在严格遵循相关步骤和要求的情况下,才能有效地使用pickit工具进行jtag口接法,从而实现对目标器件的编程和调试工作。

第一步 - 准备工作扩展:在进行jtag码口接法之前,需要进行充分的准备工作。

首先要确保所使用的pickit工具是经过认证和检测的正品,以免造成不必要的安全隐患。

还需要对jtag接口线和目标开发板或目标器件进行检查,确保它们的品质和连接接口的兼容性。

如果接口线或开发板存在损坏或不匹配的情况,可能会导致jtag口接法失败或者在编程调试过程中出现异常,影响开发工作的进行。

JTAGICE连接说明

请参阅 A VR Studio 软件帮助内 JTAGICE 的详细使用说明。

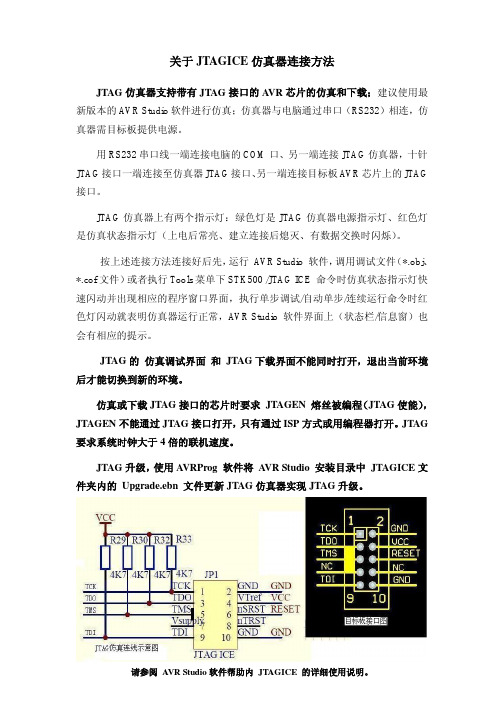

关于JTAGICE 仿真器连接方法

JTAG 仿真器支持带有JTAG 接口的A VR 芯片的仿真和下载;建议使用最新版本的A VR Studio 软件进行仿真;仿真器与电脑通过串口(RS232)相连,仿真器需目标板提供电源。

用RS232串口线一端连接电脑的COM 口、另一端连接JTAG 仿真器,十针JTAG 接口一端连接至仿真器JTAG 接口、另一端连接目标板A VR 芯片上的JTAG 接口。

JTAG 仿真器上有两个指示灯:绿色灯是JTAG 仿真器电源指示灯、红色灯是仿真状态指示灯(上电后常亮、建立连接后熄灭、有数据交换时闪烁)。

按上述连接方法连接好后先,运行 A VR Studio 软件,调用调试文件(*.obj 、*.cof 文件)或者执行Tools 菜单下STK500 /JTAG ICE 命令时仿真状态指示灯快速闪动并出现相应的程序窗口界面,执行单步调试/自动单步/连续运行命令时红色灯闪动就表明仿真器运行正常,A VR Studio 软件界面上(状态栏/信息窗)也会有相应的提示。

JTAG 的 仿真调试界面 和 JTAG 下载界面不能同时打开,退出当前环境后才能切换到新的环境。

仿真或下载JTAG 接口的芯片时要求 JTAGEN 熔丝被编程(JTAG 使能),JTAGEN 不能通过JTAG 接口打开,只有通过ISP 方式或用编程器打开。

JTAG 要求系统时钟大于4倍的联机速度。

JTAG 升级,使用A VRProg 软件将 A VR Studio 安装目录中 JTAGICE 文件夹内的 Upgrade.ebn 文件更新JTAG 仿真器实现JTAG 升级。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

我的JLINK终于用上了,哈哈,好开心,终于不用考虑是不是要借用别人的PC 机了,昨天到城隍庙电子市场忙活了一下午,终于算是满载而归,呵呵,好了,下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到

10针JTAG针序20针JTAG针序信号

1,21VTref

-2NC

33nTRST

-4GND

55TDI

-6GND

77TMS

88GND

99TCK

1010GND

-11RTCK

-12GND

613TDO

-14GND

415RESET

-16GND

-17DBGRQ

-18GND

-195V-Supply

-20GND

实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接

ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?

下图是JTAG接口的信号排列示意:

接口是一个20脚的IDC插座。

下表给出了具体的信号说明:

表 1 JTAG引脚说明

序号信号名方向说明

1 Vref Input 接口电平参考电压,通常可直接接电源

2 Vsupply Input 电源

3 nTRST Output (可选项) JTAG复位。

在目标端应加适当的上拉电阻以防止误触发。

4 GND -- 接地

5 TDI Output Test Data In from Dragon-ICE to target.

6 GND -- 接地

7 TMS Output Test Mode Select

8 GND -- 接地

9 TCK Output Test Clock output from Dragon-ICE to the target

10 GND -- 接地

11 RTCK Input (可选项) Return Test Clock。

由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。

不使用时可以直接接地。

12 GND -- 接地

13 TDO Input Test Data Out from target to Dragon-ICE.

14 GND -- 接地

15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。

可以直接对目标系统复位,同时可以检测目标系统的复位情况。

为了防止误触发,应在目标端加上适当的上拉电阻。

16 GND -- 接地

17 NC -- 保留

18 GND -- 接地

19 NC -- 保留

20 GND -- 接地

2.目标系统如何设计?

目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。

RTCK和nTRST这两个信号根据目标ASIC有否提供对应的引脚来选用。

nSRST则根据目标系统的设计考虑来选择使用。

下面是一个典型的连接关系图:

复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。

如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。

后面给出了一种电路方案的效果图。

图3一个复位电路结构的例子

在目标系统的PCB设计中,最好把JTAG接口放置得离目标ASIC近一些,如果这两者之间的连线过长,会影响JTAG口的通信速率。

另外电源的连线也需要加以额外考虑,因为Dragon-ICE要从目标板上吸取超过100mA 的大电流。

最好能有专门的敷铜层来供电,假如只能使用连线供电的话,最小线宽不应小于10mil (0.254mm)。

3. 14脚JTAG如何与20JTAG连接?

Dragon-ICE使用工业标准的20脚JTAG插头,但是有些老的系统采用一种14脚的插座。

这两类接口的信号排列如下:

这两类接口之间的信号电气特性都是一样的,因此可以把对应的信号直接连起来进行转接。

Dragon-ICE配备这种转接卡,随机配备。

原文出处:/faq2.htm。