EDA考试试卷

2014-2015第一学期EDA技术上机考试试题A卷

南昌大学2014-2015年EDA技术上机测试卷A说明 1、建议每做完一部分立刻保存文件。

2、软件可能出现异常,如不能添加元件库或元件不能旋转等,此时应先保存文件,然后关闭软件再重新打开,一般都能消除异常。

一、电路如图所示,试画出它的原理图,并按要求设计电路板。

要求:1、新建文件夹,不要放在C 盘。

文件夹名称为: 学号+姓名然后在该文件下新建设计数据库(姓名+学号.ddb)。

2、新建原理图文件,文件名字为学号.sch。

1) 原理图纸张类型和标题栏的设置:原理图纸为B 号,无标题栏。

2) 按下图画出原理图,一定要保证原理图的正确。

并给元件填上封装、编号等其它属性。

3)网络标号uo 的字体:Times New Roman,字形:斜体,大小:18。

元件属性设置见下表:注:U1-U3可在操作界面中查找元件对话框中找到,其他都在默认元件库中。

3、画好图后1)进行ERC 2)做元件表 3)做网络表4PCB 文件1)使用向导建立矩形双面板①板框尺寸为,宽5000mil,高3000mil,只保留尺寸线标注②采用插针式元件③镀铜过孔④焊盘之间允许走一根铜膜线。

2)设计规则一般铜膜线走线宽度20 mil,地线的铜膜线宽度为40mil。

3)人工布置元件,自动布线。

二、评分标准参考如下1、设计数据库文件的命名及存储路径--------------(2)分2、原理图--------------------------------------(40)分3、 ERC 检查------------------------------------(8)分4、元件表--------------------------------------(10)分5、网络表--------------------------------------(10)分6、 PCB-----------------------------------------(30)分。

EDA技术EDA技术试卷(练习题库)(2023版)

EDA技术EDA技术试卷(练习题库)1、个项目的输入输出端口是定义在()。

2、描述项目具有逻辑功能的是()。

3、关键字ARCHITECTURE定义的是。

4、M AXP1USII中编译VHD1源程序时要求()。

5、1987标准的VHD1语言对大小写是()。

6、关于1987标准的VHD1语言中,标识符描述正确的是()。

7、符合1987VHD1标准的标识符是()。

8、VHD1语言中变量定义的位置是()。

9、VHD1语言中信号定义的位置是()。

10、变量是局部量可以写在()。

11、变量和信号的描述正确的是()。

12、关于VHD1数据类型,正确的是()。

13、下面数据中属于实数的是()。

14、下面数据中属于位矢量的是()。

15、可以不必声明而直接引用的数据类型是()。

16、STD_10GIG_1164中定义的高阻是字符()。

17、STD_10GIG」164中字符H定义的是()。

18、使用STD_1OG1G」164使用的数据类型时()。

19、VHD1运算符优先级的说法正确的是()。

20、如果a=1,b=0,则逻辑表达式(aANDb)OR(NOTbANDa)的值是()。

21、不属于顺序语句的是()。

22、正确给变量X赋值的语句是()。

23、EDA的中文含义是()。

24、EPF10K20TC144-4具有多少个管脚()。

25、如果a=1,b=1,则逻辑表达式(aXORb)OR(NOTbANDa)的值是()。

26、MAX+P1USII的,数据类型为std_1ogic_vector,试指出下面那个30、在一个VHD1,数据类型为integer,数据范围0to127,下面哪个赋31、下列那个流程是正确的基于EDA软件的FPGA/CP1D和变量的说法,哪一个是不正确的:()。

33、下列语句中,不属于并行语句的是:()。

34、O在EDA工具中,能将硬件描述语言转换为硬件电路的重要工具软件称为。

35、不是操作符号它只相当与作用〃target=Zb1ank〃>在VHD1的CASE语句中,条件句中的“二>”不是操作符号,它只相当与O作用。

EDA期末考试试卷及答案(word文档良心出品)

密 封 线 内 不 得 答题班级 学号姓名赣 南 师 范 学 院2010—2011学年第一学期期末考试试卷(A 卷)(闭卷)年级 2008 专业 电子科学与技术 (本)课程名称 EDA 技术基础2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线;3、答题请用蓝、黑钢笔或圆珠笔。

一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 BA .适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件B .适配所选定的目标器件可以不属于原综合器指定的目标器件系列C .适配完成后可以利用适配所产生的仿真文件作精确的时序仿真D .通常,EDAL 软件中的综合器可由专业的第三方EDA 公司提供,而适配器则需由FPGA/CPLD 供应商提供2.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。

A .器件外部特性B .器件的综合约束C .器件外部特性与内部功能D .器件的内部功能 3.下列标识符中, B 是不合法的标识符。

A .State0B .9moonC .Not_Ack_0D .signall 4.以下工具中属于FPGA/CPLD 集成化开发工具的是 DA .ModelSimB .Synplify ProC .MATLABD .QuartusII5.进程中的变量赋值语句,其变量更新是 A 。

A .立即完成B .按顺序完成C .在进程的最后完成D .都不对 6.以下关于CASE 语句描述中错误的是 AA .CASE 语句执行中可以不必选中所列条件名的一条B .除非所有条件句的选择值能完整覆盖CASE 语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>”C .CASE 语句中的选择值只能出现一次D . WHEN 条件句中的选择值或标识符所代表的值必须在表达式的取值范围7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A .STD_LOGIC_ARITHB .STD_LOGIC_1164C .STD_LOGIC_UNSIGNEDD .STD_LOGIC_SIGNED 8.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→ A →综合→适配→时序仿真→编程下载→硬件测试。

EDA试题

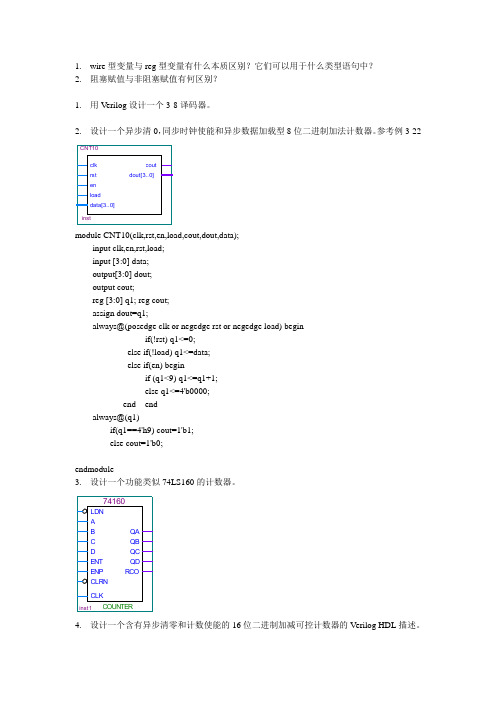

1.wire型变量与reg型变量有什么本质区别?它们可以用于什么类型语句中?2.阻塞赋值与非阻塞赋值有何区别?1.用Verilog设计一个3-8译码器。

2.设计一个异步清0,同步时钟使能和异步数据加载型8位二进制加法计数器。

参考例3-22module CNT10(clk,rst,en,load,cout,dout,data);input clk,en,rst,load;input [3:0] data;output[3:0] dout;output cout;reg [3:0] q1; reg cout;assign dout=q1;always@(posedge clk or negedge rst or negedge load) beginif(!rst) q1<=0;else if(!load) q1<=data;else if(en) beginif (q1<9) q1<=q1+1;else q1<=4'b0000;end endalways@(q1)if(q1==4'h9) cout=1'b1;else cout=1'b0;endmodule3.设计一个功能类似74LS160的计数器。

4.设计一个含有异步清零和计数使能的16位二进制加减可控计数器的Verilog HDL描述。

5.设计七人表决器。

module voter7(pass,vote);output pass;input [6:0] vote;reg pass;reg [2:0] sum;always @(vote)beginsum=0;if(vote[0]==1) sum=sum+1'b1;if(vote[1]==1) sum=sum+1'b1;if(vote[2]==1) sum=sum+1'b1;if(vote[3]==1) sum=sum+1'b1;if(vote[4]==1) sum=sum+1'b1;if(vote[5]==1) sum=sum+1'b1;if(vote[6]==1) sum=sum+1'b1;if(sum[2]) pass=0; //若超过4人赞成,则pass=0,LED1亮else pass=1;endendmoduleAltera Xilinx一、填空题(10分,每小题1分)1.用EDA技术进行电子系统设计的目标最终完成 ASIC 的设计与实现。

2021考研复习桂林电子科技大学信息与通信学院 2016硕士研究生入学考试复试试卷208通信电子电路及EDA技术A

(1)画出交流等效电路;

(2)说明振荡器的类型以及振荡器振荡的条件;

(3)计算振荡频率 fs ;

(4)计算反馈系数 F。

EC

Rb1

Rc

Cb

Rb2

Re

Ce

C1 C3

C2 L

3. 某 FM 调 制 器 的 调 制 灵 敏 度 k f 5kHz/V , 调 制 信 号 u (t) 2 cos(2 2000t) , 载 波 uc (t) 10 cos(4 106 t) 。试求:

考研复习

真题讲解

桂林电子科技大学 2016 硕士研究生入学考试复试试卷

考试科目代码 208 考试科目名称:通信电子电路及 EDA 技术 A

请注意:答案必须写在答题纸上(写在试卷上无效)。

通信电子电路

一、填空题(每空1分,共14分)

1. 理想的LC谐振回路的矩形系数是

,单LC谐振回路的矩形系数

是

。

2. 设丙类高频功放开始工作于临界工作状态,则:单独增大集电极直流电源电压Ec(其

uAM (t)

cos o t

6. 已 知 调 制 信 号 为 u (t) U cos 2 103t , 调 相 指 数 mp 10 , 此 时 PM 波 的 带 宽 是

kHz。若

U 、调制信号频率F增大一倍,此时PM波的带宽变为

7. 锁相环路包含

、

和鉴相器。

kHz。

二、计算题(每题12分,共36分)

begin

case(C_ST)

S0: begin COMOUT<= ⑶ ;

共 4页

第3 页

请注意:答案必须写在答题纸上(写在试卷上无效)。

if (SINPUT= = ⑷ ) NEXT_STATE<= ⑸ ; else if(SINPUT= = ⑹ ) NEXT_STATE<= ⑺ ; else NEXT_STATE<= ⑻ ; end

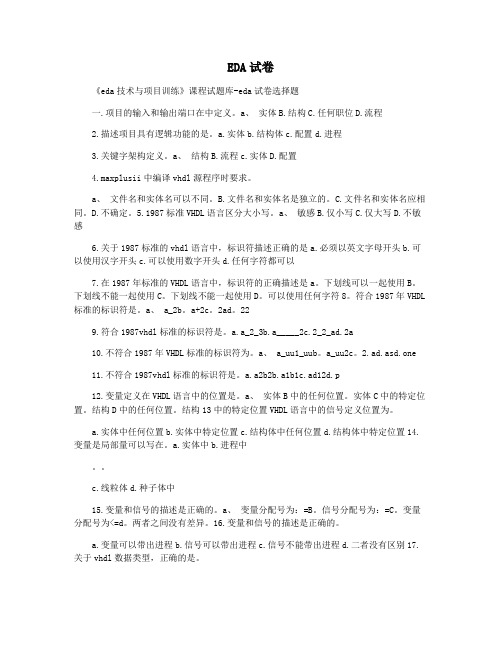

EDA试卷

EDA试卷《eda技术与项目训练》课程试题库-eda试卷选择题一.项目的输入和输出端口在中定义。

a、实体B.结构C.任何职位D.流程2.描述项目具有逻辑功能的是。

a.实体b.结构体c.配置d.进程3.关键字架构定义。

a、结构B.流程c.实体D.配置4.maxplusii中编译vhdl源程序时要求。

a、文件名和实体名可以不同。

B.文件名和实体名是独立的。

C.文件名和实体名应相同。

D.不确定。

5.1987标准VHDL语言区分大小写。

a、敏感B.仅小写C.仅大写D.不敏感6.关于1987标准的vhdl语言中,标识符描述正确的是a.必须以英文字母开头b.可以使用汉字开头c.可以使用数字开头d.任何字符都可以7.在1987年标准的VHDL语言中,标识符的正确描述是a。

下划线可以一起使用B。

下划线不能一起使用C。

下划线不能一起使用D。

可以使用任何字符8。

符合1987年VHDL 标准的标识符是。

a、 a_2b。

a+2c。

2ad。

229.符合1987vhdl标准的标识符是。

a.a_2_3b.a_____2c.2_2_ad.2a10.不符合1987年VHDL标准的标识符为。

a、 a_uu1_uub。

a_uu2c。

2.ad.asd.one11.不符合1987vhdl标准的标识符是。

a.a2b2b.a1b1c.ad12d.p12.变量定义在VHDL语言中的位置是。

a、实体B中的任何位置。

实体C中的特定位置。

结构D中的任何位置。

结构13中的特定位置VHDL语言中的信号定义位置为。

a.实体中任何位置b.实体中特定位置c.结构体中任何位置d.结构体中特定位置14.变量是局部量可以写在。

a.实体中b.进程中。

c.线粒体d.种子体中15.变量和信号的描述是正确的。

a、变量分配号为:=B。

信号分配号为:=C。

变量分配号为<=d。

两者之间没有差异。

16.变量和信号的描述是正确的。

a.变量可以带出进程b.信号可以带出进程c.信号不能带出进程d.二者没有区别17.关于vhdl数据类型,正确的是。

EDA考试试卷

EDA试卷一、选择题:1.下列是EDA技术应用时涉及的步骤:A. 原理图/HDL文本输入;B. 适配;C. 时序仿真;D. 编程下载;E. 硬件测试;F. 综合请选择合适的项构成基于EDA软件的FPGA / CPLD设计流程:A →_________ →_________ →_________ →_________ →E2.PLD的可编程主要基于A. LUT结构或者B. 乘积项结构:请指出下列两种可编程逻辑基于的可编程结构:FPGA 基于___________CPLD 基于____________3.在状态机的具体实现时,往往需要针对具体的器件类型来选择合适的状态机编码。

对于A. FPGA B. CPLD 两类器件:一位热码状态机编码方式适合于_________ 器件;顺序编码状态机编码方式适合于_________ 器件;4.下列优化方法中那两种是速度优化方法:______________、______A. 资源共享B. 流水线C. 串行化D. 关键路径优化单项选择题:5.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中,_________是错误的。

A. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;B. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;C. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的。

D.综合是纯软件的转换过程,与器件硬件结构无关;6.不完整的IF语句,其综合结果可实现________。

A. 时序电路B. 双向控制电路C. 条件相或的逻辑电路D. 三态控制电路7.在一个VHDL设计中Idata是一个信号,数据类型为std_logic_vector,试指出下面那个赋值语句是错误的。

A. idata <= "00001111";B. idata <= b"0000_1111";C. idata <= X"AB";D. idata <= 16"01";8.在VHDL语言中,下列对时钟边沿检测描述中,错误的是_______。

EDA

河北科技大学2011 —2012 学年第2 学期《EDA技术》考试试卷学院:班级:姓名:学号:题号一二三四五总分得分一、名词解释1.EDA2.VHDL3.CPLD4.FPGA5.异步复位二、简答题1.采用VHDL语言设计数字系统具有哪些特点?2.举例说明FPGA是如何通过查找表实现其逻辑功能的?3.简述用QUARTUS开发数字系统的过程?4.简述FPGA与CPLD在硬件结构上的区别?5.如何消除数字电路中的“毛刺”?三、编程题1.编程实现3-8译吗器。

2.编程实现60进制的计数器,要求带复位清零,用CLR表示,高电平有效,输出带进位端,用CO表示。

1、EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CA T)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

2、VHDL全名V ery-High-Speed Integrated Circuit HardwareDescription Language,诞生于1982年。

1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。

3、CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。

其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

EDA技术(VHDL)试卷及答案

班级 学号 姓名密 封 线 内 不 得 答 题一、单项选择题(30分)1.以下描述错误的是 CA .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境B .Altera 是世界上最大的可编程逻辑器件供应商之一C .MAX+plusII 是Altera 前一代FPGA/CPLD 集成开发环境QuartusII 的更新换代新产品D .QuartusII 完全支持VHDL 、Verilog 的设计流程2.以下工具中属于FPGA/CPLD 开发工具中的专用综合器的是 BA .ModelSimB .Leonardo SpectrumC .Active HDLD .QuartusII 3.以下器件中属于Xilinx 公司生产的是 CA .ispLSI 系列器件B .MAX 系列器件C .XC9500系列器件D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 BA .信号是描述硬件系统的基本数据对象,它的性质类似于连接线B .信号的定义范围是结构体、进程 //在整个结构体的任何地方都能使用C .除了没有方向说明以外,信号与实体的端口概念是一致的D .在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 BA .Moore 型状态机其输出是当前状态和所有输入的函数//Mealy 型状态机其输出信号是当前状态和当前输入的函数B .与Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期C .Mealy 型状态机其输出是当前状态的函数D .以上都不对6.下列标识符中, B 是不合法的标识符。

A .PP0B .ENDC .Not_AckD .sig7.大规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是 C 。

A//.FPGA 即是现场可编程逻辑器件的英文简称CPLD 复杂可编程逻辑器件 B .CPLD 是基于查找表结构的可编程逻辑器件 C .早期的CPLD 是从GAL 的结构扩展而来D .在Altera 公司生产的器件中,FLEX10K 系列属CPLD 结构 8.综合是EDA 设计流程的关键步骤,在下面对综合的描述中, D 是错误的.A .综合就是把抽象设计层次中的一种表示转化成另一种表示的过程B .综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件C .为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束D .综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)9.嵌套使用IF 语句,其综合结果可实现 A .A .带优先级且条件相与的逻辑电路B .条件相或的逻辑电路C .三态控制电路D .双向控制电路 10.在VHDL 语言中,下列对时钟边沿检测描述中,错误的是 D 。

Verilog试题 A答案

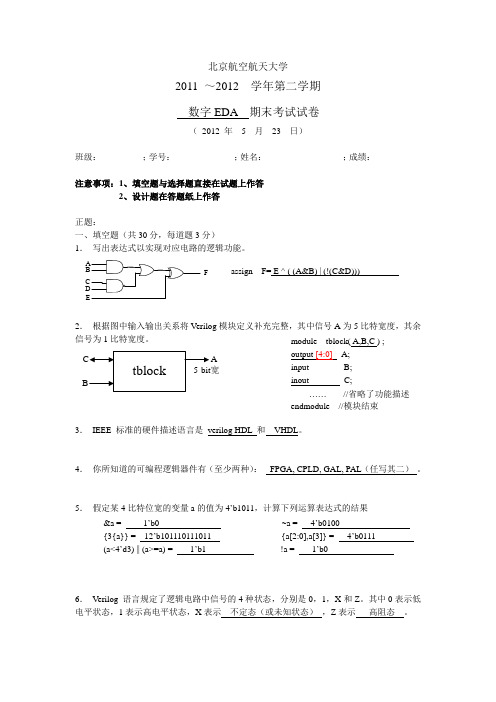

北京航空航天大学2011 ~2012 学年第二学期 数字EDA 期末考试试卷( 2012 年 5 月 23 日)班级:__________;学号:______________;姓名:__________________;成绩:___________注意事项:1、填空题与选择题直接在试题上作答2、设计题在答题纸上作答正题:一、填空题(共30分,每道题3分)1. 写出表达式以实现对应电路的逻辑功能。

F2. 根据图中输入输出关系将Verilog模块定义补充完整,其中信号A 为5比特宽度,其余信号为1比特宽度。

A 宽3. IEEE 标准的硬件描述语言是 verilog HDL 和 VHDL 。

4. 你所知道的可编程逻辑器件有(至少两种): FPGA, CPLD, GAL, PAL (任写其二) 。

5. 假定某4比特位宽的变量a 的值为4’b1011,计算下列运算表达式的结果6. Verilog 语言规定了逻辑电路中信号的4种状态,分别是0,1,X 和Z 。

其中0表示低电平状态,1表示高电平状态,X 表示 不定态(或未知状态) ,Z 表示 高阻态 。

assign F= E ^ ( (A&B) | (!(C&D)))module tblock( A,B,C ) ; output [4:0] A;input B;inout C; …… //省略了功能描述endmodule //模块结束 &a = 1’b0 ~a = 4’b0100 {3{a}} = 12’b101110111011 {a[2:0],a[3]} = 4’b0111 (a<4’d3) || (a>=a) = 1’b1 !a = 1’b07. 下面两段代码中信号in ,q1,q2和q3的初值分别为0,1,2和3,那么经过1个时钟周期后,左侧程序中q3的值变成 0 ,右侧程序中q3的值变成 2 。

8. Verilog 语言规定的两种主要的数据类型分别是 wire(或net) 和 reg 。

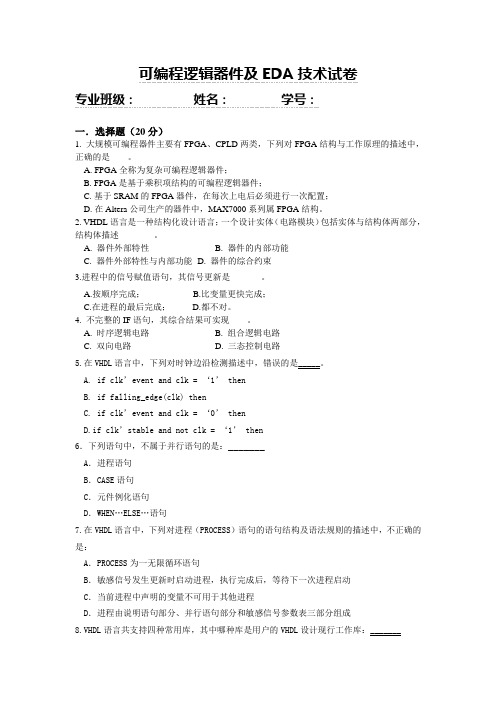

可编程逻辑器件及EDA技术考试题

可编程逻辑器件及EDA技术试卷专业班级:姓名:学号:一.选择题(20分)1. 大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是____。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

2. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述________。

A. 器件外部特性B. 器件的内部功能C. 器件外部特性与内部功能D. 器件的综合约束3.进程中的信号赋值语句,其信号更新是_______。

A.按顺序完成;B.比变量更快完成;C.在进程的最后完成;D.都不对。

4. 不完整的IF语句,其综合结果可实现____。

A. 时序逻辑电路B. 组合逻辑电路C. 双向电路D. 三态控制电路5.在VHDL语言中,下列对时钟边沿检测描述中,错误的是_____。

A. if clk’event and clk = ‘1’ thenB. if falling_edge(clk) thenC. if clk’event and clk = ‘0’ thenD.if clk’stable and not clk = ‘1’ then6.下列语句中,不属于并行语句的是:_______A.进程语句B.CASE语句C.元件例化语句D.WHEN…ELSE…语句7.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是:_______A.PROCESS为一无限循环语句B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动C.当前进程中声明的变量不可用于其他进程D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成8.VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库:_______A.IEEE库B.VITAL库C.STD库D.WORK工作库9. 电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);下列方法中______不属于面积优化。

(完整)Verilog_HDL试卷及答案,推荐文档.doc

河北大学课程考核试卷2008 —— 2009 学年第一学期2006 级电气类专业(类)考核科目 EDA 技术课程类别必修考核类型考查考核方式闭卷类别 A一、选择题:1、下列标示符哪些是合法的( B )A、 $timeB、 _dateC、 8sumD、 mux#2、如果线网类型变量说明后未赋值,起缺省值是( D )A、 xB、 1C、 0D、 z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr 被赋予的值是( A )A、 4’b1101B、 4’b0011C、 4’bxx11D、 4’bzz114、 reg[7:0] mema[255:0] 正确的赋值是( A )A、 mema[5]=3 ’d0,B、 8’d0;C、 1’b1;D、 mema[5][3:0]=4 ’d15、在 code 模块中参数定义如下,请问top 模块中 d1 模块 delay1、 delay2 的值是 ( D )module code(x,y); module top;paramee delay1=1,delay2=1; .code #(1,5) d1(x1,y1);endmodule endmoduleA、( 1,1)B、(5,5)C、( 5,1)D、( 1,5)6、“ a=4’b11001,b=4 ’bx110”选出正确的运算结果( B )A、 a&b=0B、a&&b=1C、b&a=xD、 b&&a=x7、时间尺度定义为timescale 10ns/100ps ,选择正确答案( C )A、时间精度 10nsB、时间单位 100psC、时间精度 100psD、时间精度不确定8、若 a=9,执行 $display( “current value=%0b,a=%0d ”,a,a)正确显示为( B )A、 current value=1001,a=09B、current vale=1001,a=9C、 1001,9D、 current vale=00 001001,a=99、 aways begin #5 clk=0; #10 clk=~clk;end 产生的波形( A )A、占空比 1/3B、 clk=1C、 clk=0D、周期为 1010、在 Verilog 中定义了宏名`define sum a+b+c 下面宏名引用正确的是( C )A、 out= ’sum+d;B、 out=sum+d;C、 out=`sum+d;D、都正确二、填空题:(共 15 分,每小题 3 分)1、某一纯组合电路输入为in1,in2 和 in3,输入出为 out ,则该电路描述中always 的事件表达式应写为always@(in1,in2,in3 ); 若某一时序电路由时钟clk 信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always 的事件表达是应该写为always @( posedge clk )。

eda期末考试试卷

eda期末考试试卷EDA期末考试试卷一、选择题(每题2分,共20分)1. EDA是指:A. 电子设计自动化B. 电子数据交换C. 电子文档分析D. 电子设备应用2. 在EDA工具中,用于绘制电路原理图的软件通常被称为:A. PCB DesignerB. Schematic CaptureC. Logic SimulatorD. Layout Editor3. 下列哪个不是数字逻辑门的基本类型:A. ANDB. ORC. NOTD. XOR4. 以下哪个是EDA工具中用于模拟电路行为的软件:A. VHDLB. VerilogC. RTL SimulatorD. PCB Router5. 在设计一个数字电路时,以下哪项不是设计流程的一部分:A. 需求分析B. 原理图绘制C. 电路板设计D. 手工焊接6. FPGA代表:A. 现场可编程门阵列B. 固定门阵列C. 通用门阵列D. 专用集成电路7. 在VHDL或Verilog中,以下哪个关键字用于定义一个过程:A. processB. moduleC. functionD. package8. 以下哪个是EDA工具中用于生成电路板布局的软件:A. Schematic CaptureB. Layout EditorC. PCB DesignerD. Logic Simulator9. 在数字电路设计中,同步设计和异步设计的主要区别在于:A. 使用的逻辑门类型B. 电路的复杂性C. 时钟信号的使用D. 电路的功耗10. 下列哪个不是常用的PCB设计软件:A. Altium DesignerB. EagleC. KiCadD. MATLAB二、简答题(每题10分,共30分)1. 简述EDA工具在电子设计过程中的作用和重要性。

2. 解释什么是信号完整性,并讨论它在高速电路设计中的重要性。

3. 描述一个典型的数字电路设计流程,并解释每个步骤的目的。

三、计算题(每题15分,共30分)1. 给定一个简单的数字逻辑电路,包含两个输入A和B,一个输出Y。

EDA技术试题库

EDA试题库建设[70%基础题,20%中档题,10%提高题(试题容量:20套试卷,其中每套试题填空题10空(每空2分),选择题10题(每题2分)),简答题4题(每题5分),分析题2题(每题10分),设计题2题(每题10分)。

]基础题部分填空题(140空)12.EDA3,4.VHDL56.以7.8.在PC9.VHDL10.常用11.在12.13、VHDL14、VHDL1516、VHDL17、VHDL18。

192021、VHDL22、STD_LOGIC_1164程序包是(IEEE)库中最常用的程序包。

23.文本输入是指采用(硬件描述语言)进行电路设计的方式。

24.当前最流行的并成为IEEE标准的硬件描述语言包括(vhdl)和(verilog)。

25.采用PLD进行的数字系统设计,是基于(芯片)的设计或称之为(自底向上)的设计。

26.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为(自顶向下)的设计法。

27.EDA工具大致可以分为(设计输入编辑器)、(仿真器)、(hdl综合器)、(适配器)以及(下载器)等5个模块。

28.将硬件描述语言转化为硬件电路的重要工具软件称为(综合器)。

29.用MAX+plusII输入法设计的文件不能直接保存在(根目录)上,因此设计者在进入设计之前,应当在计算机中建立保存设计文件的(工程)。

30.若在MAX+plusII集成环境下,执行原理图输入设计方法,应选择(blockdiagram/Schematic)命令方式。

31.若在MAX+plusII集成环境下,执行文本输入设计方法,应选择(.vhd)方式。

32.\maxplus2\max2lib\prim是MAX+plusII(基本)元件库,其中包括(门电路)、(触发器)、(电源)、(输入)、(输出)等元件。

33.\maxplus2\max2lib\mf是函数元件库,包括(加法器)、(编码器)、(译码器)、(数据选择器数据)、(移位寄存器)等74系列器件。

EDA试卷2017B

华侨大学本科考试卷20 —20 学年第学期学院信息课程名称电子设计自动化考试日期姓名专业学号题号一二三四总分得分注:第一题答案直接写在试卷上,其他题目答案写在答题纸上!!一.基本概念与基本知识(共30分)1. 传统的电子设计技术的设计方法通常是,而在现代电子设计领域的设计方法只有在EDA技术得到快速发展和成熟应用的今天才成为可能。

2.硬件描述语言(HDL)是EDA技术的重要组成部分,目前常用的HDL列举三种、和。

3.IP就是知识产权或知识产权模块的意思,在EDA技术和开发中具有十分重要的地位,其中通常是以HDL源文件的形式出现,应用开发过程与普通的HDL 设计也十分相识,设计周期短,设计投入少。

4.写出下列缩写的中文含义(注:在电子电路设计领域):a). LPM:b). DFT:5. 是VHDL最常用、最基本的数据类型。

6. 可编程逻辑器件从结构上分类,简单PLD和CPLD属于结构。

7. 状态机编码方式中,其中编码占用触发器较多,但其简单的编码方式可减少状态译码组合逻辑资源,且易于控制非法状态8. 目前常用的大规模可编程逻辑器件的编程工艺有三种,分别为、和。

9. VHDL每一种赋值语句都有三个基本部分组成,分别为、和。

10.FPGA仿真包括仿真和仿真,其中仿真包含硬件特性参数,仿真精度高。

二.VHDL语言综合理解。

仔细阅读下列程序,回答问题。

(共16分)1、判断下列VHDL标识符是否合法,如果有误则指出原因。

16#16A#,component,74LS010,tuas_trbmy-2、已知M和N均为STD_LOGIC类型的信号,请判断下列程序是否正确。

如果不正确,请指出并说明原因。

ARCHITECTURE stugaht OF testone ISBEGINIF (M=’1’ )THENN<=’0’ ;ELSEN<=’1’ ;END IF ;END testone ;3、已知L和M均为STD_LOGIC类型的输出端口,请判断下列程序是否正确。

EDA技术期末试卷含答案

一、单项选择题(30分)9.嵌套使用IF语句,其综合结果可实现 A 。

A.带优先级且条件相与的逻辑电路1.以下描述错误的是 C B.条件相或的逻辑电路C.三态控制电路A.QuartusII是Altera提供的FPGA/CPLD集成开发环境D.双向控制电路10.在VHDLB.Altera是世界上最大的可编程逻辑器件供应商之一语言中,下列对时钟边沿检测描述中,错误的是 D 。

A.if clk'event and clk = ‘1' then B.if falling_edge(clk) then MAX+plusIIC.是Altera前一代FPGA/CPLD集成开发环境QuartusII的更C.if clk'event and clk = ‘0' then 新换代新产品D.if clk'stable and not clk = ‘1' then11.下列那个流程是正确的基于VerilogD.QuartusII完全支持VHDL、的设计流程EDA软件的FPGA / CPLD设计流程 BA.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试.2以下工具中属于FPGA/CPLD开发工具中的专用综合器的是 BB.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试.Leonardo Spectrum C.Active HDL DQuartusII ModelSim A.B.C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;以下器件中属于3.Xilinx 公司生产的是 C/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试DMAXB.系列器件.原理图.AispLSI系列器件)语句的语句结构及语法规则语言中,下列对进程(PROCESS D .CXC9500系列器件.FLEX系列器件12.在VHDL 。

A 的描述中,正确的是4.以下关于信号和变量的描述中错误的是 B为一无限循环语句;敏感信号发生更新时启动进程,执行完..信号是描述硬件系统的基本数据对象,它的性质类似于连接线A PROCESSA B.信号的定义范围是结构体、进程成后,等待下一次进程启动BC.除了没有方向说明以外,信号与实体的端口概念是一致的.敏感信号参数表中,应列出进程中使用的所有输入信号CD.在进程中不能将变量列入敏感信号列表中.进程由说明部分、结构体部分、和敏感信号参数表三部分组成 D B .5以下关于状态机的描述中正确的是.当前进程中声明的变量也可用于其他进程 B 型状态机其输出是当前状态和所有输入的函数A.Moore 13.下列语句中,不属于并行语句的是语句B.CASE MooreB.与型状态机相比,Mealy型的输出变化要领先一个时钟周期A.进程语句…语句…ELSE D.WHEN .元件例化语句型状态机其输出是当前状态的函数.CMealy C设计现行工作VHDL语言共支持四种常用库,其中哪种库是用户的D.以上都不对14.VHDL 下列标识符中, B 库是不合法的标识符。

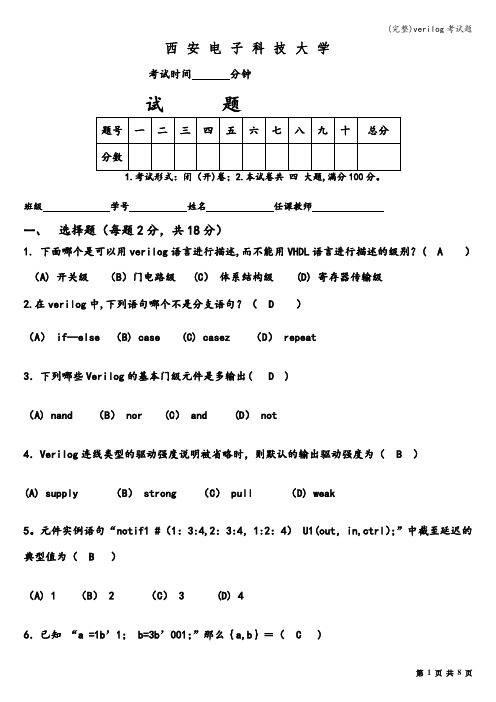

(完整)verilog考试题

西安电子科技大学考试时间分钟试题班级学号姓名任课教师一、选择题(每题2分,共18分)1. 下面哪个是可以用verilog语言进行描述,而不能用VHDL语言进行描述的级别?( A )(A) 开关级(B)门电路级 (C)体系结构级 (D) 寄存器传输级2.在verilog中,下列语句哪个不是分支语句?( D )(A) if—else (B) case (C) casez (D) repeat3.下列哪些Verilog的基本门级元件是多输出( D )(A) nand (B) nor (C) and (D) not4.Verilog连线类型的驱动强度说明被省略时,则默认的输出驱动强度为( B )(A) supply (B) strong (C) pull (D) weak5。

元件实例语句“notif1 #(1:3:4,2:3:4,1:2:4) U1(out,in,ctrl);”中截至延迟的典型值为( B )(A) 1 (B) 2 (C) 3 (D) 46.已知“a =1b’1;b=3b’001;”那么{a,b}=( C )(A) 4b’0011 (B) 3b’001 (C) 4b'1001 (D) 3b’1017.根据调用子模块的不同抽象级别,模块的结构描述可以分为(ABC )(A) 模块级 (B)门级 (C) 开关级 (D) 寄存器级8.在verilog语言中,a=4b'1011,那么 &a=(D )(A) 4b’1011 (B) 4b’1111 (C) 1b'1 (D) 1b'09.在verilog语言中整型数据与( C )位寄存器数据在实际意义上是相同的。

(A) 8 (B) 16 (C) 32 (D) 64二、简答题(2题,共16分)1.Verilog HDL语言进行电路设计方法有哪几种(8分)1、自上而下的设计方法(Top—Down)2、自下而上的设计方法(Bottom—Up)3、综合设计的方法2.specparam语句和parameter语句在参数说明方面不同之处是什么(8分)。

Verilog系统设计考试试卷与答案

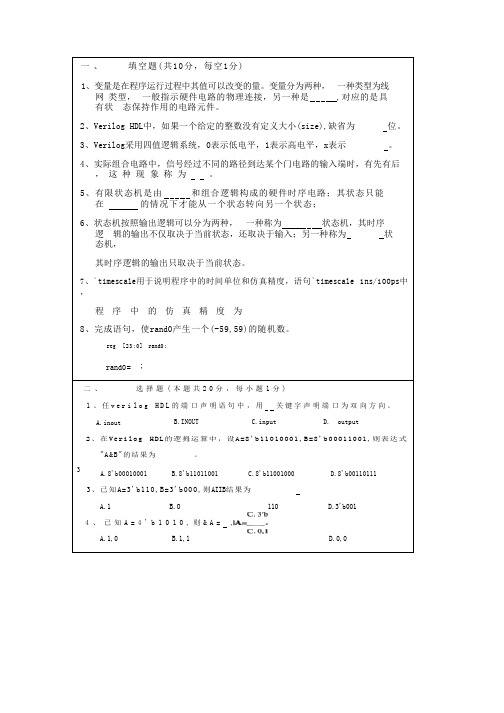

一、填空题(共10分,每空1分)1、变量是在程序运行过程中其值可以改变的量。

变量分为两种,一种类型为线网类型,一般指示硬件电路的物理连接,另一种是 ,对应的是具有状态保持作用的电路元件。

2、Verilog HDL中,如果一个给定的整数没有定义大小(size),缺省为位。

3、Verilog采用四值逻辑系统,0表示低电平,1表示高电平,x表示。

4、实际组合电路中,信号经过不同的路径到达某个门电路的输入端时,有先有后,这种现象称为。

5、有限状态机是由和组合逻辑构成的硬件时序电路;其状态只能在的情况下才能从一个状态转向另一个状态;6、状态机按照输出逻辑可以分为两种,一种称为状态机,其时序逻辑的输出不仅取决于当前状态,还取决于输入;另一种称为状态机,其时序逻辑的输出只取决于当前状态。

7、`timescale用于说明程序中的时间单位和仿真精度,语句`timescale 1ns/100ps中,程序中的仿真精度为8、完成语句,使rand0产生一个(-59,59)的随机数。

reg [23:0] rand0;rand0= ;二、选择题 ( 本题共 2 0 分,每小题 1 分 )1 、任v e r i l o g H D L 的端口声明语句中,用关键字声明端口为双向方向。

A.inoutB.INOUTC.inputD. output2、在V e r i l o g H D L的逻拇运算中,设A=8'b11010001,B=8'b00011001,则表达式"A&B"的结果为。

3A.8'b00010001B.8'b11011001C.8'b11001000D.8'b001101113、已知A=3'b110,B=3'b000,则AIIB结果为A.1B.O 110 D.3'b0014 、已知 A = 4 ' b 1 0 1 0 , 则 & A = ,A.1,0B.1,1 D.0,015、不完整的IF语句,其综合结果可实现:A . 三态控制电路B .条件相或的逻辑电路C.双向控制电路D.时序逻辑电路16、下列关于同步有限状态机的描述错误的是A. 状态变化只能发生在同一个时钟跳变沿;B.状态是否变化要根据输入信号,只要输入条件满足,就会立刻转入到下一个状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.给出下述Verilog语句的仿真输出结果(本题5分,每个1分)。

(1)$displayb ( 4'b1010 < 4'b0110 );输出为: 0

(2)$displayb ( 4'b1x10 = = 4'b1x10 ); 输出为: x

(3)$displayb ( ^4'b1110 ); 输出为: 1

(4)$displayb ( {3{2’b10}} ) ; 输出为: 101010

(5)//假设reg [3:0] a; a=4'b1010;

$displayb ( {{4{a[3]}},a} ); 输出为: 11111010 2.假设design为Lab1.v,顶层模块名为Lab1;TestBench为Lab1_TB.v,

顶层模块名为Lab1_TB, 按下述步骤要求,采用modelsim命令行方式时的完整

仿真命令序列为:(本题10分,每个2分)

创建物理库mywork: vlib mywork 映射逻辑库work至物理库mywork: vmap work mywork 编译design至work库: vlog Lab1.v 编译testbench至work库: vlog Lab1_TB.v 启动仿真工具仿真: vsim Lab1_TB 二.简答题(共45分)

1.简述下述Verilog语句的含义(所有信号均为1bit位宽;有时序信息时

请同时说明时序含义,若需要用式子表达,可用X(t)表达“t时刻时X的值”;

可均从0时刻描述)(本题10分,每个2分)

(1) assign #10 out = in1 & in2 ;

先延迟10个时间单位,再计算in1&in2的值,并赋给out。

(2) assign out = # 5 in1 | in2 ;

先计算in1&in2的值,延迟5个时间单位后,赋给out。

(3) or #(1,2,3) or_inst(o,in1,in2);

当输出为上升沿时延迟一个时间单位,输出为下降沿时延迟两个时间单位,输出为高阻态时延迟三个时间单位。

(4) `timescale 1ns / 100ps

一个时间单位为1 ns,时间精度为100ps。

(5)reg [7:0] led_out; 代码片段:led_out[7:0] <= {led_out[6:0],led_out[7]};

循环左移一位

2. 假设design为Lab1.v,顶层模块名为Lab1;TestBench为Lab1_TB.v,顶层模块名为Lab1_TB,简述使用QuartusII工具的FPGA实现、验证操作步骤。

(本题10分)

先对其进行功能仿真

再在QuartusII中基于Lab1.v建立工程project

再对其进行FPGA综合, FPGA适配,门级仿真,并配置器件

3. 简述有限状态机FSM分为哪两类?有何区别?有限状态机的状态编码风格主要有哪三种?FSM的三段式描述风格中,三段分别描述什么?(本题10分)

分为Mealy型Moore型

Mealy型的输出和现态输入均有关系,Moore型的输出只和现态有关系Binary Encoding One Hot Encoding Gray Encoding

时序电路部分 + Next_State + Ouput三段

4. 基于FPGA的设计流程大体可分为:design设计-->synthesis综合-->fit 适配-->配置FPGA,请简要描述综合、适配、配置过程的主要功能。

(本题5分)

综合:将设计转换为FPGA的primitives网表

适配:将primitives网表安排在合适的位置实现

配置:将设计下载到FPGA板上

5. 简要说明仿真时阻塞赋值与非阻塞赋值的区别(本题4分)。

赋值过程包括两个子过程:①计算右侧表达式的值②给左侧目标赋值。

阻塞过程赋值这两个子过程是可以视为连续完成的,而且在完成赋值前不允许随后的其他语句执行;非阻塞这两个子过程之间有微小的时间间隔,在这间隔内随后的语句可以执行。

6. 简要说明$display, $strobe, $monitor的区别(本题6分)。

$display:格式化文本输出,输出即显信息

$strobe:当前时间槽之后稳定的信息

$monitor:监控指定信号,当指定信号变化时,执行一次

三.设计题(共25分)

1.给出异步复位1bit DFF的完整 Verilog RTL级描述,复位信号低电平有效,复位时,输出为0。

(本题10分)

module srdff (clk, d, q,reset);

input clk,d,reset;

output q;

reg q;

always@(posedge clk or negedge reset) begin

if(!reset)

q <= 1'b0;

else

q<=d;

end

endmodule

2.给出仿真时生成时钟信号的Verilog描述,要求生成的时钟信号高电平5ns,低电平20ns。

(本题5分)

initial clk=1;

Always

begin

#5 clk=~clk;

#20clk=~clk;

end

3.给出下述电路的完整verilog描述(注意看图;不需要写Testbench;端口均为1bit位宽,名称严格按图定义;异步复位,复位信号高电平有效,复位时,Reg1=0,Reg2=1;顶层模块名统一定义为test24)(本题10分)

module test24(Din,Clk,Reset,Reg1,Reg2,Dout);

input Din,Clk,Reset;

output Dout;

reg Dout,Reg1,Reg2;

always@(posedge clk or posedge reset)

begin

if(reset) Reg1=0,Reg2=1;

Reg1<=Din;

end

always@(poseedge clk or posedge reset)

begin

if(reset) Reg1=0,Reg2=1;

Reg2<=Reg2&Reg1;

end

assign Dout=Reg2^Din;

endmodule

四.综合题(共15分)

1. 某设计接口如下述代码所示,功能要求: out1为"in1与in2",out2为"in1

或 in2",(1)请按功能要求完成设计;(2)请按课堂中testbench3模式写出testbench(testbench中读取测试向量文件,逐条测试,显示测试失败的测试向量,仿真结束时给出失败统计),并给出测试向量文件内容(简要说明测试向量存储格式,文件中穷举4个测试向量)。

(非testbench3模式不得分)(本题15分)

module Lab1(in1,in2,out1,out2);

input in1;

input in2;

output out1;

output out2;

and and_inst(out,in1,in2);

or or_inst(out2,in1,in2);

endmodule

`timescale 1ns/100ps;

module test()

reg in1,in2,out1expected,out2expected;

wire out1,out2;

reg [31:0]vectornum,errors;

reg [3:0] testvectors[10000:0];

Lab1 dut(in1,in2,out1,out2);

initial

begin

$readmemb("", testvectors);

vectornum = 0; errors = 0;

while(1) begin

#1;

{ in1,in2,out1expected,out2expected } =testvectors[vectornum]; #1;

if (out1 !== out1expected|out2!=out2expected) begin

$display("Error: inputs = %b", {in1,in2});

$display(" outputs = %b (%b expected)", out1, out1expected); $display(“outputs=%b(%b expected)”,out2,put2 expected); errors = errors + 1;

end

vectornum = vectornum + 1;

if (testvectors[vectornum] ===4'bx) begin

$display("%d tests completed with %d errors", vectornum, errors);

#10 $stop;end

end end

endmodule

测试向量文件

00_0_0

01_0_1

10_0_1

11_1_0。