去耦电容的选择

去耦电容、旁路电容、滤波电容的选择和区别

区别去耦电容去除在期间切换时从⾼高配到配电⽹网中的RF能量量储能作⽤用,供局部化的直流电源,减少跨板浪涌电流在VCC 引脚通常并联⼀一个去耦电容,电容同交隔直将交流分量量从这个电容接地有源器器件在开关时产⽣生的⾼高频开关噪声江燕电源线传播,去耦电容就是提供⼀一个局部的直流给有源器器件,减少开关噪声在板上的传播并且能将噪声引导到地。

如果主要是为了了增加电源和地的交流耦合,减少交流信号对电源的影响,就可以称为去耦电容;旁路路电容从元件或电缆中转移出不不想要的共模 RF 能量量。

这主要是通过产⽣生 AC 旁路路消除⽆无意的能量量进⼊入敏敏感的部分,另外还可以提供基带滤波功能(带宽受限)。

在电路路中,如果电容起的主要作⽤用是给交流信号提供低阻抗的通路路,就称为旁路路电容;电⼦子电路路中,去耦电容和旁路路电容都是起到抗⼲干扰的作⽤用,电容所处的位置不不同,称呼就不不⼀一样了了。

对于同⼀一个电路路来说,旁路路(bypass)电容是把输⼊入信号中的⾼高频噪声作为滤除对象,把前级携带的⾼高频杂波滤除,⽽而去耦 (decoupling)电容也称退耦电容,是把输出信号的⼲干扰作为滤除对象。

滤波电容选择经过整流桥以后的是脉动直流,波动⽅方位很⼤大,后⾯面⼀一般⽤用⼤大⼩小两个电容⼤大电容⽤用来稳定输出,因为电容两端电压不不能突变,可以使输出平滑,⼩小电容⽤用来滤除⾼高频⼲干扰,使输出电压纯净,电容越⼩小,谐振频率越⾼高,可滤除的⼲干扰频率越⾼高容量量的选择⼤大电容,负载越重,吸收电流的能⼒力力越强,这个⼤大电容的容量量就要越⼤大⼩小电容,凭经验,⼀一般104 即可1、电容对地滤波,需要⼀一个较⼩小的电容并联对地,对⾼高频信号提供了了⼀一个对地通路路。

2、电源滤波中电容对地脚要尽可能靠近地。

3、理理论上说电源滤波⽤用电容越⼤大越好,⼀一般⼤大电容滤低频波,⼩小电容滤⾼高频波。

4、可靠的做法是将⼀一⼤大⼀一⼩小两个电容并联,⼀一般要求相差两个数量量级以上,以获得更更⼤大的滤波频段.滤波电容电源和地直接连接去耦电容1.为本集成电路路蓄能电容2.滤除该期间产⽣生的⾼高频噪声,切断其通过供电回路路进⾏行行传播的通路路3.防⽌止电源携带的噪声对电路路构成⼲干扰滤波电容的选⽤用原则在电源设计中,滤波电容的选取原则是: C≥2.5T/R其中: C 为滤波电容,单位为UF; T 为频率, 单位为Hz,R 为负载电阻,单位为Ω当然,这只是⼀一般的选⽤用原则,在实际的应⽤用中,如条件(空间和成本)允许,都选取C≥5T/R.PCB制版电容的选择⼀一般的10PF 左右的电容⽤用来滤除⾼高频的⼲干扰信号,0.1UF 左右的⽤用来滤除低频的纹波⼲干扰,还可以起到稳压的作⽤用。

电源的去耦

这里再介绍一下电源去耦电路参数的选择:C1的选择: c1=K*I*tr/U,这里假设电源提供电流为I,tr为brust时间,即电压变化稳定前后的时间。

K通常取10,是经验比例。

参数含义见图11。

(粘不上)一般应用时取电容标称值在计算值附近就可以了。

C2的选择:C2为高频陶瓷电容,一般在0.1uF以下取值。

本文来自: 原文网址:/articlescn/basic/0075647.html电源的去耦模电书上讲的去耦大多是讲电源的去耦,就是一个电路的各个单元共用同一电源供电,为了防止各单元之间的耦合,需加去耦电路。

造成耦合的原因有:数字电路——在电平翻转时的瞬间会有较大的电流,且会在供电线路上产生自感电压。

功率放大电路——因电流较大,此电流流过电源的内阻和公共地和电源线路时产生电压,使得电源电压有波动。

高频电路——电路中有高频部分因辐射和耦合在电源上产生干扰。

这些干扰会对同一供电电路中的对电源电压较敏感或精度要求较高的部分,比如微弱小信号放大器、AD转换器等产生干扰,或者相互干扰,严重时使整个电路无法工作。

为了阻止这种干扰,可以加电源去耦电路来解决,一般常用的电源去耦电路有RC或LC电路,要求较高的另加用稳压电路。

你可能对RC或LC去偶的原理不太明白,这里我举个通俗的例子:(不是很确切)有一条流动的水沟,水沟的一端水波动得很厉害,波纹就会传到另一端,为了不让波纹传到另一端,可以在水沟的中间放点稻草,如果你觉得还不够,可以在稻草后面挖个水池,这样在沟的另一端水就会平静多了。

在这里,水的波动相当于电压的波动,稻草相当于电阻或电感(对交流电有阻碍),水池相当于电容(很多人不是把大电容叫做大水塘吗?)。

现在明白了吧?不相同,电源滤波使用的是大容量的电解电容,是用来去除直流电中工频波形(50Hz-100Hz)减小直流电的波动程度,即起平滑波形的作用;去耦电容的容量很小,通常为0.01-0.1uF,是用来滤除电路在工作时产生的高频谐波成分。

100nf的去耦半径

100nf的去耦半径一、100nf去耦电容的原理与作用在电子系统中,去耦电容被广泛应用于滤除电源线上的噪声和干扰,以确保电路的稳定运行。

去耦电容,也称为旁路电容,其主要作用是提供高频噪声的一个低阻抗路径,从而防止这些噪声干扰到敏感的电路部分。

100nf的去耦电容是一个常见的规格,其容量值在电路设计中具有特定的意义。

首先,我们要了解其工作原理:当噪声电压施加到去耦电容上时,它会形成一个回路,使得高频噪声以最短的路径通过低阻抗的电容回到电源,从而消除噪声对电路的影响。

二、100nf电容的理想去耦半径计算理想情况下,去耦半径是指去耦电容能够有效地滤除噪声的最大距离。

这一半径的确定与多种因素有关,如信号的频率、导线的电感和电阻、电容的等效串联电阻(ESR)等。

对于100nf的去耦电容,其理想去耦半径可以通过以下公式进行计算:理想去耦半径(m)= 根号下(L/pi×f×C)其中,L是导线的电感(H),f是信号的频率(Hz),C是去耦电容的容量(F)。

在实际应用中,由于各种因素的影响,理想去耦半径的计算可能需要进行一些调整。

例如,导线的电感和电阻、电容的ESR等都会影响到实际的去耦效果。

因此,在确定去耦半径时,需要进行综合考虑。

三、实际应用中的考虑因素在实际应用中,去耦半径的确定需要考虑以下几个因素:1.信号的频率:高频信号需要更小的去耦半径,因为高频噪声更容易通过短的路径被滤除。

2.导线的电感和电阻:长导线的电感和电阻会限制电流的流动,从而影响去耦效果。

因此,在确定去耦半径时,需要考虑导线的长度和截面积。

3.电容的等效串联电阻(ESR):ESR越小,去耦效果越好。

因此,在选择去耦电容时,应尽量选择ESR较低的产品。

4.电源和地的布局:合理的电源和地布局可以提高去耦效果。

例如,在多层PCB设计中,可以考虑在不同的层上分别布置电源和地,以减小电源和地之间的噪声。

5.其他元件的影响:在电路中,其他元件如电感、电阻等也会影响到去耦效果。

揭秘滤波电容、去耦电容 , 旁路电容的作用

经过整流桥以后的是脉动直流,波动范围很大。后面一般用大小两个电容,大电容用来稳定输出,众所周知电容两端电压不能突变,因此可以使输出平滑,小电容是用来滤除高频干扰的,使输出电压纯净,电容越小,谐振频率越高,可滤除的干扰频率越高.

容量选择:

(1)大电容,负载越重,吸收电流的能力越强,这个大电容的容量就要越大

(2)选取滤波电容:1、电压大于28.2V;2、求C的大小:公式RC≥(3--5)×0.1秒,本题中R=24V/0.5A=48欧

所以可得出C≥(0.00625--0.0104)F,即C的值应大于6250μF。

(3)电容滤波是升高电压。

滤波电容的选用原则

在电源设计中,滤波电容的选取原则是: C≥2.5T/R

原理我就不说了,实用点的,一般数字电路去耦0.1uF即可,用于10M以下;20M以上用1到

10个uF,去除高频噪声好些,大概按C=1/f 。旁路一般就比较的小了,一般根据谐振频率

一般为0.1或0.01uF

说到电容,各种各样的叫法就会让人头晕目眩,旁路电容,去耦电容,滤波电容等等,其

其中: C为滤波电容,单位为UF;

T为频率, 单位为Hz

R为负载电阻,单位为Ω

揭秘滤波电容、去耦电容 , 旁路电容的作用

滤波电容用在电源整流电路中,用来滤除交流成分。使输出的直流更平滑。

去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。

旁路电容用在有电阻连接时,接在电阻两端使交流信号顺利通过。

1.关于去耦电容蓄能作用的理解

1)去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。而实际上,芯片附近的电容还有蓄能的作用,这是第二位的。

正负电源间去耦电容位置-概述说明以及解释

正负电源间去耦电容位置-概述说明以及解释1.引言1.1 概述概述部分的内容可以从以下角度进行描述:正负电源间去耦电容位置是电子电路设计中一个非常重要的问题。

在电子设备中,正负电源提供电流和稳定的电压,而去耦电容则起到平滑和过滤电压的作用。

去耦电容的位置选择直接关系到电路的稳定性和性能的提升。

本文将对正负电源间去耦电容位置进行详细的讨论和探究。

首先,我们将介绍正负电源的基本概念和作用,以便读者能够更好地理解和把握去耦电容的重要性。

其次,我们将详细探讨正电源去耦电容的位置选择。

根据电路的结构和要求,我们将提出一些关键要点,包括但不限于去耦电容与正电源之间的距离、去耦电容与负载之间的关系等。

这些要点将有助于读者在实际应用中合理选择去耦电容的位置,以提高电路的稳定性和性能。

接着,我们将研究负电源去耦电容的位置选择。

与正电源类似,负电源去耦电容的位置也直接影响电路的性能。

我们将探讨一些关键要点,例如负电源去耦电容与地/负载之间的连接方式、位置选择的考虑因素等。

通过深入分析和研究,读者将能够准确选择负电源去耦电容的位置,以优化电路性能和提高稳定性。

最后,在结论部分,我们将总结正负电源去耦电容位置的重要性。

通过本文的阐述,读者将更好地理解去耦电容的作用和位置选择的原则,并明确其在电路设计中的必要性。

同时,我们也将提出一些进一步研究的方向,以促进这一领域的发展和提高电路设计的水平。

通过对正负电源间去耦电容位置的详细讨论,我们旨在帮助读者深入理解这一问题的关键点,并能够在实际应用中准确选择去耦电容的位置,以提高电路的稳定性和性能。

1.2 文章结构本文将分为引言、正文和结论三个部分来探讨正负电源间去耦电容位置的问题。

引言部分将对本文的主题进行概述,介绍正负电源去耦电容在电子设备中的作用,并说明文章的目的。

正文部分将重点讨论正电源去耦电容的位置和负电源去耦电容的位置。

对于正电源去耦电容位置,我们将提出一些关键要点,包括其作用、放置位置的选择以及相关的注意事项等。

去耦电容的选择

TECHNICAL NOTE DECOUPLING CAPACITORCALCULATION FOR A DDRMEMORY CHANNELIntroductionThe fast switching rates of DDR memory devices require significantly more burst current than previous memory technologies, such as SDRAM. In a worst-case scenario, as many as 81 drivers (64 data, 8 ECC, 9 strobe) may be switching from one state to the other on a memory module. In a pipelined access , the con-troller may have an additional 28 signals transitioning at the same time. This large burst current generates noise in the supply voltages as charge is drained from decoupling capacitors. Furthermore, the burst current causes supply voltages to drop momentarily until the system power supply, or voltage regulator, can begin recharging the decoupling capacitors.Traditional methods for providing power decou-pling involve placing capacitors near the switching device in locations that are convenient based on the routing of the board, and applying some predeter-mined ratio of caps to driver pins. Unfortunately, the higher switching speeds of DDR may render such typi-cal ratios less than useful. Careful planning and analy-sis should be performed to ensure that sufficient decoupling is provided.The following analysis example and recommenda-tions are based on a prototype PC motherboard that supports unbuffered DDR SDRAM. This board was designed and built by Micron Architecture Labs as a reference board for DDR memory.Current DrawTotal current per net is the combination of steady state current through the termination resistors, I dc, and the switching current through the driver, I ac. I dc is constant until the driver changes state. I ac only flows during the state transition. Because the steady state current transitions from a positive (or negative) level to a negative (or positive) level during the time that I ac is flowing through the driver, it must be accounted for at the same time (see Figure 1).Figure 1: Current Flow During LogicTransition from 1 to 0I total = I dc + I ac; where I dc = average steady state cur-rent through R s, the series resistor, R t, the parallel ter-mination resistor, and R d, the driver resistance. termination resistor. I ac = switching current for one net to change logic states.As an example, consider a memory channel that supports two double-sided, unbuffered DDR DIMMs, with R s = 0 ohms, R d = 13 ohms, and R t = 39 ohms. Assume that the worst-case switching maintains a 1 V/ ns edge rate (see Formula 1).(f 1)TBDInductanceThe critical limiting factor in designing a decou-pling system is usually not the amount of capacitance. It is the amount of inductance in the capacitor leads and the vias that attach the caps to the power and ground planes. Using 0.1µF caps in a 0603 package should provide sufficient capacitance when the follow-ing calculations are used.Via InductanceCurrent flows through a via only to the depth of the plane to which it attaches. For example, on a 0.062" board with the ground plane only 0.004" below the top layer, the effective length of the via would be 0.004". Typically, each decoupling cap attaches to an internal power plane, as well as the ground plane. I f the PCB stackup is symmetrical and the same diameter via is used for power and ground, using the length of a single via through the entire thickness of the board is equal to the sum of the via lengths for power and ground. This simplifies the calculation of the via inductance. NOTE:If via structures for power and ground are dif-ferent, e.g., two ground vias and one powervia, then separate calculations for each struc-ture should be done.To calculate the via inductance, use the following equation from Johnson & Graham’s High-Speed Digital Design: A Handbook of Black Magic (see Formula 2).(f 2) Maximum Allowable Inductance The fast switching current induces a voltage drop in the parasitic inductance of the capacitor and the vias that attach it to the voltage planes. From the standard equation V = L(di/dt), L max can be calculated. There are two current paths that ultimately flow through the driver. I n the case of a 1-to-0 transition, I dc flows through R d, R s and R t. I ac flows from the charged input gates through R d and R s into the ground plane. In the case of a 0-to-1 transition, the same current flows in the other direction from V2.5. The tolerance of MVTT is much tighter than V2.5, therefore, L max for the termi-nation voltage MVTT, should be calculated separately from L max for V2.5. For simplicity of calculations, assume that only I dc flows from MVTT and I ac flows from V2.5. In reality, MVTT contributes to the I ac cur-rent flow during the edge transition, but estimating or calculating that contribution would likely not affect the results significantly.Also note di for MVTT equals twice I dc. This is because I dc transitions from a positive value to a nega-tive value of the same magnitude. I ac transitions from 0 to its maximum value during dt, therefore di for V2.5 = I ac (see Formula 3).(f 3) Equivalent Inductance per Capacitor Package inductance for a 0603 cap can vary from manufacturer to manufacturer and from one dielectric type to another. Designers should check component data sheets for the correct inductance value if available (see Formula 4).(f 4) Number of Capacitors NeededTo calculate the number of capacitors needed, divide the equivalent inductance of each cap by the maximum allowable inductance, L max (see Formula 5).(f 5)For this example:0603 cap was used with a package inductance of 0.87nH 0603L eq = L package + L via0603L eq = 0.87nH + 0.948nH = 1.82nHN cap = L eq/L maxFor this example:M VTTN cap = 1.82nH/0.029nH = 63V2.5N cap = 1.82nH/0.073nH = 258000 S. Federal Way, P .O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900E-mail: prodmktg@, Internet: , Customer Comment Line: 800-932-4992Micron, the M logo, and the Micron logo are trademarks of Micron Technology, Inc.All other trademarks are the property of their respective owners.The capacitor count for MVTT may be reduced depending on implementation. Some designs may allow MVTT to be implemented on a surface layer island, in which case one terminal of the cap can be attached directly to the plane without a via. Addition-ally, the effective length of the ground via may be sig-nificantly reduced if the PCB stackup has the ground plane immediately below the surface layer. If this is the case (assuming h = .004"), L via = 24.5pH, which is insig-nificant compared to the capacitor package induc-tance. Therefore, for surface plane decoupling, assume L eq = L package . Given this assumption, the 0603 capaci-tor count for MVTT would be 31. For internal planes,the 0603 capacitor count equals 63. Because the toler-ance on MVTT is so tight, it is recommended that a surface plane or some other method of lowering via inductance be used.Exceptions and VariationsThe equations presented here use a linear approxi-mation of differential quantities such as di/dt. More in-depth calculations can be done to get more accu-rate predictions. Additionally, each net was assumed to be equally loaded and of the same type. In an unbuf-fered DDR channel, address, control, and clock signals will be more heavily loaded than data or strobes. These signals are also unidirectional from controller to RAM,and they run at half the speed of data and strobes. Sep-arate calculations can be done to more accurately pre-dict the current flow for these nets.The capacitor quantities in this example are very dependent on the device parameters used in the calcu-lation. This analysis should be done for each new design as device parameters may be different and willsignificantly affect the results. For instance, these cal-culations were based on using R d = 13 ohms and R t =39 ohms. Changing the resistor values to 22 and 29, for example, will increase the amount of I dc per net to 24.5mA. This reduces MVTT_L max and increases the MVTT capacitor count and the V2.5 capacitor count.Although difficult to predetermine, lower series resistance, R s will also speed up signal edges, resulting in a larger di/dt quantity. This will increase the number of decoupling caps needed for V2.5.I t is also difficult to predict what value should be used for dt. This is highly dependent on the strength of the driver being used and will vary greatly from one product family to another. Even in a fully loaded con-figuration, some devices have been measured to have edge rates of 2 V/ns, effectively switching in half the time. These devices meet all of the minimum specs for DDR SDRAMs and might run in the same system with devices that only drive 1 V/ns. But the faster devices switch the same amount of current over a lower dt time, hence they generate significantly more switching noise and, consequently, may require additional decoupling to compensate for the driver strength.I t is recommended that some experimentation be done to determine the right amount of decoupling needed. Use the equations and the most accurate data sheet information available to design a first prototype.Then, measure noise levels on MVTT and V2.5, and edge rates of data and strobes to correlate noise with decoupling amounts. New calculations based on these new measurements will give a more accurate estimate of the decoupling needs of the design.。

去耦电容选择原则

去耦电容选择原则

1. 去耦电容的容值应选择足够大,以提供足够的电流响应能力。

一般来说,容值在10uF或以上是比较常见的选择。

2. 选择电容器时,应注意其最大工作电压是否符合电路要求,以避免电容器过压损坏。

3. 需要注意电容器的尺寸和重量,以确保其可以适应所设计的电路板和整体产品结构。

4. 可以考虑使用低阻抗的电解电容器(如固态铝电解电容器)来减小电路中的串扰和噪声。

5. 根据电路的特性,可以选择使用不同类型的电容器,如铝电解电容器、固态铝电解电容器、陶瓷电容器等。

6. 在选择电解电容器时,应注意其额定寿命和温度范围是否符合电路的要求。

7. 对于需要高频去耦的电路,可以选择使用陶瓷电容器,因为其具有较低的ESR(等效串联电阻)和较好的高频性能。

8. 可以根据电路的需求选择使用多个并联的去耦电容器,以提高去耦效果和系统稳定性。

退藕电容的一般配置原则

1.14.1、退藕电容的一般配置原则1.电源输入端跨接10~100uf的电解电容器。

如有可能,接100uf 以上的更好。

2.原则上每个集成电路芯片都应布置一个0.01pf的瓷片电容,如遇印制板空隙不够,可每4~8个芯片布置一个1~10pf的但电容。

3.对于抗噪能力弱、关断时电源变化大的器件,如ram、rom存储器件,应在芯片的电源线和地线之间直接入退藕电容。

4、电容引线不能太长,尤其是高频旁路电容不能有引线。

此外,还应注意以下两点:a、在印制板中有接触器、继电器、按钮等元件时.操作它们时均会产生较大火花放电,必须采用附图所示的rc电路来吸收放电电流。

一般r取1~2k,c取2.2~47uf。

b、cmos的输入阻抗很高,且易受感应,因此在使用时对不用端要接地或接正电源。

由于大部分能量的交换也是主要集中于器件的电源和地引脚,而这些引脚又是独立的直接和地电平面相连接的。

这样,电压的波动实际上主要是由于电流的不合理分布引起。

但电流的分布不合理主要是由于大量的过孔和隔离带造成的。

这种情况下的电压波动将主要传输和影响到器件的电源和地线引脚上。

为减小集成电路芯片电源上的电压瞬时过冲,应该为集成电路芯片添加去耦电容。

这可以有效去除电源上的毛刺的影响并减少在印制板上的电源环路的辐射。

当去耦电容直接连接在集成电路的电源管腿上而不是连接在电源层上时,其平滑毛刺的效果最好。

这就是为什么有一些器件插座上带有去耦电容,而有的器件要求去耦电容距器件的距离要足够的小。

去耦电容配置的一般原则如下:●电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。

如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

去耦电容的使用

去耦电容的使⽤在直流电源回路中,负载的变化会引起电源噪声。

例如在数字电路中,当电路从⼀个状态转换为另⼀种状态时,就会在电源线上产⽣⼀个很⼤的尖峰电流,形成瞬变的噪声电压。

配置去耦电容可以抑制因负载变化⽽产⽣的噪声,是印制电路板的可靠性设计的⼀种常规做法,配置原则如下:电源输⼊端跨接⼀个10~100uF的电解电容器,如果印制电路板的位置允许,采⽤100uF以上的电解电容器的抗⼲扰效果会更好。

为每个集成电路芯⽚配置⼀个0.01uF的陶瓷电容器。

如遇到印制电路板空间⼩⽽装不下时,可每4~10个芯⽚配置⼀个1~10uF钽电解电容器,这种器件的⾼频阻抗特别⼩,在500kHz~20MHz范围内阻抗⼩于1Ω,⽽且漏电流很⼩(0.5uA以下)。

对于噪声能⼒弱、关断时电流变化⼤的器件和ROM、RAM等存储型器件,应在芯⽚的电源线(Vcc)和地线(GND)间直接接⼊去耦电容。

去耦电容的引线不能过长,特别是⾼频旁路电容不能带引线。

⾼⼿和前辈们总是告诉我们这样的经验法则:“在电路板的电源接⼊端放置⼀个1~10µF的电容,滤除低频噪声;在电路板上每个器件的电源与地线之间放置⼀个0.01~0.1µF的电容,滤除⾼频噪声。

”在书店⾥能够得到的⼤多数的⾼速PCB设计、⾼速数字电路设计的经典教程中也不厌其烦的引⽤该⾸选法则(⽼外俗称Rule of Thumb)。

但是为什么要这样使⽤呢?⾸先就我的理解介绍两个常⽤的简单概念。

什么是旁路?旁路(Bypass),是指给信号中的某些有害部分提供⼀条低阻抗的通路。

电源中⾼频⼲扰是典型的⽆⽤成分,需要将其在进⼊⽬标芯⽚之前提前⼲掉,⼀般我们采⽤电容到达该⽬的。

⽤于该⽬的的电容就是所谓的旁路电容(Bypass Capacitor),它利⽤了电容的频率阻抗特性(理想电容的频率特性随频率的升⾼,阻抗降低,这个地球⼈都知道),可以看出旁路电容主要针对⾼频⼲扰(⾼是相对的,⼀般认为20MHz以上为⾼频⼲扰,20MHz以下为低频纹波)。

去耦电容的配置原则

去耦电容的配置原则

去耦电容(Decoupling capacitor)是在电子电路中常用的元件,用于提供电流瞬态补偿和滤波作用,以保持电路的稳定性和抑制干扰。

以下是去耦电容的配置原则:

1. 配置位置:去耦电容应尽量靠近目标芯片的电源引脚。

这样可以最大限度地缩短电流路径,减少所经过的电阻和电感,提供更好的补偿效果。

2. 大小选择:去耦电容的大小应根据目标芯片的需求和工作频率来选择。

一般而言,较大的电容值能够提供更好的瞬态补偿效果。

常见的去耦电容值通常在几十微法(uF)到几百微法(uF)范围内。

3. 多电容并联:针对不同频率范围的干扰,可以配置多个电容并联来实现更好的滤波效果。

例如,可以同时配置一个较小容值的陶瓷电容和一个较大容值的电解电容,以满足高频和低频噪声的补偿需求。

4. ESR选择:等效系列电阻(ESR)是电容器内部的电阻,也会影响去耦电容的性能。

为了获得更好的高频响应和降低共振问题,可以选择具有较低ESR值的电容。

5. 电容类型选择:常见的去耦电容有陶瓷电容、铝电解电容等。

陶瓷电容具有快速充放电能力和良好的高频特性,适用于高速数字电路;铝电解电容容量较大,适用于供电稳压和较低频的补偿。

需要注意的是,去耦电容的配置需要充分考虑目标芯片的工作环境、频率特性和噪声源情况。

不同的应用场景可能需要不同的配置方式和参数选择。

因此,建议在实际设计中结合具体情况进行综合考虑,并进行实际测试和优化。

去耦电容的esl

去耦电容的esl

ESL(Equivalent Series Inductance)是指电容器内部的等效串

联电感,它会影响电容器在高频环境下的性能。

为了减小电容器的ESL,可以采取以下几种方法:

1. 使用低ESL的电容器:选择具有低ESL值的电容器,这些

电容器通常会在规格书中标明。

例如,钽电容器和多层陶瓷电容器通常具有较低的ESL。

2. 平行连接电容器:将多个电容器并联连接,以降低总ESL。

并联连接不同种类的电容器,如钽电容器与多层陶瓷电容器,可以在一定程度上抵消它们各自的ESL。

3. 降低电容器的引线长度:电容器引线的长度越短,ESL就越低。

因此,在设计电路板或布局时,可以尽量缩短电容器引线的长度。

4. 使用高频贴片电容器:贴片电容器通常具有较低的ESL。

选择具有小尺寸和高频率特性的贴片电容器,可以降低ESL。

总体而言,减小耦合电容的ESL可以通过选择低ESL电容器、并联连接电容器、缩短引线长度和使用高频贴片电容器等方法来实现。

单片机去耦电容作用

单片机去耦电容作用单片机去耦电容作用是非常重要的,因为去耦电容的作用能够提供防干扰效果,从而保证单片机的正常工作。

接下来,我们将详细介绍单片机去耦电容的作用和实现方式。

2. 单片机去耦电容应该如何选型单片机去耦电容的选型需要根据单片机的工作频率和电源电压来决定。

一般来说,单片机工作频率越高,需要的去耦电容就越大。

电源电压也是影响去耦电容选型的因素之一。

在实际应用中,可以根据单片机厂商提供的去耦电容选型公式来确定具体的电容值。

ST公司的STM32系列单片机,其去耦电容的选型公式为:Cdec = Imax × Vdec / (ΔV × Fosc)Cdec为单片机去耦电容的容值;Imax为单片机最大电流;Vdec为电压下降值,一般为0.3V;ΔV为电容器耐压值;Fosc为单片机操作频率。

3. 单片机去耦电容的实现方式单片机去耦电容的实现方式一般有两种,一种是使用表面贴装电容,另一种是使用插件式电容。

表面贴装电容常用于小型电子产品中,其特点是体积小,重量轻,可以在PCB板的两侧安装,使得整个电路板更加紧凑。

插件式电容则一般用于大型电子产品中,其特点是具有更好的耐用性和更大的电容值,但是体积较大,需要占用更多的空间。

1) 正确放置电容:将去耦电容放置在单片机电源引脚和电源电容之间,这样可以很好地滤除高频噪声。

2) 选择适当的引脚连接方式:将去耦电容与单片机连接的引脚长度要尽量短,同时最好使用银河屏蔽线等有一定抗干扰能力的线材来连接。

3) 正确的板布局:将去耦电容尽可能靠近单片机,同时在设计PCB板时还应尽量减少电源线的长度,从而降低由于线路电阻和电感产生的电流噪声。

4) 具备良好的接地和电源设计: 设计单片机电路时,需要保证其具备良好的接地和电源设计,从而使去耦电容能够起到最佳的滤波效果。

单片机去耦电容的作用非常重要,能够有效地提高单片机的抗干扰能力,保证其正常工作。

在设计单片机电路时一定要注意为其选择合适的去耦电容,同时合理安装和布局,从而有效提高单片机的可靠性。

去耦电容的选择、容值计算和pcb布局布线详解

去耦电容的选择、容值计算和pcb布局布线详解去耦电容的应用的非常广泛,在电路应用过程中对于去耦电容的容值计算和PCB电路布局布线有一些我们必须要了解的技巧。

有源器件在开关时产生的高频开关噪声将沿着电源线传播。

去耦电容的主要功能就是提供一个局部的直流电源给有源器件,以减少开关噪声在板上的传播,和将噪声引导到地。

去耦电容的容值计算去耦的初衷是:不论IC对电流波动的规定和要求如何都要使电压限值维持在规定的允许误差范围之内。

使用表达式:C⊿U=I⊿t由此可计算出一个IC所要求的去耦电容的电容量C。

⊿U是实际电源总线电压所允许的降低,单位为V。

I是以A(安培)为单位的最大要求电流;⊿t是这个要求所维持的时间。

去耦电容容值计算方法:推荐使用远大于1/m乘以等效开路电容的电容值。

此处m是在IC的电源插针上所允许的电源总线电压变化的最大百分数,一般IC的数据手册都会给出具体的参数值。

等效开路电容定义为:C=P/(fU)式中:P——IC所耗散的总瓦数;U——IC的最大DC供电电压;f——IC的时钟频率。

电容的容值选择一般取决于电容的谐振频率。

不同封装的电容有不同的谐振频率,下表列出了不同容值不同封装的电容的谐振频率:需要注意的是数字电路的去耦,低的ESR值比谐振频率更为重要,因为低的ESR值可以提供更低阻抗的到地通路,这样当超过谐振频率的电容呈现感性时仍能提供足够的去耦能力。

降低去耦电容ESL的方法去耦电容的ESL是由于内部流动的电流引起的,使用多个去耦电容并联的方式可以降低电容的ESL影响,而且将两个去耦电容以相反走向放置在一起,从而使它们的内部电流引起的磁通量相互抵消,能进一步降低ESL。

(此方法适用于任何数目的去耦电容,注意不要侵犯DELL公司的专利)IC去耦电容的数目选择在设计原理图的时候,经常遇到的问题是为芯片的电源引脚设计去耦电容,上面已经介绍了去耦电容的容值选择,但是数目选择怎么确定呢?理论上是每个电源引脚最好分配一个去耦电容,但https:///cgi-bin/appmsg?t=media/appmsg_edit&action=edit&type=10&isMul=1&isNew =1&lang=zh_CN&token=1045897676是在实际情况中,却经常看到去耦电容的数目要少于电源引脚数目的情况,如freescale提供的iMX233的PDK原理图中,内存SDRAM 有15个电源引脚,但是去耦电容的数目是10个。

退耦电容的选择和应用

退耦电容的选择和应用(zz)关键词:去耦(decouple)、旁路(Bypass)、等效串联电感(ESL)、等效串联电阻(ESR)、高速电路设计、电源完整性(PI)、信号完整性(SI)高手和前辈们总是告诉我们这样的经验法则:“在电路板的电源接入端放置一个1~10μF的电容,滤除低频噪声;在电路板上每个器件的电源与地线之间放置一个0.01~0.1μF的电容,滤除高频噪声。

”在书店里能够得到的大多数的高速PCB设计、高速数字电路设计的经典教程中也不厌其烦的引用该首选法则(老外俗称Rule of Thumb)。

但是为什么要这样使用呢?各位看官,如果你是电路设计高手,你可以去干点别的更重要的事情了,因为以下的内容仅是针对我等入门级甚至是门外级菜鸟。

做电路的人都知道需要在芯片附近放一些小电容,至于放多大?放多少?怎么放?将该问题讲清除的文章很多,只是比较零散的分布于一些前辈的大作中。

鄙人试着采用拾人牙慧的方法将几个问题放在一起讨论,希望能加深对该问题的理解;如果很不幸,这些对你的学习和工作正好稍有帮助,那我不胜荣幸的屁颠屁颠的了。

首先就我的理解介绍两个常用的简单概念。

什么是旁路?旁路(Bypass),是指给信号中的某些有害部分提供一条低阻抗的通路。

电源中高频干扰是典型的无用成分,需要将其在进入目标芯片之前提前干掉,一般我们采用电容到达该目的。

用于该目的的电容就是所谓的旁路电容(Bypass Capacitor),它利用了电容的频率阻抗特性(理想电容的频率特性随频率的升高,阻抗降低,这个地球人都知道),可以看出旁路电容主要针对高频干扰(高是相对的,一般认为20MHz以上为高频干扰,20MHz以下为低频纹波)。

什么是退耦?退耦(Decouple),最早用于多级电路中,为保证前后级间传递信号而不互相影响各级静态工作点的而采取的措施。

在电源中退耦表示,当芯片内部进行开关动作或输出发生变化时,需要瞬时从电源线上抽取较大电流,该瞬时的大电流可能导致电源线上电压的降低,从而引起对自身和其他器件的干扰。

退耦电容原理--退藕电容的一般配置原则

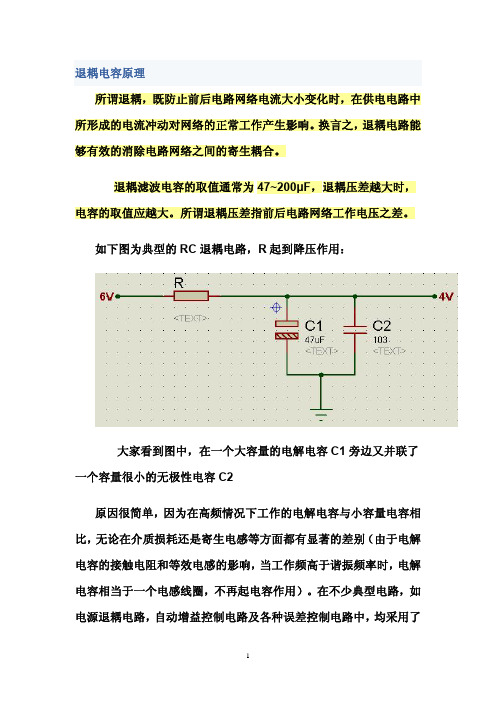

退耦电容原理所谓退耦,既防止前后电路网络电流大小变化时,在供电电路中所形成的电流冲动对网络的正常工作产生影响。

换言之,退耦电路能够有效的消除电路网络之间的寄生耦合。

退耦滤波电容的取值通常为47~200μF,退耦压差越大时,电容的取值应越大。

所谓退耦压差指前后电路网络工作电压之差。

如下图为典型的RC退耦电路,R起到降压作用:大家看到图中,在一个大容量的电解电容C1旁边又并联了一个容量很小的无极性电容C2原因很简单,因为在高频情况下工作的电解电容与小容量电容相比,无论在介质损耗还是寄生电感等方面都有显著的差别(由于电解电容的接触电阻和等效电感的影响,当工作频高于谐振频率时,电解电容相当于一个电感线圈,不再起电容作用)。

在不少典型电路,如电源退耦电路,自动增益控制电路及各种误差控制电路中,均采用了大容量电解电容旁边并联一只小电容的电路结构,这样大容量电解电容肩负着低频交变信号的退耦,滤波,平滑之作用;而小容量电容则以自身固有之优势,消除电路网络中的中,高频寄生耦合。

在这些电路中的这一大一小的电容均称之为退耦电容。

Re: 大电容由于容量大,所以体积一般也比较大,且通常使用多层卷绕的方式制作,这就导致了大电容的分布电感比较大(也叫等效串联电感,英文简称ESL)。

电感对高频信号的阻抗是很大的,所以,大电容的高频性能不好。

而一些小容量电容则刚刚相反,由于容量小,因此体积可以做得很小(缩短了引线,就减小了ESL,因为一段导线也可以看成是一个电感的),而且常使用平板电容的结构,这样小容量电容就有很小ESL 这样它就具有了很好的高频性能,但由于容量小的缘故,对低频信号的阻抗大。

所以,如果我们为了让低频、高频信号都可以很好的通过,就采用一个大电容再并上一个小电容的方式。

常使用的小电容为 0.1uF的瓷片电容,当频率更高时,还可并联更小的电容,例如几pF,几百pF的。

而在数字电路中,一般要给每个芯片的电源引脚上并联一个0.1uF的电容到地(这个电容叫做退耦电容,当然也可以理解为电源滤波电容,越靠近芯片越好),因为在这些地方的信号主要是高频信号,使用较小的电容滤波就可以了。

详细解析电源完整性去耦电容原理及选型

详细解析电源完整性去耦电容原理及选型(电源)完整性在现今的(电子产品)中相当重要。

有几个有关电源完整性的层面:(芯片)层面、(芯片封装)层面、电路板层面及系统层面。

在电路板层面的电源完整性要达到以下三个需求:1、使芯片引脚的电压噪声+电压纹波比规格要求要小一些(例如芯片电源管脚的输入电压要求1V之间的误差小于+/-50 mV)2、控制接地反弹(地弹)(同步切换噪声SSN、同步切换输出SSO)3、降低电磁干扰(EMI)并且维持(电磁兼容)性((EMC)):电源分布(网络)(PDN)是电路板上最大型的导体,因此也是最容易发射及接收噪声的(天线)。

“地弹”,是指芯片内部“地”电平相对于电路板“地”电平的变化现象。

以电路板“地”为参考,就像是芯片内部的“地”电平不断的跳动,因此形象的称之为地弹(ground bounce)。

当器件输出端由一个状态跳变到另一个状态时,地弹现象会导致器件逻辑输入端产生毛刺。

对于任何形式封装的芯片,其引脚必会存在电感(电容)等寄生(参数),而地弹主要是由于GND引脚上的阻抗引起的。

(集成电路)的规模越来越大,开关速度不断提高,地弹噪声如果控制不好就会影响电路的功能,因此有必要深入理解地弹的概念并研究它的规律。

我们可以用下图来直观地解释一下。

图中开关Q的不同位置代表了输出的“0”“1”两种状态。

假定由于电路状态转换,开关Q接通RL 低电平,负载电容对地放电,随着负载电容电压下降,它积累的电荷流向地,在接地回路上形成一个大的(电流)浪涌。

随着放电电流建立然后衰减,这一电流变化作用于接地引脚的电感LG,这样在芯片外的电路板“地”与芯片内的地之间,会形成一定的电压差,如图中VG。

这种由于输出转换引起的芯片内部参考地电位漂移就是地弹。

芯片A的输出变化,产生地弹。

这对芯片A的输入逻辑是有影响的。

接收逻辑把输入电压和芯片内部的地电压差分比较确定输入,因此从接收逻辑来看就像输入(信号)本身叠加了一个与地弹噪声相同的噪声。

去耦电容

在电路设计中,如何选择去耦电容,旁路电容?

检举 | 2011-9-15 12:54 提问者: xpc4dw3sqpz | 浏览次数:882次

我来帮他解答

输入内容已经达到长度限制还能输入 9999 字插入图片删除图片插入地图删除地图插入视频视频地图回答即可得2分经验值,回答被选为满意回答可同步增加经验值和财富值参考资料:匿名回答提交回答取消

2.抑制高频的电感 用粗漆包线穿入轴向有几个孔的铁氧体芯,就构成了高频扼制器件。将其串入电源线或地线中可阻止高频信号从电源/地线引入。这种元件特别适用于隔开一块印制电路板上的模拟电路区、数字电路区、以及大功率驱动区的供电。应该注意的是它必须放在该区储能电容与电源之间而不能放在储能电容与用电器件之间。

请给我一个去耦电容和旁路电容的作用最通俗的解释,谢谢!

检举 | 2012-5-16 14:56 提问者: 我要去鸟巢 | 浏览次数:24次

我来帮他解答

输入内容已经达到长度限制还能输入 9999 字插入图片删除图片插入地图删除地图插入视频视频地图回答即可得2分经验值,回答被选为满意回答可同步增加经验值和财富值参考资料:匿名回答提交回答取消

去藕电容和旁路电容

去藕电容就是起到一个小电池的作用,满足电路中电流的变化,避免相互间的耦合干扰。关于这个的理解可以参考电源掉电,Bulk电容的计算,这是与之类似的。

旁路电容实际也是去藕合的,只是旁路电容一般是指高频噪声旁路,也就是给高频的开关噪声提高一条低阻抗泄防途径。

去耦电路中电容器的使用

去耦电路中电容器的使用去耦电路(Decoupling circuit)是电子设备中常用的一个电路,用于去除电源线上的高频噪声以提供稳定的电源电压。

其主要原理是利用电容器的特性,将高频噪声引导到地,从而实现去噪的效果。

本文将详细介绍去耦电路中电容器的使用。

电容器是一种能存储电荷并在电场中储存能量的被动电子元件。

在去耦电路中,电容器被用于去除电源线上的高频噪声。

因为电容器具有通过直流电流,而阻抗对交流电压具有很低的阻抗特性。

所以,如果在电源线上添加电容器,它将会成为一个开路,直流电流不会通过它,但是高频噪声却容易通过。

为了更好地理解去耦电路中电容器的使用,我们将从以下几个方面进行说明。

1.电容器的选择:在去耦电路中使用的电容器通常选择电解电容器或陶瓷电容器。

电解电容器具有较大的电容值和较低的ESR(Equivalent Series Resistance),适合用于较高的频率范围。

而陶瓷电容器则具有较小的体积和较低的ESR,适合在限制空间中使用。

2.电容器的位置:在去耦电路中,电容器应该尽可能地靠近负载器件,并且与电源线之间应尽可能短距离连接。

这样可以最大限度地降低电源线上的高频噪声。

3.电容器的并联:为了提供更好的去噪效果,可以在电源线上并联多个电容器。

这样可以增加去耦电路的容量,提高噪声频率范围。

4.电容器的容值:电容器的容值决定了去耦电流的大小。

通常情况下,去耦电流的容值应该选择较大,以保证稳定的电源电压。

但是过大的容值可能会增加电容器的成本和尺寸。

5.电容器的电压:在选择去耦电容器时,要确保其额定电压大于电源电压,以防止电容器过压引起故障。

6.电容器的ESR:ESR是电容器内部等效串联电阻。

较低的ESR值能提供更好的工作性能,减少能量损耗。

所以在电容器选择时,要考虑ESR值的大小。

总之,去耦电路中电容器的使用是提高电路性能和稳定性的重要手段。

通过选择合适的电容器类型、容值和并联方式,可以有效降低电源线上的高频噪声,提供清晰稳定的电源电压,确保电子设备的正常工作。

去藕电容 一大一小 总结

总结:1.电源对地常接一大一小的电容(去耦电容)2.由于制作的原因,大电容的分布电感比较大,电感对高频信号的阻抗是很大的,所以,大电容的高频性能不好;小容量电容分布电感很小,这样它就具有了很好的高频性能,但由于容量小的缘故,对低频信号的阻抗大3.大容量电解电容肩负着低频交变信号的退耦,滤波,平滑之作用;而小容量电容则以自身固有之优势,消除电路网络中的中,高频寄生耦合。

4所谓去耦,既防止前后电路网络电流大小变化时,在供电电路中所形成的电流冲动对网络的正常工作产生影响。

换言之,去耦电路能够有效的消除电路网络之间的寄生耦合。

去耦滤波电容的取值通常为47~200μF,退耦压差越大时,电容的取值应越大。

所谓去耦压差指前后电路网络工作电压之差。

耦合电容如何布置?有什么原则?是不是每个电源引脚都要布置一个0.1uF电容,有时看到0.1uF和10uF并联使用,为什么?所谓去耦,既防止前后电路网络电流大小变化时,在供电电路中所形成的电流冲动对网络的正常工作产生影响。

换言之,去耦电路能够有效的消除电路网络之间的寄生耦合。

去耦滤波电容的取值通常为47~200μF,退耦压差越大时,电容的取值应越大。

所谓去耦压差指前后电路网络工作电压之差。

如下图为典型的RC去耦电路,R起到降压作用:大家看到图中,在一个大容量的电解电容C1旁边又并联了一个容量很小的无极性电容C2原因很简单,因为在高频情况下工作的电解电容与小容量电容相比,无论在介质损耗还是寄生电感等方面都有显著的差别(由于电解电容的接触电阻和等效电感的影响,当工作频高于谐振频率时,电解电容相当于一个电感线圈,不再起电容作用)。

在不少典型电路,如电源去耦电路,自动增益控制电路及各种误差控制电路中,均采用了大容量电解电容旁边并联一只小电容的电路结构,这样大容量电解电容肩负着低频交变信号的去耦,滤波,平滑之作用;而小容量电容则以自身固有之优势,消除电路网络中的中,高频寄生耦合。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

去耦电容的选择

在高速时钟电路中,尤其要注意元件的RF去耦问题。

究其原因,主要是因为元件会把一部分能量耦合到电源/地系统之中。

这些能量以共模或差模RF的形式传播到其他部件中。

陶瓷片电容需要比时钟电路要求的自激频率更大的频率,这样可选择一个自激频率在10~30 MHz,边沿速率是2 ns或者更小的电容。

同理可知,由于许多PCB的自激范围是200~400 MHz,当把PCB 结构看做一个大电容时,可以选用适当的去耦电容,增强EMI的抑制。

表5-1和表5-2所示给出了电容选择方面有用的数据。

从这两个表中,可以知道由于引线中不可避免存在较小电感,表面安装元件具有更高的(大约两个数量级)自激频率。

铝电解电容不适用于高频去耦,主要用于电源或电力系统的滤波。

由实际经验可知,选择不同去耦电容的依据,通常是根据时钟或处理器的第一谐波来选择。

但是,町电流是由3次或5次谐波产生的,此时就应该考虑这些谐波,采用较大的分立电容去耦。

在达到200~300 MHz以上频率的电流工作状态后,0.1μF 与0.01μF并联的去耦电容由于感性太强,转换速度缓慢,不能提供满足需要的充电电流。

在PCB上放置元件时,必须提供对高频RF的去耦。

必须确保所选去耦电容能满足可能的要求。

考虑自激频率的时候需要考虑对重要谐波的抑制,一般考虑到时钟的5次谐波。

以上这些要点对高速时钟电路尤为重要。

对去耦电容容抗的计算是选择去耦电容的基础,表示为

其中,Xc是容抗(Ω);f是谐振频率(Hz);C为电容大小。

选择去耦电容的关键是计算所用电容的容值大小,这里向大家介绍常在高速电路里使用的波形法。

如图1所示,逻辑状态由0转换到1,实际的时钟边沿速率发生了变化。

虽然切换位置仍然保持不变,但t1、t2,已改变,这是因为电容充、放电使信号边沿变化变缓的原因。

图1 时钟信号的容性影响

利用表的公式可以计算图1中的时钟边沿变化率。

在设计时要注意的是,必须确保最慢的边沿变化率不会影响其工作性能。

傅里叶分析可以从时域到频域对信号进行分析。

在射频(RF)频谱分布中,射频能量随频率下降而减少,从而改善了电磁干扰(EMI)的性能。

表电容方程

在计算去耦电容之前,需要先画出戴维宁等效电路。

总的阻抗值等于电路中两个电阻的并联。

假定图2所示的戴维宁等效电路中,ZS=150Ω,Z L=1.0 kΩ,那么

图2 戴维宁等效电路

方法一:在已知时钟信号的边沿速率时,用式(5-9)来计算。

其中,当信号的边沿速率t r,单位为ns时,电容最大值C max,单位为nF;当tr,单位为ps时,C max,单位为pF;R1为网络的总电阻,单位为Ω。

由式(5-9)可知,必须选择适当的电容,使当t r=3.3RC时满足信号上升/下降沿的需要。

选择不当会引起基线漂移。

这里的基线就是判断逻辑1或0的稳态电平。

3.3是时间常数,其3倍等于一个上升时间。

例:(1)如果设计信号的边沿速率为10 ns,电路等效阻抗为130Ω,计算最大电容值为

(2)某信号上、下沿均为8.33ns:频率为80MHz;R为典型的TTL巴参数33Ω;则tr=tf=3.3 ns(为上、下沿的1/4)。

计算最大电容值为

方法二:首先决定所要滤除的最高频率,然后用式(5-10)获得在最小信号畸变情况下的最大电容值。

例:在Rt=130Ω的情况下,滤除一个50MHz的信号,在忽略源内阻Zc时,求C min。

在使用去耦旁路电容时,需要考虑以下几点:

· 使电容的引线最短,线路电感最小。

· 选择适合的额定电压和介电常数的电容。

· 如果边沿速率的畸变容许3倍于C的大小,应使用大一级的电容标称值。

· 电容安装好后,必须检查是否工作正常。

· 太大的电容会导致信号的过大畸变。