06第六章输入-输出接口

chap6微机原理与接口技术第六章——I、O接口和总线

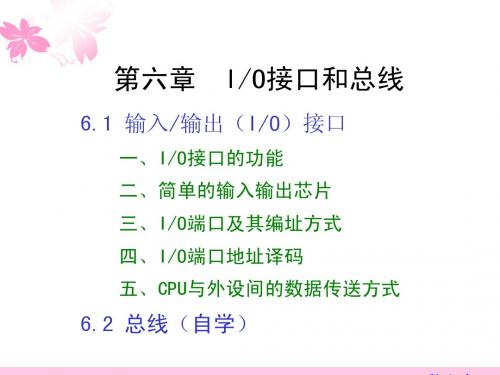

第六章I/O接口和总线本章介绍1.I/O接口I/O接口的功能简单的输入输出接口芯片I/O端口及其寻址方式CPU与外设间的数据传送方式 PC机的I/O地址分配2.总线IBM PC总线AT总线或ISA总线6-1、I/O接口一.I/O接口的功能1.采用I/O接口的必要性计算机和外设之间的信息交换带来一些问题:速度不匹配信号电平不匹配信号格式不匹配时序不匹配因此I/O设备不能直接与CPU的系统总线相连,必须在CPU与外设之间设置专门的接口电路来解决这些问题。

可编程输入输出接口芯片随着大规模集成电路技术的发展,出现了许多通用的可编程接口芯片,可用它们来方便地构成接口电路。

后面几章将介绍常见的可编程I/O接口芯片的原理、编程方法及与CPU的连接方法。

可编程中断控制器8259A可编程计数器/定时器8253可编程外围接口芯片8255A串行通信和可编程接口芯片8253AA/D和D/A转换芯片。

本章介绍最常用的简单I/O接口芯片,主要有缓冲器(Buffer)和锁存器(Latch)。

二、简单的输入输出接口芯片1.缓冲器74LS244和74LS245连接在总线上的缓冲器都具有三态输出能力。

在CPU或I/O接口电路需要输入输出数据时,在它的使能控制端EN(或G)作用一个低电平脉冲,使它的内部的各缓冲单元接通,即处在输出0或1的透明状态。

数据被送上总线。

当使能脉冲撤除后,它处于高阻态。

这时,各缓冲单元像一个断开的开关,等于将它所连接的电路从总线脱开。

74LS244和74LS245就是最常用的数据缓冲器。

除缓冲作用外,它们还能提高总线的驱动能力。

8个三态缓冲单元,分成两组,分别由门控信号为低电平时,数据传送;高电平时,输出高阻态。

单向缓冲器,只能从端。

OE 2.锁存器74LS3731. I/O端口1.数据端口(Data Port)用来存放CPU与外设之间交换的数据,长度一般为1-2个字节,主要起缓冲作用。

2.状态端口(Status Port)用来指示外设的当前状态。

计算机原理 第六章输入输出系统

1

2

3

为保证总线所传输的信息的有效性,总线 信息应具有单一性:在同一时刻至多只能有一 个部件向总线发送信息,但可以有多个部件同 时接收总线信息。

1. 总线电路: 输出挂在总线上的部件需通过“总线电路” 向总线发送信息。

总线电路由三态输出器件(TSL器件)承担。 input TSL control output

1. ISA总线:用于IBM PC/XT 微机系统,(8086),一共62根信号线, 其中20根地址线,8根数据线,4个读写信号,6个中断请求线,3 路DMA请求,还包括时钟、电源线和地等,总线带宽 8.33 MB/s。

2.EISA总线 (80386), 数据线扩展到了32位,带宽达到了33.3MB/s。 3. PCI总线:(Peripheral component interconnection)(外围部 件互连) 总线频率为33 MHZ→66MHZ→133MHZ, 可以直接连接高速外部 设备。 同步时序总线,对地址信号和数据信号分时复用, 64根线,采用集中式的总线仲裁方式。 4.AGP总线(加速图形接口总线) AGP总线把主存和显存连接起来,不再走PCI总线。 5.USB总线(通用串行总线)主要用于连接低速输入输出设备。 带宽为1.5MB/s。

3. 控制总线CB(Control Bus) 控制总线用来传送各类控制/状态信号。

包括I/O读写命令,MEMR/W存储器读写命令,应答信号,总线请求与 总线使用信号,复位信号,时钟信号等。

4. 电源线

许多总线标准中都包含了电源线的定义,主要有+5V逻辑电源;GND逻 辑电源地;-5V辅助电源;±12V辅助电源。

2.计数器查询方式

在计数器查询方式中,总线上的任一设备申请使用总线时,通过 BR线发出总线请求。

微机原理与接口技术_第6章 IO接口

三、I/O端口编址 (续) 2.I/O独立编址(续)

缺点: 专用I/O指令增加指令系统复杂性,且I/O指 令类型少,程序设计灵活性较差; 要求处理器提供MEMR#/MEMW#和IOR#/IOW#两 组控制信号,增加了控制逻辑的复杂性。

三、I/O端口编址 (续)

PC系列微机I/O端口访问 1.I/O端口地址空间

程序控制方式

程序控制方式是指CPU与外设之间的数据传送由程序 控制完成。 程序控制方式又分为无条件传送和条件传送两种 1.无条件传送方式(同步传送) 特点:输入时假设外设已准备好,输出时假设外设 空闲。 要求:输入接口加缓冲器,输出接口加锁存器。 应用:对简单外设的操作。

1. 无条件传送方式(同步传送) 输入接口的设计要求:

寻 址 确定输入端口地址 AB、M/ IO、ALE、DT/R 等待数据输入 等待数据输入 输入缓冲器 读入数据 输入缓冲器 DB CPU

一、 I/O 接口的功能 (续)

3. I/O接口应具有的功能(解决的方案)

1) 设置数据缓冲器以解决两者速度差异所带来的 不协调问题; 输出时: CPU DB 锁存器 输出设备数据线

以上三类信息分别通过各自的寄存器和相应的控制逻辑 来完成信息的传送。通常将这类寄存器和相应的控制逻辑称 为I/O端口。CPU与一个外设之间通常有三个端口。数据端口 (输入/输出);状态端口;控制端口。

二、I/O接口的一般结构 (续) I/O接口组成:接口由接口硬件和接口软件组成。 1.接口硬件

接口

这类接口面对总线,因此要使用三态输出器件; 对于输入信号有记忆功能的一般使用三态门; 对于输入信号无记忆功能的一般还要增加锁存功能;

1. 无条件传送方式(同步传送)

《输入输出接口》课件

01 传输速率

衡量数据传输速度的重要指标,决定设备的数据处 理效率。

02 数据稳定性和可靠性

保证数据传输过程中数据稳定性和可靠性,避免数 据丢失或损坏。

03 兼容性和扩展性

设备与不同设备之间的兼容性,以及接口的扩展性, 是影响设备互通性的重要因素。

总结

输入输出接口在计算机系统中扮演着至关重要的角色,其技 术原理涉及物理连接、通信协议、数据处理和性能指标等多 个方面。只有深入了解和掌握输入输出接口的技术原理,才 能更好地应用于实际生产和工作中。

未来输入输出接口的趋势

个性化定制接 口

根据不同用户需求 定制接口功能

多功能集成接 口

整合多种接口功能, 提升设备性能

01 技术标准的统一和整合

不同设备间的兼容性与统一标准问题

02 硬件与软件协同发展

接口硬件与软件的协同设计与优化

03

创新技术的应用推 不动断探索新技术,推动输入输

出接口的创新与发展

输入输出接口的分类

并行接口

同时传输多个数据 位

通用接口

具有多种功能

串ห้องสมุดไป่ตู้接口

逐位传输数据

● 02

第2章 输入输出接口的技术 原理

输入输出接口的 物理连接

输入输出接口的物理连接包括插口、插槽等连接方式。这 些连接方式在设备之间传输数据起着至关重要的作用,而 接口标准及接口规范则规定了各种设备之间通信的准则和 规范。

输入输出接口的通信协议

数据传输方式

串行传输

通信协议

USB

通信协议

RS232

数据传输方式

并行传输

数据缓冲与缓存

数据缓冲用于临时存储数据, 以平衡不同速度设备之间的数 据传输。缓存则用来提高数据 访问速度和性能。

第六章PL的基本原理及组成

第六章PL的基本原理及组成PL(Programmable Logic)是可编程逻辑器件,是一种集成电路芯片,由逐行可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)两种类型组成。

PL的基本原理是通过组合逻辑和时序逻辑的组合,根据用户的需求进行逻辑运算和控制,实现各种数字电路的功能。

PL器件根据所需要的功能和规模的不同,可以灵活地进行编程和配置。

PL的组成主要包括:1. 逻辑单元(Logic Elements):也称为查找表(Look-up Table),是PL中最基本的组件。

逻辑单元负责实现布尔函数和逻辑运算,每个逻辑单元可以实现多个逻辑门的功能。

2. 管理电路(Routing Circuitry):用于连接逻辑单元之间的信号线,将不同逻辑单元之间的输入和输出进行连接。

3. 配置存储器(Configuration Memory):用于存储逻辑单元的配置信息,包括逻辑单元的功能和连接方式。

配置存储器可以进行编程和擦除,以实现不同数字电路的配置。

4. 输入/输出接口(IO Interface):用于与外部系统进行通信,将外部信号输入到PL中,或将PL中的输出信号输出到外部系统中。

5. 时钟管理电路(Clock Management Circuitry):用于产生和管理时钟信号,控制逻辑单元的时序运算。

6. 测试和调试电路(Test and Debug Circuitry):用于进行PL器件的测试和调试操作,对逻辑运算结果进行验证。

PL的工作过程包括配置和工作两个阶段:1. 配置阶段:将用户设计好的逻辑电路的功能和连接方式编写成其中一种配置文件,通过编程器(Programmer)将配置文件写入配置存储器中。

在配置阶段,配置存储器被编程为实现特定的逻辑功能和连接方式。

2.工作阶段:在配置阶段完成后,PL器件进入工作阶段,根据配置存储器中的配置信息,逻辑单元开始进行逻辑运算和控制。

通过输入接口,PL器件接收外部信号,并根据配置存储器中的配置信息进行逻辑运算,输出结果通过输出接口输出到外部系统中。

第六章 人机交互 — 输入接口

1.6 实验结果

单击全速运行按钮(快捷键F5),程序会运行并停留在main()主函数处; 继续全速运行,在PC机上的“串口调试助手”的发送对话框输入数字,如 下图所示,实验板上的LED亮灭状态随着输入数字的不同发生相应的变化。

二、键盘应用

键盘的用途: 用PC机键盘控制计算机;用手机键盘发送短信息;用遥 控器控制家用电器等等。 键盘是最为直接的控制手段,也是最容易被人们接收的 控制方法。应用键盘可以大大提高应用系统的灵活性和可控 制性。

当PC机发来数据,ARM启动UART0的中断服务程序,把接收的数据放到 KeyCode全局变量中。

UART0中断服务程序

程序中读取宿主机发来的数据,然后把接收的数据处理后,发送 给全局变量KeyCode作为按键值,最后退出中断。 程序清单 UART0中断服务程序

/******************************************************************** * 文件名:UART0_IRQ() * 功能:UART0中断服务子程序 * 全局变量:KeyCode ********************************************************************/ void __irq UART0_IRQ(void) { uint8 Data; Data = U0RBR; // 取得宿主机发来的数据 KeyCode = Data - 0x30; // 把数字字符转换成相应的数字 while((U0IIR & 0x04) == 0x04) Data = U0IIR; // 通过读取U0IIR寄存器来清除中断标志 VICVectAddr = 0 ; // 通知中断结束 }

第六章 IO接口和总线

1、缓冲器 74LS244

单路基本组成:

真值表 A

B

G#

0

A

1

B

1

0 G

1

0

高阻

0

状态

1A1 1A2

/1G 1A1 2Y4 1A2 2Y3 1A3 2Y2 1A4 2Y1 GND

1 2 3 4 5 6 7 8 9 10

1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4

244

20 19 18 17 16 15 14 13 12 11

需要输入设备送入信息,输出设备送出结果,这些输 入输出设备被称为外设。

通信:计算机(CPU)与外设间的数据、状态和控制

命令的交换过程统称为通信。

2、CPU与外设直接通信存在的问题 速度不匹配(CPU快,外设慢) 信号电平不匹配 (CPU使用TTL电平,外设多为机电设备) 信号格式不匹配 (CPU总线上为并行数字量,而外设有串行模拟量等) 时序不匹配 解决方案: 用I/O接口:把外设连接到CPU总线上的一组逻辑电 路的总称。用于协调外设与主机之间的信息交换。

2、译码的常用方法

线选法

利用一根地址线,产生指定的端口地址的选择信号。

A7

PORT1

当A7=1,选中PORT1,地址可为80H 当A6=1,选中PORT2,地址可为40H 当A5=1,选中PORT3,地址可为20H

A6

PORT2

对于PORT1,地址为81H,82H,83H

等仍可选中。

A5

PORT3

无条件输出电路例子 例:假设该端口号为

0# D0

80H,要想让0、2、4、

6号灯亮,如何编写

D1

1D 2D

第六章模拟量输入输出接口

捕捉时间/保持下降率与Ch有关;Ch最好为聚苯/聚 四氟乙烯电容。

微机系统与接口

东南大学 36

生产过程微机控制系统结构

微机系统与接口

东南大学 30

采样/保持器(Sample/Holder)

作用:解决快变模拟信号的AD转换问题 使转换误差小于量化误差(书P395计算)

常用S/H芯片 LF1/2/398, AD582K 主要参数:

工作电压;捕捉时间;输入电阻;输出电阻; 功耗

微机系统与接口

东南大学 31

逐次比较模数转换器ADC

AD574转换时序

微机系统与接口

东南大学 19

读AD574转换结果时序

微机系统与接口

东南大学 20

AD574A应用——接口(也可参考书P400)

微机系统与接口

东南大学 21

AD574A应用——控制信号

控制信号——由地址译码电路产生

使R/C=0,启动A/D转换 ——地址译码输出DR0控制

(转换完)读入高4位 ——地址译码输出DR1控制

Is(off) 漏电流。 在开关断开时,仍有电流通过开关(0.2~2nA)

Iout(off) 开关断开时,输出端的电流。(1~10nA) ton(μs) 选通信号EN达到50%到开关接通的时间延 迟。(0.8μs) ts 选通信号EN达到50%到开关断开时的延迟。

微机系统与接口

东南大学 29

MUX主要性能参数(续)

JNZ TEST ;未转换完,再测试

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

输入/输出指令

❖ IN输入指令

❖ 直接端口寻址方式

❖格式: IN AL(或AX),PORT ❖操作: (AL字节或AX字)(PORT)

例 取端口61H的内容. IN AL,61H ;取数据 MOV BL,AL ;放入BL中

16

❖ 间接端口寻址方式

❖格式: IN AL(或AX),DX ❖操作: (AL字节或AX字)((DX))

❖ I/O端口地址是绝对地址,并不分段。 ❖ I/O指令都不影响标志位。

20

表6-5 PC/XT机系统板配置的端口地址

地址范围 000H~01FH 020H~03FH 040H~05FH 060H~07FH 0A0H~0BFH 080H~09FH

I/O接口名称 DMA控制器 中断控制器 定时器8253/8254 并行接口芯片8255 NMI屏蔽寄存器 DMA页面寄存器

18

❖ 间接端口寻址方式

❖格式: OUT DX,AL(或AX) ❖操作: ((DX)) (AL字节或AX字)

例 将寄存器BL的数据放入异步串行接口(COM1) 的端口3F8H中. MOV DX,3F8H ;取地址 MOV AL,BL ;取数据 OUT DX,AL ;放入BL中

19

I/O指令的使用规则

0D000H~ 0D0FFH

网络接口控制器(NIC)

计算机的端口地址

22

AEN

A3 A4 A5 A6 A7 A9

A8

74LS04

74LS30

CS

O J10 O O J12 O

图 6-5 可选式译码电路

23

J10通 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1011111000

~

1011111 111

❖ 缺点是:外设占用了内存单元,使内存容量减少。

13

端口寻址的输入输出方式

❖ 外设端口所在空间与存储器空间各自独立。 ❖ 特点:

❖ CPU有专门的I/O指令,用地址来区分不同的外设; ❖ 一个外设往往有多个端口; ❖ 在硬件上,必须用控制线来区分是寻址内存还是外

设。

14

❖ 3. 8086的端口访问 8086/8088采用IN和OUT指令访问端口。

21

地址范围

I/O接口名称

0000H~000FH

DMA控制器

0020H~0021H 0040H~0043H

可编程中断控制器(Programmer

Interrupt Controller) 系统定时器(System Timer )

03F8H~03FFH 0778H~077BH

串行接口1(COM1) 并行接口1(LPT1)

地址为:2F8H-2FFH

24

计算机的输入输出是通过I/O接口来实现的。 ❖ 为什么需要I/O接口?

❖ 各种外设的操作方法不同,由CPU统一控制 不切合实际。

❖ 外设的数据传输速率比存储器和CPU慢,使 得高速总线不能直接与外设相连。

❖ 外设所使用的数据格式、时序等不一致。

3

I/O模块

外部设备

4

I/O模块的一般结构

系统接口

数据线

备 控

外设

←———→ 制

控制联络 器

←———→

6

❖ I/O接口的基本功能

❖ (1)实现主机和外围设备之间的数据传送控制.

其中包括同步控制,设备选择和中断控制等.DMA还具有 直接访问存储器功能,并给出存储器地址.

❖ (2)实现主机同外围设备之间的数据缓冲.

在数据传送过程中,先将数据送入数据缓冲寄存器,然后 再送到目的设备(输出)或主机(输入).

例 取异步串行接口(COM1)的端口3F8H的内容. MOV DX,3F8H ;取地址 IN AL,DX ;取数据 MOV BL,AL ;放入BL中

17

❖ OUT输出指令

❖ 直接端口寻址方式

❖格式: OUT PORT,AL(或AX) ❖操作: (PORT) (AL字节或AX字)

例 将寄存器BL的数据放入端口61H中. MOV AL,BL ;取数据 MOV 61H,AL ;放入61H中

❖ ⑵按照数据传送的控制方式可分成程序控制输入输 出接口、程序中断输入输出接口和直接存储器存取 (DMA)接口等。

8

❖ 2. I/O设备的编址方式

❖ I/O设备的编址

❖为了CPU便于对I/O设备进行寻址和选择, 必须给众多的I/O设备进行编址,也就是给 每一台设备规定一些地址码。

9

❖有两种寻址方法Biblioteka ❖ I/O端口与CPU之间的数据通信都是通过这两个指 令实现的。

❖ I/O端口使用16位二进制编址,端口地址从0000H 到FFFFH。

❖ 前256个端口(0000H-00FFH)可以使用直接端口 寻址和间接端口寻址两种方式;当端口号大于255 时( 0100H-FFFFH)必须使用间接端口寻址方式。

数据寄存器 状态/控制寄存器

地址线 控制线

I/O 逻辑

外设接口

外部设备 界面接口

…...

外部设备 界面接口

数据 状态 控制

数据 状态 控制

5

接口与主机、外设间的连接

主机

系统接口 地址信息 —————→

数据(并) ←————→

控制联络信息 ←————→

接口

外设识别

数据/命令/状态

控制电路

设备接口

设

数据(并/串)

微机接口技术

第六章 输入/输出接口

一个简单的微机系统需要CPU、存储器、 基本的输入/输出系统以及将它们连接在一 起的各种信号线和接口电路。

外部设备通过接口电路和系统总线相联, 接口电路的作用是把计算机输出的信息变成 外设能够识别的信息,把外设输入的信息转 化成计算机所能接受的信息。

2

❖ 1. I/O接口的基本概念

10

输入输出设备 硬盘控制器 软盘控制器 单色显示器/并行打印机 彩色图形显示器 异步通信控制器

占用地址数 地址码(16进制)

16

320~32FH

8

3F0~3F7H

16

3B0~3BFH

16

3D0~3DFH

8

3F8~3FFH

11

FFFFFH

内存空间

供 I/O 接 口使用

FFFFFH

内存空间 1M

I/O 空间 FFFFH

❖ (3)接受主机的命令,提供设备接口的状态,按照主机 的命令控制设备.

❖ (4)设置信号电平、信息转换与提供地址译码电路.

7

❖ I/O接口类型

❖ ⑴按照数据传送的宽度可分为并行接口和串行接口.

❖ 并行接口中,设备和接口是将一个字节(或字)的所有位同 时传送.

❖ 串行接口中,设备和接口间的数据是一位一位串行传送的, 而接口和主机之间是按字节或字并行传送. 接口要完成数 据格式的串—并变换.

⑴专设I/O指令.

例指令IN完成输入,指令OUT完成输出操作.其地址码 指出I/O设备的设备代码. 这是I/O空间独立于存储器空间 的情况,即设备码的编码和存储器的存储单元的编码是平 行存在的.

⑵利用访问存储器指令完成I/O功能.

使用这种方法时,从主存的地址空间中分出一部分地 址码作为I/O的设备代码,当访问到这些地址时,表示被访 的不是主存储器,而是I/O设备寄存器(例如,设备的数据缓 冲器或设备的状态寄存器). 这时I/O空间和存储器空间是 合在一起的,即I/O设备和存储单元是统一编址的.

00000H

00000H

0000H

(a)存储器映射方式示意图

(b)I/O 映射方式示意图

图6-4 I/O 映射方式和存储器映射方式的示意图

12

存储器对应输入输出方式

❖ 把一个外设端口作为存储器的一个单元来对待, 故每个外设端口占有存储器的一个地址。

❖ 其优点是:

❖ CPU对外设的操作可使用全部的存储器操作指令; ❖ 不需要专门的输出输出指令及控制信号。