对布尔代数中卡诺图的研究

离散数学中的布尔函数与卡诺图

离散数学是数学的一个分支,研究的是离散结构和离散型对象的性质。

其中,布尔函数是离散数学中的重要概念之一,而卡诺图则是布尔函数的一种可视化工具和简化方法。

布尔函数是指由布尔代数中的逻辑运算(如与、或、非)构成的函数。

它将一组布尔变量映射到布尔值的集合上。

布尔函数的输入和输出都只能是0(假)和1(真)。

布尔函数在电子电路设计、计算机科学、密码学等领域有着广泛的应用。

在离散数学中,我们通常用真值表来表示布尔函数,并通过逻辑运算的组合来描述其性质。

然而,随着布尔函数的规模增大,真值表的表示变得复杂而不直观。

卡诺图(Karnaugh Map)成为一种常用的工具,用于优化和简化布尔函数的表示。

卡诺图是由一张由2的幂次方的格子组成的表格构成,表格的每个格子表示布尔函数的一个可能输入组合。

通过将真值表中的不同输入组合映射到卡诺图的格子上,并将对应的输出值填入格子中,我们可以更加直观地观察和分析布尔函数的模式。

利用卡诺图,我们可以进行布尔函数的最小化和化简操作。

最小化操作是指通过合并相邻格子中具有相同输出值的格子,从而得到一个更简洁的布尔函数表示。

而化简操作是指通过合并相邻格子中具有相同输入变量的格子,从而得到一个更简洁的真值表表示。

卡诺图的使用规则是相邻格子之间仅有一个变量取值不同。

通过观察这种变化的模式,可以找到多个相邻格子可以合并的可能。

通过将相邻格子合并,我们可以得到一个更简化的布尔函数或真值表表示,从而减少计算复杂度。

卡诺图的优点是直观且易于理解。

通过观察格子的组合模式,我们可以更容易地理解和分析布尔函数的性质。

此外,卡诺图还可以用于表示多个布尔函数之间的关系,进一步帮助我们进行逻辑分析和优化。

总结来说,离散数学中的布尔函数与卡诺图是相辅相成的概念。

布尔函数作为离散数学中的重要概念,用于描述逻辑运算和电子电路的行为。

而卡诺图作为布尔函数的可视化工具和简化方法,帮助我们更直观地观察和分析布尔函数的模式,进而进行最小化和化简操作。

卡诺图 集成电路 外特性

= ∑m(0,1,3,5,6,9,11,13)

(2)填:把1填入到卡诺图中与这些最小项对应的方格内

F CD 00 AB 00 1 0

01

11 10 01 11 10 2

1 1

15 1 13 19

13

7

15

4

12 8

16

14 10

卡诺图表示的逻辑函数

111

1.4.3 卡诺图化简逻辑函数

★提示: ①逻辑函数为最小项表达式,则省变直接填;

C AB 00 01 11 0 0 2 1 1 3 7 5

1、定义:卡诺图是最小项按一定规律排列而成的方格图。

C

AB 00

0 ABC m0 ABC m2 ABC m6

ABC m4

1

ABC m1 ABC m3

ABC m7 ABC m5

6

4

三变量 (a)

01 11 10

三变量 (b)

10

2、结构与特点 (1)二进制数据标注:

回顾

利用布尔代数化简逻辑函数 基本公理 基本规则 化简方法

并项法 吸收法 消去法 配项法

最简形式

第一章 开关理论基础

数制与编码 逻辑函数 布尔代数 卡诺图 集成门电路的外特性

1.4.1 最小项的基本概念

一、定义及其性质

1、定义:n变量逻辑函数中,m为包含n个因子的乘积 项,且n个变量均以原变量或反变量的形式在m中仅出 现一次,则m为该组变量的最小项。最小项的个数为2n。 最小项可以编号,记作mi。

2、化简步骤

变

填

圈

简

表示逻辑函数

化简逻辑函数

多变量卡诺图化简的算法实现

多变量卡诺图化简的算法实现汪靖;林植【摘要】提出了一种对包含任意多个变量的卡诺图进行化简的算法,给出了算法整体设计流程图以及关键函教伪代码.借助计算机实现多变量卡诺图的化简,为后续工程系统的设计分析提供了可靠依据.【期刊名称】《智能计算机与应用》【年(卷),期】2010(000)002【总页数】3页(P75-77)【关键词】布尔代数式;多变量;卡诺图;算法【作者】汪靖;林植【作者单位】【正文语种】中文【中图分类】TP3021 算法介绍布尔代数式化简的原则是逻辑电路所用的门电路最少,各个门电路的输入端最少,表现在布尔代数式化简中就是使用尽可能少的布尔变量表示布尔代数式。

使用卡诺图化简得到的最简布尔代数式可以用与或式、或与式和无反变量形式表示[1]。

仅以与或式为例进行算法描述,其他两种形式可以在此基础上稍加修改。

1.1 化简原理假设需化简的逻辑表达式A中含有m个逻辑项ai(i为整数,0≤i≤m),其中ai 由若干个布尔变量组成,记为x0x1…xn。

例如:逻辑表达式图1 逻辑表达式A的卡诺图卡诺图化简的基本原理是合并A中所有相邻项,使得布尔变量数最少。

所谓相邻项是指在两个逻辑项中,除某个对应位布尔量相反外,其余对应位都相同的项[2,3]。

例如,逻辑项a0=0000和a1=0001相邻,可以合并为000*,合并时相异位用“*”作标记,从组成形式上可以看出000*消去了一个逻辑变量。

1.2 算法分析根据卡诺图的标注方式和化简表达式的基本原理,算法分四个步骤实现。

(1)求出各项的相邻项。

从a0开始,依次求出ai在A中出现的各相邻项。

(2)合并相邻项。

首先将ai依次与其各相邻项aj合并新的逻辑项bt,此处相异位可以是0与1相异、0或1与*相异。

其次,将ai和aj作为bt的源项。

如果ai或aj本身已由其他逻辑项合并而来,则将ai或aj的源项替代ai或aj。

最后,为了与未合并项区别,将已参与合并的逻辑项ai、aj及各自源项的合并次数分别增加1。

卡诺图应用研究

卡诺图应用研究摘要在对卡诺图的应用上,由于很多课本都很零散地作了分析,而且是本着用到提到,不用不提的思想。

为此,本文针对卡诺图应用研究作出了较为系统的总结。

采取由易到难,由一方面到多方面的应用分析。

通过系统总结,可以让读者更为直观,全面的认识卡诺图,了解卡诺图,应用卡诺图。

关键词卡诺图;逻辑函数;最小项Abstract: this paper summarized the applied research of the Karnaugh map more systematically. This paper analyzed the application from easy to difficult, on the one hand to a wide range. Systematic summary to give readers a more intuitive and comprehensive understanding of the Karnaugh map for the Karnaugh map, the application Karnaugh map.Key words: Karnaugh map; logic function; minterm 中图分类号:TP33文献标识码:A文章编号:2095-2104(2012)02-随着数字技术的快速发展,现代电子设备已经从模拟化向数字化转变。

目前,大多数电路只在信号采集、微弱信号放大、高频大功率输入等局部采用模拟电路,其余部分广泛采用数字技术及数字处理电路。

因此,对数字电路的分析与研究成为电子工程技术人员必须掌握的知识。

在数字电子技术中数字逻辑电路的设计是非常重要的,而卡诺图在逻辑电路设计中又起到非常重要的作用,所以本文对卡诺图的应用作出进一步的分析与讨论。

1 逻辑函数卡诺图运用代数法化简逻辑函数时,必须熟练掌握逻辑代数的基本公式并具备一定的技巧。

对布尔代数中卡诺图的研究

第25卷第3期合肥工业大学学报(自然科学版)Vol.25No.3 2002年6月JOURN AL OF HEFEI U NIVERSITY OF T ECH NOLOGY Jun.2002对布尔代数中卡诺图的研究方志鸣(黄山学院物理系,安徽黄山 245021)摘 要:由于卡诺图具有几何相邻与逻辑相邻之间的良好对应关系,故在布尔代数中得到广泛应用,文章分析了传统卡诺图在简化多变量(n>5)函数时,其对应关系所面临的困难,提出三维卡诺图及卡诺图阵列的概念。

采用适当的排列方式可将图中几何相邻与逻辑相邻的对应项增加到6个以上,为了使其具有实用性,又引入一定的画图规则,对三维卡诺图加以改进,并举例说明它们的使用方法。

结果表明,采用该方法对六变量至八变量的逻辑函数进行综合化简时,仍具有简便直观、可靠性高及易操作等优点,且有较好的实用价值。

关键词:几何相邻;逻辑相邻;三维卡诺图;卡诺图阵列中图分类号:O153.2 文献标识码:A 文章编号:1003-5060(2002)03-0455-04Research on Karnaugh map in Boolean algebraFANG Zhi-ming(Dept.of Physics,Huan gshan College,Huangsh an245021,China)Abstract:Karnaug h map can be used larg ely in Boo lean alg ebra because it has fine correspondence be-tw een adjacency on g eo metr y and adjacency on log ic.In this paper,the difficulty of co rrespondence in sim plifying the m ultiple-variable(n>5)function w ith the traditional Kar naugh map is analyzed,and the concepts o f three-dimensional Karnaug h map and Karnaugh map array are proposed.By using pr oper range,the correspondence term s betw een adjacency on geom etry and adjacency on logic can in-crease to six or more in the map.Some pictorial rules are adopted,and the three-dim ensional Kar-naugh map is improved for practicality o f the map,and the usag e o f the im pro ved map is illustrated w ith examples in the paper.T he lo gic functions of six to eight variables ar e simplified and sy nthesized by using the improved m ap.The r esult show s that the presented m ethod has the advantages of sim-plicity,intuition,g ood reliability and easy operation,so it is valuable in practical use.Key words:adjacency on geometry;adjacency on logic;three-dimensional Kar naugh map;Karnaugh map array在有关文献[1~4]中,使用卡诺图时只讨论到四变量为止,因为通常画出的五变量及五变量以上的卡诺图用来化简逻辑函数时,已逐渐失去了简便直观的优点,故应用较少。

数电逻辑代数化简技巧

数电逻辑代数化简技巧

数电逻辑代数化简是在数字电路设计中常用的一种技巧,通

过化简布尔代数表达式,可以简化电路的结构,减少器件的数量,提高电路的性能。

以下是数电逻辑代数化简的一些常见技巧:

1.逻辑运算律:逻辑运算律是化简布尔代数表达式的基础,

包括交换律、结合律、分配律、德摩根定律等。

熟练掌握这些

运算律可以帮助我们快速进行化简。

2.卡诺图法:卡诺图是一种图形化的工具,用于帮助我们分

析和化简布尔代数表达式。

通过将变量的状态进行排列组合,

并将对应结果写入卡诺图中,可以找出表达式中的最小项或最

小项组合,从而进行化简。

3.最小项和最大项:在代数化简中,我们常常使用最小项和

最大项来表示布尔代数表达式。

最小项是指在布尔代数表达式

中只有一个变量为真,其他变量为假的项。

最大项则是在布尔

代数表达式中只有一个变量为假,其他变量为真的项。

4.公式规则:我们可以根据特定的公式规则进行化简。

例如,若两个最小项仅相差一个变量的状态,则可以使用合并法则将

它们化简为一个更简单的布尔表达式。

5.真值表法:对于复杂的布尔表达式,我们可以先构造出真值表,然后根据真值表的规律进行化简。

这种方法适用于表达式较为复杂的情况,但相对于其他方法来说,计算量较大。

总而言之,数电逻辑代数化简是一种对布尔代数表达式进行简化的方法,在数字电路设计中有着重要的作用。

准确应用这些化简技巧,可以帮助我们简化电路结构,提高电路性能,以及减少成本和故障率。

第七讲 卡诺图

000 010 110 011 111

m0 m2 m6 m3 m7

卡诺图

卡诺图是真值表的另一种形式,可以帮助是图形 化相邻

– 有利于使用结合定理

A 0 1

0 1

A 0 1 0

2 3

B 0 1 0 1

F 1 0 1 0

B

1 1 0

0 0 1 1

12

2和3个变量的卡诺图

A A B ABC ABC ABC ABC

价廉物美的计算设备人的计算方法计算方法描述输入输出行为数据编码真值表优化的组合电路和之积pos积之和sop布尔函数开关电路逻辑门电路逻辑门的实现逻辑映射综合分析应用问题文字规范说明开关电路andornandorandnor其它andorinv功能描述开关函数真值表时序图其它soppos最小项范式最大项范式开关函数化简

23

例3的卡诺图

f(A,B,C,D) = m(1,2,4,6,9)

Step 2 AB CD

0

A 01 11

12 8

00

4

10 Step 1

00

1 5

1

13 9

01

3

1

7 15 11

1 D

11 C 10

2 6 14 10

1

1 B

Step 3

24

卡诺图化简指导原则

n变量卡诺图中的每个单元都有n个逻辑相邻的单 元。 单元可以被合并为大小为 2,4,8,…,2k 的组。 每个被合并组中包含的所有单元都对一些变量有 相同的值。 合并尽可能多的单元,这将导致组所对应的项内 字母的个数最少(扇入)。 尽可能用最少的组覆盖所有的最小项,这将导致 结果中包含最少的积项(门数和最后一级或门的 扇入)。 应该从最“孤立”单元开始。

离散数学中的布尔函数与卡诺图简化

在离散数学中,布尔函数与卡诺图简化是一种重要的方法,用于简化复杂的布尔函数表达式。

布尔函数是由逻辑运算符组成的函数,其值只能为0或1。

而卡诺图是一种图形化的工具,用于展示布尔函数的真值表和简化布尔函数的过程。

通过利用布尔函数和卡诺图简化方法,我们可以将复杂的逻辑问题转化为简单的布尔运算,提高了逻辑电路设计的效率。

首先,我们需要了解布尔函数的基本概念和运算规则。

布尔函数由不同的逻辑运算符组成,如与(AND)、或(OR)、非(NOT)等,通过这些运算符可以将多个输入变量映射到一个输出变量。

布尔函数的真值表展示了各种输入组合对应的输出结果。

但是,当布尔函数的输入变量较多时,真值表会变得非常庞大,难以进行分析和简化。

这时,卡诺图的方法就派上了用场。

卡诺图是由一些方格组成的二维矩阵,在每个方格中填写布尔函数的真值。

卡诺图通过将相邻的1组合成最大的尽量少的项来简化布尔函数。

相邻的1指的是在卡诺图中相邻的方格上的1。

我们可以通过观察并合并相邻的1来减少布尔函数的项数,从而简化布尔函数。

这种简化过程是基于布尔函数的特性和运算规则进行的。

卡诺图简化方法的核心思想是找到最小项或最大项的组合,使得布尔函数的项数减少到最低。

布尔函数的项数越少,逻辑电路设计的复杂度就越低,设计效率就越高。

通过合并相邻的1,我们可以将多个项合并成一个更简单的项,从而减少布尔函数的项数。

卡诺图的布局方式影响了项的合并方式,实际中有两种典型的布局方式:标准布局和格雷布局。

标准布局是将卡诺图每行或每列的邻接位的不同变量值用灰码表示,而格雷布局是将卡诺图每行或每列的相邻位的不同变量值用灰码表示。

使用不同的布局方式会对卡诺图的合并结果产生一定的影响,因此在实际应用中需要根据具体情况选择合适的布局方式。

布尔函数的简化不仅可以提高逻辑电路设计的效率,还可以减少电路的面积和功耗。

随着电子技术的不断发展,电路的面积和功耗成为了设计者需要考虑的重要因素。

通过使用布尔函数和卡诺图简化方法,可以将复杂的逻辑电路简化为更小、更节能的电路,从而提高整体系统的性能和可靠性。

布尔代数在数电优化中的应用

布尔代数在数电优化中的应用布尔代数是一种用于描述和分析逻辑关系的数学工具,它在数电电路的优化中扮演着重要的角色。

通过布尔代数的运算和化简方法,可以简化和优化电路的设计,提高电路的性能和效率。

本文将探讨布尔代数在数电优化中的应用。

一、布尔代数的基本概念和运算法则布尔代数是基于两个值(真和假)的二值逻辑系统。

在布尔代数中,引入了逻辑运算符(与、或、非)和逻辑常数(真、假)来描述逻辑关系。

与(AND)运算符表示逻辑与的关系,当且仅当两个输入都为真时,输出结果才为真。

或(OR)运算符表示逻辑或的关系,当且仅当至少一个输入为真时,输出结果才为真。

非(NOT)运算符表示逻辑非的关系,当输入为真时,输出结果为假;当输入为假时,输出结果为真。

利用这些运算符,可以通过布尔代数的运算法则进行复杂逻辑表达式的化简和优化,从而使电路的设计更加简洁高效。

二、布尔代数在逻辑电路的优化中的应用逻辑电路是由逻辑门组成的,逻辑门实现了不同的逻辑功能。

在设计逻辑电路时,通过运用布尔代数的方法,可以对逻辑门的结构进行优化,以提高电路的性能和效率。

1. 逻辑表达式的化简通过使用布尔代数的运算法则,可以对逻辑表达式进行化简。

化简后的逻辑表达式具有更简洁的结构,减少了电路中的元件数量和逻辑门的级数,从而提高了电路的运行速度和性能。

2. 最小项和最大项在布尔代数中,最小项指的是满足函数的真值表中只有一个输出是真,其余输出皆为假的项。

最大项则是只有一个输出是假,其余输出都为真的项。

通过找出逻辑函数的最小项或最大项,可以更加方便地对逻辑电路进行优化设计。

3. 卡诺图法卡诺图是一种用于化简布尔代数表达式的图形工具。

通过将逻辑函数转化为卡诺图,可以直观地找出逻辑表达式的最小项和最大项,进而对逻辑电路进行优化。

卡诺图法能够避免繁琐的运算过程,提高了化简的效率。

4. 辅助变量方法在布尔代数的运用中,引入辅助变量可以简化逻辑电路的设计。

通过添加辅助变量,可以将原有复杂的逻辑函数分解成多个简单的逻辑函数,从而减少了电路中的逻辑门数量,提高了电路的性能和容错性。

卡诺定理的简单证明

卡诺定理的简单证明一、背景介绍1.1 卡诺定理的定义在电子系统设计与分析中,卡诺定理是一种用于简化布尔函数表达式的方法。

它可以将复杂的布尔函数通过逻辑操作简化为最简形式,从而减少电路的逻辑门数量,提高电路效率。

1.2 卡诺图的概念卡诺图是一种用于表示布尔函数的图形工具。

它通过在二维平面上绘制布尔函数取值为1的区域,并根据布尔函数的特性进行拓展,最终得到最简形式。

二、卡诺图的绘制2.1 布尔函数的真值表首先,我们需要根据给定的布尔函数,列出其真值表。

真值表是一个将所有可能的输入组合对应的输出列出来的表格。

例如,我们考虑一个三变量的布尔函数F(A, B, C),其真值表如下:A B C F0 0 0 10 0 1 00 1 0 10 1 1 11 0 0 01 0 1 11 1 0 01 1 1 12.2 绘制卡诺图接下来,我们将根据真值表的结果来绘制卡诺图。

卡诺图的绘制要求相邻格子中只能有一位二进制数不同。

对于三变量的布尔函数,我们可以绘制一个4格的卡诺图,如下所示:C\AB00 | 01 | 11 | 10----|----|----|----0 | - | X | 1 | -----|----|----|----1 | 0 | X | 0 | -绘制卡诺图的步骤是将真值表中取值为1的格子画上1,并根据布尔函数的特性进行格子的拓展。

2.3 写出卡诺图的最简形式通过观察卡诺图,我们可以找到布尔函数的最简形式。

最简形式是指将卡诺图中的格子进行合并,发现规律,并写出化简后的布尔函数。

根据前述卡诺图的示例,我们可以观察到以下合并规律: - 位1和位2合并:A’BC - 位3和位4合并:AC’因此,布尔函数F(A, B, C)的最简形式为:F = A’BC + AC’三、卡诺定理的证明接下来,我们将使用卡诺定理证明上述布尔函数的最简形式。

根据卡诺定理的定义,对于一个n变量的布尔函数,可以通过将相邻格子划线的方式,将布尔函数转化为最简形式。

卡诺图法在《离散数学》教学中的应用

卡诺图法在《离散数学》教学中的应用[摘要] 本文主要阐述了卡诺图法在《离散数学》教学中的几个具体应用,诸如如何利用卡诺图表示或化简命题公式、求解公式的主析(合)取范式、化简布尔代数以及证明布尔恒等式等。

[关键词] 卡诺图命题公式卡诺圈布尔代数范式离散数学是以研究离散量的结构和相互间的关系为主要目标,其研究对象一般是有限个或可数个元素。

因此,它充分描述了计算机科学离散性的特点,是计算机科学中基础理论的核心课程。

由于离散数学具有很强的逻辑推理性,因而卡诺图可以用来表示或化简命题公式、求解公式的主析(合)取范式、化简布尔代数以及证明布尔恒等式等。

一、用卡诺图表示命题公式具体做法是,根据命题公式所包含的命题变元数目,先画出相应的极小项卡诺图;然后,将公式中包含的极小项,在卡诺图对应的方格中填上“1”;公式中不包含的极小项方格中填上“0”或不填,所得图形就是该命题公式的卡诺图。

【例题1】用卡诺图表示下列命题公式(1)A=﹁(P→Q)(2)B=(﹁P∧Q)→R【解】(1)A是一个二变元命题公式,先画好二变元极小项卡诺图,然后在A包含的极小项对应的方格中填上“1”(见图1)。

公式A的极小项表达式为:A=P∧﹁Q(2)B是一个三变元命题公式,除画好二变元极小项卡诺图外(见图2),还需将公式展示成极小项表达式为:B=(﹁P∧﹁Q∧﹁R)∨(P∧Q∧﹁R)∨(﹁P∧﹁Q∧R)∨(P∧﹁Q∧﹁R)∨(﹁P∧Q∧R)∨(P∧﹁Q∧R)∨(P∧Q∧R)二、用卡诺图化简命题公式或布尔代数通常的化简步骤是:1.画出命题公式或布尔代数的卡诺图。

2.对卡诺图中的1方格画卡诺圈。

(1)在满足合并条件下,卡诺圈应尽可能大;(2)在覆盖所有1方格的前提下,卡诺圈的个数应尽可能少;(3)每个1方格可根据合并的需要被多个卡诺圈包含,但至少被一个卡诺圈包含。

3.将卡诺图上的所有卡诺圈对应的“合取”项相“析取”,便可得到命题公式或布尔代数的最简表达式(可能有多个)。

布尔代数在数电优化中的应用

布尔代数在数电优化中的应用布尔代数是数学中的一种代数系统,广泛应用于逻辑电路和计算机科学领域。

在数电(数字电路)优化中,布尔代数起到至关重要的作用。

本文将探讨布尔代数在数电优化中的应用。

一、布尔代数的基本概念布尔代数是由英国数学家乔治·布尔(George Boole)在19世纪提出的一套逻辑系统。

它以真(1)和假(0)为基础,通过逻辑运算符(如与、或、非)对逻辑表达式进行处理。

布尔代数的基本运算规则包括交换律、结合律、分配律等,这些规则为优化数电电路提供了方法和依据。

二、布尔代数在数电优化中的应用1. 逻辑函数化简在数电电路设计中,逻辑函数往往非常复杂,包含大量的逻辑运算。

布尔代数可以通过逻辑运算符和基本规则对逻辑函数进行简化和优化,从而减少电路中的器件数量和功耗。

例如,使用布尔代数的定理和规则,可以将冗长的逻辑函数化简为更简洁的形式,从而提高电路的效率和可靠性。

2. 逻辑门的设计逻辑门是数字电路的基本构建模块,包括与门、或门、非门等。

通过布尔代数的运算规则,可以将复杂的逻辑功能实现为简单的逻辑门的组合。

例如,使用布尔代数可以设计出多路选择器、加法器、多功能逻辑单元等高级逻辑门,从而满足复杂电路的需求。

3. 逻辑电路的最小化在数字电路中,最小化逻辑电路的数量和延迟是优化电路性能的关键。

布尔代数可以通过不断应用简化规则,实现电路的最小化。

通过减少逻辑门的数量和电路路径的长度,可以提高电路的响应速度、降低功耗,并减少电路的复杂性。

4. 真值表分析真值表是描述逻辑函数行为的一种方法,它展示了逻辑函数的输入和输出的所有可能组合,通过对真值表的分析,可以确定逻辑函数的特性和性能。

布尔代数可以帮助分析真值表,找出逻辑函数的规律和特点,为电路优化提供依据。

5. 布尔方程与卡诺图布尔代数中的布尔方程和卡诺图是数电优化中常用的工具。

通过将逻辑函数转化为布尔方程和卡诺图形式,可以更直观地理解逻辑函数的结构和逻辑关系,并通过化简和优化布尔方程和卡诺图,实现电路的最小化和优化。

数字电路设计中的逻辑门电路优化方法研究

数字电路设计中的逻辑门电路优化方法研究数字电路设计是现代电子技术中的重要一环。

在数字电路中,逻辑门电路起着至关重要的作用。

逻辑门电路是由逻辑门组成的电路,它能够实现不同的逻辑功能。

然而,在实际的数字电路设计中,逻辑门电路的优化是必不可少的。

本文将探讨数字电路设计中的逻辑门电路优化方法。

首先,我们需要了解逻辑门电路的基本原理。

逻辑门是由晶体管等电子元件组成的,它能够根据输入信号的逻辑状态产生相应的输出信号。

在数字电路中,常见的逻辑门有与门、或门、非门等。

这些逻辑门可以通过逻辑运算来实现不同的逻辑功能,如与运算、或运算、非运算等。

在数字电路设计中,逻辑门电路的优化是为了提高电路的性能和效率。

一种常见的逻辑门电路优化方法是使用布尔代数。

布尔代数是一种逻辑代数,它能够通过逻辑运算和布尔函数来描述逻辑门电路的行为。

通过对逻辑门电路进行布尔化简,可以减少电路的复杂度和延迟,从而提高电路的性能。

另一种逻辑门电路优化方法是使用卡诺图。

卡诺图是一种图形化的方法,它能够将逻辑门电路的真值表转化为逻辑方程。

通过对逻辑方程进行化简,可以减少逻辑门的数量和延迟,从而提高电路的性能。

卡诺图的优点是直观、简单,适用于中小规模的逻辑门电路优化。

此外,还有一种逻辑门电路优化方法是使用逻辑综合。

逻辑综合是一种自动化的电路设计方法,它能够将逻辑门电路的行为描述转化为逻辑门的结构描述。

通过逻辑综合,可以根据电路的性能要求生成最优的逻辑门电路。

逻辑综合的优点是能够快速生成最优的逻辑门电路,适用于大规模的逻辑门电路优化。

除了以上的方法,还有一些其他的逻辑门电路优化方法。

例如,使用时钟树优化方法可以减少逻辑门电路的时钟延迟,提高电路的性能。

使用电路分区方法可以将大规模的逻辑门电路分成多个小规模的子电路,从而提高电路的可维护性和可测试性。

使用电路布线方法可以优化逻辑门电路的布线,减少信号传输的延迟和功耗。

综上所述,数字电路设计中的逻辑门电路优化方法有很多种。

第三章:布尔代数分析与数字电路逻辑化简表示(不同的展开方式)

第二章:布尔代数及其分析数字电路基于排列组合与数字集合论,和数理逻辑有一定距离。

在逻辑函数的计算方面,使用数理逻辑的非计算,能够化简布尔表达式。

布尔逻辑代数引进数字电路,与命题的真假判断有区别,因此逻辑函数用数字函数描述更有广泛的内涵:既包括逻辑计算也包括组合功能.英国数学家布尔的研究导致逻辑代数的出现,并被命名为布尔代数。

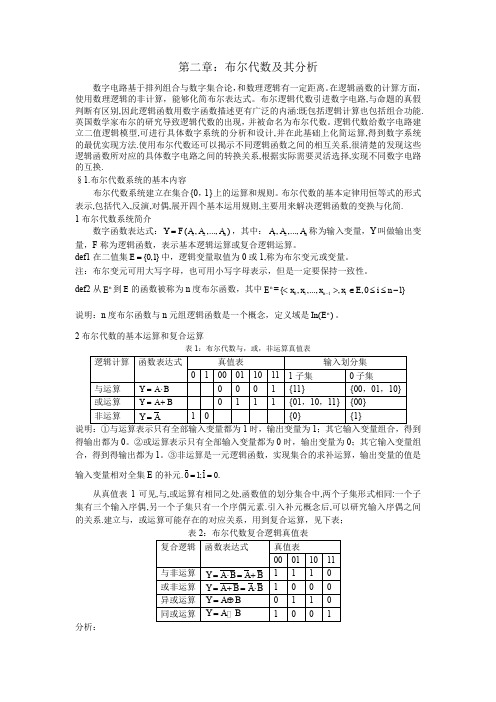

逻辑代数给数字电路建立二值逻辑模型,可进行具体数字系统的分析和设计,并在此基础上化简运算,得到数字系统的最优实现方法.使用布尔代数还可以揭示不同逻辑函数之间的相互关系,很清楚的发现这些逻辑函数所对应的具体数字电路之间的转换关系,根据实际需要灵活选择,实现不同数字电路的互换.§1.布尔代数系统的基本内容布尔代数系统建立在集合{0,1}上的运算和规则。

布尔代数的基本定律用恒等式的形式表示,包括代入,反演,对偶,展开四个基本运用规则,主要用来解决逻辑函数的变换与化简. 1布尔代数系统简介数字函数表达式:12(,,...,)n Y F A A A =,其中:12,,...,n A A A 称为输入变量,Y 叫做输出变量,F 称为逻辑函数,表示基本逻辑运算或复合逻辑运算。

def1在二值集{0,1}E =中,逻辑变量取值为0或1,称为布尔变元或变量。

注:布尔变元可用大写字母,也可用小写字母表示,但是一定要保持一致性。

def2从n E 到E 的函数被称为n 度布尔函数,其中n E =011{,,...,,,01}n i x x x x E i n -<>∈≤≤- 说明:n 度布尔函数与n 元组逻辑函数是一个概念,定义域是()n In E 。

2布尔代数的基本运算和复合运算表1:布尔代数与,或,非运算真值表说明:①与运算表示只有全部输入变量都为1时,输出变量为1;其它输入变量组合,得到得输出都为0。

②或运算表示只有全部输入变量都为0时,输出变量为0;其它输入变量组合,得到得输出都为1。

使用卡诺图的技巧

使用卡诺图的技巧摘要:卡诺图是一种常用于简化逻辑表达式和优化电路的工具。

它通过比较不同的组合输入和输出值,帮助我们找到最小化逻辑电路所需要的最简化表达式。

本文将介绍一些使用卡诺图的技巧,包括如何使用它来快速找到最简逻辑表达式、使用简化的布尔代数来简化电路等内容。

关键词:卡诺图、逻辑表达式、电路、布尔代数、优化正文:卡诺图是一种非常有用的工具,尤其是在电路设计和逻辑优化的过程中。

它的本质原理是比较不同输入和输出组合,以此来确定最小化逻辑电路所需要的最简化表达式。

下面介绍一些利用卡诺图的技巧:1. 确定卡诺图大小当我们需要使用卡诺图来简化逻辑表达式时,首先需要确定卡诺图的大小。

卡诺图的大小通常取决于所涉及的变量的数量。

计算出变量的数量后,我们可以使用下表来确定卡诺图的大小:变量(数目) | 卡诺图大小--------------|-------------1 | 2x12 | 2x23 | 4x44 | 4x45 | 8x86 | 8x87 | 8x88 | 8x82. 组织卡诺图一旦我们知道了卡诺图的大小,接下来的步骤就是将逻辑表达式中的每个变量映射到卡诺图中的一个格子上。

这样做的时候,可以采用灵活的方法,比如按字典顺序排列或按变量重要性对格子进行排序。

3. 找到主项和独立项在卡诺图中找到主项或者独立项,是确定最简逻辑表达式所必需的步骤。

主项代表着其输入变量的组合可以覆盖整个逻辑表达式中的输出。

独立项表示在逻辑表达式中单独出现的变量,可以使用这些项来表示逻辑表达式中的重复项。

4. 简化布尔代数卡诺图可以帮助我们简化布尔代数。

布尔代数也是一种常用于逻辑电路的表达式,通常包括AND、OR和NOT这些运算符。

卡诺图可以将不同的逻辑表达式映射到一个单一的布尔表达式,并消除其中的冗余项。

总之,卡诺图是一种非常有用的工具。

通过使用它,我们可以快速找到最简逻辑表达式和优化电路,以及简化布尔代数表达式。

在电路设计和逻辑优化中,熟练掌握卡诺图的技巧将是一个非常有用的技能。

什么是数字电路中的布尔代数

什么是数字电路中的布尔代数数字电路中的布尔代数数字电路是由逻辑门和触发器等基本元件组成的电路,广泛应用于计算机、通信和电子设备等领域。

而数字电路中的布尔代数则是指一种逻辑数学系统,用于描述和分析数字电路中的逻辑关系。

本文将介绍什么是数字电路中的布尔代数,以及它的应用和相关概念。

一、布尔代数的基本概念和运算规则布尔代数是由英国数学家乔治·布尔在19世纪中叶提出的,它是一种二值代数系统,只有两个基本值:真(1)和假(0)。

在数字电路中,我们通常用1表示高电平(True),用0表示低电平(False)。

布尔代数的基本运算包括与运算(AND)、或运算(OR)、非运算(NOT)和异或运算(XOR)等。

与运算表示两个输入信号同时为真时输出为真,其代数运算符为“∧”或“*”;或运算表示两个输入信号中至少一个为真时输出为真,其代数运算符为“∨”或“+”;非运算表示将输入信号取反,输出与输入相反,其代数运算符为“¬”或“~”;异或运算表示两个输入信号不相同时输出为真,其代数运算符为“⊕”。

二、布尔代数和数字电路的应用布尔代数在数字电路中起到了至关重要的作用。

通过布尔代数的逻辑分析和运算规则,我们可以设计各种复杂的数字电路,如加法器、减法器、乘法器、逻辑门和触发器等。

布尔代数的应用还包括逻辑函数的化简和最小化、逻辑门电路的设计与实现,以及数字电路的逻辑模拟和测试等。

通过运用布尔代数的方法和技巧,我们可以简化复杂的逻辑表达式,提高数字电路的性能和可靠性。

三、布尔代数的扩展和相关概念除了基本的布尔代数运算,还有一些扩展的布尔代数运算和相关概念:1. 离散数学中的布尔代数:布尔代数是离散数学中的一个重要分支,研究集合上的代数结构和逻辑关系。

2. 布尔函数和真值表:布尔函数是指接受布尔值作为输入并产生一个布尔值作为输出的函数。

真值表则是用来描述布尔函数输入和输出之间的关系。

3. 卡诺图:卡诺图是一种用来化简和最小化布尔函数的图形工具。

简化布尔代数表达式的方法与技巧

简化布尔代数表达式的方法与技巧布尔代数是一种逻辑运算系统,可以用来描述与、或、非等逻辑关系。

在数学、计算机科学、电子工程等领域中广泛应用。

为了简化布尔代数表达式,我们可以运用以下方法与技巧。

1. 使用布尔代数的基本定律布尔代数有一组基本定律,包括交换律、结合律、分配律和德摩根定律。

我们可以利用这些定律来重新组织布尔代数表达式,使其更加简洁。

2. 使用卡诺图卡诺图是一种二维图形方法,可以用于找到最简布尔代数表达式。

将每个变量的取值组合在一个表格中,然后找到包含最多1的矩形,将其转化为布尔代数表达式。

通过卡诺图,我们可以直观地看到布尔代数表达式的规律,从而进行简化。

3. 应用代数化简法代数化简法通过代数变换的方式来简化布尔代数表达式。

例如,利用分配律将一个复杂的布尔代数表达式分解成多个简单的表达式,并进行合并和化简。

4. 使用布尔恒等原理布尔恒等原理是指在布尔代数中,可以将两个具有相同结果的布尔表达式相互替换,而不改变整个系统的结果。

通过应用布尔恒等原理,我们可以将复杂的布尔代数表达式化简为更简单的形式。

5. 运用布尔代数的特殊规则布尔代数还有一些特殊规则,如零元和单位元、幂等性、互补律等。

这些规则可以帮助我们在简化布尔代数表达式时更加灵活地处理。

6. 使用计算机工具辅助现代计算机和软件提供了许多布尔代数表达式的简化工具。

通过使用这些工具,我们可以快速而准确地得到最简布尔代数表达式。

总结起来,简化布尔代数表达式的方法与技巧包括使用布尔代数的基本定律、应用卡诺图、代数化简法、布尔恒等原理、布尔代数的特殊规则以及计算机工具的辅助。

通过合理运用这些方法和技巧,我们能够简化复杂的布尔代数表达式,提高计算效率和逻辑分析能力。

卡诺图的绘制原理和应用

卡诺图的绘制原理和应用1. 卡诺图的介绍卡诺图是一种用于逻辑函数简化的图形工具,可以帮助我们更好地理解和分析逻辑函数的真值表。

通过将真值表中的1和0进行组合,可以得到卡诺图的绘制结果。

卡诺图的绘制原理基于布尔代数,可以帮助我们简化逻辑函数,减少逻辑门的数量和逻辑延迟。

2. 卡诺图的绘制步骤卡诺图的绘制步骤如下:2.1 确定输入变量的数量首先,需要确定逻辑函数的输入变量的数量。

这将决定卡诺图的行数和列数。

2.2 绘制卡诺图的表格根据输入变量的数量,绘制一个二维表格,表格的行数和列数由输入变量的数量决定。

2.3 根据真值表填入卡诺图将逻辑函数的真值表中的1和0填入卡诺图的相应位置。

每个格子可以表示一个最小项或者一个最大项。

2.4 确定最小项或者最大项的分组根据卡诺图中的相邻格子,确定可以进行合并的最小项或者最大项,并进行分组。

每个组可以包含2的幂个最小项或者最大项。

2.5 确定简化后的逻辑函数根据分组结果,可以得到简化后的逻辑函数。

将分组中的最小项或者最大项组合在一起,可以得到简化后的逻辑函数。

3. 卡诺图的应用卡诺图在逻辑电路设计和布尔代数中有着广泛的应用。

以下是卡诺图的一些主要应用:3.1 逻辑函数的简化卡诺图可以帮助我们简化复杂的逻辑函数。

通过卡诺图的绘制和分析,可以找到最简化的逻辑表达式,从而减少逻辑门的数量和逻辑延迟。

3.2 逻辑电路的设计卡诺图可以帮助我们设计逻辑电路。

通过卡诺图的绘制和分析,可以得到逻辑电路的最优设计方案,从而提高电路的性能和可靠性。

3.3 错误检测和校正卡诺图可以用于错误检测和校正。

通过对逻辑函数进行卡诺图的绘制和分析,可以找到逻辑函数中的错误和冗余,并进行校正。

3.4 数据压缩和编码卡诺图可以用于数据压缩和编码。

通过对数据的逻辑函数进行卡诺图的绘制和分析,可以得到数据的最小表示,从而减少存储空间和传输带宽。

3.5 自动化工具的支持卡诺图可以作为自动化工具的支持。

许多逻辑设计软件和硬件工具都提供了卡诺图的绘制和分析功能,可以帮助工程师更快地完成逻辑设计工作。

《卡诺图教学》课件

2 深入研究

如有兴趣,您可以进一步学习卡诺图背后的原理和其它高级技术。

3 与他人分享

将您所学的卡诺图知识分享给其他人,使更多人受益。

卡诺图可用于解决复杂问题,如优化电路设计或使程序运行更高效。

1

电路设计

我们可以使用卡诺图来简化电路,并减少构建和操作成本。

2

程序设计

在程序设计中,我们可以使用卡诺图来识别关键覆盖,并优化程序的性能。

3

逻辑分析

我们可以使用卡诺图来帮助分析和设计复杂的逻辑系统。

卡诺图和布尔代数的联系

卡诺图与布尔代数之间存在密切联系。布尔代数是由George Boole在19世纪中发明的一种形式化 逻辑体系,卡诺图则是一种实际应用布尔代数的方法。

《卡诺图教学》PPT课件

欢迎来到《卡诺图教学》课件。在本课程中,您将学习卡诺图的基本概念、 历史背景、解决实际问题的方法以及与布尔代数的关系。

什么是卡诺图?

卡诺图是一种图形化的布尔代数工具,用于找出逻辑表达式或布尔函数的最小化结果。

电路应用

卡诺图可用于简化电路设计和分 析,使其更加高效。

软件开发

卡诺图可用于软件开发中的代码 优化与调试。

使用相同的术语

卡诺图和布尔代数使用相同的术语,如变量、项、合取项等。

解决相同的问题

它们都专注于寻找逻辑表达式或布尔函数的最小化结果。

互为补充

布尔代数提供了理论和算法基础,而卡诺图则提供了直观、图形化和实际可行的工具。

卡诺图的特点和优点

卡诺图具有以下优点:简单易学、直观易懂、适用范围广、结果准确。

简单易学

逻辑分析

卡诺图可用于逻辑分析,以帮助 分析和设计复杂的逻辑系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第25卷第3期合肥工业大学学报(自然科学版)Vol.25No.3 2002年6月JOURN AL OF HEFEI U NIVERSITY OF T ECH NOLOGY Jun.2002对布尔代数中卡诺图的研究方志鸣(黄山学院物理系,安徽黄山 245021)摘 要:由于卡诺图具有几何相邻与逻辑相邻之间的良好对应关系,故在布尔代数中得到广泛应用,文章分析了传统卡诺图在简化多变量(n>5)函数时,其对应关系所面临的困难,提出三维卡诺图及卡诺图阵列的概念。

采用适当的排列方式可将图中几何相邻与逻辑相邻的对应项增加到6个以上,为了使其具有实用性,又引入一定的画图规则,对三维卡诺图加以改进,并举例说明它们的使用方法。

结果表明,采用该方法对六变量至八变量的逻辑函数进行综合化简时,仍具有简便直观、可靠性高及易操作等优点,且有较好的实用价值。

关键词:几何相邻;逻辑相邻;三维卡诺图;卡诺图阵列中图分类号:O153.2 文献标识码:A 文章编号:1003-5060(2002)03-0455-04Research on Karnaugh map in Boolean algebraFANG Zhi-ming(Dept.of Physics,Huan gshan College,Huangsh an245021,China)Abstract:Karnaug h map can be used larg ely in Boo lean alg ebra because it has fine correspondence be-tw een adjacency on g eo metr y and adjacency on log ic.In this paper,the difficulty of co rrespondence in sim plifying the m ultiple-variable(n>5)function w ith the traditional Kar naugh map is analyzed,and the concepts o f three-dimensional Karnaug h map and Karnaugh map array are proposed.By using pr oper range,the correspondence term s betw een adjacency on geom etry and adjacency on logic can in-crease to six or more in the map.Some pictorial rules are adopted,and the three-dim ensional Kar-naugh map is improved for practicality o f the map,and the usag e o f the im pro ved map is illustrated w ith examples in the paper.T he lo gic functions of six to eight variables ar e simplified and sy nthesized by using the improved m ap.The r esult show s that the presented m ethod has the advantages of sim-plicity,intuition,g ood reliability and easy operation,so it is valuable in practical use.Key words:adjacency on geometry;adjacency on logic;three-dimensional Kar naugh map;Karnaugh map array在有关文献[1~4]中,使用卡诺图时只讨论到四变量为止,因为通常画出的五变量及五变量以上的卡诺图用来化简逻辑函数时,已逐渐失去了简便直观的优点,故应用较少。

本文将卡诺图加以改进,可应用于五变量以上的逻辑函数的化简,而且不失其直观和简便的优点。

收稿日期:2001-08-14;修改日期:2001-11-04作者简介:方志鸣(1947-),男,安徽歙县人,黄山学院讲师.1 将卡诺图扩展成空间图形同一逻辑函数的2个最小项中,若仅有1个变量不同而其余变量相同时,则称它们是逻辑相邻的。

即1个n 变量的逻辑函数,对于它的任何一个最小项,当且仅当其中某一变量求反后,就可得到这个最小项的一个逻辑相邻项。

由于每个最小项都包含有n 个变量因子,所以每个最小项都可以有n 个逻辑相邻项,卡诺图在排列变量各种取值组合时,是按循环码规律进行,即相邻两组取值组合之间只有1个变量的值不同,故在卡诺图中任何几何位置相邻的最小项在逻辑上也相邻,从而可以合并化简,这种对应关系一目了然,非常直观。

但是,这种直观只能对四变量以下的卡诺图而言,因为目前给出的都是二维平面卡诺图,这种图中的某一小方格(对应于1个最小项)最多只有上、下、左、右4个几何相邻的小方格,正好等于1个四变量最小项的4个逻辑相邻项,而五变量以上的卡诺图,有些逻辑相邻的小方格并不相邻接,使其几何相邻与逻辑相邻之间失去了良好的对应关系[2,5],这是利用卡诺图化简时所面临的困难。

为了解决这个问题,须对传统的卡诺图作技术处理[6],经过折叠翻转等处理后,将六变量平面卡诺图[2]变成1个有4层方格图重叠在一起的空间图形,称之为三维卡诺图,因体现三维方向上的互换性,三维卡诺图可用1个4×4×4的正方体表示,如图1所示。

应注意与最小项对应的是每个小方块而不是小方格,显然,每个小方块(最小项)就多出前后2个相邻块,共有6个几何相邻块,经处理得到的三维卡诺图,在相互垂直的A B ,CD ,EF 三维方向上最小项均按循环码规律排列,确保了几何相邻与逻辑相邻的对应关系。

然而,图1的画法在使用中还有问题,即在A B 方向上,处于A B =01,11,10那几层图形上的大多数小方块被A B =00的这一层图形所遮盖,无法填写和观察合并。

为了便于操作,将卡诺图仍画成4×4的平面形式,但是规定每个小方格包含有逻辑函数在A B 方向的4个最小项,所以它仍旧是三维的,为了防止在观察和画圈合并时产生混淆,可将这4个最小项沿对角线方向填写。

按照这种约定,图1变成了图2所示的形式,为简便起见,图2某方格子中斜向填写的10、26、58和42实际上代表的是图1中的m 10,m 26,m 58和m 42这4个最小项。

图1 三维形式的卡诺图 图2 改进后的三维卡诺图2 用三维卡诺图化简多变量的逻辑函数利用三维卡诺图化简逻辑函数时,可以采用卡诺图画圈合并最小项的方法,只是应注意每个最小项除了有上、下、左、右4个几何相邻项以外,还多出了对角线方向(即前后)的2个几何相邻项,所以,合并时必须在A B ,CD ,EF 三个方向上同时观察和画圈,举例说明其用法。

456 合肥工业大学学报(自然科学版) 第25卷例1 f 1(A ,B ,C ,D ,E )=∑m (4,5,6,7,13,15,20,21,22,23,25,27,29,31)解 这是五变量的逻辑函数,所以三维卡诺图在垂直于纸面的方向上只有A =0和A =1两层图形,如图3所示。

对于序号在16以上的最小项,可以填在小方格的右上方,如果1个小方格中,只有一部分最小项取值是1,为了便于观察和画圈,对于那些取值为0的最小项最好也填入0,如卡诺图最下面一行中的2个小方格一样。

容易看出,第二行的4个小方格中有8个最小项相邻且可合并,用1个类似于平行四边形的圈画出,表示是在与纸面垂直的平面内进行操作,合并得B -C 。

还有,在中央的4个方格内有8个最小项也可以合并,这种合并是在与纸面平行和垂直的几个平面上同时进行,可以用1个类似于立方体六角形的圈画出,合并得CE 。

另外,在卡诺图的中下部,A =1这一层图形上有4个最小项可合并,因为是在与纸面平行的平面上进行,所以用1个四方形的圈画出,合并得A BE 。

最后结果为f 1=B -C +CE +A BE 例2 f 2(A ,B ,C ,D ,E ,F )=∑m (0,1,3,7,16,17,23,24,33,35,39,55)+∑d(10,18,19,26,51,56) 解 同理,用卡诺图可化简六变量函数,本函数中的约束项用“X ”标示,参照前面的约定在三维卡诺图中填写和画圈合并,如图4所示。

这里要注意的是位于A B =01这一层图形中的四角上有4个最小项可以合并,化简结果得f 2=C -EF +A -C -D -E -+A -B D -F -+B -C -D -F 图3 三维卡诺图化简五变量函数 图4 三维卡诺图化简六变量函数3 用卡诺图阵列实施化简由Shannon ′s theor em [7]推导,对n 变量二值逻辑函数中的某一变量x i 进行展开,可将该函数分解为2个(n -1)变量的子函数,即f (x 0,x 1,…,x n -1)=x i f (x 0,x 1,…,x i -1,1,x i +1,…,x n -1)+x -i f (x 0,x 1,…,x i -1,0,x i +1,…,x n -1) 如果n >6,经逐步递推,可以将其分解为2n -6个六变量的子函数,因此n 变量(n >6)函数的图形可以用2n -6个六变量的子卡诺图表示,形成一个卡诺图阵列。

一般情况下,七、八变量函数的卡诺图阵列分别有2个和4个六变量的子图。

以七变量函数为例,其展开式为f (A ,B ,C ,D ,E ,F ,G )=A -f (0,B ,C ,D ,E ,F ,G )+A f (1,B ,C ,D ,E ,F ,G )=A -f 0(B ,C ,D ,E ,F ,G )+A f 1(B ,C ,D ,E ,F ,G ) 易知,每个最小项除了在自己所在的子卡诺图中有6个逻辑相邻项之外,还在另一个子卡诺图的对应位置上有1个逻辑相邻项,它们也可以合并。

对这样的卡诺图阵列简化时,除了按三维卡诺图的规则进行操作外,还应在2个子卡诺图上找出相应位置的乘积项进行合并,才能得到最简结果[2,6]。

457第3期 方志鸣:对布尔代数中卡诺图的研究例3 f =A -B -C -D -F -+A B -D -E -G +A B -F G +A -B -C D -E -G +A -B -C -FG -+B -C -D -F G 解 画出七变量函数的2个子卡诺图f 0(A =0)和f 1(A =1),将有关变量值分别填入,如图5所示。