三位二进制减法计数器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

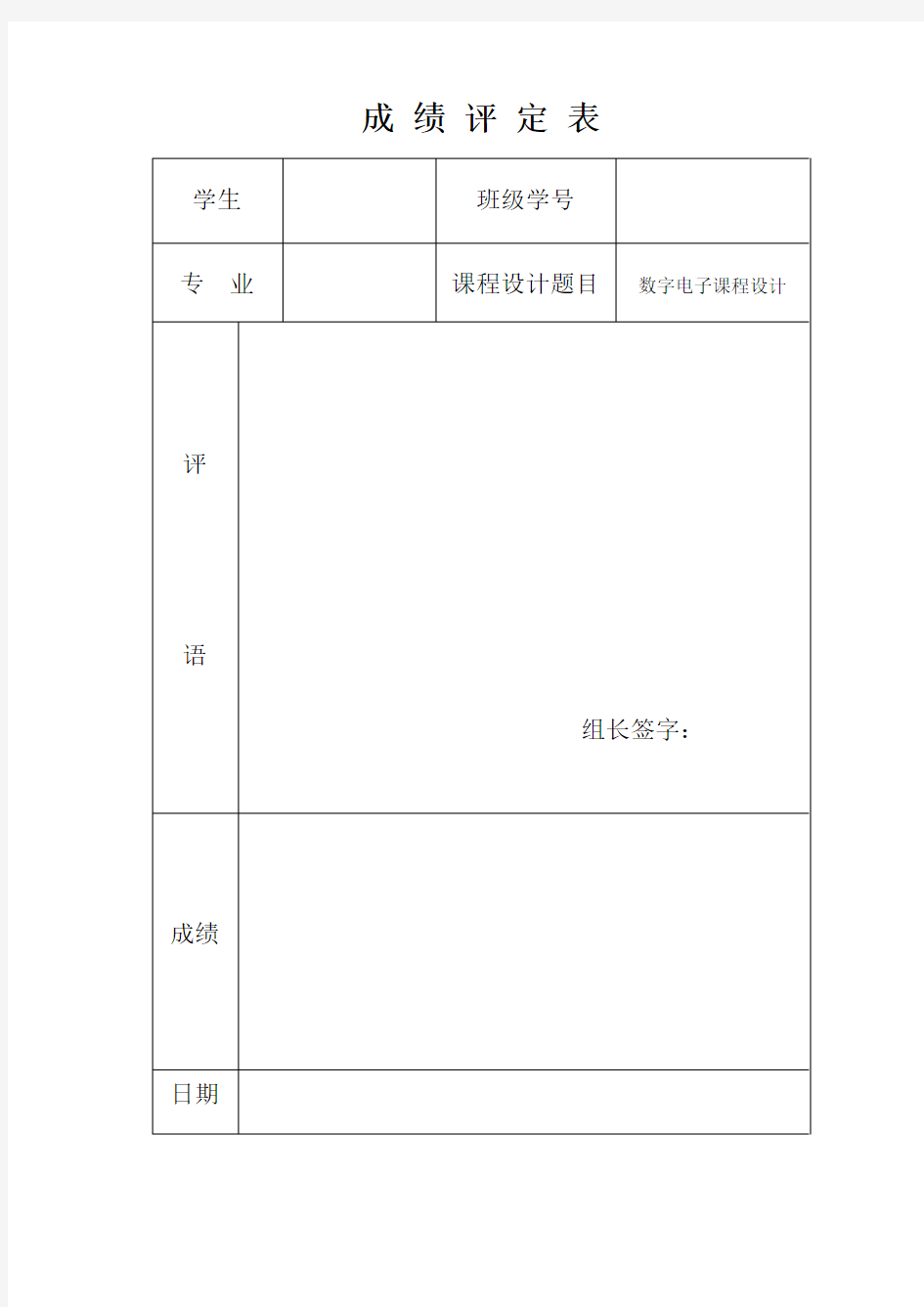

成绩评定表

课程设计任务书

目录

1 课程设计的目的与作用 (1)

2 设计任务 (1)

2.1 三位二进制同步减法计数器 (1)

2.2串行序列发生器的设计 (1)

2.3基于74191芯片仿真设计54进制减法计数器并显示计数过程

(1)

3设计原理 (2)

3.1三位二进制减法计数器 (2)

3.2串行序列发生器的设计 (2)

3.374191芯片仿真设计54进制减法计数器并显示计数过程 (2)

4实验步骤 (3)

4.1三位二进制减法计数器(无效状态000,110) (3)

4.2串行序列发生器的设计 (9)

串行序列信号发生器的总体框图: (9)

4.3 74191芯片仿真设计54进制减法计数器并显示计数过程 . 13

5 仿真结果分析 (16)

6 设计总结 (16)

7 参考文献 (16)

1 课程设计的目的与作用

1.了解同步计数器及序列信号发生器工作原理;

2.掌握计数器电路的分析,设计方法及应用;

3.掌握序列信号发生器的分析,设计方法及应用

2 设计任务

2.1 三位二进制同步减法计数器

1.设计一个循环型三位二进制减法计数器,其中无效状态为(000,110),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.2串行序列发生器的设计

1.设计一个能循环产生给定序列的串行序列信号发生器,其中发生序列(1101),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.3基于74191芯片仿真设计54进制减法计数器并显示计数过程

1.设计一个基于74191芯片仿真设计54进制减法计数器并显示计数过程,组合电路部分选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理

3.1 三位二进制减法计数器

1.计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序逻辑部件。计数器按长度可分为:二进制,十进制和任意进制计数器。计数器不仅有加法计数器,也有减法计数器。如果一个计数器既能完成累加技术功能,也能完成递减功能,则称其为可逆计数器。在同步计数器中,个触发器共用同一个时钟信号。

2.时序电路的分析过程:根据给定的时序电路,写出各触发器的驱动方程,输出方程,根据驱动方程带入触发器特征方程,得到每个触发器的次态方程;再根据给定初态,一次迭代得到特征转换表,分析特征转换表画出状态图。

3.CP是输入计数脉冲,所谓计数,就是记CP脉冲个数,每来一个CP脉冲,计数器就加一个1,随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器记满时再来CP脉冲,计数器归零的同时给高位进位,即要给高位进位信号。

3.2 串行序列发生器的设计

1.序列是把一组0,1数码按一定规则顺序排列的串行信号,可以做同步信号地址码,数据等,也可以做控制信号。

2.计数型序列信号发生器是在计数器的基础上加上反馈网络构成。要实现序列长度为M序列信号发生器。其设计步骤为:

a.先设计一个计数模值为M的计数器;

b.再令计数器每一个状态输出符合序列信号要求;

c.根据计数器状态转换关系和序列信号要求设计输出组合网络

3.3 74191芯片仿真设计54进制减法计数器并显示计数过程

1.写出的二进制代码

2.求归零逻辑

3.异步置数的值

4实验步骤

4.1三位二进制减法计数器(无效状态000,110)

所给无效状态为000、110,对其余有效状态进行逻辑抽象可以得到减法器设计电路的原始状态图如图1.4.3所示:

加法真值表:

三位二进制加法计

数器的总体框图

输入脉冲串行序列输出图1.4.2三位二进制加法计数器的总体框图

(1)状态图

111 0/ 101 0/ 100 0/ 011 0/ 010 0/ 001

1/

图1.4.3减法器的状态图

(2)选择的触发器名称:选用三个CP下降沿触发的边沿JK触发器

(3)输出方程:Y= Q—

2

n Q—n

1

Q

n

(4)状态方程

Q

1

n Q

n

Q

2

n 00 01 11 10

图1.4.4电路次态的卡诺图

Q

1

n Q

n

Q

2

n 00 01 11 10

图1.4.5 Y 的卡诺图

Q 1n Q 0n

Q

图1.4.6 1

1

+n Q 的卡诺图

Q 1n Q 0n

Q

图1.4.7 1

+n Q 的卡诺图

由卡诺图得出状态方程为:

Q 2n+1=n

Q 20Q +n Q 2n

Q 1

Q 1n+1 =n

Q 10Q +012Q Q Q +21Q Q Q 0n+1=n

Q 0+(12Q Q +12Q Q )0Q

(5)驱动方程

0J =1 1J =02Q Q 2J =1Q 0K = Q 1̅̅̅Q 2̅̅̅̅̅ Q 1Q 2̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 1K =20Q Q 2K =0Q (6)时钟方程 0CP =1CP =2CP =3CP

图1.4.8设计电路的逻辑电路图 (7)仿真结果