并行存储器系统

【计算机组成原理】存储系统

【计算机组成原理】存储系统存储器的层次和结构从不同⾓度对存储器进⾏分类:1.按在计算机中的作⽤(层次)分类 (1)主存储器。

简称主存,⼜称内存储器(内存),⽤来存放计算机运⾏期间所需的⼤量程序和数据,CPU 可以直接随机地对其进⾏访问,也可以和告诉缓冲存储器(Cache)及辅助存储器交换数据,其特点是容量较⼩、存取速度较快、单位价格较⾼。

(2)辅助存储器。

简称辅存,⼜称外存储器(外存),是主存储器的后援存储器,⽤来存放当前暂时不⽤的程序和数据,以及⼀些需要永久性保存的信息,它不能与CPU 直接交换信息。

其特点是容量极⼤、存取速度较慢、单位成本低。

(3)⾼速缓冲存储器。

简称 Cache,位于主存和 CPU 之间,⽤来存放正在执⾏的程序段和数据,以便 CPU 能⾼速地使⽤它们。

Cache 地存取速度可与 CPU 的速度匹配,但存储容量⼩、价格⾼。

⽬前的⾼档计算机通常将它们制作在 CPU 中。

2.按存储介质分类 按存储介质,存储器可分为磁表⾯存储器(磁盘、磁带)、磁芯存储器、半导体存储器(MOS型存储器、双极型存储器)和光存储器(光盘)。

3.按存取⽅式分类 (1)随机存储器(RAM)。

存储器的任何⼀个存储单元的内容都可以随机存取,⽽且存取时间与存储单元的物理位置⽆关。

其优点是读写⽅便、使⽤灵活,主要⽤作主存或⾼速缓冲存储器。

RAM ⼜分为静态 RAM (以触发器原理寄存信息,SRAM)和动态 RAM(以电容充电原理寄存信息,DRAM)。

(2)只读存储器(ROM)。

存储器的内容只能随机读出⽽不能写⼊。

信息⼀旦写⼊存储器就固定不变,即使断电,内容也不会丢失。

因此,通常⽤它存放固定不变的程序、常数和汉字字库,甚⾄⽤于操作系统的固化。

它与随机存储器可共同作为主存的⼀部分,统⼀构成主存的地址域。

由ROM 派⽣出的存储器也包含可反复重写的类型,ROM 与RAM 的存取⽅式均为随机存取。

⼴义上的只读存储器已可已可通过电擦除等⽅式进⾏写⼊,其“只读”的概念没有保留,但仍然保留了断电内容保留、随机读取特性,但其写⼊速度⽐读取速度慢得多。

【doc】并行系统的以存储器为中心的互联机制MCIM

并行系统的以存储器为中心的互联机制MCIM第22卷第4期1999年4月计算机PUTERSV o】.22No4ADr19991~并行系统的以存储器为中心的互联机制MCIM李三立戈弋武剑峰(算机率西五i北京10.084)5?0哆摘要并行系统中计算结点之间的互联网络IN(InterconnecfionNetwork)一直是并行体系结构的研究热.30年来曾研究过多种IN的结构及其特性,然而这些都是以逻辑电路为基础的.本文提出~种以多端口快速静态存储器(MPFSRAM)为中心的并行系统互联机制.称之为MCIMMCIM不同于共享数据的菇享存储器,它的容量较小,戈lj分为多十消息传递的通信邮区,并通过每十端口的访同接口(PA1).连接8—16十计算结点.常用的四端口存储器可组成32~64个计算结点的并行系统,构成当前国际流行的超结点".MCIM并行系统可充分利用MPFS—RAM的频宽.使消息传递的数据传输率达到10Gbps以上;可使数据发送和接收按流水线方式进行,从而减少消息传递的延迟.本支描述了MCIM的原理,PAI的仲裁和选择作用以及以存储器为中心的体系结构的实现物理布局.本文还描述了MCIM并行系统的仿真工作.并给出了实验结果关键词蹦存储器为中,fi,的互联机制.并行系统,消息传递分类号:TP302,f7害嚣He蔓徽MCIM:MEM0RYCENTRICINTERC0NNECT10NMECHANISM FoRPARALLELSYSTEMLISan~LiGEYLWUJian—Feng(Departm~tofComputerS~'enceandEngineering,TsingAuaUm'ver~'ty,BeOing100084) AbstractTheInterconneefionNetwork(IN)whichconnectscomputingnodesinparalle1sys —ternsremainsthekeyissueinparalle1architectureresearch.Inthepast30years,thestructures andfeaturesofvariousINShavebeenstudied.however.almostal1theseINSarebuiltontheba sisollogiccircuits.Thispaperproposesakindofintereonnectionmechanisminparallelsystemst hatistermedMemorvCentrieInterconnectionMeehanism,shortlyforMCIM.MCIMdiffersfro mthedatasharingorientedSharedMemoryconcept,MCIMemploysMulti—PortedFastStaticRAM(MPFSRAM)withconsiderablysmallstoragecapacity.MPFSRAMisdividedintoseveralc om-municationmailboxesformessagepassing,inwhicheachportcorrespondsaPortAccessInte rface(PADthatlinks8—16computingnodes.Soaconventionalfour—portmemorycanconstructapar—alldsystemwith32—64computingnodes,itconstitutesas.一called"Supernode"thatispromis—ingintheparallelsupercomputingarea.MCIMparalMsystemcanfullyutilizethebandwidth ofMPFSRAM,itallowsthedatatransmissionrateformessagepassingreachingabove10Gbps; it allowsthedatasendinganddatareceivingtobeoperatedinpipelinedmode,thusitreducesthel a—tencyofmessagepassing.ThispaperdescribestheprincipleofMCIMoperation,thearbitrati onandselectionfunctionofPAl,andthephysicallayoutforimplementingmemoryeentriearchit ecture.ThispaperalsoillustratesthesimulationframeworkforMCIMparalMsystem,andgives theexperimenta1results.率文1997一锄05收到,修改文1998—05—18收到.率瀑题得到国家攀登计划资助李--Or男,1995年生中N2:~N院士,博士生导师,从事计算机体系结构,网络并行计算并行处理等方面的研究戈弋,男,博士研究生,从事计算机体系结构,并行处理等方面的研究?武剖蜂,男,博士研究生,从事计算机体系结掏并行处理等方面研究计算机KeywordsMemoryeentricinterconneetionmechanism,parallelsystem.messagepassing 1概述在高性能计算的实现途径中.MPP技术的发展曾经经过几次反复.目前MPP技术的一个重要发展趋势是采用结点数不是太多,但每一个结点的性能很高的结构.或称为超结点(Supernode).多个超结点之间用专门设计的互联网络连接,如SGI的O—RIGIN2000和SUN最新公布的STARFIRE,这种类型的每个超结点都可包含B4到128个处理机.而这两个新型高性能并行系统代表了一个方向.即扩展性(Scalability),模块性(Modularity)和软件可移植性(Por*abdity)都很强.它也标志着公司生产的批量高性能并行系统进人市场的开端.目前的超结点系统一般都采用多级互联的组成结构.例如STARFIRE就是通过二级总线的紧耦合结构来组成一个超结点.其第一级是由24个CPU构成的单总线SMP结构的处理单元(Pu).各处理单元之间通过第二级的系统总线进行通信.为了解决系统总线带来的瓶颈问题,它在第二层采用了4组独立的总线控制逻辑,井利用交叉开关(Crossbar)结构来进行数据交换.这样的实现虽然弥补了上述的缺陷,但是增加了设计的复杂性,同时在传输链路建立时,要求收发处理单元和系统总线都空闲,操作延时较大.且不利于系统资源的有效利用.为此本文提出了一种适用于超结点结构并行计算机系统的互联机制,其中并不以逻辑电路为基础. 而是以多端口快速静态存储器为基础.我们称之为"以存储器为中心的互联机制"(MCIM).2MCIM原理近年来国际上计算机工业发展的一个重要特征是存储器工艺的迅速发展.存储器芯片的容量和速度都有了大幅度的提高.价格大大下降.不仅大容量主存芯片已有1Gbps产品,而且静态存储器的发展也很快,其存储周期可小于5ns.新型的双端口和四端口的快速静态存储器FSRAM已有商售产品这些都为我们实现MCIM提供了有利的条件2.1McIM结构图1是用四端口快速静态存储器进行消息传递(Messagepassing)的并行系统互联原理图.端口访问接口PAI——端{萋臣已磊磊赢压石五田臣墨端口.端口访问接口PAl图IMCIM通信原理图端口访阿接口AI图1的中间就是用于消息传递的多端E1存储器.从逻辑上来看.它分为四个消息传递的邮箱区,每个邮箱对应于一个端口.要发送的消息或数据首先放到与目的端E1对应的邮箱中,再通过端E1传输到目的结点.在物理实现上,我们可以将整个存储器分成许多固定长度的消息缓冲区(据统计,在一般的应用中大部分的消息长度都不超过2KB,可以选择此参数为消息缓冲区的合适长度;或者可以将缓冲区的长度进一步减小.在此情况下可以获得类似WormHole传输的一些优点).对每一个要传输的消息提供一个缓冲区.对于较长的消息,可以将其分为几个较短的包进行传输,来保证缓冲区不会溢出.消息传送完毕就释放缓冲区.发往同一端口的消息组成一个消息队列,对应于逻辑意义上的消息传递邮箱.从而有效地利用存储空间,采用这种通信机制可以很方便地实现消息的广播和选播等传输模式,此时只需将一个消息包同时放入多个消息队列中即可.PAl(端口访问接口)是实现多端口存储器消息传递的重要部分,也是MCIM从根本上区别于共享存储器数据共享的重要部分.它控制着对应端口消息的发送与接收,负责分配空闹的消息缓冲区,管理端口的消息队列,以及对结的访问请求进行仲裁和应答.因为多端口存储器可以支持多个端口同时对同一数据的访问操作,消息的发送和接收可以并发地进行,即以数据流水的方式在结点之间传送消息,从而显着地减少了传输延时.2.2MCIM的特点作为一个消息传递的互联机制,MCIM有一些与传统上以逻辑电路为基础的互联网络所不同的特点r1.由于多端口存储器通信可采用同时读写或流水的操作方式,数据传输的延时可以降到两个周期.目前市场上的多端口静态存储器的读写周期达到5ns,以四个端E1.每个端E164位为计.MCIM的聚合频宽可达50Gbps,而延时仅为10ns,具有较好的传输性能.4期李三立等:并行系统的存储器为中心的互联机制MCIM 2.可以在端口之间实现多种传输方式.在MCIM的基础上,不仅能实现多对端口之间点对点的数据传输,还可以支持选播,广播等传输方式.甚至能实现全部端口同时发送或者接收的操作.以此为基础的互联机制.能根据不同应用的要求,灵活地选用各种通信模式,而不需要软件上的调整.从而减少了通信的软件开销,有利于提高系统的效率.例如在共享存储的多处理机系统中,其一致性协议经常'要用广播或选播方式发送数据的一致性消息.如果用点对点的通信模式,就要求结点将同一消息重复地发送多次.而MCIM只需由PAl进行相应的操作即可一次发完所有的消息.3.由于多端口存储器本身就支持数据的存储及其在各端口之间的交换,只需要在此基础上增加一些控制逻辑,就可以实现互联的功能3以MCIM为基础的并行系统采用四端口陕速静态存储器的MCIM并行系统中,对应于每一个存储端口.有一排计算结点,每排有k个(图2).每个计算结点可以是一个处理机, 也可以是多于一个处理机的SMP计算结点.这样. 系统中共有4×k个计算结点.通过四个端口,结点机可以向快速静态存储器MPFSRAM读或写数据字,其字长可达64位.目前从技术上已经能制造读写周期为5ns的静态存储器了.".采用这种快速静态存储器,MCIM的聚台频宽可达到50Gbps.图2MCIM并行系统结构图仲裁与选择是MCIM并行系统中的重要部分,见图2,当某排上的一个计算结点,如P要发送数据到目标结点机中去,它要使用FSRAM的端口2. 因为该排上的另外结点也可能同时要使用端口2, 这就会发生竞争,因此需要根据各结点的状态和优先权来进行仲裁.同样,目标结点(如P)接收数据. 也可能要争用存储端口3.这时也要根据第3排上结点的状态和优先权来进行仲裁,并且根据目标结点地址来选择接收结点.在MCIM并行系统中.仲裁与选择的任务主要由端口访问接口PAl来完成.在收到结点的访问请求后,它根据相应的状态信息进行选择,给出应答信号.不仅如此.PAl还要实现其它一些功能.包括对消息缓冲队列的管理及与结点和存储端口的应答. 图3是PAl的逻辑结构简图.其中DC是~个双向的数据通道.它是由NCI与MCI共同控制的. 在给定的控制信号下,数据可在处理单元与存储端口之间流动.存储器控制单元MCU(MemoryCon—trolUnit)是实现PAl对存储端口操作的部分,所有的端口操作命令都是由MCU发出.由于在数据传输的过程中是PAl而非结点直接访问中央快速静态存储器的端口,因此向端口发出读写命令及地址信号都通过存储控制单元来完成.同时MCU向数据通道传送控制信号,保证数据从存储器到处理单元的传输.缓冲医管理单元BMU(BufferManage—mentUnit)主要负责对端口消息缓冲队列的管理. 在消息传递前申请空闲缓冲医,传输完毕后释放无计算机用的缓冲区,并记录状态信息.当然,缓冲区管理单元还需要向MCU提供传输缓冲区的地址.以启动传输进程.结点控制单元NCU(NodeControlUnit) 负责PAI与处理单元之间的交换操作及传输进程控制首先它要对处理单元的传输请求进行仲裁和选择,给出适当的响应,然后通过与发送单元的交互操作控制数据的传输,同时向存储控制单元发送信号.启动存储操作.存储端口和"端口访问接口"相配合的是,每一个结点必须有它自己的特征字1w.这个特征字1w要送到一个特征字寄存器IWR中,见图4.特征字寄存器是直接在PAl中参与仲裁与选择的.特征字是由若干字段所组成的,它包括本结点状态,优先权,目的端NCU结控制单元IWR:特征字寄存器MCU;存储控制单元BMU缓冲区管理单元口号以及目标结点地址,当然也可以把传送字节数作为选用的字段.如果传送字节数是放在被传送的消息(Message)数据之中(实用情况往往如此),则IWR中可以不包含它.4消息的发送与接收圈4特征字寄存器LWR组成以MCIM为互联的并行系统中,发送结点机如要发送消息到目标结点.它先送出消息的特征字1w到特征字寄存器IWR,其中的本结点状态,优先权和目的端口号等字段先参与仲裁.如结点P.要发送数据到目标结点机去,则它在端VI访问控制PAI 中参与仲裁,以决定它是否能在P"P多个结点机中首先竞争到使用端VI2的权利.如果它能竞争到端VI2.则发送结点P开始把要发送的数据按IWR中的目的端口号,写入多端口MPFSRAM中相应队列的消息传递缓冲区中去,如目前的目的端口号为2.与此同时,发送结点P的特征字寄存器中的目标结点地址,将被送到相应目标结点所在的仲裁与选择器中去参与选择.若目前的目标结点地址为P则将送到PAl.中去参与选择.由于P一P的特征字也在PAla中等待选择,则此时要看目标地址P的本结点状态是否为"空闲"(即为…0),还是"(即为"1"),以及它的优先权能否使P竞争到存储端口3.如果P.的本结点状态为"忙",或其优先权较低,不能争用到端VI3,则要根据调度算法去等待,或者发送结点及接收结点重新再发新的特征字1w.若接收结点P为"空闲",而且其优先权也能争用到存储端VI3,则P.将从消息传递缓冲区队列3中逐个接收(读出)消息数据.由于这是多端VI存储器,所以发送数据和接收数据是可以并发地进行的.接收结点要在接收每一个数据以后,就把该消息缓冲区中的存储单元清零,然后再从其次一个存储单元中读出下一个数据.清零操作可以在两次相邻的读数操作中完成,不会影响读操作的连续进行.在接收结点Pj读出发来的数据过程中,禁止任何第三排中的结点在此时发送信.息,因为在PAla的仲裁中它必然失败,不可能在存储端VI3接收数据的过程中争用到端口3.当接收结点开始接收发送来的数据.以及接收完发来的全部数据以后,都要发出一个应答信号.4期李三立等:并行系统的存储器为中心的互联机制MCIM 消息传递时数据通信的仲裁与选择以及数据的读写时序关系见图5.可以看出,发送数据与接收数A:发送结点参与仲裁AIIB:发送结点发送数据BC:目标结点地址选择CD:目标结点接收数据DE;通信邮箱中原数据清零EF:接收结点发出应答信号F鼓据II数据2据之间的延迟只有两个存储周期.如在快速静态存储器中(如周期为5ns),则其延迟时间只有10ns.数据1I数据2UUUUU图j发送数据与接收数据时序圉假如在本排中的处理机结点之间要传送消息,也有一个仲裁与选择的过程.发送结点的特征字要先送到其相应的PAI中去参与仲裁,根据其本结点状态和优先权选择出一个结点占有端口,然后根据目标结点地址挑选目标结点.若目标结点为同排结点,由NCU向目标结点发送选择命令.当目标结点答以接收准备好"时.NCU可向发送结点发信号.开始传输过程.由于本排的各结点机的数据线是通过结点的选择门连接在一起的,当选择门打开以后, 发送结点可以直接通过数据总线快速地把数据传送到接收结点中去,这个过程就象DMA传送一样,不必经过中间的存储器.5仿真模拟和实验结果我们的仿真模拟实验主要研究MCIM并行系...1墼堡II墼堡l统互联性能中的传输频带宽度以及时间延迟.目前适度并行的高性能计算机一般采用单息线SMP或多级总线的并行结构,它们又往往是前述超结点结构的技术基础.本文的仿真实验将MCIM与这两种类型的并行系统进行比较和分析.5.1实验模型在选择实验模型时,我们先选用双端口的快速静态存储器.这是在市场上比较常用的商售产品MCIM的仿真模型结构见图6.处理机组l一4对应于图2中的各排结点.模型中每一对读端口和写端口对应多端口存储器的一个存储端口.通信数据从写端口进入存储器,从读端口被取出.相应的写仲裁和读仲裁分别控制着结点对端口的读写操作.Bank l4对应于各个端口的消息缓冲队列.由于数据在其上的写端口和读端口之间单向流动,故用FIFO 模型即可模拟消息缓冲队列.图6MCIM仿真模型结构发送结点首先通过写伸裁获得对端口的写权限,即可将数据写入相应的缓冲队列中.同样,接收结点在经过读仲裁得到对读端口的访问权岳,才可以从中央存储器中读出数据.整个过程根据收发结计算机学撮点的状况分为两个阶段灵活地进行.5.2模拟结果与分析在仿真模拟时.我们假设:计算简单产生消息(Message)的机率是按泊松分布的;而目标结点地址的分配是均匀分布的;发送消息数据的长度则是按指数分布.其中实验中假设处理机结点数为16; 对于MCIM,假设分别有4个读和写端口;G是MCIM并行系统中每个结点发送消息数据的时间间隔的期望值,它表明处理机结点对端口访问的繁忙程度,在此作为实验比较的自变量;而Length是消息长度的期望值,它对系统性能的影响与G相关,为了更准确地描述变化趋势,在此设其为512位,这也是符台实际情况的.为了反映在实际过程中的不确定性…G和Length都是随机变量.图710是MCIM在改变发送时间间隔和消息长度的情况下的带宽和延时曲线.1O305O7O9011o130l5017019O21o23025027029o3lO3303503703904lO43045047o 49051o消息发送间隔(Cycle囹7MCIM带宽与消息发送频繁程度的关系曲线—带图9MCIM带宽与消息长度的关系曲线256512102420484096平均诮息长度(bits图l0MCIM延时与消息长度的关系曲线4期李三立等:并行系统的以存储器为中心的互联机制MCIM由图中的曲线可知,MCIM的消息传输性能与消息的长度和发送的频度都相关.随着消息长度的增加或者发送间隔的减少.传输的延时逐渐变大,系统的吞吐量也在增大,直到达到饱和.囤为当消息长度变大或变小时,消息之间为竞争资源发生冲突的概率增大了,从而导致传输延时的变化.但是系统的吞吐量并不囤此受到影响,仍然逐1.::42.O步增加至最大传输率.这是由MCIM的传输机制所决定的,由于中央存储器的存在,它不需要整个链路都空闲时才能进行传输过程,而是最大限度地利用系统资源.圉12是在其它条件相同的情况下,MCIM与多级总线多处理机(MP)系统(如图11)的传输频宽和延时的比较.图11多级总线MP系统结构图48648096ll2128l4416ofa)图12模拟实验结果(MCIM与多级总线结构)在模拟实验中,对于MCIM的SRAM的读写方式分为两种:方式1.即写即读消息开始写入后,在开始写人的下一个周期.只要目标地址结点的读存储端口空闲,就可以进行读操作方式2.同步读写.只有在发送结点的写存储端口和接收结点的读存储端口都空闲时,才可以写入消息数据,同时目标地址结点以流水线方式读出数据. 实验曲线中,B是读写方式1的结点信息传输频宽;是读写方式1的消息传输平均延时;B是读写方式2的结点信息传输频宽;Ta是读写方式2 的消息传输平均延时.B和,,s指的是二级总线系统的平均带宽和延时,占s和7s是系统总线宽度两倍于下层总线时系统的结点平均带宽和延时. 从图示的结果可以看出,对于多级总线的多处理机系统,MCIM在传输性能上仍具有一定的优势这是因为在多级总线系统中.上层的总线往往成为系统的瓶颈.即使增加其频带宽度,由于仲裁及响应时间的延时较大,其传输性能仍不如MCIM的互联网络.与多级总线的互联结构相比,MCIM有以下几个优点首先,由于采用存储器为中心的互联机制.MCIM每个端口的数据宽度可以达到8到32个字节,超过了并行系统互联网络通路的宽度;其次.MCIM紧耦合的实现方式和消皇流水的收发,使之具有更高的频率和更小的延迟;而多端I:1存储器的特点及硬件实现的端I:1仲裁,避免了传输过程中消息的阻塞.所以与目前结点频宽为几百Mbps的并行系统的互联网络相比,MCIM是一项有一定优点的互联技术.6结论以存储器为中心的互联机制MCIM是一种新型的概念和结构,以MCIM构成的并行系统是一个新园ii21一了计算机的研究领域,它具有数据传输频带宽,数据传输延时小等显着优点.采用商售的多端口FSRAM,比并行系统互联网络中定制的路由器要简单便宜.如把MCIM系统看成是超结点,并把它与阿格栅结构结合起来,可为百万亿次的巨型超级计算机技术开辟良好前景.亦可将其连接在因特网上,利用它较强的计算能力来在更广泛的范围内进行并行操作和资源共享参考文献1李三立,武剑峰,戈弋McIM——存储器为审心的互联机制2345S。

并行机紧耦合松耦合系统原理构成以及存储体系结构

并行机紧耦合松耦合系统原理构成以及存储体系结构姓名:________________________班级:________________________学号:________________________并行机紧耦合松耦合系统原理构成以及存储体系结构摘要计算机发展的趋势是越来越先进,越来越高级。

从数据处理、信息处理到知识处理,最终到智能处理,每前进一步,都要求增强计算机系统的处理能力。

计算机发展的历史表明:为了达到高性能,除了必须提高元器件的速度外,系统结构的改进是另一种重要途径,特别是当元器件的速度达到极限时,改进系统结构就成为问题的焦点。

对此,了解紧耦合松耦合系统原理构成以及存储体系结构十分重要。

AbstractTrends in computer development is more advanced, more and more advanced. From the data processing, information processing to knowledge processing, eventually to the intelligent processing. Every step, require enhanced processing capabilities of the computer system .The history of computer development shows that in order to achieve high performance,in addition to the need to improve the speed of external components. Improved system architecture is another important way. In particular, when the speed limit is reached components.Improved system architecture has become the crux of the problem. Therefore,learn tightly coupled and loosely coupled systems theory constitutes storage architecture is very important.关键字:紧耦合;松耦合;存储体系;Cache一致性一.多处理机系统多处理机系统是由多台处理器组成的计算机系统。

存储系统的基本要求和并行主存系统

证明:m n 1 时成立。

用归纳法证明(续)

k (1 )

k 1 n k 1

( n 1)(1 ) n n(1 ) n 1 ( n 1)(1 ) n n(1 ) n 1 ( 1 ) (1 ) n

带入上式:

Bm k * p(k ) k (1 ) k 1 m(1 ) m1

k 1

m

由数学归纳法得:

Bm (1 )i

i 0

m 1

是一个等比级数,因此:

B

1 - 1

m

用归纳法证明

k 1 m 1 k ( 1 ) m ( 1 ) k 1 m 1 i ( 1 ) i 0 m 1

A 1, A 2,,, A k

( 2) A 1, A 2,,, A k 是在k个地址中没有两个或两 个以上的地址处于同一模体中,显然, k <= m (3)截取的k个地址的队列,能同时访问k个模体, k = 1,2,…m

另设: P(k)表示申请长度为k,且不冲突的概率密度函 m 数。显然k的平均值:

存储器的价格

c C / SM

总价格 C 每位价格 c

举例:频宽平衡

假定一台计算机200MIPS(2亿次)

CPU取指令:200MW/s 指令字长为一个字W CPU取操作数和保存结果:400MW/s 各种I/O:5MW/s 总和:605MW/s , 假定存储器字长为一个字 主存的访问周期( 1/605=0.0016528)《=16.5ns 实际上,主存(DRAM)(动态随机存储器) 在200ns内。

B

自学考试_计算机系统结构考前复习资料全

第一章计算机系统结构的基本概念从处理数据的角度看,并行级别有位串字串,位并字串,位片串字并,全并行。

位串字串和位并字串基本上构成了SIMD。

位片串字并的例子有:相联处理机STARAN,MPP。

全并行的例子有:阵列处理机ILLIAC IV。

从加工信息的角度看,并行级别有存储器操作并行,处理器操作步骤并行,处理器操作并行,指令、任务、作业并行。

存储器操作并行是指可以在一个存储周期内并行读出多个CPU字的,采用单体多字、多体单字或多体多字的交叉访问主存系统,进而采用按内容访问方式,位片串字并或全并行方式,在一个主存周期内实现对存储器中大量字的高速并行操作。

例子有并行存储器系统,以相联存储器为核心构成的相联处理机。

处理器操作步骤并行是指在并行性概念中引入时间因素,让多个处理过程在时间上错开,轮流重复地执行使用同一套设备的各个部分,加快硬件周转来赢得速度。

例子有流水线处理机。

处理器操作并行是指一个指令部件同时控制多个处理单元,实现一条指令对多个数据的操作。

擅长对向量、数组进行处理。

例子有阵列处理机。

指令、任务、作业并行是指多个独立的处理机分别执行各自的指令、任务、作业。

例子有多处理机,计算机网络,分布处理系统。

并行性的开发途径有时间重叠(Time Interleaving),资源重复(Resource Replication),资源共享(Resource Sharing)。

时间重叠是指在并行性概念中引入时间因素,让多个处理过程在时间上错开,轮流重复地执行使用同一套设备的各个部分,加快硬件周转来赢得速度。

例子有流水线处理机。

资源重复是指一个指令部件同时控制多个处理单元,实现一条指令对多个数据的操作。

例子有阵列处理机,相联处理机。

资源共享是指用软件方法让多个用户按一定时间顺序轮流使用同一套资源以提高资源的利用率,从而提高系统性能。

例子有多处理机,计算机网络,分布处理系统。

SISD:一个指令部件控制一个操作部件,实现一条指令对一个数据的操作。

第三章 存储系统(4)-并行存储器和多模块交叉(1)

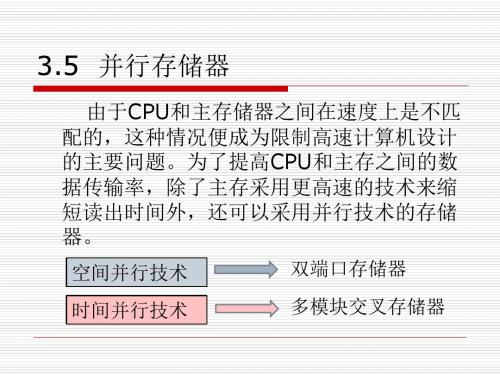

3.5 并行存储器

相联存储器

原理:按内容存取的存储器,可以选择记录 (关键字)的一个字段作为地址 组成:见下一页图 主要用途:在虚拟存储器中存放段表、页表和 快表,也可以作Cache的行地址

3.5 并行存储器

3.5 并行存储器

由于CPU和主存储器之间在速度上是不匹 配的,这种情况便成为限制高速计算机设计 的主要问题。为了提高CPU和主存之间的数 据传输率,除了主存采用更高速的技术来缩 短读出时间外,还可以采用并行技术的存储 器。

空间并行技术 时间并行技术

双端口存储器 多模块交叉存储器

3.5 并行存储器

3.5 并行存储器

两个独立端 口各拥有?

该SRAM容 量大小为?

3.5 并行存储器

2、无冲突读写控制

当两个端口的地址不相同时,在两个端口上进行读写操 作,一定不会发生冲突。当任一端口被选中驱动时,就可 对整个存储器进行存取,每一个端口都有自己的片选控制 (CE)和输出驱动控制(OE)。读操作时,端口的OE(低电平 有效)打开输出驱动器,由存储矩阵读出的数据就出现在 I/O线上。

3.5 并行存储器

假设有n个存储体,每个存储体的容量为m个存 储单元 顺序方式:

log

n 2

log

m 2

片选,存储体 选择

每个存储体内 的地址

3.5 并行存储器

1、顺序方式 [例]M0-M3共四个模块,则每模块8字。 顺序方式: M0:0—7 M1:8-15 M2:16-23 M3:24-31 5位地址组织如下: X X X X X 高位选模块,低位选块内地址 特点:某个模块进行存取时,其他模块不工作,优点是某 一模块出现故障时,其他模块可以照常工作,通过增添模 块来扩充存储器容量比较方便。缺点是各模块串行工作, 存储器的带宽受到了限制。

计算机系统结构课后习题答案

计算机系统结构基本习题和答案填空题1、从(使用语言的)角度可以将系统看成是按(功能)划分的多个机器级组成的层次结构。

2、计算机系统结构的层次结构由高到低分别为(应用语言机器级,高级语言机器级,汇编语言机器级,操作系统机器级,传统机器语言机器级,微程序机器级)。

3、应用程序语言经(应用程序包)的(翻译)成高级语言程序。

4、高级语言程序经(编译程序)的(翻译)成汇编语言程序。

5、汇编语言程序经(汇编程序)的(翻译)成机器语言程序。

6、在操作系统机器级,一般用机器语言程序(解释)作业控制语句。

7、传统机器语言机器级,是用(微指令程序)来(解释)机器指令。

8、微指令由(硬件)直接执行。

9、在计算机系统结构的层次结构中,机器被定义为(能存储和执行相应语言程序的算法和数据结构)的集合体。

10、目前M0由(硬件)实现,M1用(微程序(固件))实现,M2到M5大多用(软件)实现。

以(软件)为主实现的机器成为虚拟机。

(虚拟机)不一定全用软件实现,有些操作也可用(固件或硬件)实现。

11、透明指的是(客观存在的事物或属性从某个角度看不到),它带来的好处是(简化某级的设计),带来的不利是(无法控制)。

12、计算机系统结构也称(计算机体系结构),指的是(传统机器级的系统结构)。

它是(软件和硬件/固件)的交界面,是机器语言汇编语言程序设计者或编译程序设计者看到的(机器物理系统)的抽象。

13、计算机组成指的是(计算机系统结构的逻辑实现),包括(机器级内的数据流和控制流)的组成及逻辑设计等。

计算机实现指的是(计算机组成的物理实现),它着眼于(器件)技术和(微组装)技术。

14、确定指令系统中是否要设乘法指令属于(计算机系统结构),乘法指令是用专门的高速乘法器实现还是用加法器实现属于(计算机组成),乘法器和加法-移位器的物理实现属于(计算机实现)。

15、主存容量与编址方式的确定属于(计算机系统结构),主存是否采用多体交叉属于(计算机组成),主存器件的选定属于(计算机实现)。

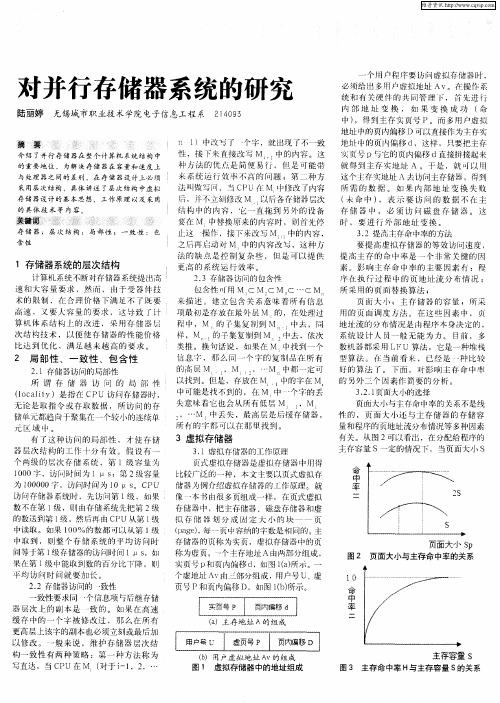

对并行存储器系统的研究

撮 要

薯

介 绍 了并行存 储 器在 整个计算 机 系统结 构 中

的 重 要 地 位 , 为解 决 存 储 器 在 容 量 和 速 度 上 与 处 理 器之 间 的 差 别 , 在 存 储 器 设 计上 必 须 采 用 层 次 结 构 , 具 体 讲 述 了层 次 结 构 中虚 拟

种 方法 的 优点是 简便 易行 ,但 足可能 带 来 系 统 运 行 效 率 不 高 的 问 题 ; 第 种 方 法 叫做写同 ,当 CP M } U I 修改 了内容 J

有 关 。从 图 2 以 看 出 ,在 分 配给 程序 的 可 主 存 容 量 S一 定的 情 况 下 , 当 页面 大 小 S

命

所 何 的 字 都 可 以 在 那 找 到 。

系统 设 计 人 员 一 般 无 能 为 力 。 目前 , 多 数机器都采 用 L FU 算 法 ,它 是 一 种 堆 栈 型 算 法 。 任 当 前 看 来 , 已 经 是 一种 比 较

程 中,M 的 1集 复 制到 M , 中去 ,同 | 、 样 ,M. 的 子 集 复 制 到 M 一 中 去 ,依次 类 推 。 换 句 话 说 ,如 果 在 M 中找 到 一 个 信息 事 ,耶么 同 ・ 个字的 复制 品在 所有 的 高 层 M ,M , …M 中 都 一 定 可 以找到 。但是 ,存放在 M + 中的字在 M, , 中 可 能 是 找 不 列 的 , 任 M, 一个 字 的 丢 中 失 意 味 着 它 也 会 从 所 有 低 层 M ,M M 中 丢 失 ,最 高 层 是 后 援 存 储 器 ,

维普资讯

对并行存储器系统的研究

陆丽婷 无锡城市职业技术 学院 电子信 息工程 系 2 4 9 10 5

计算机组成原理习题答案第六章

1.如何区别存储器和寄存器?两者是一回事的说法对吗?解:存储器和寄存器不是一回事。

存储器在CPU 的外边,专门用来存放程序和数据,访问存储器的速度较慢。

寄存器属于CPU 的一部分,访问寄存器的速度很快。

2.存储器的主要功能是什么?为什么要把存储系统分成若干个不同层次?主要有哪些层次?解:存储器的主要功能是用来保存程序和数据。

存储系统是由几个容量、速度和价存储系统和结构各不相同的存储器用硬件、软件、硬件与软件相结合的方法连接起来的系统。

把存储系统分成若干个不同层次的目的是为了解决存储容量、存取速度和价格之间的矛盾。

由高速缓冲存储器、主存储器、辅助存储器构成的三级存储系统可以分为两个层次,其中高速缓存和主存间称为Cache -主存存储层次(Cache 存储系统);主存和辅存间称为主存—辅存存储层次(虚拟存储系统)。

3.什么是半导体存储器?它有什么特点?解:采用半导体器件制造的存储器,主要有MOS 型存储器和双极型存储器两大类。

半导体存储器具有容量大、速度快、体积小、可靠性高等特点。

半导体随机存储器存储的信息会因为断电而丢失。

4.SRAM 记忆单元电路的工作原理是什么?它和DRAM 记忆单元电路相比有何异同点?解:SRAM 记忆单元由6个MOS 管组成,利用双稳态触发器来存储信息,可以对其进行读或写,只要电源不断电,信息将可保留。

DRAM 记忆单元可以由4个和单个MOS管组成,利用栅极电容存储信息,需要定时刷新。

5.动态RAM 为什么要刷新?一般有几种刷新方式?各有什么优缺点?解:DRAM 记忆单元是通过栅极电容上存储的电荷来暂存信息的,由于电容上的电荷会随着时间的推移被逐渐泄放掉,因此每隔一定的时间必须向栅极电容补充一次电荷,这个过程就叫做刷新。

常见的刷新方式有集中式、分散式和异步式3种。

集中方式的特点是读写操作时不受刷新工作的影响,系统的存取速度比较高;但有死区,而且存储容量越大,死区就越长。

分散方式的特点是没有死区;但它加长了系统的存取周期,降低了整机的速度,且刷新过于频繁,没有充分利用所允许的最大刷新间隔。

以存储为中心的并行结构系统

摘

要: 存储效率是存储器设计者关注的 中心问题 , 以存储互连的并行结构 系统在利用多端 口存储互连传输

的基础上可 以提高系统资源 的利用率 。从以存储 为中心的并行结构 的角度 出发 , 研究运用多端 口互连机制提 高计算机速度的方法。

关键词 : 结点 ; 超 并行 ; 存储 访 问

中图分类号 : P 9 T 33

闲 , 都可 以 向前 流动 , 样 消息 分组 可 以用接 近 链路 交 换 的速 度 它 这 在 网络 中传输 同时还 能减少 网络阻塞 的可 能性 。

,

图 1 多端口存储消息传递示意图 Fg Mutpr s rg es i i . l-ot t ae sa n i o m g g

收稿 日期 :0 70— 5 20 —72

基金项 目: 江苏省煤炭工业科技发展计划基金 资助项 目(0 510 ; 2 0 —1 ) 中国矿业大学基金 资助项 目( 4 5 ) OD 5 1

通 讯 联 系人 : 申 (9 7 )男 , 苏兴 化 人 , 国矿 业 大 学 教 授 , 导 。E malxzs @ p b X . if. e 张 1 5一 , 江 中 博 — i:zhh u . Zjno nt s

端 口访 问接 口 P l Al

收, 负责分 配 空闲 的消 息缓 冲 区 , 管理 端 口的 消息 队列 及对 结 点 的 访 问请 求进 行 回应 。在 实现 网络互连 中交换 时 , 是通 过 多端 口静 态

端 口

{

通信邮箱 区域 1 通信邮箱区域 2 通信邮箱区域 3 通信邮箱区域 4

文献标识码 : A

文章 编号 :0 16 0 (0 7 0—3 20 1 0—6 0 2 0 )40 0—4

并行存储器无冲突访问探讨

并行存储器无冲突访问探讨并行存储器无冲突访问是一种提高计算机性能的重要方法。

在传统的计算机系统中,访问共享存储器时会出现冲突,需要通过锁机制或者其他方法进行同步,导致并行性能的下降。

而并行存储器无冲突访问的思想是通过设计合理的存储器架构,使得不同处理器访问存储单元时不存在冲突,从而提高系统的并行处理效率。

要实现并行存储器无冲突访问,需要考虑以下几个方面:1.存储器的设计。

在并行存储器架构中,存储器一般被划分为多个并行的块或者通道,每个块或通道可以由不同的处理器独立访问,在同一时刻可以有多个处理器同时访问存储器。

这样的设计可以最大限度地减少不同处理器之间的冲突,提高系统的并发性能。

2.存储器的访问策略。

为了最大限度地减少冲突,需要设计合理的存储器访问策略。

一种常见的策略是将存储器划分为多个通道,并在每个通道中使用独立的缓存。

这样,不同处理器访问不同通道时不会发生冲突。

另一种策略是将存储器按块划分,并在每个块中使用独立的存储单元。

这样,不同处理器访问不同块时也不会发生冲突。

3.访问冲突检测和解决。

虽然设计了合理的存储器架构和访问策略,但仍然可能存在访问冲突。

为了检测和解决这些冲突,可以采用一些技术,例如通过引入冲突检测单元来监视存储器访问的冲突情况,并在发生冲突时采取相应的措施,例如延迟处理或者重试。

4.任务划分和调度。

并行存储器无冲突访问需要合理的任务划分和调度。

对于计算密集型的任务,可以将其划分为多个子任务,并交由不同处理器并行执行,从而减少访问存储器的冲突。

对于存储密集型的任务,可以采用一些优化策略,例如数据预取、数据压缩等,减少对存储器的访问次数,提高系统的并行性能。

并行存储器无冲突访问的思想可以广泛应用于各个领域的并行计算,例如大规模数据处理、机器学习、图形计算等。

通过合理的存储器架构设计和访问策略,可以充分利用计算机的并行性能,提高系统的计算效率。

然而,实现并行存储器无冲突访问并不是一件容易的事情,需要综合考虑多个因素,例如存储器带宽、处理器速度、任务负载等,同时还需要解决数据一致性和缓存一致性的问题。

[精彩]3并行主存与存储

![[精彩]3并行主存与存储](https://img.taocdn.com/s3/m/90cea8443a3567ec102de2bd960590c69ec3d8cd.png)

3.并行主存与存储3.1 什么是存储系统?对于一个由两个存储器M1和M2构成的存储系统,设M1的命中率为h ,两个存储器的容量分别为S1和S2,访问速度分别为T1和T2,每千字节的价格分别为C1和C2。

(1)在什么情况下,整个存储系统的每千字节的平均价格接近于C2? (2)写出这个存储系统的等效访问时间Ta 的表达式。

(3)假设存储系统的访问效率e=T1/Ta ,两个存储器的速度比r=T2/T1。

试以速度比r 和命中率h 来表示访问效率e 。

(4)写出r=5,20,100时,访问效率e 和命中率h 的关系式。

(5)如果r=100,为了使访问效率e>0.95,要求命中率h 是多少?(6)对于(4)所要求的命中率实际上很难达到。

假设实际的命中率只能达到0.96。

现采用一种缓冲技术来解决这个问题。

当访问M1不命中时,把包括被访问数据在内的一个数据块都从M2取到M1中,并假设被取到M1中的每个数据平均可以被重复访问5次。

请设计缓冲深度(即每次从M2取到M1中的数据块的大小)。

【参考答案】解:存储系统是指多个性能各不相同的存储器用硬件或软件方法连接成一个系统。

这个系统对应用程序员透明。

在应用程序员看来,它是一个存储器,其速度接近速度最快的那个存储器,存储容量与容量最大的那个存储器相等或接近,单位容量的价格接近最便宜的那个存储器。

(1)当S2>>S1(2)Ta=h·(3)e=T1/Ta=T1/(h·T1+(1-h)·T2) =1/(h+ (1-h)·T2/T1) =1/(h+ (1-h)·r) (4)r=5, e=1/(5-4h); r=20, e=1/(20-19h); r=100, e=1/(100-99h)。

(5)由e=1/(h+ (1-h)·r)= 1/(h+ (1-h)·100)>0.95 得 h>94/94.05=99.958% (6)h=0.96 设缓冲深度为A ,则n=5·A 由 h’=99.95%=(h+n -1)/n 求得A=163.2 由3个访问速度、存储容量和每位价格都不相同的存储器构成一个存储系统,其中M1靠近CPU 。

并行存储器PPT

分时启动

5

第五页,编辑于星期五:十五点 十分。

❖ 相联存储器的概念

❖ 相联存储器的组成

• 存储体,存放信息的部件。

• 输入检索寄存器,用来存放待检索的内容。 • 屏蔽寄存器,用来决定输入检索寄存器的哪些项参与检索比较,

哪些项不参与。 • 比较器,是相联存储器的核心,由字比较器和位比较器两部分组成。 • 字匹配寄存器,用来记录比较结果。 • 数据寄存器,用来存放某个单元的内容。 • 地址寄存器和地址译码器,使相联存储器同时具有按地

谢谢观看

第九页,编辑于星期五:十五点 十分。

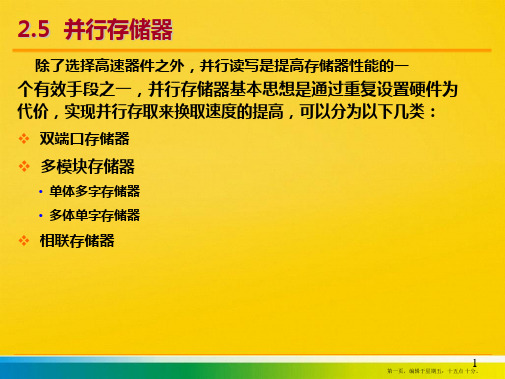

2.5 并行存储器

除了选择高速器件之外,并行读写是提高存储器性能的一

个有效手段之一,并行存储器基本思想是通过重复设置硬件为 代价,实现并行存取来换取速度的提高,可以分为以下几类:

❖ 双端口存储器

❖ 多模块存储器

• 单体多字存储器 • 多体单字存储器

❖ 相联存储器

1

第一页,编辑于星期五:十五点 十分。

第五页,编辑于星期五:十五点 十分。

第四页,编辑于星期五:十五点 十分。

除相了联选 存择储高器速结器构件框之图外:,并行读写是提高存储器K性能+的0一

K+1

K+2

除了选择高速器件之外,并行读写是提高存储器性能的一

MAR3

3 7 M3

K+3

MDR0

MDR1

MDR2

MDR3

DB

4

第四页,编辑于星期五:十五点 十分。

2

第二页,编辑于星期五:十五点 十分。

❖ 基本思想:并行设置多个存储模块,在一个存取周期内,多个存储模

块同时存取多个字以提高整体速度。

❖ 单体多字存储器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

页单位

M3:磁盘 存储器 a 页面A b 页面B 段G

段F 段单位

a 页面A 段F b 页面B 段G

M4:磁带机 后援存储器

5.2.2 一致性(coherence)

1.一致性定义

同一个信息项与后继存储器层次的副本是 一致的。 如果在高速缓存中的一个字被修改过,那 么在所有更高层上该字的副本也必须立即或最 后加以修改 。

空间局部性(spatial locality):一个 进程访问的各项的地址彼此很近,例如,表操 作或数组操作含对地址空间中某一区域的集中 访问。 顺序局部性(sequential locality):在 典型程序中,除非转移指令产生不按次序的转 移外,指令都是顺序执行的。

局部性原理指导我们去设计高速缓存、主存储器 以及虚拟存储器组织。

第五章 并行存储器系统

5.1 存储器系统的层次结构 5.2 包含性、一致性和局部性

5.2.1 包含性 5.2.2 一致性 5.2.3 局部性

5.3 存储器容量的规划 5.4 虚拟存储器技术 5.5 交叉访问的存储器

5.2 包含性、一致性和局部性

5.2.1 包含性(inclusion)

1. 包含性的定义 M0 M1 M2…… Mn 所有信息项最初存放在最外层Mn,在处 理过程中,它的子集复制到Mn-1,同样, Mn-1的子集复制到Mn-2,…… 如果在Mi中找到一个信息字,那么同一个 字的复制品在所有的高层Mi+1,Mi+2,……, Mn中都一定可以找到。

分布存储器: 系统结构灵活,可扩展性好; 处理机数目可达成百上千,处理速度有 巨大的发展潜力; 算法设计、编程以及任务动态分配比较 困难; 很难在处理机之间传递复杂的数据结构, 难于进程迁移; 不能支持需要存储空间的大规模数据处 理要求。

分布存储的两种编程方法:

(1)message-passing,用send,receive 原语实现通信,要求程序员在进程的整个运行 期间对数据的移动都很清楚; (2)romote procedure call,语言一级传 送控制与数据,可以看作是本地调用,但透明 度有限。

每 位 成 本 增 加

五个参数:

存取时间ti:从CPU到第i层存储器的往返时间 存储器容量Si:第i层的字节或字的数量 每字节成本Ci:第i层存储器的成本为CiSi 传输带宽bi:相邻层之间传送信息的速率 传输单位Xi:i和i+1层之间数据传送的粒度 对存储器系统中各层次存储器的特性,1993 年的统计数据如下表:

第五章 并行存储器系统

5.1 存储器系统的层次结构 5.2 包含性、一致性和局部性 5.3 存储器容量的规划 5.4 虚拟存储器技术

5.3.1 共享存储和分布存储 5.3.2 DSM与SVM 5.3.3 虚拟存储器的主要技术

5.5 交叉访问的存储器

5.4 虚拟存储器技术

提要: 虚拟存储器提供了几乎没有限制的存储 器工作空间。 虚拟地址在编译时产生。 虚拟地址到物理地址的转换在运行时进 行,需要使用转换表和映象系统。 替换策略。

f i (1 h1 )(1 h2 ) (1 hi 1 )hi

是指在较低层次有i-1次缺失而在Mi有一次 命中时访问Mi成功的概率。

f

i 1

n

i

1, f1 h1

通常情况下,有:

f1 f 2 f n

这说明,访问内存比访问外存要多。

5.3.2 有效存取时间

存储器层次 第0层 第1层 第2层 第3层 第4层 特性 CPU寄存器 高速缓存 主存储器 磁盘存储器 磁带存储器 设备工艺 存取时间 容量(字节) ECL 10ns 512B SRAM 25-40ns 128KB 72 DRAM 60-100ns 512MB 5.6 磁盘机 10-20ms 磁带机 2-20min

缺点: 这两种方法都是用来解决不同地址空间的问 题,在接点间传递复杂数据结构时都比较困难, 需要打包,传递指针也不可能实现。由于个处 理机拥有不同的地址空间,使得进程迁移时, 该进程所分配到的操作系统资源也得一起移动 (打开得文件、文件存取控制块等),这很费 时。

5.4.2 DSM与SVM

1.DSM和SVM的提出

(1 h1 )(1 h2 ) (1 hn 1 ) hn t n

5.3.3 层次结构的优化

目标: 使Teff接近于M1的t1, 总成本接近于Mn的Cn。 优化过程可以表达为:对一个线性规划求 最小值问题:

S i 0, ti 0, 对于i 1,2, , n Ctotal Ci S i C0 (总价格的上限)时,

如果在同样的预算限制条件下,要吧主存储 器容量提高64M字节,那么只好以减少磁盘容 量为代价,但是这一变化并不影响高速缓存的 命中率。如果使用合适的页面替换算法,可能 会增加主存储器的命中率,Teff有所降低。

层次化存储器系统必须解决的问题:

(1)数据块在较高层存储器中存放在哪个 位置?即块和页的定位问题。如果一个块存放 在某一上层存储器中,怎样确定并找到该块, 即块的寻址问题。 (2)不命中的将从下层存储器中访问,并 将该块调入上层存储器中,但是如果上层存储 器中已无空闲空间,则势必将上层存储器中的 某一块调出,但应调出那一块,即替换问题。 (3)在写访问时,写入上层存储器中的数 据必须在适当的时候写入下层存储器,何时写?

每当发生缺失时,就要付出代价去访问较 高层次的存储器。这种缺失在Cache中称为块 缺失。在主存储器中称为缺页错(page fault),因为块和页面是这些层次之间传送 信息的单位。 缺页错付出的时间代价要比块缺失付出的 更大:

Teff

i 1

n

f i ti h1t1 (1 h1 ) h2t 2

2.维护一致性的两种策略

(1)写直达(write-through,WT),即如果 在Mi(i=1,2,…,n-1)中修改了一个字,则 在Mi+1中需要立即修改。

(2)写回(write-back,WB),即如果在 Mi+1 中的修改延迟到Mi中正在修改的字被替换 时才进行。

5.2.3 局部性(locality)

i 1 n n

要将有效存取时间Teff f i ti 减到最小值。

i 1

例子:存储器层次结构设计

存储器层次 高速缓存 存取时间 容量 价格/K字节

t1 = 25ns s1=512K字节 c1=1.25美元

主存储器

磁盘阵列

t2 = 未知 s2=32M字节 c2=0.2美元

t3 = 4ms s3 = 未知 c3=0.0002美元

60-228GB 512G-2TB 0.23 0.01

成本(美分/KB) 18000

带宽(MB/S) 400Βιβλιοθήκη 800传送单位 字:4-8B

250-400

80-133

3-5

0.18-0.23

块:32B 页:0.5-1KB

文件:5- 后援存储器 512KB

分配管理 编译器分配 硬件控制 操作系统 操作系统/ 操作系统/ 用户 用户

Hennessy和Patterson(1990年)提出了一条 90-10规则:典型程序在10%的代码上可能要耗 费其执行时间的90%(例如嵌套循环操作的最 内层循环)。 时间局部性(temporal locality):最近 的访问项(指令或数据)很可能在不久的将来 再次被访问。即对最近使用区域的集中访问。

要达到有效存取时间Teff=10.04s,高速缓存 命中率为h1=0.98,主存储器命中率h2=0.9,总 成本上限为15000美元。

解:

C C1S1 C2 S 2 C3 S 3 15000 代入有:S 3 39.8GByte Teff h1t1 (1 h1 )h2t 2 (1 h1 )(1 h2 )h3t3 10.04 代入可得t 2 903ns

5.3.1 命中率

在Mi中找到一个信息项时,称之为命中,反 之称为缺失。 假定在层次结构中的存储器层次为Mi和Mi-1, 其中i=1,2,…,n。在Mi层的命中率hi则是信 息项可在Mi中找到的概率。它是表示两个相邻 层Mi-1和Mi特性的函数。在Mi中的缺失率定义为 1-hi。

相继层的命中率是存储器容量、管理策略 和程序行为的函数,它是独立的随机变量,其 值在0到1之间。我们假设h0=0和hn=1,这意味 着CPU总是先访问M1,并且访问到最外层Mn时总 是命中的。 对Mi的访问频率为:

5.4.1 共享存储和分布存储

MIMD系统可以分为两种:

(1)tightly coupled shared-Memory multiprocessors (2)loosely coupled distributed-Memory multiprocessors 它们可以用图表示如下:

P1 share-Memory multiprocessors SM1

DSM系统编制的程序比用消息传递方式编制的 程序效率高: (1)在DSM系统中,数据都是以块的方式进行传 送,如果一个程序具有较高的局部性,则当把一 个数据块传送到一个结点后,该结点对它的访问 就成为本地访问,而消息传递方式的每次访问都 需要通讯。

第五章 并行存储器系统

5.1 存储器系统的层次结构 5.2 包含性、一致性和局部性 5.3 存储器容量的规划

5.3.1 命中率 5.3.2 有效存取时间

5.4 虚拟存储器技术 5.5 交叉访问的存储器

5.3 存储器容量的规划

存储器层次结构的性能是由层次结构的有 效存取时间Teff决定的,它依赖于相继层 次的命中率和访问频率。

第五章 并行存储器系统

5.1 存储器系统的层次结构 5.2 包含性、一致性和局部性 5.3 存储器容量的规划 5.4 虚拟存储器技术 5.5 交叉访问的存储器