DDR3注定要夺取DRAM王座

DDR3测试读写

DDR3测试读写(1)今天是重阳节,所以提前祝福重阳节快乐。

因为DDR3讲解内容比较多,所以分解成3节进行讲解。

一个做FPGA的人如果不懂DDR3,Serdes,那基本等于没学习fpga。

所以必须掌握ddr控制器才能深入fpga具体功能。

注意以后基本工具都是用的vivado2014.02版本。

用ise导致不一样,不要问我。

该工程参考的xilinx的文档xtp225。

首先是打开vivado,建完工程以后,然后点击IP catalog,打开ip库。

找到Memory Interface Generator IP核。

然后会出现图1.2页面图1.1图1.2的显示信息是当前工程设置的器件信息。

vivado不像以前的ISE,分离IP工程。

现在都是一个工程。

所以要注意观察该页面显示的器件是否正确。

经常有人选错速度等级而导致无法通过后期时序仿真。

图1.2图1.3是选择创建一个设计。

图1.3图1.4选择ddr3芯片。

图1.4图1.5显示的是兼容引脚。

选择next。

图1.5图1.6是选择选择DDR的时钟,记住,DDR是双边沿。

所以上面写的400MHz,也就是DDR 800M。

选额内存类型是SODIMMs。

内存类型是MT6JTF12864HZ-1G6类型。

Data Mask 数据掩码,可以选择或者不选择,类似于sdram的dqm信号。

有人问这有啥作用。

就等于内存中,你要改变其中几个bit而不是改变全部bit。

所以用掩码方式更好的。

否则你要读出来,然后再写入,这种方法太消耗时间。

图1.6图1.7是表示选择整个IP输入时钟多少,基本DDR3寄存器控制。

基本IP输入时钟在SPARTAN6的MIG核是没有选择,需要手动修改时钟文件。

这里有提供输入时钟选择。

读写burst的方式,一个顺序读取还有个strict 跳跃式读取。

除非你有特殊的要求,一般都是顺序读取。

输出驱动电阻控制RZQ/7和RTT电阻,这个电阻是从datasheet手册得到的。

DDR3必读内容介绍DDR3

1.DDR的发展:2003年秋季Intel公布了DDR2内存的发展计划。

而随着当时CPU 前端总线带宽的提高和高速局部总线的出现,内存带宽成为系统越来越大的瓶颈。

处于主流DDR技术已经发展到极至,因此DDR2脱颖而出。

DDR2的实际工作频率是DDR的两倍。

这得益于DDR2内存拥有两倍于标准 DDR内存的4bit预读取能力。

下图为DDR和DDR2预读取能力的对比。

DDR2内存技术最大的突破点其实不在于用户们所认为的两倍于DDR的传输能力,而是在采用更低发热量、更低功耗的情况下(由2.5V降为1.8V),DDR2 可以获得更快的频率提升,突破标准DDR的400MHZ限制。

DDR内存通常采用TSOP芯片封装形式,这种封装形式可以很好的工作在 200MHz上,当频率更高时,它过长的管脚就会产生很高的阻抗和寄生电容,这会影响它的稳定性和频率提升的难度。

这也就是 DDR的核心频率很难突破275MHZ的原因。

而DDR2内存均采用FBGA封装形式。

不同于目前广泛应用的 TSOP 封装形式,FBGA封装提供了更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了良好的保障。

2007年中Intel表示支持DDR3的发展,随后DDR3慢慢走上了历史的舞台,根据由JEDEC协会所制定的规格来看,由技术面来切入DDR3与DDR2的异同点,DDR3拥有高频率低电压的优点,DDR3可以比DDR2运作时省下约30%的电力,速度方面DDR3从800Mbps起跳最高可以至1600Mbps,几乎是DDR2的二倍速度,正因为高传输率的关系,DDR3可以在一个时序(Clock)之中传出8bit的数据,比起DDR2的4bit也是二倍的数据传输量,低电压更是DDR3的优势之一,1.5V 的电压比DDR2的1.8V降低了17%。

下面的图表总结了DDR,DDR2,以及DDR3的一些重要的区别:2、认识内存相关工作流程与参数首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其中所起到的作用。

AC7021B 开发板 用户手册说明书

文档版本控制目录文档版本控制 (2)(一)简介 (4)(二)ZYNQ芯片 (5)(三)DDR3 DRAM (7)(四)QSPI Flash (11)(五)eMMC Flash (12)(六)时钟配置 (14)(七)USB转串口 (15)(八)LED灯 (16)(九)复位按键 (18)(十)JTAG接口 (18)(十一)拨码开关配置 (19)(十二)电源 (20)(十三)结构图 (21)(十四)连接器管脚定义 (22)(一) 简介AC7021B(核心板型号,下同)核心板,ZYNQ 芯片是基于XILINX 公司的ZYNQ7000系列的XC7Z020-2CLG484I 。

ZYNQ 芯片的PS 系统集成了两个ARM Cortex™-A9处理器,AMBA®互连,内部存储器,外部存储器接口和外设。

ZYNQ 芯片的FPGA 内部含有丰富的可编程逻辑单元,DSP 和内部RAM 。

这款核心板使用了2片SK Hynix 公司的H5TQ4G63AFR-PBI 这款DDR3芯片,每片DDR 的容量为4Gbit ;2片DDR 芯片组合成32bit 的数据总线宽度,ZYNQ 和DDR3之间的读写数据时钟频率高达533Mhz ;这样的配置,可以满足系统的高带宽的数据处理的需求。

为了和底板连接,这款核心板的4个板对板连接器扩展出了PS 端的USB 接口,千兆以太网接口,SD 卡接口及其它剩余的MIO 口。

以及PL 端的BANK13, BANK33, BAN34和BANK35的几乎所有IO 口(198个),其中BANK33和BANK34的IO 的电平可以通过更换核心板上的LDO 芯片来修改,满足用户不用电平接口的要求。

对于需要大量IO 的用户,此核心板将是不错的选择。

而且IO连接部分,ZYNQ 芯片到接口之间走线做了等长和差分处理,并且核心板尺寸仅为60*60(mm ),对于二次开发来说,非常适合。

AC7021B 核心板正面图AC7021B 核心板背面图(二) ZYNQ 芯片开发板使用的是Xilinx 公司的Zynq7000系列的芯片,型号为XC7Z020-2CLG484I 。

DDR3详解

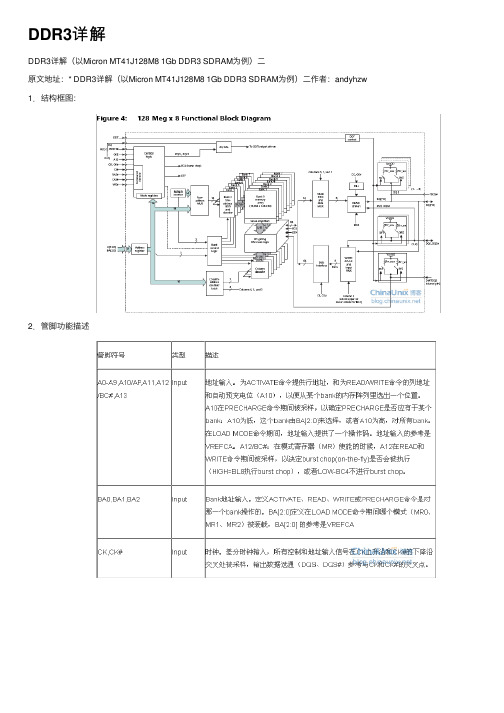

DDR3详解DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)⼆原⽂地址:* DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)⼆作者:andyhzw 1.结构框图:2.管脚功能描述3.状态图:Power on: 上电Reset Procedure: 复位过程Initialization: 初始化ZQCL: 上电初始化后,⽤完成校准ZQ电阻。

ZQCL会触发DRAM内部的校准引擎,⼀旦校准完成,校准后的值会传递到DRAM 的IO管脚上,并反映为输出驱动和ODT阻值。

ZQCS: 周期性的校准,能够跟随电压和温度的变化⽽变化。

校准需要更短的时间窗⼝,⼀次校准,可以有效的纠正最⼩0.5%的RON和RTT电阻。

Al:Additive latency.是⽤来在总线上保持命令或者数据的有效时间。

在ddr3允许直接操作读和写的操作过程中,AL是总线上的数据出现到进⼊器件内部的时间。

下图为DDR3标准所⽀持的时间操作。

Write Leveling:为了得到更好的信号完整性,DDR3存储模块采取了FLY_BY 的拓扑结构,来处理命令、地址、控制信号和时钟。

FLY_BY的拓扑结构可以有效的减少stub的数量和他们的长度,但是却会导致时钟和strobe信号在每个芯⽚上的flight time skew,这使得控制器(FPGA或者CPU)很难以保持Tdqss ,tdss和tdsh这些时序。

这样,ddr3⽀持write leveling这样⼀个特性,来允许控制器来补偿倾斜(flight time skew)。

存储器控制器能够⽤该特性和从DDR3反馈的数据调整DQS和CK之间的关系。

在这种调整中,存储器控制器可以对DQS信号可调整的延时,来与时钟信号的上升边沿对齐。

控制器不停对DQS进⾏延时,直到发现从0到1之间的跳变出现,然后DQS的延时通过这样的⽅式被建⽴起来了,由此可以保证tDQSS。

飞思卡尔i.MX6平台DRAM接口高阶应用指导-DDR3篇

飞思卡尔i.MX6平台DRAM接⼝⾼阶应⽤指导-DDR3篇飞思卡尔i.MX6平台DRAM接⼝⾼阶应⽤指导-DDR3篇本⽂意于介绍基于i.MX6平台如何使⽤官⽅⼯具调试DDR3.以下内容会在本⽂中涉及:原理图及PCB版图设计规则,DDR3初始化代码⽣成⼯具,DDR3⾃校准和压⼒测试⼯具。

Contents1DRAM Design Consideration (2)2DDR3 initialization Script Generation Aid (3)3DDR Stress Test Tool (10)4Further Reading (19)1 设计DRAM 的注意事项飞思卡尔的硬件应⽤团队总结了⼀个名为 “HW Design Checking List for i.Mx6” 的⽂档来分享i.MX6硬件设计经验。

请通过以下链接来获得该⽂档: https:///doc/5cb1ce021eb91a37f0115c67.html /docs/DOC-938191.1 原理图和布线设计规则下表中的内容摘⾃“HW Design Checking List for i.Mx6”。

使⽤i.MX6平台进⾏设计时务必遵循⾥⾯的规则。

设计者应当逐条予以确认。

如有任何疑问或不确定之处,请寻求飞思卡尔的技术⽀持本们的帮助。

原理图检查清单 1i.Mx6和DDR 芯⽚的ZQ 管脚需要分别外加⼀个1%精度的240欧姆电阻到地 2提供⼀路低噪声并且等于50%NVCC_DRAM 电压值的电源给DRAM_VREF 管脚(更多细节请参考原⽂档) 3DRAM_RESET 管脚需要外接⼀个10 K 欧姆的电阻到地(更多细节请参考原⽂档) 4差分时钟端接设计规则(更多细节请参考原⽂档) 5 如果DDR3颗粒的数量少于等于四颗-PCB 顶⾯两颗底⾯两颗,建议使⽤T 拓扑结构。

如果PCB 单⾯需要部多于两颗DDR3颗粒,建议使⽤Fly-by 拓扑结构。

DDR3基本知识

DDR3基本知识一、DDR3简介DDR3(double-data-rate three synchronous dynamic random access memory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。

DDR3在DDR2的基础上继承发展而来,其数据传输速度为DDR2的两倍。

同时,DDR3标准可以使单颗内存芯片的容量更为扩大,达到512Mb至8Gb,从而使采用DDR3芯片的内存条容量扩大到最高16GB。

此外,DDR3的工作电压降低为1.5V,比采用1.8V的DDR2省电30%左右。

说到底,这些指标上的提升在技术上最大的支撑来自于芯片制造工艺的提升,90nm甚至更先进的45nm制造工艺使得同样功能的MOS管可以制造的更小,从而带来更快、更密、更省电的技术提升。

DDR3的发展实在不能说是顺利,虽然在2005年就已经有最初的标准发布并于2007年应用于Intel P35 “Bearlake”芯片组上,但并没有像业界预想的那样很快替代DDR2,这中间还经历了对SDRAM业界影响深远的金融危机,不但使DDR3占领市场的速度更加减慢,还使DDR3在技术上一度走在世界领先地位的内存大厂奇梦达倒闭,实在是让人惋惜。

虽然如此,DDR3现今是并行SDRAM家族中速度最快的成熟标准,JEDEC标准规定的DDR3最高速度可达1600MT/s(注,1MT/s即为每秒钟一百万次传输)。

不仅如此,内存厂商还可以生产速度高于JEDEC标准的DDR3产品,如速度为2000MT/s的DDR3产品,甚至有报道称其最高速度可高达2500MT/s。

二、DDR存储器特性1) 时钟的上升和下降沿同时传输数据DDR存储器的主要优势就是能够同时在时钟循环的上升和下降沿提取数据,从而把给定时钟频率的数据速率提高1倍。

例如,在DDR200器件中,数据传输频率为200 MHz,而总线速度则为100 MHz。

2) 工作电压低DDR1、DDR2和DDR3存储器的电压分别为2.5、1.8和1.5V,因此与采用3.3V的正常SDRAM芯片组相比,它们在电源管理中产生的热量更少,效率更高。

DDR3简介

DDR3简介DDR3(double-data-rate three synchronous dynamic random access memory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。

DDR3在DDR2的基础上继承发展而来,其数据传输速度为DDR2的两倍。

同时,DD R3标准可以使单颗内存芯片的容量更为扩大,达到512Mb至8Gb,从而使采用DDR3芯片的内存条容量扩大到最高16GB。

此外,DDR3的工作电压降低为1.5V,比采用1.8V的DDR2省电30%左右。

说到底,这些指标上的提升在技术上最大的支撑来自于芯片制造工艺的提升,90nm甚至更先进的45nm制造工艺使得同样功能的MOS管可以制造的更小,从而带来更快、更密、更省电的技术提升。

DDR3的发展实在不能说是顺利,虽然在2005年就已经有最初的标准发布并于2007年应用于Intel P35 “Bearlake”芯片组上,但并没有像业界预想的那样很快替代DDR2,这中间还经历了对SDRAM业界影响深远的金融危机,不但使DDR3占领市场的速度更加减慢,还使DDR3在技术上一度走在世界领先地位的内存大厂奇梦达倒闭,实在是让人惋惜。

虽然如此,DDR3现今是并行SDR AM家族中速度最快的成熟标准,JEDEC标准规定的DDR3最高速度可达160 0MT/s(注,1MT/s即为每秒钟一百万次传输)。

不仅如此,内存厂商还可以生产速度高于JEDEC标准的DDR3产品,如速度为2000MT/s的DDR3产品,甚至有报道称其最高速度可高达2500MT/s。

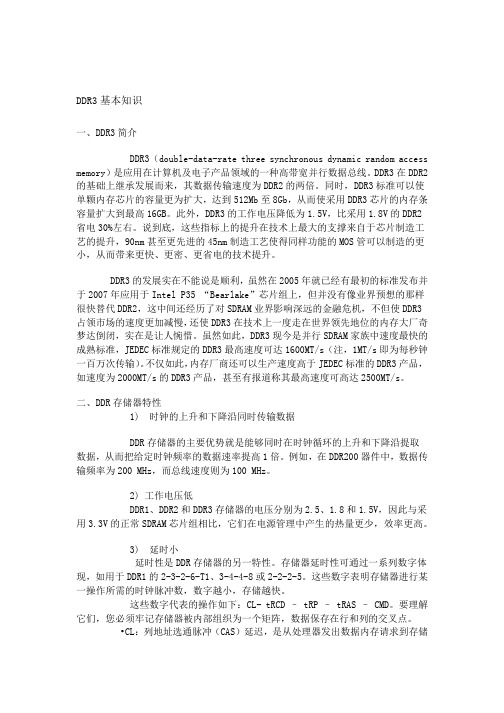

内存的工作速度内存技术从SDR,DDR,DDR2,DDR3一路发展而来,传输速度以指数递增,除了晶圆制造工艺的提升因素之外,还因为采用了Double Data Rate以及Prefetch两项技术。

实际上,无论是SDR还是DDR或DDR2、3,内存芯片内部的核心时钟基本上是保持一致的,都是100MHz到200MHz(某些厂商生产的超频内存除外)。

DDR3问题详细描述

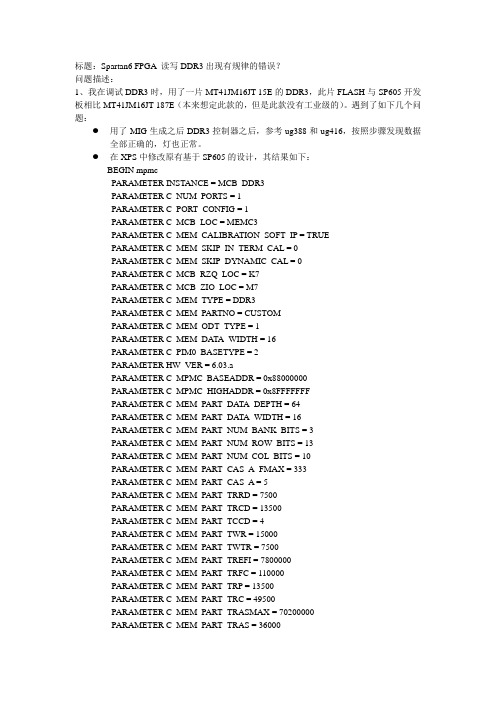

标题:Spartan6 FPGA 读写DDR3出现有规律的错误?问题描述:1、我在调试DDR3时,用了一片MT41JM16JT-15E的DDR3,此片FLASH与SP605开发板相比MT41JM16JT-187E(本来想定此款的,但是此款没有工业级的)。

遇到了如下几个问题:●用了MIG生成之后DDR3控制器之后,参考ug388和ug416,按照步骤发现数据全部正确的,灯也正常。

●在XPS中修改原有基于SP605的设计,其结果如下:BEGIN mpmcPARAMETER INSTANCE = MCB_DDR3PARAMETER C_NUM_PORTS = 1PARAMETER C_PORT_CONFIG = 1PARAMETER C_MCB_LOC = MEMC3PARAMETER C_MEM_CALIBRA TION_SOFT_IP = TRUEPARAMETER C_MEM_SKIP_IN_TERM_CAL = 0PARAMETER C_MEM_SKIP_DYNAMIC_CAL = 0PARAMETER C_MCB_RZQ_LOC = K7PARAMETER C_MCB_ZIO_LOC = M7PARAMETER C_MEM_TYPE = DDR3PARAMETER C_MEM_PARTNO = CUSTOMPARAMETER C_MEM_ODT_TYPE = 1PARAMETER C_MEM_DATA_WIDTH = 16PARAMETER C_PIM0_BASETYPE = 2PARAMETER HW_VER = 6.03.aPARAMETER C_MPMC_BASEADDR = 0x88000000PARAMETER C_MPMC_HIGHADDR = 0x8FFFFFFFPARAMETER C_MEM_PART_DATA_DEPTH = 64PARAMETER C_MEM_PART_DATA_WIDTH = 16PARAMETER C_MEM_PART_NUM_BANK_BITS = 3PARAMETER C_MEM_PART_NUM_ROW_BITS = 13PARAMETER C_MEM_PART_NUM_COL_BITS = 10PARAMETER C_MEM_PART_CAS_A_FMAX = 333PARAMETER C_MEM_PART_CAS_A = 5PARAMETER C_MEM_PART_TRRD = 7500PARAMETER C_MEM_PART_TRCD = 13500PARAMETER C_MEM_PART_TCCD = 4PARAMETER C_MEM_PART_TWR = 15000PARAMETER C_MEM_PART_TWTR = 7500PARAMETER C_MEM_PART_TREFI = 7800000PARAMETER C_MEM_PART_TRFC = 110000PARAMETER C_MEM_PART_TRP = 13500PARAMETER C_MEM_PART_TRC = 49500PARAMETER C_MEM_PART_TRASMAX = 70200000PARAMETER C_MEM_PART_TRAS = 36000BUS_INTERFACE SPLB0 = mb_plbPORT MPMC_Clk0 = clk_66_6667MHzPLL0PORT MPMC_Rst = sys_periph_resetPORT MPMC_Clk_Mem_2x = clk_666_6667MHzPLL0_nobufPORT MPMC_Clk_Mem_2x_180 = clk_666_6667MHz180PLL0_nobufPORT MPMC_PLL_Lock = Dcm_all_lockedPORT mcbx_dram_addr = fpga_0_MCB_DDR3_mcbx_dram_addr_pinPORT mcbx_dram_ba = fpga_0_MCB_DDR3_mcbx_dram_ba_pinPORT mcbx_dram_ras_n = fpga_0_MCB_DDR3_mcbx_dram_ras_n_pinPORT mcbx_dram_cas_n = fpga_0_MCB_DDR3_mcbx_dram_cas_n_pinPORT mcbx_dram_we_n = fpga_0_MCB_DDR3_mcbx_dram_we_n_pinPORT mcbx_dram_cke = fpga_0_MCB_DDR3_mcbx_dram_cke_pinPORT mcbx_dram_clk = fpga_0_MCB_DDR3_mcbx_dram_clk_pinPORT mcbx_dram_clk_n = fpga_0_MCB_DDR3_mcbx_dram_clk_n_pinPORT mcbx_dram_dq = fpga_0_MCB_DDR3_mcbx_dram_dq_pinPORT mcbx_dram_dqs = fpga_0_MCB_DDR3_mcbx_dram_dqs_pinPORT mcbx_dram_dqs_n = fpga_0_MCB_DDR3_mcbx_dram_dqs_n_pinPORT mcbx_dram_udqs = fpga_0_MCB_DDR3_mcbx_dram_udqs_pinPORT mcbx_dram_udqs_n = fpga_0_MCB_DDR3_mcbx_dram_udqs_n_pinPORT mcbx_dram_udm = fpga_0_MCB_DDR3_mcbx_dram_udm_pinPORT mcbx_dram_ldm = fpga_0_MCB_DDR3_mcbx_dram_ldm_pinPORT mcbx_dram_odt = fpga_0_MCB_DDR3_mcbx_dram_odt_pinPORT mcbx_dram_ddr3_rst = fpga_0_MCB_DDR3_mcbx_dram_ddr3_rst_pinPORT rzq = fpga_0_MCB_DDR3_rzq_pinPORT zio = fpga_0_MCB_DDR3_zio_pinEND但是程序进入DDR3运行时发现程序跑飞。

ddr3 学习分享

读/写

激活命令(active)

每次开始读写任务之前,Bank中的目标行必须进行激活命令,进入激活状态。 最多4个Bank可同时进入激活状态。 同一个Bank中不同行激活命令之前都需要进行Precharge命令。

读/写

当Bank中目标行激活后,就可以发出读/写命令。

过程:

首先确定行(包括片选及L-bank的确定),行有效命令,并使其处于激活状态; 然后确定列,列寻址信息与读/写命令同时发出。

DDR3 学习总结

Xieyu 2017.12.04

INDEX

MEMORY DDR3基本概念 DDR3工作机制

MEMORY

RAM

SRAM

DRAM

静态随机存储器 由触发器存储数据

动态随机存储器 MOS管栅极电容存储电荷

DRAM

SDRAM

DDR RRAM

单倍数据速率随机存储器 在时钟脉冲的上升沿读取数据速率动态存储器

而SR又分为:

1. 2.

局部自刷新

MR17来设置局部自刷新

Refresh&Precharge

Precharge(预充电):

DRAM工作时,L-BANK中只有一个行激活,当进行完读写操作后,在同一个LBANK操作时,关闭一行,打开另一行的过程称为预充电。 关闭行的过程,需要S-AMP对行内所有数据进行重写,地址进行复位。其过程 与REFRESH一样。

LPDDR3 pin脚定义

CK_t,CK_c CKE CS_n 差分时钟信号(Input) 时钟使能(Input) 片选(Input)

CA0-CA9

DQ0-15/31 DQS_t,DQS_c DM ODT ZQ Vdd/Vss

DDR3设计调试

DDR3设计调试DDR3设计配置:1.关于配置寄存器:部分配置寄存器基地址在0x2100_0000#define DDR3_BASE_ADDR (0x21000000)#define DDR_SDCFG (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000008))#define DDR_SDRFC (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000010))#define DDR_SDTIM1 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000018))#define DDR_SDTIM2 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000020))#define DDR_SDTIM3 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000028))#define DDR_PMCTL (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000038))#define RDWR_LVL_RMP_WIN (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000D4)) #define RDWR_LVL_RMP_CTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000D8)) #define RDWR_LVL_CTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000DC))#define DDR_ZQCFG (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000C8))#define DDR_PHYCTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000E4))⼤部分寄存器位于chip-level registers 0x0262_0000 #define DDR3PLLCTL0 (*(unsigned int*)(0x02620330))#define DDR3PLLCTL1 (*(unsigned int*)(0x02620334))#define DATA0_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262040C))#define DATA1_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620410))#define DATA2_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620414))#define DATA3_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620418))#define DATA4_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262041C))#define DATA5_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620420))#define DATA6_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620424))#define DATA7_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620428))#define DATA8_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262042C))#define DATA0_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262043C))#define DATA1_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620440))#define DATA2_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620444))#define DATA3_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620448))#define DATA4_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262044C))#define DATA5_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620450))#define DATA6_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620454))#define DATA7_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620458))#define DATA8_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262045C))#define DDR3_CONFIG_REG_0 (*(unsigned int*)(0x02620404))#define DDR3_CONFIG_REG_12 (*(unsigned int*)(0x02620434))#define DDR3_CONFIG_REG_23 (*(unsigned int*)(0x02620460))#define DDR3_CONFIG_REG_24 (*(unsigned int*)(0x02620464))⼆、KICK Unlock和DDR3 PLL配置初始化DDR3控制器之前必须完成KICK Unlock和DDR3 PLL的配置。

DDR3内存

DDR3内存优点1、频率的大幅度增加。

DDR3内存目前的规格有:DDR3-800、DDR3-1066、DDR3-1333、DDR3-1600。

起始频率为800Mhz,最高规格的DDR3-1600运行频率达到了1600Mhz,已经是DDR2内存最高频率的两倍,更有疯狂玩家将DDR3内存超频到2000Mhz以上。

不过现在的高端Intel 处理器也仅仅只有1333Mhz的前端总线,所以内存有点浪费了。

2、带宽的提高。

首先解释一下带宽的概念,带宽指的是内存的带宽,作一个比喻,我们可以把cpu和北桥看作是两个具有密切联系的城市,内存是两个城市之间交易的仓库和运输公路,内存容量相当于仓库的容量,带宽则是两座城市之间的公路。

DDR3内存可以提供高达12.8Gb/s的带宽,如果双通道的话则可以提供高达25.6Gb/s的带宽。

3、DDR2内存采用的4bit数据预取技术提升频率,DDR3内存则采用的是8bit数据预取技术提升频率。

4、延迟值的增加,绝对延迟的降低。

延迟指的是系统进入数据进行存取操作就绪状态前等待内存响应的时间。

体现内存延迟的就是我们通常说的时序,如:DDR2-800的标准时序是5-5-5-18,DDR3-800内存标准时序达到了6-6-6-15。

四个数字第一个数字表示为CAS Latency(简称CL值)内存CAS延迟时间,重要参数。

第二个数字RAS-to-CAS Delay (简称tRCD)内存行地址传输到列地址的延迟时间。

第三个则是ROV-Precharge Delay代表内存行地址选通脉冲预充电时间。

第四个ROW-active Delay(tRAS)代表内存行地址选通延迟,这些参数数值越低越好。

其实整个内存的延迟需要将颗粒的运行频率计算在内,所以CL值和延迟值是两个不同的概念,实际上DDR3内存的绝对延迟值相比DDR2内存降低了。

5、功耗的降低。

电压降至 1.5v。

DDR3-800相对DDR2-800降低达72%,DDR3-1066相对DDR2-1066降低达83%。

DDR3内存深度解析

DDR3内存深度解析2007年第⼆季度开始,DDR3平台就会全⾯启动。

从去年开始,全球各⼤内存芯⽚⼚商已经陆续推出DDR3颗粒,在今年秋季IDF展会上已经出现⽐较成熟的DDR3内存模组,估计明年开始将⼤量投⼊⽣产。

另⼀⽅⾯,全球最⼤的主板芯⽚供应商Intel 已经在蓝图上公布明年第⼆季度就会推出⽀持DDR3内存的新平台,看来草船、东风皆备,内存终于再次⾯临更新换代。

DDR2内存技术简单回顾 IT业界的正式内存规格是由JEDEC-- Joint Electronioc Device Engineering Council制定的,这包括了DDR、DDR2以及准备推出的DDR3,在官⽅规格中DDR最⾼速度为DDR400,但由于制程进步,DDR的速度已经完全超越了官⽅原定标准,故此后期出现了超⾼速DDR566并⾮官⽅规格。

继DDR400之后,JEDEC已认定DDR2为现时主流内存标准,虽然名字上只差毫厘,但DDR2和DDR2是完全不兼容的,⾸先DDR2的为240Pin接⼝⽐DDR的184Pin长,另外电压也⽐DDR的2.5v低许多,在1.8v的同频率下DDR2可⽐DDR低⼀半功耗,⾼频低功耗是DDR2内存的优点,⽽缺点则是DDR的延迟值⽐较⾼,在同频率下效能较低。

不单在规格上不兼容,其实DDR和DDR2在技术上有很⼤分别。

我们⽤的内存是透过不停充电及放电的动作记录数据的,上代SDRAM内存的核⼼频率就相等于传送速度,⽽每⼀个Mhz只会有传送1 Bit的数据,采⽤1 Bit Prefetch。

故此SDRAM 100Mhz的频宽为100Mbps。

但随着系统内部组件速度提升,对内存速度的要求增加,单纯提升内存频率已经不能应付需求,幸好及时发展出DDR技术。

DDR与SDRAM的分别在于传统SDRAM只能于充电那⼀刻存取数据,故此每⼀下充电放电的动作,只能读写⼀次,⽽DDR却把技术提升⾄在充电及放电时都能存取数据,故此每Mhz有两次存取动作,故此DDR会⽐SDRAM在同⼀频率下效能提⾼⼀倍,⽽100Mhz的DDR却可达⾄200Mbps存取速度,由于每⼀个Mhz都要有⼆次的资料存取,故此DDR每⼀Mhz会传送2Bit,称为2Bit Prefetch,⽽DDR颗粒频率每提升1Mhz,所得的效果是SDRAM的两倍。

DRAM Standards_DDR2 vs. DDR3 vs. DDR4

for Data Bus

Clock

Strobe

Single Ended and Differential Strobe Differential

Differential Strobe

Strobe

Not too much changes from DDR3 to DDR4 ???

04.08.2009

Hermann RZQ/6 Ohm ZQ calibration of output drive Strength

DDR2

Full and Reduced Drive Strength MR based calibration of output drive Strength

EKH - EyeKnowHow 09.10.2012

4

DDR4 Architecture

DDR4:

8bit Prefetch per Bank Group with Burst Length 8 Burst Chop 4 Burst Chop 4 (On the Fly or Programmable) Only Read burst switch between Sequential and Interleaved

EKH - EyeKnowHow 09.10.2012

6

DDR4 TDQS (RDQS)

DDR4

TDQS for x8 only

DDR3

TDQS support for mixed x4/x8 configurations

DDR2:

RDQS feature

EKH - EyeKnowHow 09.10.2012

EKH - EyeKnowHow 09.10.2012

DDR3

2002年 DDR3宣称

早在2002年6月28日,JEDEC就宣布开始开发DDR3内存标准,但从2006的情况来看,DDR2才刚开始普及, DDR3标准更是连影也没见到。不过已经有众多厂商拿出了自己的DDR3解决方案,纷纷宣布成功开发出了DDR3内存 芯片,从中我们仿佛能感觉到DDR3临近的脚步。而从已经有芯片可以生产出来这一点来看,DDR3的标准设计工作 也已经接近尾声。

DDR3

计算机内存规格之一

01 技术概论

03 与DDR2比较 05 性能优势

目录

02 新型设计 04 内存改进 06 发展历史

DDR3是一种计算机内存规格。它属于SDRAM家族的内存产品,提供了相较于DDR2 SDRAM更高的运行效能与更 低的电压,是DDR2 SDRAM(同步动态动态随机存取内存)的后继者(增加至八倍)。

(4)通用性好:相对于DDR变更到DDR2,DDR3对DDR2的兼容性更好。由于针脚、封装等关键特性不变,搭配 DDR2的显示核心和公版设计的显卡稍加修改便能采用DDR3显存,这对厂商降低成本大有好处。

DDR3显存在新出的大多数中高端显卡上得到了广泛的应用。许多低端的显卡也有采用DDR3显存的。

发展历史

与DDR2比较

1.突发长度(Burst Length,BL):由于DDR3的预取为8bit,所以突发传输周期(Burst Length,BL)也 固定为8,而对于DDR2和早期的DDR架构系统,BL=4也是常用的,DDR3为此增加了一个4bitBurst Chop(突发突 变)模式,即由一个BL=4的读取操作加上一个BL=4的写入操作来合成一个BL=8的数据突发传输,届时可通过A12 线来控制这一突发模式。而且需要指出的是,任何突发中断操作都将在DDR3内存中予以禁止,且不予支持,取而 代之的是更灵活的突发传输控制(如4bit顺序突发)。

三星DDR3 DRAM产品系列

1.5V 78 ball FBGA 1.35V Now

1.5V 78 ball FBGA 1.35V Now

8Banks

K4B2G0846E K4B2G0446E K4B2G0846E K4B4G0446B K4B4G0846B

1.5V 78 ball FBGA 1.35V Now

4Gb B-die

1. SAMSUNG Memory : K

2. DRAM : 4

3. DRAM Type B : DDR3 SDRAM

10. Revision M : 1st Gen. A : 2nd Gen. B : 3rd Gen. C : 4th Gen. D : 5th Gen. E : 6th Gen. F : 7th Gen. G : 8th Gen. H : 9th Gen. 11. "-" 12. Package Type H M B E O : : : : : FBGA (Halogen-free & Lead-free) FBGA (Halogen-free & Lead-free, DDP) FBGA (Halogen-free & Lead-free, Flip Chip) FBGA(Lead-free & Halogen-free, QDP) FBGA(Lead-free & Halogen-free, QDP for 64GB LRDIMM)

2Gb E-die

Dec. 2012

DDR3 SDRAM Memory

Package & Power, Temp. & Speed BCF8/H9/K0/MA BCF8/H9/K0/MA BYF8/H9/K0 BYF8/H9/K0 HCF8/H9/K0 HCF8/H9/K0 HYF8/H9 HYF8/H9 HCF8/H9/K0/MA HCF8/H9/K0/MA HYF8/H9/K0 HYF8/H9/K0 BCH9/K0/MA BCH9/K0/MA BYH9/K0 BYH9/K0 HCF8/H9/K0/MA HCF8/H9/K0/MA HCH9/K0 HYF8/H9/K0 HYF8/H9/K0 HYH9/K0 BCH9/K0/MA BCH9/K0/MA BYH9/K0 BYH9/K0 BCH9/K0/MA BCH9/K0/MA BYH9/K0 BYH9/K0 MCK0 MYH9/K0 MCH9/K0 MYH9/K0 ECH9/K0 EYH9/K0 OCK0 OYF8/H9/K0 Org. 256M x 4 128M x 8 256M x 4 128M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 1G x 4 512M x 8 256M x 16 1G x 4 512M x 8 256M x 16 1G x 4 512M x 8 1G x 4 512M x 8 1G x 4 512M x 8 1G x 4 512M x 8 DDP 512M x 16 DDP 512M x 16 DDP 256M x 32 DDP 256M x 32 QDP 4G x 4 QDP 4G x 4 QDP 4G x4 QDP 4G x4 1.5V 78 ball FBGA 1.35V Now 1.35V 1.5V 78 ball FBGA Now VDD Voltage1 1.5V 78 ball FBGA 1.35V Now PKG Avail. NOTE

DDR3的工作原理

硬件十万个为什么—— DDR3的工作原理杜盼dzplay@目录☐DDR的片内结构☐DDR的读写流程☐DDR的基础命令☐DDR的读写时序与参数DDR的片内结构框图上图是一片容量4Gb,数据位宽为8bit的DDR3 SDRAM的结构图DDR的片内结构说明1.控制器单元:包括输入命令解析,模式配置&控制部分;2.行地址选通单元:行激活通过此处操作;3.Bank控制逻辑:行/列地址解码用到bank选通4.列地址选择单元,读写操作同时在打开列地址的时候送到1;5.内部存储阵列,此处分8个bank,已4g8bit的颗粒为例;每个bank分65536行,128列,每个cell存储8*bl的数据宽度;6.读写数据缓存及接口驱动;dq数据在此变换位宽后内外交互;7.锁存与控制逻辑:刷新与预充电用到该模块。

目录☐DDR的片内结构☐DDR的读写流程☐DDR的基础命令☐DDR的读写时序与参数DDR的操作☐启动:上电->解复位->初始化->ZQCL-> LEVELING->IDLE(READY) ☐读:IDLE->行激活->读数据(1次或多次突发)->预充电->IDLE☐写:IDLE->行激活->写数据(1次或多次突发)->预充电->IDLE☐刷新:IDLE->REF->IDLE☐自刷新的进入与退出:IDLE->SFR->IDLE☐定期校正:IDLE->ZQCS->IDLE,一般外部温度或电压改变时操作☐动态更改配置:IDLE->MRS/MPR->IDLEDDR 的读操作(内部流程图)1243DDR的读操作(步骤说明)ddr发起一次读的过程包含一系列命令有:1.操作开始于Active命令——Active命令同时并发含带地址位,以选择Bank和Row地址(BA0-BA2选择BANK、A0-A15选择Row)。

DRAM信号完整性

DRAM的信号完整性RAM的种类目前D厂常用的是SDRAM、DDR、DDR2,DDR3还用不到。

SRAM容量不能满足要求,成本又太高。

DRAM,每个内存单元更少的电路实现,内存单元基于电容器上贮存的电荷,典型的DRAM 单元使用一个电容器及一个或三个FET(场效应晶体管)制成。

低成本、高密度,缺点:信息易丢失。

SRAM,每单元六个FET 器件。

与DRAM 相比,SRAM 使用起来更简便,接口更容易,数据访问时间更快。

DRAM读取具有破坏性,也就是说,在读操作中会破坏内存单元行中的数据。

因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。

这一操作称为预充电,是行上的最后一项操作。

必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。

DDR2 SDRAM 较DDR SDRAM 有多处改进。

DDR2 SDRAM时钟速率更高,从而提高了内存数据速率。

随着时钟速率提高,信号完整性对可靠运行内存变得越来越重要。

随着时钟速率提高,电路板上的信号轨迹变成传输线,在信号线末端进行合理的布局和端接变得更加重要。

目前DRAM的信号带宽:DDR SDRAM 数据速率内存时钟DDR-266 266 Mb/s/ 针脚133 MHzDDR-333 333 Mb/s/ 针脚166 MHzDDR-400 400 Mb/s/ 针脚200 MHzDDR2 SDRAM 数据速率内存时钟DDR2-400 400 Mb/s/ 针脚200 MHzDDR2-533 533 Mb/s/ 针脚266 MHzDDR2-667 667 Mb/s/ 针脚333 MHzDDR2-800 800 Mb/s/ 针脚400 MHzDDR2-1066 1066 Mb/s/ 针脚533 MHzDDR3 SDRAM 数据速率内存时钟DDR3-800 800 Mb/s/ 针脚400 MHzDDR3-1066 1066Mb/s/ 针脚533 MHzDDR3-1333 1333Mb/s/ 针脚667 MHzDDR3-1600 1600 Mb/s/ 针脚800 MHzDDR3-1866 1866 Mb/s/ 针脚933 MHzDDR3-2133 2133 Mb/s/ 针脚1066 MHzDRAM的时钟和命令信号的端接相对简明,因为这些信号是单向的,并端接在电路板上。

一种应用于DDR3 DRAM的ZQ校准方法

2 zQ校 准 电路 架构

现 不 同程度 影 响下 的偏移 2)ZQ引脚 仃 可能 没 有 外接参 考 电 m 在 这 类

罔 1为 zQ校准 电路 的架构 图 .如图示 ,住 校准 — 广作 进 i-ft,t,利用 zQ端 【1的 外接 电 l5fi,首先 进 行 对 卜托 电 5II的校 准 I 作 ,然 后荩于 对 卜扎 电阻 的预俏 , 进 行 下j. 电 阻 的校准 此 处的 f 托 电阻 与下扎 电阻

Key words:DRAM;ZQ calibration;comparator;SAR

k ●● ^ ,^ … ^… :…

…

n

匝

——————

1 简 介

短校ห้องสมุดไป่ตู้准 I 作 (ZQCS)只有 64个时 钟周 期 .校 准 l 作 的基 小思路 为 :长 校准 川于在 芯 片刚肩 动时 刻和 自

一 种应用于 DDR3 DRAM 的 ZQ 校准 方法

· 王 小光 ,王 嵩,谈杰 ,李进 (西安 紫光 国芯 半导体有限公 司,陕西 西安 ,710075)

摘要 :在 当今 的 DRAM存储 器技术 中,zQ管脚的作用是为 了能够给 高速的接 口电路提供更为准确 的阻 抗 。本 文 引入 了一种 DDR3的 zQ校 准方 法 ,该 电路 在 38 am的 DRAM工艺 中 已经得到 实现 。它 包括 了比较 器校 准 ,zQ状 态监 测 ,长 、短 校 准模 式和 调试 模 式 。该 电路 可 以 支持 多颗 芯 片封 装形 式下 的共 享 zQ端 口 的工作条件。文 中介绍 了一种 能提 高校准速度的 SAR搜索方法,测试结果表明该电路在工艺偏差 巨大的 DRAM生产工艺下仍 旧满足 JEDEC的各项指标要求,并具有 非常 出色的鲁棒性。 关键 词 :DRAM;ZQ校 准 ;比较 器 ;逐 次逼 近算 法