PDP信号存储处理IP核的设计与VerilogHDL实现

HDLC协议IP核的设计(全文)

HDLC协议IP核的设计(全文)《电子设计工程杂志》2014年第十一期1HDLC的帧结构首先回顾一下HDLC基本的帧结构形式。

HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组合所表示的命令和响应来实现,这些监控比特和信息比特一起以帧的形式传送。

每帧的起始和结束以”7E”(01111110)做标志,两个”7E”之间为数据段(包括地址数据、控制数据、信息数据)和帧校验序列。

帧校验采用CRC算法,对除了插入的”零”以外的所有数据进行校验。

为了避免将数据中的”7E”误为标志,在发送端和接收端要相应地对数据流和帧校验序列进行”插零”及”删零”操作。

2原理框图基于FPGA的HDLC协议的实现原理框图如图1所示。

该框图包括3个部分:对外接口部分、HDLC发送部分、HDLC接收部分。

以下对3个部分的实现分别进行论述。

2.1对外接口模块对外接口部分主要实现HDLC对外的数据交换。

包括CPU接口、发送FIFO、发送接口、接收FIFO以及接收接口。

本设计是以总线的形式实现HDLC与外部CPU的通信。

当需要发送数据时,外部CPU通过总线将待发数据写入FIFO(FIFO的IP核在各开发软件中都是免费提供的,在程序中只需直接调用即可,故在此不再详细描述)。

之中。

发送数据准备就绪标志(TX_DAT_OK);接收数据时,当对外接口模块接收到数据有效信号时,根据接收模块发来的写信号(WR_MEM)将数据写入接收FIFO中。

接收完一帧数时向CPU 发送中断信号(INT),通知CPU读取数据。

2.2HDLC发送模块HDLC发送部分主要实现HDLC发送功能。

当接收到数据准备就绪标志(TX_DAT_OK)后,向对外接口模块发送读使能(RD_MEM_EN)和读信号(RD_MEM),通过局部总线将待发数据存入发送缓冲区,在T_CLK的控制下将数据从HDLC_TXD管脚发出。

数据发送模块采用状态机来完成发送各个阶段的切换。

状态切换流程图如图2所示。

verilog-hdl讲座

Verilog-HDL与CPLD/FPGA设计应用讲座主编: 常晓明第 1 讲 Verilog-HDL与CPLD/FPGA设计1.1 从模拟世界到数字世界1.2 数字电路的不同设计过程1.3 用HDL描述数字电路1.4 HDL有几种?1.5 硬件实现的承担者---CPLD/FPGA1.6 Xilinx公司的CPLD--XC9500系列1.7 结语1.1 从模拟世界到数字世界在70年代初期,家用电子产品末过于晶体管收音机、电唱机、扩大器了。

那时,笔者所在的一个小城市销售3管晶体管收音机。

她一上市就优先供应农村,为的是让中央人民广播电台的声音直达有线广播不能到达的山区。

开始时城市人是较难得到这样的家电产品的。

笔者当时常出差于上海,为了自己能装一台梦寐以求的收音机,节省每天的2角钱出差补助,吃的是阳春面,用节省的钱去买晶体管等元器件。

当时的元件市场可以说是"一片模拟世界"。

到了1974年前后,笔者所在的电信单位搞技术革新,用晶体管代替继电器,研制晶体管交换机。

当时我对豆粒大的晶体管能代替形如打火机大的继电器而震撼不已,加之没有震动声音、耗电低等优点,更是使我着迷。

当时,看到老技术员用晶体管搭建门电路,实现"与""或"等功能。

业余时间自己也自费购买元件,搭建一些功能电路。

到了1975年以后,中小规模集成电路逐步上市。

之后的几年,在大学里也开始讲授集成电路的课程。

1979年以后,日本的荧光显示式计算器开始在中国市场出现;1983年前后,微处理器的学习形成高潮。

1986年,在数字技术的进步与微处理器技术的影响下,笔者开始动手制作Z80单片机。

在不用任何调试设备的情况下,自己编写机器代码,组装编程器,……直到制作出第一台最简单的单板机。

第一次感受数字技术和微处理器,使笔者兴奋不已。

近几年来,随着IT业的高速发展,整个电子世界都朝着数字化、小型化、多功能化、低耗电的方向发展,学习数字电路的条件与过去相比也发生了巨大的变化。

Verilog+HDL简明教程

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

V erilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

V erilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。

但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。

当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

===============================中文版Verilog HDL简明教程:第1章简介V erilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

V erilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

V erilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

Verilog_HDL讲座第7讲用Verilog_HDL做CPLD设计_组合逻辑

图 6 2 位二进制编码器的引脚配置画面

7.4 1 位数据比较器的实现

数据比较器是用来对两个二进制数 的大小进行比较或检测是否相等的逻辑 电路,在数字逻辑的设计中占有重要的 位置。

1位数据比较器应有两个宽度为1的 数据输入端口。设其输入分别为 A 和 B, 输出分别为 A = B 、A > B 和 A < B 。可列 出真值表,如表 4 所示。

图 1 与非门设计的逻辑功能框图

我们考虑采用如图 3 所示的逻辑功能框

图来实现。

其中,S1_1 和 S1_2 表示开关,对

应表 1 中的 S1 和 S2,打开时为高电平,

闭合时为低电平,作为输入;LED0 表

示发光二级管,对应表 1 中的 LED,作

为输出;33、34 和 44 为上述变量对应 芯片 XC9536 的引脚;33 和 34 旁边的

/* ENCORDER

*/ / /

主模块

module E N C ( S1, LED );/ /

模块名及参数定义,范围至 endmodule

input [3:0] S1; // 输入端

口定义,S1[0]—S1[3]分别对应第34、33、

29 和 28 脚

output [1:0] L E D ; // 输出端

技术讲座

TECHNICAL LECTURES TECHNICAL LECTURES TECHNICAL LECTURES TECHNICAL LECTURES

ELECTRONIC PRODUCTS

CHINA

电平,闭合时为低电平,作为 2-1 数据 选择器的输入;LED0 表示发光二级管, 对应表 2 中的 F,作为其输出。29、33、 34 和 44 是上述变量对应芯片 XC9536 的 引脚。虚线框中的部分是 CPLD 设计,实 现 2-1 数据选择器的功能。

Verilog HDL基础

还可以在模块实例引用时,改变引用模块或实例中已 定义的参数。

module decode(A,F) parameter IN_Width=4,OUT_Width=16; …

endmodule;

4.4 变量--数据类型

wire型

用assign赋值的组合逻辑信号,输入输出信号 默认为wire型,取值为0、1、x和z

4.2 Verilog基本语法—语言要素

间隔符: Verilog 的间隔符主要起分隔文本的作用, 可以使文本排列有序,便于阅读与修改。

间隔符包括空格符(\b)、TAB 键(\t)、换行符(\n) 及换页符。

注释符:注释只是为了改善程序的可读性,在编译时 被忽略。

多行注释符“/* --- */”:用于写多行注释; 单行注释符“//”:以开始到行尾结束为注释文字。

如:8’b01010011,8’h53

x代表不定值,z代表高阻,每个字符所代表的 宽度取决于所用进制

下划线:用来分隔数,以提高程序可读性

如16’b0011101001010001可写成 16’b0011_1010_0101_0001

4.4常量--parameter

Parameter用来定义一个标识符代表一个常量,称为 符号常量,用以提高程序的可读性,经常用于定义变 量的宽度。

4.7 循环移位寄存器(1)

always @ (posedge clk) if(preset) begin q3=0; q2=1; q1=1; end begin q3=q2; q2=q1; q1=q3; end;

北航夏宇闻复杂数字逻辑系统的VerilogHDL设计方法简介

信号处理的工作是可以事后进行。

• 实时系统:

信号处理的工作必须在规定的很短的时间内完 成。

数字信号处理系统的实现

• 非实时系统: 通用的计算机和利用通用计算机改装的设备,

主要工作量是编写 “C” 程序。

• 实时系统: 信号处理专用的微处理器为核心的设备,主 要工作量是编写汇编程序。

行步骤是否正确。 逻辑综合:把RTL级模块转换成门级 。 后仿真:用门级模型做验证,检查门的互连逻辑

其功能是否正确。 布局布线: 在门级模型的基础上加上了布线延时 布局布线后仿真:与真实的电路最接近的验证。

行为级和RTL级

module muxtwo (out, a, b, sl);

input a,b,sl;

end endmodule

Verilog HDL模块的测试

`include myadder.v module t; wire [8:0] sumout; reg [7:0] ain, bin; reg clk; myadder(.clock(clk), .reset(rst), .a(ain), .b(bin), .sum(sumout));

• 行为级:有关行为和技术指标模块,容易理 解

• RTL级:有关逻辑执行步骤的模块,较难理 解

• 门级 :有关逻辑部件互相连接的模块,很 难理解

• 开关级:有关物理形状和布局参数的模块, 非常难理解

抽象级别和综合与仿真的关系

行为仿真:行为的验证和验证模块分割的合理性 前仿真 :即 RTL级仿真,检查有关模块逻辑执

International)

有哪几种硬件描述语言? 各有什么特点?

• VHDL - 比VerilogHDL早几年成为I EEE标准; - 语法/结构比较严格,因而编写出的 模块风格比较清晰; - 比较适合由较多的设计人员合作完成 的特大型项目(一百万门以上)。

基于FPGA的浮点运算器IP核的设计与实现

基于FPGA的浮点运算器IP核的设计与实现摘要

本文介绍了基于FPGA的浮点运算器IP核的设计与实现。

在实现过程中,我们采用Verilog HDL实现了一个32位浮点运算器的IP核,它能提

供执行加法、减法、乘法、除法以及规范化的功能,并具有很高的精确度。

在Xilinx FPGAs上实现,该IP核实现了高性能和可靠性。

实验结果表明,这种FPGA浮点运算器IP核的性能可以满足各种应用需求。

关键词:FPGA;浮点运算;IP核;Verilog HDL

1. Introduction

随着技术的发展,浮点运算在计算机体系结构中越来越重要。

它不仅

可以提高运算精度,而且可以准确表达计算机的结果。

为了实现高质量的

数字信号处理(DSP)系统,FPGA浮点运算器IP核变得越来越重要。

FPGA的浮点运算器IP核提供了一个高性能、可靠的实现环境,使得

浮点运算器在DSP系统中得以良好的应用。

此外,基于FPGA的浮点运算

器IP核还具有可编程性、低功率、灵活性和低成本等优势。

本文讨论了使用Verilog HDL实现基于FPGA的浮点运算器IP核的设

计与实现。

它包括浮点运算器的功能、实现及性能等方面的介绍。

2. Design and Implementation of FPGA Floating Point Unit

2.1 Floating Point Unit Design

在本文中,我们采用Verilog HDL实现了一个具有32位数据宽度的

浮点运算器IP核。

此外,它还具有加法、减法、乘法、除法以及规范化

的功能。

EDA设计技术教学课件 第3章 Verilog HDL语言

第3-6页

■

©淮南师范学院电子工程学院

VerilogHDL与CPLD|\FPGA设计 电子教案

关键字

Verilog HDL定义了一系列保留字,即关键字, 注意只有小写的关键字才是保留字。 • 例如: always \always ALWAYS • 标识符always是个关键字,而标识符ALWAYS 不是关键字,转义标识符\always与关键字 always并不完全相同。

第3-7页

■

©淮南师范学院电子工程学院

VerilogHDL与CPLD|\FPGA设计 电子教案

3.3注释

在Verilog HDL中有两种形式的注释,用于编译 控制或添加注释信息。例如下述用于编译控制 的注释语句: / * begin //(1) if(Count>15)Count = 0; //(2) else Count = Count+1; //(3) end //(4) */ //(5)

第3-11页

■

©淮南师范学院电子工程学院

VerilogHDL与CPLD|\FPGA设计 电子教案

在模块或语句块的起始部分或关键部分,应 明确注释该语句块的相关信息

initial // Clock generator begin clk = 0; #10 forever #10 clk = !clk; end

VerilogHDL与CPLD|\FPGA设计 电子教案

第3章 Verilog HDL语言

EDA设计技术

第3-1页

■

©淮南师范学院电子工程学院

VerilogHDL与CPLD|\FPGA设计 电子教案

3.1 Verilog HDL的前世今生

对Verilog HDL影响最大的是Brunel大学开发 的HILO-2系统。HILO-2成功地将门级和寄 存器传输级的抽象结合起来,还支持校验、 仿真、时序分析、失效仿真和测试; 1983年冬, Gateway Design Automation公司 设计了Verilog HDL语言; 1988年,当时名不见经传的Synopsys公司将 Verilog HDL引入到它的综合工具中;

基于CPLD/FPGA平台I2C总线IP核的设计

基于CPLD/FPGA平台I2C总线IP核的设计摘要:本文通过对一个I2C总线IP核的设计,介绍了用VHDL语言设计和实现该IP核的过程。

首先简要介绍了I2C总线协议的标准及应用,分析了影响8位MPU的传输速率低的因素,然后提出了基于CPLD/FPGA平台设计“虚拟器件”I2C总线IP核的设想。

其次给出系统自顶向下的设计方案。

接着对系统的功能进行了详细的总体规划与层次设计,讲解了系统体系结构和系统各个功能模块的电路设计。

最后进行了调试,并给出在MAX+Plus II 10.0环境下的仿真波形。

关键词:I2C总线VHDL IP核CPLD/FPGA一、系统设计的背景与意义在现代通讯类产品、仪器仪表、工业测控系统中,逐渐形成了以一个或多个微处理器组成的智能系统,并且对外围电路之间主要是实现控制功能,因而I2C 总线对应用系统的开发带来很多好处:一方面,二线制的I2C串行总线使得各电路单元之间只需最简单的连接,而且可实现电路系统的模块化、标准化设计;另一方面,标准的I2C总线模块的组合方式大大地缩短了新产品的开发周期,并且I2C总线系统构成具有最大的灵活性和极好的可维护性。

目前,在绝大多数单片机应用系统中仍保持着单主结构(其中包括一些双主系统中,主节点之间不能进行直接通信的情况)。

在单主系统中,I2C总线只存在着主方式,I2C总线的数据传输状态比较简单,主要是实现单片机(或MCU)对I2C总线简单的读/写操作。

因此,利用VHDL硬件语言实现I2C总线接口功能,并通过下载到CPLD/FPGA实现与其他节点的数据传输,使这些器件不受系统单片机必须带有I2C总线接口的限制。

这也大大地扩展了I2C总线器件的适用范围,使I2C总线在应用系统设计中有着更为广泛的应用。

二、系统设计方案目前,许多IC器件广泛采用I2C接口来读/写数据,但是多数的8位微处理器都没有专用的I2C接口,因此一般只有通过GPIO口利用软件编程来实现I2C 总线的数据传送。

Vivado集成开发环境Verilog HDL设计流程

编译RTL源文件 并且加载RTL网表,用于交互式分析。 设计者可以查看RTL结构,语法和逻辑定义。

分析和报告能力包括:

Vivado HDL基本设计流程

--详细描述

RTL编译有效性和语法检查; 研究网表和原理图; 设计规则检查; 使用一个RTL端口列表的早期I/O引脚规划; 可以在一个视图中选择一个对象,然后在其他视图中交叉检测,

Vivado HDL基本设计流程 --FPGA配置电路

Vivado HDL基本设计流程 --硬件平台配置

下载设计到FPGA 生成PROM文件 烧写到SPI Flash

设计验证 先断电再上电 设计验证

硬件开发平台介绍

A7-EDP-1

FPGA CLB资源

XC7A75T-FGG484

Vivado HDL基本设计流程 --详细描述

详细描述(Elaboration)是指将RTL优化到FPGA技术。 Vivado集成开发环境允许实现下面的功能:

顺利完成综合过程后,就会生成综合后的网表。设计者就可 以将综合后的网表,以及XDC文件或者Tcl脚本一起加载到存 储器中,用于后续的实现过程。

硬件连接关系

--LED灯

硬件连接关系

--开关驱动电路

硬件连接关系

--FPGA连接电路

Vivado HDL基本设计流程 --设计实现

Vivado工具实现流程:Tcl命令

使用硬件开发平台上的六个LED灯来显示六种逻辑运算 的结果。

Vivado HDL基本设计流程

--框图表示

建立新的设计工程 添加新的设计文件 详细描述(Elaboration)

行为级仿真 设计综合(Synthesis) 设计约束(Constraint) 设计实现(Implement)

Verilog HDL语言在FPGACPLD开发中的应用

Verilog HDL语言在FPGA/CPLD开发中的应用摘要:通过设计实例详细介绍了用Verilog HDL语言开发FPGA/CPLD的方法,并通过与其他各种输入方式的比较,显示出使用Verilog HDL语言的优越性。

关键词: Verilog HDL;FPGA/CPLD;EDA1 引言近30年来,由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。

特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA和嵌入系统的多种模式。

可以说EDA产业已经成为电子信息类产品的支柱产业。

EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(HDL)描述电路系统。

就FPGA和CPLD开发而言,比较流行的HDL 主要有Verilog HDL、VHDL、ABEL-HDL和 AHDL 等,其中VHDL和Verilog HDL因适合标准化的发展方向而最终成为IEEE标准。

但与VHDL相比,Verilog HDL有个最大的优点:它是一种非常容易掌握的硬件描述语言,只要有C语言的编程基础,一般经过2~3个月的认真学习和实际操作就能掌握这种设计技术。

并且完成同一功能Verilog HDL的程序条数一般仅为VHDL的1/3。

而VHDL设计技术则不很直观,需要有EDA编程基础,通常需要有多余半年的专业培训才能掌握这们技术。

可见,用Verilog HDL语言有更高的优越性。

2 设计实例通常设计数字电路大都采用自顶向下将系统按功能逐层分割的层次化设计方法,这比传统自下向上的EDA设计方法有更明显的优势(当时的主要设计文件是电路图)。

因为由自顶向下的设计过程可以看出,从总体行为设计开始到最终逻辑综合,形成网络表为止。

每一步都要进行仿真检查,这样有利于尽早发现系统设计中存在的问题,从而可以大大缩短系统硬件的设计周期。

这也是HDL语言设计系统硬件的最突出的优点之一。

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

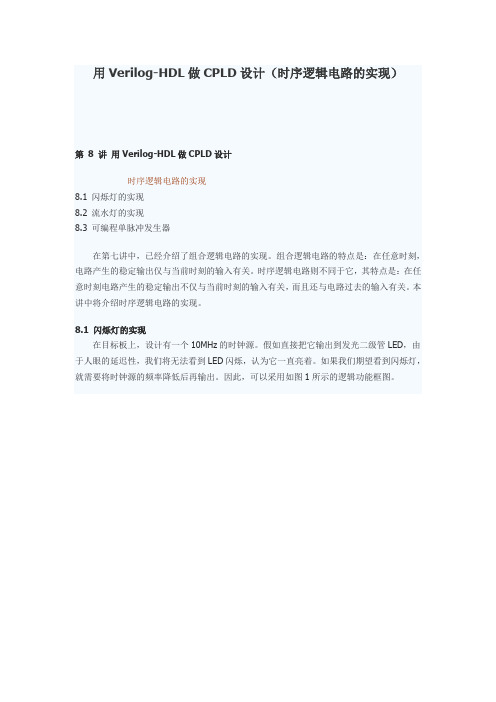

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)第8 讲用Verilog-HDL做CPLD设计时序逻辑电路的实现8.1 闪烁灯的实现8.2 流水灯的实现8.3 可编程单脉冲发生器在第七讲中,已经介绍了组合逻辑电路的实现。

组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。

时序逻辑电路则不同于它,其特点是:在任意时刻电路产生的稳定输出不仅与当前时刻的输入有关,而且还与电路过去的输入有关。

本讲中将介绍时序逻辑电路的实现。

8.1 闪烁灯的实现在目标板上,设计有一个10MHz的时钟源。

假如直接把它输出到发光二级管LED,由于人眼的延迟性,我们将无法看到LED闪烁,认为它一直亮着。

如果我们期望看到闪烁灯,就需要将时钟源的频率降低后再输出。

因此,可以采用如图1所示的逻辑功能框图。

图1 闪烁灯的逻辑功能框图其中,CLK表示10MHz的时钟源,作为输入;LED0-LED7表示发光二极管,作为输出;6、44、43、38、37、36、35、40和42是上述变量对应芯片XC9536的引脚。

虚线框中的部分是CPLD设计,用于实现闪烁灯的功能。

如图1所示,在XC9536中,加入计数电路与判别电路。

计数电路可用计数器实现。

每来一个时钟脉冲CLK,计数器就加1。

而每当判断出计数器达到某个数值时,就使得灯LED0-LED7的亮灭反转一次,即:周期性地输出高电平"1"和低电平"0"。

这样设计也就相当于把10MHz的时钟源分频后再输出。

如果最终要使得灯1s闪烁一次,即:输出1Hz的时钟脉冲,就需要把10MHz的时钟经过107分频。

根据上述分析,可以得到下面的Verilog- HDL 描述。

/* 闪烁灯的Verilog-HDL描述*/module LIGHT ( CLK, LED ); // 模块名及端口参数,范围至endmoduleinput CLK; // 输入端口定义,对应第6脚output [7:0] LED;// 输出端口定义,LED[0]-LED[7]分别对应第44、43、38、37、36、35、40和42脚reg [7:0] LED; // 输出端口定义为寄存器型reg [22:0] buffer; // 中间变量buffer定义为寄存器型always @ ( posedge CLK )// always语句,表示每当CLK的上升沿到来时,完成begin-end之间语句的操作begin // 顺序语句,到end止buffer = buffer +1; // 缓冲器buffer按位加1if ( buffer == 23'b11111111111111111111111)// 判别buffer中的数值为(2^23-1)≈10^7时,做输出处理//"23"表示以位计的数值长度,"b"表示二进制,"11…1"表示二进制的数字序列beginLED=~LED; // LED[0]-LED[7]反转一次,即:由0变为1,或由1变为0endendendmodule把以上闪烁灯的描述,用WebPACK Project Navigator软件,生成目标文件,并通过下载电缆写入芯片XC9536中。

VerilogHDL数字集成电路设计原理与应用教学课件ppt作者蔡觉平_第2章

第2章 Verilog HDL基础知识2.1 Verilog HDL的语言要素2.2 数据类型2.3 运算符2.4 模块本章小结12 Verilog HDL 语法来源于C 语言基本语法,其基本词法约定与C 语言类似。

程序的语言要素也称为词法,是由符号、数据类型、运算符和表达式构成的,其中符号包括空白符、注释符、标识符和转义标识符、关键字、数值等。

2.1 Verilog HDL 的语言要素2.1.1 空白符 空白符包括空格符(\b)、制表符(\t)、换行符和换页符。

空白符使代码看起来结构清晰,阅读起来更方便。

在编译和综合时,空白符被忽略。

Verilog HDL程序可以不分行,也可以加入空白符采用多行编写。

3 例2.1-1空白符使用示例。

initial begin a = 3'b100; b = 3'b010; end 相当于: initial begin a = 3'b100; b = 3'b010; end452.1.2 注释符 Verilog HDL语言中允许插入注释,标明程序代码功能、修改、版本等信息,以增强程序的可阅读性和帮助管理文档。

Verilog HDL中有两种形式的注释。

(1) 单行注释:单行注释以“//”开始,Verilog HDL忽略从此处到行尾的内容。

(2) 多行注释:多行注释以“/*”开始,到“*/”结束,Verilog HDL忽略其中的注释内容。

需要注意的是,多行注释不允许嵌套,但是单行注释可以嵌套在多行注释中。

例2.1-2 注释符使用示例。

单行注释: assign a=b & c; //单行注释 多行注释: assign a[3:0]=b[3:0]&c[3:0;]; /*注释行1 注释行2 */ 非法多行注释:/*注释内容 /*多行注释嵌套多行注释*/ 注释内容*/ 合法多行注释:/*注释内容 //多行注释嵌套单行注释*/672.1.3 标识符和转义标识符 在Verilog HDL中,标识符(Identifier)被用来命名信号名、模块名、参数名等,它可以是任意一组字母、数字、$符号和_(下划线)符号的组合。

VHDL 和Verilog LPM模块&IP核应用

7.3 基于LPM的流水线乘法累加器设计

7.3.3 乘法累加器的仿真测试

7.3 基于LPM的流水线乘法累加器设计

7.3.3 乘法累加器的仿真测试

7.3 基于LPM的流水线乘法累加器设计

7.3.4 乘法器的Verilog文本表述和相关属性设置

7.3 基于LPM的流水线乘法累加器设计

演示示例:/KX_7C5EE+/EXPERIMENTs/EXP23_DDS/DDSP。

实验与设计

7-6 DDS移相信号发生器设计

(1)实验原理:

(2)实验内容1: (3)实验内容2: (4)实验内容3: (5)思考题:(6) 实验报告:

实验与设计

7-7 4X4阵列键盘键信号检测电路设计

(1)实验原理:

7.4.4 Verilog的存储器描述及相关属性

1.存储器端口描述

2.存储器的Verilog一般描述

7.4 LPM 随机存储器的设置和调用

7.4.4 Verilog的存储器描述及相关属性

2.存储器的Verilog一般描述

7.4 LPM 随机存储器的设置和调用

7.4.4 Verilog的存储器描述及相关属性

3.存储器初始化文件属性应用

7.4 LPM 随机存储器的设置和调用

7.4.4 Verilog的存储器描述及相关属性

3.存储器初始化文件属性应用

7.4 LPM 随机存储器的设置和调用

7.4.4 Verilog的存储器描述及相关属性

4.文本方式调用存储器LPM模块

7.4 LPM 随机存储器的设置和调用

1.在VerilogHDL和VHDL中例化 2.使用端口和参数定义 3.使用端口和参数定义生成宏功能模块

verilog hdl 题目

Verilog HDL简介及应用1. 概述Verilog HDL作为一种硬件描述语言,在数字电路设计领域中得到了广泛的应用。

本文将从Verilog HDL的定义、特点、基本语法、应用领域等方面进行介绍,以便读者对Verilog HDL有一个清晰的认识。

2. Verilog HDL的定义Verilog HDL即Verilog Hardware Description Language,是一种硬件描述语言,用于对数字电路进行描述、模拟和验证。

它是一种硬件描述语言,类似于C语言,但是它更关注于硬件层面的描述和设计。

3. Verilog HDL的特点(1)泛型性:Verilog HDL支持泛型编程,能够描述各种类型的数字电路,包括组合逻辑和时序逻辑。

(2)并发性:Verilog HDL支持并发描述,在描述数字电路时可以使用并发结构描述各个逻辑单元的交互关系。

(3)模块化:Verilog HDL支持模块化设计,模块之间可以进行层次化的描述和连接,使得复杂的电路可以被分解成多个独立的模块进行设计和验证。

4. Verilog HDL的基本语法(1)模块声明:使用module关键字声明一个模块,包括输入、输出和内部信号的声明。

(2)数据类型:Verilog HDL支持多种数据类型,包括bit、reg、wire、integer等。

(3)运算符:Verilog HDL支持各种运算符,包括赋值运算符、逻辑运算符、位运算符、条件运算符等。

(4)控制结构:Verilog HDL支持if-else、for循环、while循环等控制结构。

(5)并发语句:Verilog HDL使用always关键字和符号来描述并发执行的逻辑。

5. Verilog HDL的应用领域Verilog HDL广泛应用于数字电路的设计、仿真和验证之中,包括但不限于:(1)集成电路(IC)设计:Verilog HDL可用于描述芯片内部的数字电路,进行功能验证和时序分析。

Verilog HDL

白皮书从 LTE 无线通信算法到 FPGA 原型实现:一套完整的 MATLAB 与Simulink 工作流程简介无线通信是智能手机、高可靠性自动驾驶系统和低功耗物联网 (IoT) 设备设计创新的核心。

设计这些系统需要跨多个学科密切合作。

将算法模型部署到 FPGA 硬件可以进行无线测试和验证。

直接从系统级算法和模型自动生成 HDL 代码,无需工程师依赖规范文档或手动构建和编写代码。

本白皮书介绍了将 MATLAB® 算法和 Simulink® 模型直接转换为适用于 FPGA 的 HDL 的工作流程,主题包括:• 使用 MATLAB 和 LTE System Toolbox™ 进行符合 LTE 标准的算法建模• 从基于帧的 MATLAB 算法过渡到数据流的 Simulink 实现• 基于 Fixed-Point Designer™ 和目标硬件特性的定点实现• 通过使用经过验证的知识产权 (IP) 加速设计• 生成 HDL 并在目标硬件上部署,在本例中为 Xilinx® Zynq®我们将通过一个 LTE 小区搜索和主信息块 (MIB) 恢复设计来说明该过程。

MathWorks 创建此设计的初衷是为了满足关键客户需求。

该设计现在已经成为 LTE HDL Toolbox™ 提供的参考应用。

此工作流程中还将使用 LTE System Toolbox 和 HDL Coder™。

在硬件中实现无线通信算法通信工程师可以使用 MATLAB 和 Simulink 以及附加工具箱,在算法级别开发、仿真和优化其应用。

但是,为了将这些算法实现到原型设计或生产部署需要跨多种角色进行协调,这极大地增加了项目的复杂性。

不同的技能和工作环境图 1 显示了在硬件中构建无线通信应用所需的技能。

工程师通常只在这些领域中的一个或两个领域拥有专业知识,因此项目通常涉及跨角色和跨部门协调。

图 1:在硬件上设计无线通信应用原型或部署所需的技能和工作环境。

基于VerilogHDL的IP核参数化设计

基于VerilogHDL的IP核参数化设计

徐晨;袁红林

【期刊名称】《微电子学与计算机》

【年(卷),期】2005(22)12

【摘要】指出了IP核参数化设计的重要性,分析了IP核的参数类型及相互关系。

在分析基于VerilogHDL的IP核参数化设计方法及所面临困难的基础上,提出了一种附加的编译预处理方法并设计了相应的工具软件ECP。

IP核由VerilogHDL和ECP扩展的语句混合编程,经ECP处理后生成VerilogHDL源文件。

应用该方法后,提高了Ver-ilogHDL在描述功能、性能、结构及优化策略等参数化的复杂模型时所需要的灵活性,增强了VerilogHDL的建模能力。

作为一个IP核参数化设计的实例,介绍了C*Core系统中断控制IP的参数化设计过程,给出了FPGA验证的结果。

【总页数】4页(P85-88)

【关键词】IP核;参数化设计;VerilogHDL;编译预处理;中断控制IP

【作者】徐晨;袁红林

【作者单位】南通大学江苏省专用集成电路设计重点实验室

【正文语种】中文

【中图分类】TN402

【相关文献】

1.基于NIOSⅡ IP核的video over ip设计 [J], 宋灿

2.3-DES IP核的VerilogHDL设计 [J], 王甫莉;陈健;郭晋亮

3.PDP信号存储处理IP核的设计与VerilogHDL实现 [J], 邱崧;胡文静;刘锦高;李外云

4.基于VerilogHDL的异步串行通信IP核设计 [J], 李健;吕胜涛

5.C8051微控制器IP软核的参数化设计 [J], 蒋华;袁红林

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

b M n r me eie sg sb s d o rlg y FS a d Pa a t rz d De in a e n Ve i .Th P c r sr aie n e i e nXi n GA o eI o ei e l da d v rf do l x FP z i i

邱 崧 胡文静h , , 刘锦高 李外云 ,

(. 1华东师范大学电子系, 上海 206 ;. 00 22湖南理工学院。 长沙 440 ) 106 摘 要 : 介绍了等离子显示器的基本电路系统及寻址显示分离子场驱动方法, 设计了一种具有伪轮廓消除功能的 P) I P信号 存储处理 I 核, I 作为 P P信号控制系统的核心部分, ) D 它具备通用的外部电路接口, 有较强的可移植性和可复用性 , 稍加改动 便可应用于不同类型和不同参数的 P P显示控制, D 缩短了设计周期。利用 V ro D el H L语言中有限状态机和参数化设计思 ig 想对 I 核进行了描述和设计, I ) 并在 Xl x in 公司的 F G i P A器件上实现了 I P核的功能验证。 关 键词 : 核; 交流等离子显示器I 伪轮廓; ro D I Vel H L 现场可编程门阵列, ig 有限状态机

中图分类号:N 1. 4 T 95 0

文献标识码 : A

文章编号:0 599 (06 0-540 1 0-40 20 )202大屏幕显示器 件, 其优越的性 能已得到业界 的公认 。但 P P显 D 示器及其驱动的核心技术主要 由国外大公 司主宰 ,

维普资讯

第2 卷 9

第2 期

电 子 器 件

C i s or a o l t n D v e h ee Jun l fEe r ei s n co c

v0 . 9 No 2 12 .

20 0 6年 6月

J n 2 0 u .0 6

脚

o D i a PI 咖 f Ps nl Io P g o

I oe n s mp m na o ae el D PC r dI l et i B s o V ro H L a tI e tn d n ig

QI o g ,HUWe-ig , UJn -a LIWa-u US n njn LI igg o , i n y

Ab ta t Th o to l g s se a d ADS Su - eo sd iig meh d o DP a eito u e .Asfc r n sr c : e c n r li y tm n n b f l l rv n t o fP r r d c d i n o ei l t ePDP c n r l n ic i,P h o tol g cr ut DP in lp o e sn P r sd sg e O h v n v ra i uti tra e i sg a r c s i g I Co ei e in d t a eu ie s lcr i n e fc s c a dr d c ef leo t n .Th sI C r ih i r n pa tb ea dr u a l a era i d f dt — n e u et as u l e h i i P o ewh c Sta s ln a l n e s bec n b e dl mo i e of y i l d p od fe e tP O a or d c h e inc ce a tt i r n DP S st e u et ed sg y l.Th a d r e c i t no i P C r r p s d f eh r wa ed s rp i ft sI ei p o o e o h o s

d v c. e ie

Ke r s I r ;ACPDP;f leo tie ywo d :P C e o as u l ;Ve i g HDL;FPGA;fnt tt c i e n rl o iiesa ema hn

EE :2 0 76

P DP信 号存 储 处 理 I P核 的设 计 与 Vei g rl HDL实现 o

( . a t hn om l nvr t , h n h i 00 2 C i ; n nIs tt o c ne n eh o g t h n s 10 6 C i ) 1 E sC iaN r a i s y S a g a 0 6 ・ n 2Hu a t ue fS i c a d T cn l y C a gh 4 4 0 。 h n U ei 2 h a ni e o a a

1 P P屏板及驱动控制 系统结构 D

图1 为简化的 A P P屏板及其显示驱动控制 CD

系统结构, 主要由三个部分组成 。

来自 接口 电路

的 觳

特别是作 为 P P显示器核心构件 的小信号处理驱 D 动芯片目前 由各生产厂家 自行提供 , 规格不统一。 I P核可重用设计 方法是未 来大规模 集成 电路 的主 流设计方法 , 如能将这类芯片以可重用 I P核的形式 实现, 将有利于 P P驱动系统的 S C设计过程 , D O 从 而提高我 国 P P行业 的核 心竞争力 。本文 以当今 D 市场主流的 8 2 8 分辨率寻址 显示 分离驱动式 5 ×4 0 A P P为例 , 了一种信号存储处理 I CD 设计 P核, 来实 现数字视频信号的存储 、 处理和转换