创新中心FPGA开发板技术要求

fpga技术要求

fpga技术要求FPGA技术要求1. 硬件设计能力熟悉FPGA结构与原理熟悉FPGA的内部结构和工作原理,包括查找表(Look-Up Table, LUT)、触发器(Flip-Flop)、时钟分配网络等。

了解FPGA中逻辑门的实现方法和时序控制的原理。

掌握硬件描述语言熟练掌握至少一种硬件描述语言,如VHDL(VHSIC Hardware Description Language)或Verilog。

能够根据需求编写出可综合到FPGA的硬件描述代码,包括设计各种逻辑电路、状态机、时钟域处理等。

信号处理能力具备信号处理的基础知识,能够对各种类型的输入信号进行采样、滤波、时域/频域转换等处理。

能够设计和实现基于FPGA的信号处理算法,例如数字滤波器、快速傅里叶变换等。

2. 软件工具熟悉FPGA开发平台具备对FPGA开发平台的熟悉程度,如Xilinx的Vivado或Altera的Quartus。

能够使用开发平台进行FPGA的开发、综合、仿真和下载。

能力应用软件工具进行仿真与调试具备使用软件工具进行FPGA设计的仿真和调试能力,例如ModelSim等仿真工具,能够准确验证设计的正确性,并对可能存在的问题进行调试和优化。

熟悉高级综合工具熟悉高级综合工具,如Xilinx的Vivado HLS或Altera的HLS工具。

能够通过高级综合工具,将C/C++等高级语言代码转换为FPGA硬件描述代码,提高设计效率和可移植性。

3. 项目经验具备项目管理经验具备项目管理经验,能够在有限的时间和资源下,组织和管理FPGA项目的开发和验证工作。

能够根据项目要求,合理规划开发进度和资源分配,保证项目高质量地完成。

有FPGA设计实践经验具备一定的FPGA设计实践经验,能够独立完成FPGA设计任务。

能够根据需求,完成FPGA硬件设计、仿真验证、性能优化等工作。

参与过复杂FPGA项目参与过复杂FPGA项目的开发,有从0到1完成复杂功能模块的经历。

FPGA开发板使用说明书(二版)

目 录第一章综述 (1)核心板介绍EP1C12核心板资源介绍 (1)EP2C35核心板资源介绍 (2)FPGA开发板介绍FPGA开发板资源介绍 (4)第二章 系统模块功能介绍 (7)EP1C12核心板模块说明EP1C12F324C8芯片说明 (9)NOR FLASH模块说明 (10)SRAM模块说明 (11)FPGA接口I/O说明 (12)EP2C35核心板模块说明EP2C35F484C8芯片说明 (19)NOR FLASH模块说明 (20)SRAM模块说明 (21)S D R A M模块说明 (22)NAND FLASH模块说明 (23)FPGA接口I/O说明 (24)核心板使用注意事项 (29)FPGA开发平台模块说明液晶显示模块 (31)RTC实时时钟模块 (33)USB接口模块 (33)音频CODEC接口模块 (34)EEPROM存储模块 (35)数字温度传感器模块 (36)其它功能模块 (37)FPGA开发平台使用注意事项 (38)第三章 软件的安装 (39)QUARTUSII的安装 (39)QUARTUSII的授权 (46)NIOSII IDE的安装 (51)附表一核心板载资源与FPGAEP1C12I/O接口对照表 (55)附表二核心板载资源与FPGAEP2C35I/O接口对照表 (60)附表三EP1C12/ EP2C35与开发板硬件资源I/O接口对照表 (66)第一章综述FPGA开发平台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。

系统根据用户不同的设计需求来更换其它不同系列的核心板,如: EP1C12、EP2C20、EP3C25等。

所以,不管从性能上而言,还是从系统灵活性上而言,无论您是初学者,还是资深硬件工程师,它都会成为您的好帮手。

FPGA课程设计——要求_题目_安排

FPGA课程设计——要求_题目_安排FPGA课程设计要求1、FPAG课设所选题目要求采用自顶向下的全正向设计方法,并选用Verilog_HDL语言为设计输入工具。

2、要求电路的功能仿真和FPGA后仿真验证全部正确通过,且功能仿真和后仿真建议采用第三方验证工具(Modelsim),综合与布局布线工具为:Quartus II。

3、课程设计的具体评定标准:(1)完成功能和引脚定义,提交《技术规范》;(10分)(2)完成总体方案及详细方案设计,提交《设计方案》;(10分)(3)完成验证方案设计,提交《功能验证方案》;(10分)(4)完成电路设计和功能仿真,提交电路设计源代码,功能仿真激励源代码及功能仿真结果报告;(15分)(5)完成设计电路的FPGA综合及布局布线,提交综合及布局布线报告和引脚分布报告;(10分)(6)采用第三方工具完成后仿真,提交后仿真结果报告;(10分)(7)基于FPGA开发板完成设计电路的功能测试验证,提交硬件测试结果报告;(30分)(8)积极与教师和同学进行技术交流沟通,撰写课设的心得体会;(5分)4、题目要求独立完成,设计和报告如有雷同,将一个成绩平均分配雷同的同学。

说明1:课程设计时间段内任意时间点名未到(吃饭时间12:00 ~ 12:40除外)、迟到扣3分/次,玩游戏扣20分/次。

说明2:迟到、点名未到6次及6次以上者课程设计成绩直接记:不及格。

FPGA课程设计题目序号题目说明1简易数据流检测器设计及FPGA功能验证设计一个有限状态机检测5位二进制序列“10010”,要求数据采用串行输入,检测结果用一个高脉冲来指示。

用FPGA开发板上的按键作为数据流输入,led或数码管作为输出指示。

2可逆加减计数器及FPGA功能验证可预置16位可逆加减计数器。

要求计数器有16位计数输出同时有进位和借位输出,预置输入采用同步方式。

用FPGA开发板上的按键作为加减计数控制输入,数码管(或led)作为计数值输出。

fpga使用注意!!

------------------------------------------------------------------------------------ 本板子由哈尔滨工程大学青年创业电子设计小组(简称青创电子设计小组)开发,对板子及其相关的实例、教程具有完全的自主设计权。

请勿将例程、电路图、教程用作其它商用,否则将追究其法律责任!!!。

若要在网络上以学习的目的发布相关内容,请注明出处!

-----------------------------------------------------------------------------------

注意:为了方便查找,我们在每个文件夹的名字中都带了中文注释,但在运行这些文件夹中的工程时,最好把文件夹名字里的这些中文注释去掉,防止产生不必要的错误,耽误大家的学习。

关于如何利用好这些实例,以帮助你更快速的学好VHDL的一点建议:

(1)将配套实例先在开发板上运行一遍,观察实验结果;(2)仔细分析实验代码,经自己最大的努力看懂它们:

(3)自己将实验代码重新写一遍(一个字一个字的敲入计算机,请一定不要复制我们提供的现成代码),然后在Quartus下进行调试;

(4)看看是否可以用另外的方法实现实验所要达到的效果,假如可以,可自己编写代码进行调试。

经过以上四步的练习,相信初学者可以很好的掌握

VHDL的编程,熟练的操作Quartus软件,对CPLD 开发流程也有了比较深刻的体会。

我们提供了视频教程,喜欢视频教学的读者可结合视频学习。

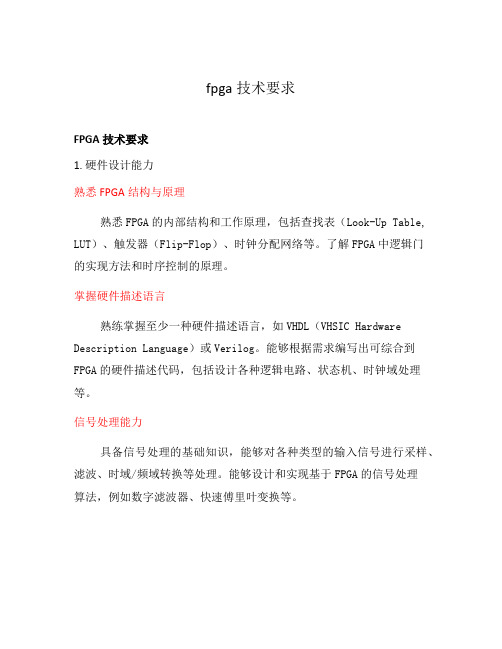

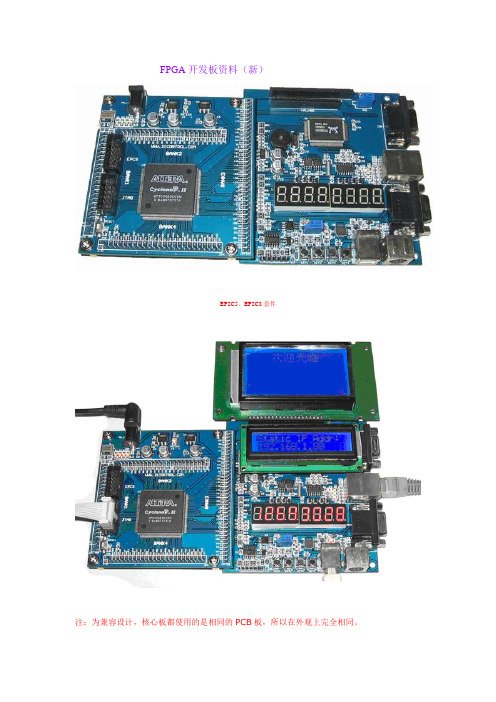

FPGA开发板资料

FPGA开发板资料(新)EP2C5、EP2C8套件注:为兼容设计,核心板都使用的是相同的PCB板,所以在外观上完全相同。

我们秉承一贯以来实用的理念,处处用心为用户着想,重新精心打造,每个功能都精心设计实用的例子程序,并重新编写详细的教程,无论用于学习或是研制产品原型,都非常具有实际意义。

另外我们设计了包含Cyclone、CycloneII 等多款核心板供用户选择,不断开发和供应各种实用的功能扩展板,扩展性能卓越。

无论学习、开发,该套件都是您合适的首选。

质量保证:(1)我们竭诚为顾客提供超值的产品。

任何产品邮发之前都经过严格的检验和测试,保证每个功能都工作良好。

如果有质量问题,7天内免费更换,一年保修,对于人为造成的损坏(如使用不当烧毁芯片等),我们仍给以免费维修,但需以成本价收取芯片费用。

(2)于外地客户,我们采用信誉良好的航空快递公司进行配送,保证产品快速完好地送到客户手上,如果在配送过程中有损坏,我们负责给予更换。

(3)我们严格控制产品出厂的质量,做到每块板卡邮出之前经过再三测试,如遇特殊情况,请及时联系我们,我们会给予精诚的解决方案。

我们视质量和服务是我们获得顾客长期信赖和合作的根本,更是我们赖之成长的源泉。

技术支持:采用电话、BBS、QQ、QQ客户群等方式。

套件包括:一、FPGA核心板:多种核心板供选择,所采用的FPGA分别有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心:EP2C8Q208C8、EP2C5Q208C8、EP2C20Q208C8;CycloneIII核心:EP3C16Q240C8、EP3C25Q240C8;(3)SDRAM:8MByte;(4)Flash:8MByte;(5)EPCS1、EPCS4、EPCS16配置芯片:EP1C6和EP2C5核心板配备EPCS1;EP1C12和EP2C8以及EP2C20核心板配备EPCS4;EP3C16和EP3C25配备EPCS16(即容量为16Mb);(6)提供配置模式:JTAG和AS;(7)两个或一个50Mhz有源时钟;(8)所有IO、Avalon总线、配置管脚等都通过4排插针引出,用户可以充分自由发挥,扩展更灵活;(9)4个LED;(10)一个复位按键。

FPGA 开发板用户手册

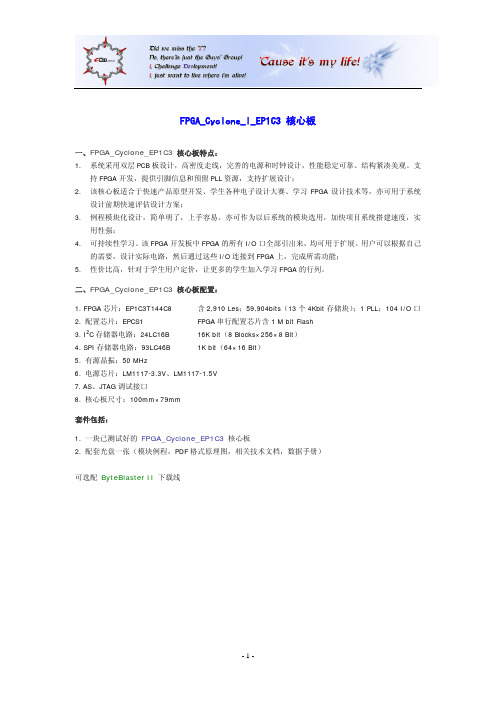

FPGA_Cyclone_I_EP1C3 核心板一、FPGA_Cyclone_EP1C3 核心板特点:1.系统采用双层PCB板设计,高密度走线,完善的电源和时钟设计,性能稳定可靠、结构紧凑美观。

支持FPGA开发,提供引脚信息和预留PLL资源,支持扩展设计;2.该核心板适合于快速产品原型开发、学生各种电子设计大赛、学习FPGA设计技术等,亦可用于系统设计前期快速评估设计方案;3.例程模块化设计,简单明了,上手容易。

亦可作为以后系统的模块选用,加快项目系统搭建速度,实用性强;4.可持续性学习。

该FPGA开发板中FPGA的所有I/O口全部引出来,均可用于扩展。

用户可以根据自己的需要,设计实际电路,然后通过这些I/O连接到FPGA上,完成所需功能;5.性价比高,针对于学生用户定价,让更多的学生加入学习FPGA的行列。

二、FPGA_Cyclone_EP1C3 核心板配置:1. FPGA芯片:EP1C3T144C8 含2,910 Les;59,904bits(13个4Kbit存储块);1 PLL;104 I/O口2. 配置芯片:EPCS1 FPGA串行配置芯片含1 M bit Flash3. I2C存储器电路:24LC16B 16K bit(8 Blocks×256×8 Bit)4. SPI存储器电路:93LC46B 1K bit(64×16 Bit)5. 有源晶振:50 MHz6. 电源芯片:LM1117-3.3V、LM1117-1.5V7. AS、JTAG调试接口8. 核心板尺寸:100mm×79mm套件包括:1. 一块已测试好的FPGA_Cyclone_EP1C3 核心板2. 配套光盘一张(模块例程,PDF格式原理图,相关技术文档,数据手册)可选配 ByteBlaster II 下载线Periphery_For_FPGA外设板Periphery_For_FPGA外设板特点:1. 该外设板是基于FPGA的硬件描述语言和软内核嵌入式系统的SOPC开发平台。

fpga技术要求

fpga技术要求

(原创版)

目录

1.FPGA 技术的定义和基本原理

2.FPGA 技术的主要要求

3.FPGA 技术的应用领域

正文

FPGA(现场可编程门阵列)技术是一种集成电路设计技术,它的基本原理是通过将多个逻辑门和其他电子元件组合在一起,形成一个可重新配置硬件架构的数字电路。

FPGA 技术具有灵活性高、开发速度快、可重构性强等优点,因此在现代电子技术中有着广泛的应用。

FPGA 技术的主要要求包括以下几个方面:

首先,FPGA 技术要求具有较高的灵活性。

FPGA 器件可以根据需要实时地改变其硬件结构,从而实现不同的逻辑功能。

这种灵活性使得 FPGA 技术非常适用于需要频繁更改设计方案的电子系统,如人工智能、图像处理等领域。

其次,FPGA 技术要求具有较快的开发速度。

FPGA 设计可以通过编程实现,而不需要进行复杂的硬件设计。

这使得 FPGA 技术的开发速度相比传统的硬件设计方法要快得多,可以大大缩短产品的研发周期。

最后,FPGA 技术要求具有较强的可重构性。

FPGA 器件可以根据需要实时地改变其硬件结构,从而实现不同的逻辑功能。

这种可重构性使得FPGA 技术非常适用于需要频繁更改设计方案的电子系统。

FPGA 技术的应用领域非常广泛,包括但不限于人工智能、图像处理、通信、汽车电子等领域。

例如,FPGA 技术可以用于实现深度学习算法,实现高效的图像识别和处理;FPGA 技术也可以用于设计高速的通信芯片,

实现高速、稳定的数据传输。

FPGA实验核心开发板简介

一、主要器件及特性

1、FPGA:EP1C12Q240C8,配置芯片EP1C12

2、一片256K X 16Bit的异步SRAM 3、一片4M X 32Bit d SDRAM支持166M byte 4、一片2M X 8Bit或者1M X 16Bit的Flash读写速度为 90ns 5、9针RS-232串口 6、PS/2鼠标,键盘接口 7、USB2.0高速数据接口:采用Cypress公司CY7C68013 芯片实现了USB接口的扩展 8、LCD1602带背光字符型液晶模块

开发板说明

一、开发板电源

1、USB供电:J8跳到USB_VCC 2、外部电源供电: 外部1A/5V直流开关电源,J8 跳到EX_VCC

3、EDA底板供电:将开关电源插到EDA底板上, J8跳到EX_VCC

二、LCD接口

J11插入LCD1602

三、配置端口

板上两个配置端口:AS和JTAG

四、与EDA底板进行连接时的注意事项

七、主板上外设LED

Байду номын сангаас

八、主板上系统时钟

九、主板上4 x 4矩阵键盘和按键

十、主板上蜂鸣器

十一、主板上温度测试

主要电路及管脚

二、LED和按键

1、4个发光二极管

2、4个按键

3、两位动态扫描数码管

一、主板PS2

二、主板RS232

三、主板VGA接口

四、主板步进电机接口(J11短接5V)

五、主板液晶接口(J27) 标准字符液晶LCD1602,汉字图像液晶LCD12864

六、主板上外设数码管

FPGA开发板硬件设计方案070516

FPGA 开发板硬件设计方案引言在FPGA 选型报告中,我们阐明了产品用途和设计目标,列出了具体的规格需求并最终选定了Altera stratixII EP2S180F-1020作为FPGA 器件,本文将详细说明FPGA 整体设计方案。

一、 器件布局1、 器件总体布局图协同集团北京研发中心文档基本信息 文档级别 总页数 13 文档 名称FPGA 开发板硬件设计方案编制人 宋波 所在部门 硬件开发 审核人曹占生编制日期2007-6-8高速A/D 高速A/D 高速A/D 高速D/A U S B 2.0RS-232 扩展口24P i n扩展口24PinPOWER SUPPL Y: 16V大电流开关稳压器: 5V 、3.3V 、1.8V 、1.2V LDO: 2.8V DC/DC: 12V DC/DC: -5V高速A/D 高速D/A 高速D/A 高速D/A RJ45以太网 键盘音频A/D 音频A/D 音频D/A 音频D/ACMOS 摄像头串口LCDSD Card4X PCI-Express 接口D D R S D R A M 接口并口LCD FPGA EP2S180SRAMFLASHDDR SDRAMJTAG MICTOR 程控逻辑芯片Crystal U S B 2.0RS-232高密connector高密connector高密c o n n e c t o r高密c o n n e c t o rSD CardSharp LCD 扩展口24P i n2、器件总体布局考虑因素➢实用性:将各种应用接口布置在板边方便使用,包括高速A/D D/A的SMA端子、音频A/D D/A的RCA端子、摄像头Connector、LCD Connector、键盘接口、RJ-45接口、RS-232接口、USB2.0 OTG接口、CF Card(可选)、SD Card、Power supply端子、扩展口;PCI-e和DDR存储器接口可放置于板内。

1.2 FPGA的设计方法与要求

利用HDL语言,采用“ Top→down”(自顶向下)设计方法 具有以下优点: ①在“ Top→down”(自顶向下)的设计过程中,每一步 都可以进行仿真,可以在系统设计过程发现设计存在的问题, 可大大缩短系统的设计周期,降低费用,使电路设计更趋合 理,其体积和功耗也可减小。 ②采用HDL语言,就可免除编写逻辑表达式或真值表的 过程,使设计难度大幅度下降,,从而可以缩短设计周期。 ③采用HDL语言设计系统硬件电路时,主要的设计文件 是用HDL语言编写的源程序,也可以将HDL语言编写的源程 序转换成电原理图形式输出,降低了硬件电路设计难度,。 ④用HDL语言的源程序作为归档文件资料量小,便于保 存,可继承性好。

EDA(Electronics Design Automation)即电子设 计自动化。现在数字系统设计依靠手工已经无法 满足设计要求,设计工作需要在计算机上采用EDA 技术完成。EDA技术以计算机硬件和系统软件为基 本工作平台,采用EDA通用支撑软件和应用软件包, 在计算机上帮助电子设计工程师完成电路的功能 设计、逻辑设计、性能分析、时序测试直至 PCB (印刷电路板)的自动设计等。在EDA软件的支持 下,设计者完成对系统功能的进行描述,由计算 机软件进行处理得到设计结果。利用EDA设计工具, 设计者可以预知设计结果,减少设计的盲目性, 极大地提高设计的效率。

利用HDL语言,采用“ Top→down”(自顶向下) 设计方法的设计系统硬件电路,一般分为三个步骤, 如图1.2.2所示。

图1.2.2 “ Top→down”(自顶向下)设计系统硬件的过程

①行为描述:

对系统进行行为描述的目的是在系统设 计的初始阶段,通过对系统行为描述的 仿真来发现系统设计中存在的问题。在 行为描述阶段,考虑的是系统的结构及 其工作过程是否能达到系统设计规格书 的要求,并不考虑其实际的操作和算法 用什么方法来实现。行为描述是对整个 系统的数学模型的描述,其设计与器件 工艺无关。

fpga开发板使用手册

FPGA开发板使用手册一、硬件概述FPGA开发板是一种基于可编程逻辑器件(FPGA)的嵌入式系统开发板,它为电子工程师提供了一个高度灵活和可定制的平台,可用于开发各种数字系统,如通信、控制、数据处理等。

本手册旨在帮助用户了解和使用这款FPGA开发板,充分发挥其性能和功能。

二、开发板规格本开发板规格如下:1. 尺寸:90mm x 60mm x 1.6mm。

2. FPGA型号:Xilinx XC7020。

3. 内存容量:128MB DDR3。

4. 存储器:8GB eMMC。

5. 接口类型:USB 2.0,以太网 10/100Mbps,RS232等。

6. 电源电压:5V。

7. 重量:约15克。

三、硬件连接本开发板可通过以下方式与外围设备连接:1. USB接口:用于连接电脑进行编程和调试。

2. 以太网接口:用于连接网络。

3. RS232接口:用于连接其他串口设备。

4. GPIO接口:用于连接其他数字设备。

5. I2C接口:用于连接I2C总线设备。

6. SPI接口:用于连接SPI总线设备。

7. HDMI接口:用于显示输出。

8. SRAM接口:用于高速数据存储。

9. UART接口:用于串口通信。

四、FPGA设计工具安装与使用FPGA设计工具是用于编写和调试FPGA逻辑代码的软件环境。

本开发板支持的FPGA设计工具有Xilinx Vivado和Intel Quartus等。

用户需要根据所选工具,下载并安装相应的软件,然后按照软件说明进行安装和配置。

在安装过程中,请注意选择与本开发板兼容的版本和配置。

安装完成后,用户可以使用FPGA设计工具编写逻辑代码,并通过开发板的接口将代码下载到FPGA中运行。

五、FPGA设计基本原则在FPGA设计中,需要遵循以下基本原则:1. 模块化设计:将复杂问题分解为多个简单的子问题,逐个解决,便于调试和维护。

2. 尽量使用硬件加速器:利用FPGA的并行处理能力,提高系统性能。

芯创电子手把手教你学习FPGA_焊接技术篇

20121.前言 (4)2.焊接技术 (4)2.1.焊接的基础知识 (4)2.3.焊接的工具 (5)3.手工焊接工艺 (5)3.1.元器件引线加工成型 (5)3.2.元器件的插装 (6)3.3.手工烙铁焊接技术 (6)3.4.五步焊接法 (7)3.5.焊接质量的检查 (7)4.贴片元件的手工焊接技巧 (8)4.1.贴片阻容元件的焊接 (8)4.2.芯片的焊接 (8)5.后焊技术知识 (10)5.1.如何清理松香 (10)5.2.PCB的摆放 (11)5.3.电烙铁的日常维护和保养 (11)6.焊接电路板的注意事项 (11)7.电路板对应丝印层的识别 (12)8.DIY单板的焊接注意事项 (13)1.前言随着电子元器件的封装更新换代加快,电子发展已朝向小型化、微型化发展,手工焊接难度也随之增加,在焊接当中稍有不慎就会损伤元器件,或引起焊接不良,所以我们必须对焊接原理,焊接过程,焊接方法,焊接质量的评定,及电子基础有一定的了解.2.焊接技术2.1.焊接的基础知识一、锡焊锡焊是焊接的一种,它是将焊件和熔点比焊件低的焊料共同加热到锡焊温度,在焊件不熔化的情况下,焊料熔化并浸润焊接面,依靠二者原子的扩散形成焊件的连接。

其主要特征有以下三点:⑴焊料熔点低于焊件;⑵焊接时将焊料与焊件共同加热到锡焊温度,焊料熔化而焊件不熔化;⑶焊接的形成依靠熔化状态的焊料浸润焊接面,由毛细作用使焊料进入焊件的间隙,形成一个合金层,从而实现焊件的结合二、锡焊必须具备的条件⑴焊件必须具有良好的可焊性;⑵焊件表面必须保持清洁;⑶要使用合适的助焊剂;⑷焊件要加热到适当的温度;⑸合适的焊接时间;三、焊点合格的标准1、焊点有足够的机械强度:一般可采用把被焊元器件的引线端子打弯后再焊接的方法。

2、焊接可靠,保证导电性能。

3、焊点表面整齐、美观:焊点的外观应光滑、清洁、均匀、对称、整齐、美观、充满整个焊盘并与焊盘大小比例合适。

满足上述三个条件的焊点,才算是合格的焊点。

fpga技术要求

fpga技术要求摘要:一、FPGA 技术简介1.FPGA 的定义与作用2.FPGA 的原理与结构二、FPGA 技术要求1.硬件设计要求a.逻辑门数量b.布线资源c.存储器容量d.封装形式2.软件设计要求a.编程语言与工具b.设计流程与方法c.验证与仿真3.性能要求a.工作频率b.功耗c.可靠性4.开发环境与工具a.开发软件b.调试与验证工具c.硬件平台三、FPGA 技术的应用领域1.通信领域2.数据中心3.人工智能4.工业控制5.航空航天6.其他领域正文:FPGA 技术,即现场可编程门阵列(Field-Programmable Gate Array),是一种可以由用户编程定义硬件架构的集成电路。

它具有灵活性高、可重构性强、开发周期短等优点,广泛应用于各个领域。

本文将从FPGA 技术简介、技术要求以及应用领域三个方面进行阐述。

一、FPGA 技术简介FPGA 是一种集成电路,其主要功能是实现数字逻辑电路。

与传统的ASIC(专用集成电路)相比,FPGA 最大的优势在于其灵活性。

用户可以根据需要对FPGA 进行编程,定义其硬件架构,从而实现特定功能。

FPGA 的核心部分是由可编程逻辑单元(PLU)、输入输出模块(I/O)以及布线资源组成的。

通过将这些单元进行组合连接,用户可以实现各种复杂的数字逻辑电路。

二、FPGA 技术要求1.硬件设计要求硬件设计要求包括逻辑门数量、布线资源、存储器容量以及封装形式等方面。

逻辑门数量决定了FPGA 的计算能力,用户需要根据实际需求选择合适的逻辑门数量。

布线资源是连接各个逻辑单元的关键,影响着信号传输的延迟与功耗。

存储器容量则决定了FPGA 可以存储的数据量,对于一些需要大量存储数据的应用具有重要意义。

封装形式则影响到FPGA 与其他器件的连接以及信号传输。

2.软件设计要求软件设计要求包括编程语言与工具、设计流程与方法以及验证与仿真等方面。

FPGA 的编程语言主要有VHDL、Verilog 等,设计工具包括Xilinx 的ISE、Altera 的Quartus 等。

FPGA开发板硬件设计方案070516

FPGA开发板硬件设计方案070516FPGA(Field Programmable Gate Array)是一种可重新配置的集成电路芯片,可用于实现各种数字逻辑功能。

FPGA开发板是用于学习、开发和验证FPGA设计的硬件平台。

本文将介绍一个FPGA开发板的硬件设计方案,包括主要组成部分和详细设计考虑。

1.FPGA选型:首先需要选择适合项目需求的FPGA芯片。

选择FPGA时需要考虑项目的计算需求、I/O需求、资源使用和成本等因素。

常用的FPGA厂商有Xilinx和Altera,选型时可以根据具体项目需求选择适合的系列和型号。

2.主要组成部分:一个基本的FPGA开发板通常包括以下主要组成部分:-FPGA芯片:用于实现项目的数字逻辑功能。

-存储器:用于存储程序和数据。

通常包括片上存储器和外部存储器,如DDR3/DDR4SDRAM等。

-时钟源:提供时钟信号以驱动FPGA芯片。

-外部接口:包括GPIO、UART、SPI、I2C、以太网口、HDMI等,用于与外部设备通信。

-电源模块:提供稳定的电源供电,包括可切换的电源电压和电流限制功能。

-JTAG接口:用于将开发板与开发工具连接,进行烧录和调试操作。

-显示屏:用于在开发板上显示信息。

3.详细设计考虑:在设计FPGA开发板时,还需要考虑以下方面的详细设计:-时钟设计:需要设计合适的时钟源,提供稳定的时钟信号。

可以选择使用晶振或者外部时钟源,同时需要考虑时钟的分频、倍频和时钟分配等。

-电源设计:需要设计稳定的电源供应模块,包括电源电压和电流的限制,以及电源滤波和短路保护等。

-外部接口设计:根据项目需求选择合适的外部接口,并进行相应的接口电路设计和信号匹配。

-存储器设计:根据计算需求选择适当的存储器类型,并进行存储器接口电路设计和时序优化。

-PCB布局设计:需要进行合理的PCB布局设计,以保证信号完整性和电磁兼容性。

可以根据芯片数据手册和设计指南来进行布局。

-仿真和验证:设计完成后需要进行仿真和验证,确保FPGA开发板按照设计要求正常工作。

fpga技术要求

fpga技术要求

摘要:

1.FPGA 技术的概念

2.FPGA 技术的要求

3.FPGA 技术的应用领域

正文:

FPGA 技术,即现场可编程门阵列技术,是一种集成电路设计技术,具有高度灵活性和可重构性。

FPGA 器件可以在芯片级进行硬件编程,根据需要实现特定的功能。

这种技术在电子设计领域有着广泛的应用,但要掌握它,需要了解其技术要求。

首先,FPGA 技术的一个重要要求是熟悉硬件描述语言(HDL)。

硬件描述语言是一种用于描述数字电路和模拟电路的文本语言。

FPGA 设计者需要使用HDL 编写代码,定义电路的逻辑功能。

常用的HDL 有Verilog 和VHDL。

掌握这些语言,是进行FPGA 设计的基本前提。

其次,FPGA 技术要求具备电路设计和分析能力。

设计者需要理解数字电路的原理,能够设计出符合逻辑功能的电路。

同时,还需要掌握电路分析的方法,对设计的电路进行功能验证和时序分析。

再次,FPGA 技术要求了解FPGA 器件的特性。

FPGA 器件有不同的类型和规格,设计者需要根据需求选择合适的器件。

此外,还需要了解器件的引脚分配、时钟管理、电源设计等方面的知识。

最后,FPGA 技术要求具备较强的问题解决能力。

在设计过程中,可能会

遇到各种问题,如逻辑错误、时序约束等。

设计者需要具备分析问题和解决问题的能力,以确保设计顺利进行。

FPGA 技术在多个领域有广泛的应用,如通信、计算机、汽车电子等。

掌握FPGA 技术,可以为我国的电子信息产业发展做出贡献。

FPGA教学套件技术要求

• Digilent USB-JTAG端口,支持FPGA编程和通信

• USB-UART桥接

• 12位VGA输出

• USB HID主机的鼠标,键盘和记忆棒

• 24个拨码开关

• 24个用户LED

• 5个用户按键

• 3组4位7段显示器

• 4个Pmod连接器(扩展4-7组外设)

• 3个标准的12引脚Pmod

• 1个两用XADC信号/标准的Pmod

• I2C实验单元(EEPROM)

• 3-8译码电路扩展

•兼容各种PMOD模块

2套

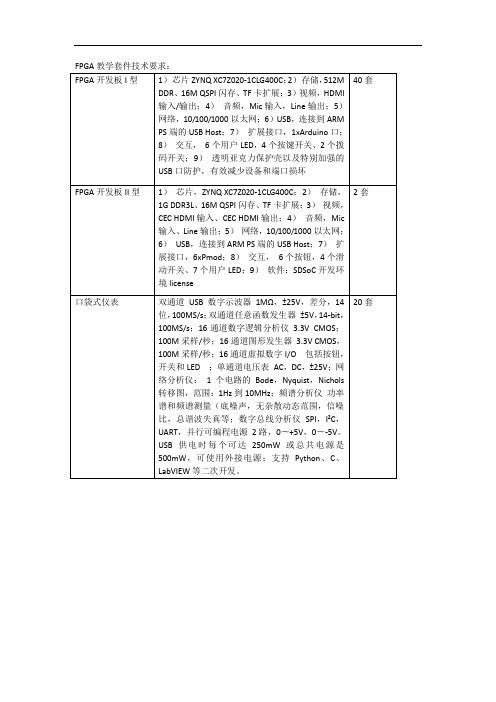

FPGA教学套件技术要求:

FPGA开发板I型

1)芯片ZYNQ XC7Z020-1CLG400C;2)存储,512M DDR、16M QSPI闪存、TF卡扩展;3)视频,HDMI输入/输出;4)音频,Mic输入,Line输出;5)网络,10/100/1000以太网;6)USB,连接到ARM PS端的USB Host;7)扩展接口,1xArduino口;8)交互,6个用户LED,4个按键开关、2个拨码开关;9)透明亚克力保护壳以及特别加强的USB口防护,有效减少设备和端口损坏

2套

口袋式仪表

双通道USB数字示波器1MΩ,±25V,差分,14位,100MS/s;双通道任意函数发生器±5V,14-bit,100MS/s;16通道数字逻辑分析仪3.3V CMOS;100M采样/秒;16通道图形发生器3.3V CMOS,100M采样/秒;16通道虚拟数字I/O包括按钮,开关和LED;单通道电压表AC,DC,±25V;网络分析仪:1个电路的Bode,Nyquist,Nichols转移图,范围:1Hz到10MHz;频谱分析仪功率谱和频谱测量(底噪声,无杂散动态范Байду номын сангаас,信噪比,总谐波失真等;数字总线分析仪SPI,I²C,UART,并行可编程电源2路,0〜+5V,0〜-5V。USB供电时每个可达250mW或总共电源是500mW,可使用外接电源;支持Python、C、LabVIEW等二次开发。

FPGA综合实验开发板实用指南

FPGA综合实验开发板实用指南目录一、开发板概述 (1)1.1开发板结构框图 (1)1.2开发板实物照片 (1)1.3 JTAG接口信号分配图 (2)1.4 FPGA配置模式 (2)1.5 FPGA芯片的片外时钟源 (4)1.6 实验板的测试用引脚 (4)1.7 实验板的电源开关 (4)1.8 实验板的标准配件 (4)二、开发板主要资源 (5)2.1矩阵键盘 (5)2.2独立按键 (5)2.3 LED数码管 (6)2.4 发光LED阵列 (6)2.5 串口 (7)2.6 片外SRAM (7)2.7 蜂鸣器 (7)2.8 耳机插孔 (7)2.9 USB声卡 (8)2.10 JP4引脚 (8)2.11排针引脚 (8)2.12 Pdone引脚 (8)附录一:FPGA管脚分配表 (9)附录二、FPGA综合实验开发板实物照片 (11)电子科技大学VLSI设计中心2010年5月12日一、开发板概述 1.1开发板结构框图图1. 综合实验开发板结构框图1.2开发板实物照片5V 直流电源接口图2. 综合实验开发板实物照片FPGA 芯片型号:Xilinx 公司Spartan-3系列xc3s200 PQ208-4c PROM 芯片型号:xcf02s应用开发工具:Xilinx 公司的ISE (推荐7.1i 及以上版本)电源开关耳机插孔USB 接口片外 SRAM 串口JTAG 接口 独立按键 矩阵 键盘LED 数码管发光LED 阵列 用户自定义 FPGA 引脚 FPGA芯片 FPGA 配置模式 选择开关 蜂鸣器VDD 5V 3.3VGND1.3 JTAG 接口信号分配图图3. 实验板的JTAG 下载接口信号分配图1.4 FPGA 配置模式Spartan-3的配置模式如下表所示。

表中M2、M1、M0为模式选择的配置管脚。

配置管脚的PCB 原理图及PCB 实物图分别如图4所示。

图4中右边PCB 实物图拨码开关S23,当拨码开关拨至下方(OFF )时为‘1’,拨码开关拨至上方(ON )时为‘0’。

FPGA开发板 使用说明书

目录第一章 综述 (1)其次章 系统模块 (1)第三章 软件的介绍 (10)第四章 USB 电缆的安装与运用 (27)第一章 综述THSOPC-3型FPGA开发板是依据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性试验开发板,除了满意高校专、本科生和探讨生的SOPC教学试验开发之外,也是电子设计和电子项目开发的志向工具。

一、好用范围:●自主创新应用开发;●单片机与FPGA联合开发;●IC设计硬件仿真;●科研项目硬件验证与开发;●高速高档自主学问产权电子产品开发;●毕业设计平台;●探讨生课题开发;●电子设计竞赛培训;●现代DSP开发应用;●针对各类CPU IP核的片上系统开发;●DSP Biulder系统设计。

二、硬件配置:THSOPC-3型FPGA开发板基于Altera Cyclone II 器件的嵌入式系统开发供应了一个很好的硬件平台,它可以为开发人员供应以下资源:●支持+5V 电源适配器干脆输入或者USB接口供电,5V、3.3V、1.2V混合电压源;●FPGACycloneII FPGA EP2C8,40万门,2个锁相环;●isp单片机AT89S8253。

isp单片机AT89S8253及开发编程工具,MCS51兼容,12KB isp可编程Flash ROM,2KB ispEEPROM,都是10万次烧写周期;2.7-5.5V工作电压;0-24MHz工作时钟;可编程看门狗;增加型SPI串口,9个中断源等。

此单片机可与FPGA联合开发,特别符合实现当今电子设计竞赛项目的功能与指标实现;●EPM3032 CPLD;● 4 Mbits 的EPCS4 配置芯片;●512KB高速SRAM;●20MHz 高精度时钟源(可倍频到300MHz);● 4 个用户自定义按键;●8 个用户自定义开关;●8 个用户自定义LED;● 2 个七段码LED;●标准AS 编程接口和JTAG调试接口;●两个标准2.54mm扩展接口,供用户自由扩展;●RS-232 DB9串行接口;●PS/2键盘接口;●VGA 接口;●4X4键盘;●液晶显示屏20字X4行;●USB-Blaster 编程器,可对FPGA 通过JTAG 口编程、调试、测试;单片机编程ByterBlasreMV 编程器;●光盘:配套子程序库、资料、编程软件、试验指导书。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

创新中心FPGA开发板技术要求

通信与信息工程学院创新中心因大学生创新训练及实践教学需要,拟采购FPGA口袋实验平台32套、电子系统设计FPGA开发板7套、基于ZYNQ的开源量测FPGA开发板4套,要求该批设备为同一生产厂家产品,具体技术要求如下:

一、FPGA口袋实验平台32套

1.主芯片:Xilinx Artix FPGA,逻辑单元不低于33,280、Slices不低于5,200、分布式RAM不低于

400Kb、DSP单元不低于90个、BlockRAM不低于1,800Kb;

2.板上时钟不低于100MHz;

3.板卡配置方式:支持USB-JTAG编程接口和SPI闪存配置方式;

4.板上需要有不少于2Mbit的SRAM;

5.需要有SPI闪存;

6.需要提供不少于16个LED、不少于8个的拨码开关、不少于8个DIP开关、不少于5个按键;

7.提供通用扩展IO不少于32pin;

8.板上7段数码管不少于8个;

9.板上需要提供VGA视频输出接口与Audio音频接口;

10.提供用于系统调试的USB-UART接口;

11.板卡需要具有板载蓝牙模块;

12.板卡需要具有板载DAC模块;

13.板卡需要具有可调节的电位器,为XADC提供模拟输入;

14.板卡需要具有XADC;

15.要求提供Xilinx Vivado完全正式版开发工具以及license;

16.提供Xilinx Vivado相关培训资料;

17.提供Xilinx Vivado开发流程培训;

18.提供板卡开发流程上手视频;

19.提供不少于12个参考实验案例,包括蓝牙远程控制实验,嵌入式Microblaze实验。

二、电子系统设计FPGA开发板7套

1.主芯片:Xilinx Artix FPGA,逻辑单元不低于33,280、Slices不低于5,200、分布式RAM不低于

400Kb、DSP单元不低于90个、BlockRAM不低于1,800Kb;

2.板上时钟不低于100MHz;

3.板卡配置方式:支持JTAG编程接口和SPI闪存配置方式;

4.板上需要有不少于8Mbit的SRAM;

5.需要具有板载SMA接口、80MSPS采样率、10bit分辨率ADC;

6.需要具有板载SMA接口、165MSPS采样率、10bit分辨率DAC;

7.需要具有独立时钟/FPGA输出/外部SMA输入可选的ADC时钟;

8.需要具有板FPGA提供DAC时钟;

9.需要提供不少于4个LED、不少于4个的拨码开关、不少于2个按键;

10.需要提供不少于20个GPIO;

11.需要具有底板连接器支持5V单电源供电;

12.需要支持USB供电;

13.需要具有128-64液晶;

14.需要具有4×4小键盘;

15.需要具有RS-232接口;

16.需要具有VGA接口;

17.需要具有PWM信号接口;

18.需要具有高速PMOD接口;

19.需要具有可插拔的TM4C1294XL Launchpad。

三、基于ZYNQ的开源量测FPGA开发板4套

1.要求主控芯片使用ZYNQ-7000系列芯片,集成两颗ARM Cortex-A9硬核,提供

2.8万FPGA逻辑

单元、2Mb片上block RAM以及80个DSP计算单元;

2.板上需要提供4个12-bit、100k/s采样的模拟输入;

3.板上需要提供4个12-bit、100k/s采样的模拟输出;

4.需要具有板载125MSPS采样率、14bit分辨率、双通道ADC,带宽50MHz;

5.需要具有板载125MSPS采样率、14bit分辨率、双通道DAC,带宽50MHz;

6.板上需要提供4Gb DDR3内存以及MicroSD卡;

7.板上需要提供千兆以太网连接器、USB2.0接口、USB-UART接口;

8.板上需要提供至少16个扩展IO;

9.需要具有提供扩展子板用于连接外部功能模块,并支持IIC、SPI等总线接口;

10.需要支持网络远程访问,并且支持Python、Matlab、Labview、Scilab远程控制。