有关C6000DSP的Cache的操作

cache的工作原理

cache的工作原理

缓存是一种用于提高计算机系统性能的技术,其工作原理是将经常被访问的数据存储在一个更快速但容量较小的存储器中,以此提供更快的数据访问速度。

具体来说,计算机的存储体系可以分为多级,通常包括主存储器(RAM)、辅助存储器(硬盘、固态硬盘)以及处理器内

部的高速缓存。

在这个层次结构中,缓存位于处理器和主存之间。

当处理器需要访问某个数据时,首先会检查高速缓存中是否存在该数据。

如果数据在高速缓存中被命中(即存在),则处理器可以直接从缓存中获取,从而大大缩短了访问时间。

如果数据不在缓存中,则称为缓存未命中。

当发生缓存未命中时,处理器会通过一种称为缓存替换策略的算法从主存中将相应的数据加载到缓存中。

常用的替换策略有最近最少使用(LRU)和先进先出(FIFO)等。

缓存替换策

略的目标是尽可能地提高缓存的命中率,以减少对主存的访问。

此外,缓存还采用了一种称为缓存一致性协议的机制来保持数据的一致性。

由于多核处理器的普及,每个核心都可能有自己的缓存,因此需要确保各级缓存之间的数据一致,避免出现存储器访问的时序问题。

总的来说,缓存通过存储经常访问的数据并提供高速访问,可以大大加快计算机系统的运行速度。

但缓存的容量和缓存替换

策略选择等也是需要权衡的问题,因为过小的缓存容量或选择不当的替换策略可能导致频繁的缓存未命中,反而降低系统性能。

C6000系列DSP Flash二次加载技术研究

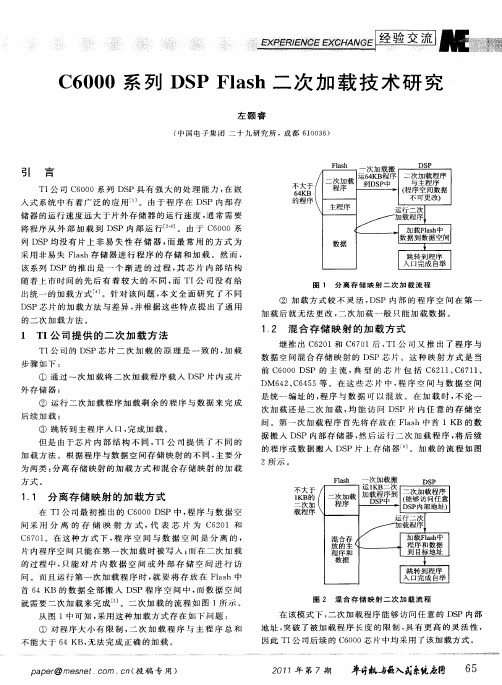

次 加 载 还 是 二 次 加 载 , 能 访 问 DS 均 P片 内 任 意 的 存 储 空 间 。第 一 次 加 载 程 序 首 先将 存 放 在 Fls a h中 首 1KB 的数 据 搬 入 DS P内 部存 储 器 , 后 运 行 二 次 加 载 程 序 , 后 续 然 将

的 程 序 或 数 据 搬 入 DS P片 上 存 储 器 ] 。加 载 的 流 程 如 图

图 2 混合 存 储 映射 二 次 加 载 流 程

在该 模 式 下 , 二次 加 载 程 序 能 够 访 问 任 意 的 D P内部 S 地 址 , 破 了被 加载 程 序 长 度 的 限 制 , 有 更 高 的灵 活 性 , 突 具

1 T 公 司 提 供 的 二 次 加 载 方 法 I

TI 司 的 DS 公 P芯 片 二 次 加 载 的 原 理 是 一 致 的 , 载 加 步骤 如 下 :

1 2 混合 存 储 映射 的加 载 方 式 .

继 推 出 C 2 1和 C 7 1后 , 公 司 又 推 出 了 程 序 与 6O 60 TI

方式 。

1 1 分 离 存 储 映 射 的 加 载 方 式 .

在 TI 司 最 初 推 出的 C6 0 P中 , 序 与 数 据 空 公 0 0DS 程

问 采 用 分 离 的 存 储 映 射 方 式 , 表 芯 片 为 C6 O 和 代 2l

不 大 于 1 B的 K 二 次 加

问 。 而 且 运 行 第 一 次 加 载 程 序 时 , 要 将 存 放 在 Fa h 中 就 ls

混 合 存 放 的主 程 序 和 数 据

// /

J 程序和数据

跳 转 到程 序 入 口完 成 自举

TMS320C6000-DSP-指令详解

*-R[ucst5] *--R[ucst5]

带15位常数偏移量 *+B14/B15 的寄存器相对寻址 [ucst15]

*R--[ucst5]

基地址+变址 *+R[offsetR] *++R[offsetR] *R++[offsetR]

*- R[offsetR] * --R[offsetR] *R--[offsetR]

2- n ≤ | x | ≤ 1 - 2- n

Q格式定点数

定点整数是纯整数,约定的小数点位置在有效数 值部分最低位之后。若数据 x 的形式为 x = x0 x1x2…xn ( 其中x0为符号位,x1~xn 是尾数, xn 为最低有效位 ),则在计算机中的表示形式为:

Q15 格式数

1≤ | x | ≤ 2n - 1

同样一个16位数,若小 数点设定的位置不同, 它所表示的数也就不同。

Q0 : 2000H=8192 Q15 :2000H=0.25

Q格式定点数

所谓定点格式,即约定机器中所有数据的小数点位置是固定不变的。在 计算机中通常采用两种简单的约定:将小数点的位置固定在数据的最高 位之前,或者是固定在最低位之后。一般常称前者为定点小数,后者为 定点整数。

3、按寻址方式的加减法运算类指令ADDA/SUBA 此类指令在默认方式下做线性加减法运算。但当源操作数src2

是A4~A7或B4~B7中的一个时,它按AMR寄存器指定的寻址 方式做线性或循环计算。指令的操作数有字/半字/字节3种。 此类指令只在功能单元.D1或.D2运行。

11

算术运算类指令

5 寻址方式

寻址方式指CPU是如何访问其数据存储空间。C6000全部采 用间接寻址,所有寄存器都可以做线性寻址的地址指针。 A4~A7,B4~B7等8个寄存器还可作为循环寻址的地址指针, 由寻址模式寄存器AMR控制地址修改方式:线性方式(默认) 或循环方式。

cache相关概念及工作原理介绍

cache相关概念及工作原理介绍【原创版】目录一、Cache 的概念二、Cache 的作用三、Cache 的工作原理四、Cache 的类型与结构五、Cache 的应用场景正文一、Cache 的概念Cache,即高速缓存,是一种存储技术,它位于主存与 CPU 之间,作用是提高 CPU 访问存储器的速度。

Cache 可以看作是主存的一个高速副本,它将主存中频繁访问的数据复制到自身,当 CPU 需要再次访问这些数据时,可以直接从Cache 中获取,从而减少了 CPU 与主存之间的访问延迟。

二、Cache 的作用Cache 的主要作用是提高 CPU 的运行效率。

随着 CPU 处理速度的提升,主存的访问速度逐渐成为系统性能的瓶颈。

通过使用 Cache,可以减少 CPU 等待主存读写完成的时间,从而提高 CPU 的执行效率。

三、Cache 的工作原理Cache 的工作原理主要包括两个方面:一是缓存策略,即如何判断哪些数据需要被缓存;二是替换策略,即当 Cache 空间不足时,如何选择淘汰哪些缓存数据。

1.缓存策略缓存策略主要根据程序的访问模式来判断。

一般来说,缓存策略可以分为以下三种:- 时域局部性(Temporal Locality):程序在一段时间内多次访问相同的数据。

这种局部性可以通过缓存来提高访问速度。

- 空间局部性(Spatial Locality):程序在访问一个数据时,很可能还会访问其附近的数据。

这种局部性可以通过缓存来提高访问速度。

- 随机访问(Random Access):程序访问的数据与缓存中存储的数据无关,这种访问模式无法通过缓存来提高访问速度。

2.替换策略当 Cache 空间不足时,需要选择一些缓存数据进行替换。

替换策略主要有以下几种:- 最近最少使用(Least Recently Used,LRU):选择最近最少使用的数据进行替换。

- 时间戳(Timestamp):记录每个数据在 Cache 中的时间,选择最早进入Cache 的数据进行替换。

第2章 TMS320C6000系列CPU、指令系统、伪指令

2.3.1 程序存储器

2. 片内程序存储器 TMS320C6201/C6204/C6205/C6701的内部程序存储器可以由用户配置为Cache 或存储器映射的程序空间。如图2-17所示。

2.3.1 程序存储器

允许对一个存储区进行程序取指的同时在另一个存储区进行DMA访问,如图218所示。

2.3.2 内部数据存储器

2.3.3 二级内部存储器

命中时将在单周期内向CPU返回相应的数据。如图2-28所示为T存储器

2. 一级数据Cache(L1D) 一级数据Cache(L1D)是含有64个集的4KB的双路联合集缓存,每行大小为 32B,由于存取的最小单位为字,所以每一个申请提交的地址的最低2位都将被L1D 忽略,位2作为字地址,位3和位4作为4个8字节子行的选择子,其后的6bit选择缓

2.4.3 汇编伪指令

1.定义段伪指令 2.初始化常数伪指令

3.对准程序计数器伪指令

4.输出列表格式伪指令 5.引用其它文件伪指令 6.条件汇编伪指令 7.汇编时使用的符号伪指令 8.其它伪指令 9.伪指令参考

1. 数据存储器控制器 数据存储器控制器在TMS320C62x/C67x DSP结构中的位置见图2-16。具有如下 功能 : 对CPU和DMA控制器访问内部数据存储器的申请进行仲裁; 对CPU访问EMIF的申请进行处理; 作为CPU通过外设总线控制器访问内部集成外设的桥梁; CPU请求数据读并写到内部程序存储器;或者通过外围设备总线控制器 的内部集成外设以及EMIF; DMA控制器请求对内部数据存储器进行读写; CPU不能通过数据存储控制器访问内部程序存储器。

第2章 TMS320C6000系列DSP硬件结构

数据存储器

• 2.内部数据存储器 • (1)TMS320C6201/C6204/C6205内部数据存储器的结构 • 数据存储器组成见表2-14。

数据存储器

同其他块相连的数据存储器控制器框图见图2-21。

数据存储器

• (2)TMS320C6701内部数据存储器的结构 • TMS320C6701的内部数据存储器容量为64KB,分为两块,占据地址 为8000 0000h~80007 FFFh和8000 8000h~8000 FFFFh,便于 CPU和DMA控制器或CPU的A和B侧对两块中的数据同时存取而不发 生冲突。表2-15和图2-22列出数据存储器组成和连接图。

数据存储器

• (3)内部存储器的双CPU访问

• (3)内部存储器的双CPU访问 • CPU和DMA均可以对8位字节、16位字的数据进行读写,数据存储控 制器对每个16位的块进行单独的仲裁,尽管是对16位宽的字执行,但 块具有字节使能功能以支持字节宽数据的访问。 • (4)内部存储器的DMA访问 • DMA控制器可以与CPU同时进行对片内数据RAM的访问,只要它们 要存取的数据位于不同的块中,或是位于相同块的不同Bank中。如果 都要访问同一个存储体,就会产生资源冲突,此时通过设置的 DMA/CPU优先级来决定访问顺序。

DSP CSL的使用

DSP CSL的使用(cache,timer)芯片支持库(CSL)提供了一个用于配置和控制片上外设的C语言接口。

它有各个分立的模块组成,并被编译成为库文件。

每个模块对应一个单独的外设,除了个别提供通用程序支持的模块。

使用CSL可以方便片上外设的使用,缩短开发周期,提高程序的可移植性,硬件抽象。

在硬件层标准化并相互兼容(见CCS->help->contents->TMS320C6000 DSP Reference->C6000Libraries->C6000 Chip Support Library)◎需要手动加入库文件:C:\CCStudio_v3.1\C6000\csl\lib\cslDM642.lib/** 功能:CSL中cache module和timer module的使用示例* 说明:需要手动加入库文件:C:\CCStudio_v3.1\C6000\csl\lib\cslDM642.lib,建议到TI网站下载最新的CSL库更新,否则有些模块可能会出问题* 设计者: 3881* 日期:2010-5-28*/#include <csl.h>//顶层应用程序模块,用于初始化CSL#include <csl_timer.h>#include <csl_cache.h>//结构体,用于配置TIMERTIMER_Config MyConfig = {0x00000200, /* ctl */0xFFFFFFFF, /* prd */0x00000000/* cnt */};TIMER_Handle myhTimer;void main(){…//初始化CSL,使用任何CSL函数前必须初始化,只需初始化一次CSL_init();//初始化L2cacheCACHE_setL2Mode(CACHE_128KCACHE);CACHE_enableCaching(CACHE_EMIFA_CE00);//初始化定时器myhTimer = TIMER_open(TIMER_DEV0, 0);TIMER_config(myhTimer, &MyConfig);//开启定时器(如有必要,将cnt清零)TIMER_setCount(myhTimer, 0x00000000);TIMER_start(myhTimer);myprocess();//读取时间TIMER_pause(myhTimer);TestTime = TIMER_getCount(myhTimer)*0.00001271565;//换算成ms,//关闭定时器TIMER_close(myhTimer);}。

DSP函数解释

IRQ_enable(IRQ_EVT_EDMAINT);//允许IRQ

HWI_enable(); //开硬件中断 ห้องสมุดไป่ตู้

EDMA_intEnable(2); //允许EDMA中断

EDMA_enableChannel(hEdmaCha5);//允许EDMA通道5

CSL_init(); //初始化芯片函数库

CACHE_clean(CACHE_L2ALL,0,0);//清缓存

CACHE setL2Mode(CACHE_128KCACHE);//将L2缓存设为128K

CACHE_enableCaching(CACHE_EMIFA_CE00);//允许外存CEOO作为缓存

CACHE_enableCaching(CACHE_EMIFA_CE01);//允许外存CE01作为缓存

EMIFA_config(&emifaCfg0); //设置EMW数据总线

IRQ_reset(IRQ_EVT_EDMAINT);//复位IRQ

IER=0x303; //设置中断寄存器

EDMA_config(hEdmaCha5,&edmaCfg0);//设置EDMA

第五章C6000系列DSPs的集成外设1

64MB~ 3C20 0000~7FFF FFFF 1GB 256MB 8000 0000~8FFF FFFF 256MB 9000 0000~9FFF FFFF 256MB A000 0000~AFFF FFFF 256MB B000 0000~BFFF FFFF 1GB C000 0000~FFFF FFFF

McBSP1

OR

IIC 1

HPI

OR

GPIO McASP 1

IIC 0

2 Timers PLL

Power Down Logic

Boot Configuration

C67xTM DSP Core

Level 1 Data Cache

4K Bytes

• 片内采用2级高速缓 存结构,程序和数据 拥有各自独立的高速 缓存。

256KB~ 0004 0000~017F FFFF 24MB 256KB 0180 0000~0183 FFFF

128KB 0184 0000~0185 FFFF

128KB 0186 0000~0187 FFFF

256KB 256KB

0188 0000~018B FFFF

018C 0000~018F FFFF

L2写命中的分配

L2 L1P读总线宽度 L2 L1D读总线宽度 L1DL2写总线宽度 L1DL2驱逐总线宽度 L2 EDMA读总线宽度 L2 EDMA写总线宽度

数据写入命 中的L2区域 256bit 128bit 32bit 128bit 64bit 64bit

13

• 分配(allocate):是在Cache中寻找一个位置来存储新的、未缓存的 数据的过程

Program fetch

cache处理流程

cache处理流程Cache处理流程在计算机系统中,缓存(Cache)是一种用于存储临时数据的高速存储器。

它被用于提高数据访问速度,减少对主存储器的访问次数,从而提高整个系统的性能。

在计算机系统中,缓存处理流程可以概括为以下几个步骤:数据请求、缓存命中、缓存未命中、数据读取、数据写入和替换算法。

1. 数据请求:当计算机系统需要读取或写入数据时,首先会发出数据请求。

数据请求可以是来自于CPU的指令请求,也可以是来自于外部设备的输入输出请求。

数据请求通常包含要访问的数据地址和访问类型(读取或写入)。

2. 缓存命中:在缓存中进行数据访问之前,首先需要检查数据是否已经存在于缓存中。

这个过程称为缓存命中检测。

如果数据已经存在于缓存中,则称为缓存命中;如果数据不存在于缓存中,则称为缓存未命中。

3. 缓存未命中:当数据未命中缓存时,需要从主存储器中读取数据。

在进行数据读取之前,可能还需要进行一些其他操作,例如地址转换、物理内存访问等。

这些操作会增加数据读取的延迟。

4. 数据读取:当数据未命中缓存时,需要从主存储器中读取数据。

数据读取的过程涉及到地址传输、数据传输、数据写入等操作。

数据读取的速度通常比较慢,因为主存储器的访问速度相对较低。

5. 数据写入:在对数据进行修改或更新时,需要将数据写入缓存和主存储器中。

数据写入的过程类似于数据读取,涉及到地址传输、数据传输、数据写入等操作。

数据写入的速度也比较慢,因为需要保证数据的一致性和可靠性。

6. 替换算法:当缓存已满时,需要使用替换算法来确定哪些数据应该被替换出去,以腾出空间存储新的数据。

替换算法的选择会影响缓存的性能和命中率。

常见的替换算法有最近最少使用(LRU)、先进先出(FIFO)等。

缓存处理流程包括数据请求、缓存命中、缓存未命中、数据读取、数据写入和替换算法。

通过使用缓存,计算机系统可以提高数据访问速度和系统性能,减少对主存储器的访问次数。

然而,缓存也会带来一些问题,例如缓存一致性、缓存失效等,需要在设计和实现中加以考虑和解决。

cache的工作流程

cache的工作流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 数据请求:当 CPU 需要访问主存中的数据时,它首先会检查 cache 是否已经缓存了该数据。

C6000体系结构与汇编语言2--寄存器

中断和中断寄存器

C6000中断的3种类型: Reset,NMI,可屏蔽中断 中断源:32个 中断选择号:5bit 中断:16个 中断选择子(寄存器): 外中断极性寄存器:INT4~INT7硬件中断

中断服务表( IST )

IST是包含中断服务 代码的取指包的一 个地址表。当CPU 开始处理一个中断 时,它要参照IST进 行。

CPU版本

Powerdown逻辑

Powerdown逻辑

大小端位

Little-endian ordering, in which bytes are ordered from right to left, the most significant byte having the highest address Big-endian ordering, in which bytes are ordered from left to right, the most significant byte having the lowest address 大小端位由DSP的EN管脚设置

C6000 体系结构和汇编语言之二 ---寄存器

本节内容

CPU寄存器:需要硬件背景知识 控制寄存器; 中断寄存器; DMA寄存器; 外设寄存器; 串口寄存器.

可观察的核寄存器

核寄存器: 非存储器映射; MVC指令修改

还有ICR,ISR

可观察的核寄存器

控制/状态寄存器:CSR

控制/态寄存器:CSR

大小端位

PCC和DCC: cache 模式

指CPU读指令 直接从片外读程序

针对C6211/C6711/C64XX

PGIE位

C6000体系结构与汇编语言4--存储器

C620x/C670x Cache的结构

直接映射式: cache的行(line)容量256-bit,可容纳8条32bit的指令。Cache中每一行对应一个取指包, 直接映射外存中某个地址的内容。

C6201/C6204/C6205/C6701 Cache地址的解析

C6202(B)/C6203(B) Cache地址的解析

C621x/C671x/C64x的L1D

双路组联想结构

6BIT,64组

5BIT,32字节

128组

访问L1D cache 阻塞: CPU的数据访问如果命中L1D,将单周期返回需要的数据。如果 没有命中L1D,但是命中L2,对于C621x/C671x,CPU将被阻塞4 个周期;对于C64x,CPU将被阻塞2~8个周期。

Cache存储系统组成

Cache系统组成原理

Cache系统工作原理

Cache和主存储器都划分成相同大小的 块(有的地方也称行,line) 块(Block)的大小是2的整次幂,一块 包含若干字,字可分为字节。 Cache与主存储器之间以块为单位进行 数据交换。 主存储器的块可以采用某种地址映象和 地址变换映射到Cache上的块。

C620x/C670x的片内数据存储器

C6201/C6204/C6205片内数据存储器的 组织结构: 思考:为什 么分为多个 bank?2个 block?

C6701片内数据存储器的组织结构

思考:为什 么C67的bank 数为8?C62 为4?

C620x/C670x对片内数据存储器的访问

数据访问的格式控制: 边界限制 DMA数据传输 优先级

Cache系统工作原理(全相联)

有关C6000系列DSP的内联函数

在c中,为了解决一些频繁调用的小函数大量消耗栈空间或是叫栈内存的问题,特别的引入了inline修饰符,表示为内联函数数。

栈空间就是指放置程序的局部数据也就是函数内数据的内存空间,在系统下,栈空间是有限的,假如频繁大量的使用就会造成因栈空间不足所造成的程序出错的问题,函数的死循环递归调用的最终结果就是导致栈内存空间枯竭。

下面我们来看一个例子#include <stdio.h>inline char* dbtest(int a); //函数原形声明为inline即:内联涵数int main(){int i = 0;for (i=1;i<=10;i ){printf("%d is %s/n",i,dbtest(i));}return 0;}char* dbtest(int a)//这里不用再次inline,当然加上inline也是不会出错的{return (a%2>0)?"奇":"偶";}上面的例子就是标准的内联函数的用法,使用inline修饰带来的好处我们表面看不出来,其实在内部的工作就是在每个for循环的内部任何调用dbtest(i)的地方都换成了(i%2>0)?"奇":"偶"这样就避免了频繁调用函数对栈内存重复开辟所带来的消耗。

说到这里很多人可能会问,既然inline这么好,还不如把所谓的函数都声明成inline,嗯,这个问题是要注意的,inline的使用是有所限制的,inline只适合涵数体内代码简单的涵数使用,不能包含复杂的结构控制语句例如while switch,并且不能内联函数本身不能是直接递归函数(自己内部还调用自己的函数)。

说到这里我们不得不说一下在c语言中广泛被使用的#define语句,是的define的确也能够做到inline 的这些工作,但是define是会产生副作用的,尤其是不同类型参数所导致的错误,由此可见inline有更强的约束性和能够让编译器检查出更多错误的特性,在c 中是不推荐使用define的。

第2章 TMS320C6000系列的硬件结构-244

2.4.3 片内2级(L2)高速缓存的结构 1) C621x/C671x的L2容量为64KB,C64x 的L2容量为1024KB;

2)可以工作在5种模式下,由CCFG中的 L2MODE控制

L2的五种模式

高速缓存访问逻辑

2.4.4 片内高速缓存的控制

控制寄存器 除了前面提到的多个cache控制寄存器,C621x/ C671x

C621x/C671x/C64x2级高速缓存结构

C621x/C671x 2级存储器结构

2.4.1 片内1级程序(L1P)高速缓存的结构

1)C621x/C671x和C64x 区别 C621x/C671x的L1P行大小为64 B ,缓存64组 C64x L1P的行大小为32 B,缓存512组

2.4.1 片内1级程序(L1P)高速缓存的结构

/C64x还提供了一组存储器属性寄存器(Memory Atribute Registers,MAR),用于控制外存某一段空间 的高速缓存使能。

本章小结

1 C6000系列DSP处理器组成 CPU内核、外设和存储器

2 C6000DSP芯片的CPU结构 CPU数据通路和控制

3 片内存储器和二级内部存储器 结构原理、寄存器和应用

习题

1 cache —地址的解析

2 对片内数据存储器的访问

假设源地址xxxxxx00h中预先存放的数据为A8A76543h

不同endian模式下数据访问结果 LDH(地址位:00h) 大端: 小端:

第2章 TMS320C6000系列的硬件结构

本章内容提要: Biblioteka 芯片的设计角度出发,利用简单的汇编指令实现经典的

数字信号处理算法-点积运算,同时引出C6000DSP芯片 的结构。

如何使用DSP的cache(转)

如何使用DSP的cache(转)C6747在执行一块算法的执行时间在114ms左右,需求要20ms以下。

6000属于分层存储器体系架构,内部RAM跟CPU不同频运行,只有cache使能才跟CPU同频。

可能是cache没打开。

下面转载一遍文章。

非常感谢原创。

处理器中的cache是存放于处理器四周的高速存储器,它可以用来保存运算处理时的一些共有的指令,从而加速运算的速度。

在本文中,将比较cache存储器和系统中的普通的存储器,随后将先容cache的一些基本理论和基本术语,以及在高速处理器结构中cache的重要性。

以TI的TMS320C64x DSP结构为基础,将着重向开发者先容cache是如何工作,如何配置,以及如何正确使用cahce,本文将以cache的一致性贯串全文。

存储器结构在图一中,左边的模块先容了普通的存储器系统结构,CPU和内部存储器均工作在300MHZ。

当CPU访问外部存储器时,将不会发生存储器访问禁止的情况。

并且当访问内部存储器时也不会发生访问延迟的情况。

当CPU的时钟增加到600MHZ时,只有当存储器的速度也增加到600MHZ时才不会发生访问等待的状态。

很不幸,对于大多数情况下同样频率工作在600MHZ的内部存储器价格将十分昂贵。

而300MHZ的也不是好的选择,由于将大幅降低CPU的频率。

设想一个算法需要在每个周期访问存储器,每一次对存储器的访问需等待一个周期,加倍了访问周期从而抵消了CPU的双倍工作频率。

图一:普通存储器和多层存储器结构解决的办法就是采用一个多层次的存储器。

最靠近CPU的存储器由一块速度快但体积小组成,访问时不存在任何延迟。

稍阔别一些CPU的采用体积大但速度稍慢的存储器。

对于低级别的存储器来说,最靠近CPU的这块存储器便是典型的cache存储器位置法则当然,这个解决办法必须工作在CPU能够最快访问最近的存储器的情况时。

由于位置法则,对于大多数CPU来说这一情况都是适用的。

cache的读数操作流程

cache的读数操作流程Cache是计算机系统中的一种高速缓存存储器,用于存储最近被访问过的数据,以提高数据访问速度。

在计算机系统中,CPU通过读取和写入内存中的数据来执行各种操作。

然而,由于内存的访问速度相对较慢,为了提高CPU的运行效率,通常会在CPU和内存之间添加一个高速缓存存储器,即Cache。

Cache的读数操作流程通常包括以下几个步骤:1. 缓存命中检查:当CPU需要读取数据时,首先会检查Cache中是否已经存储了该数据。

如果Cache中已经存在需要的数据,即发生了缓存命中,CPU可以直接从Cache中读取数据,而无需访问内存,从而提高了数据访问速度。

2. 缓存未命中处理:如果在Cache中未找到需要的数据,即发生了缓存未命中,CPU需要从内存中读取数据。

此时,CPU会向内存发送读取请求,并等待内存返回数据。

3. 数据加载到Cache:一旦内存返回数据,CPU会将数据加载到Cache中,以便下次访问时可以直接从Cache中读取数据。

同时,CPU还会更新Cache中的标记位和其他相关信息,以确保Cache中的数据与内存中的数据保持一致。

4. 数据传输到CPU:最后,CPU从Cache中读取数据,并将数据传输到执行单元进行相应的操作。

在数据传输过程中,Cache会根据CPU的访问模式和策略进行数据预取和预取处理,以提高数据访问效率。

总的来说,Cache的读数操作流程可以帮助CPU快速访问最近被访问过的数据,从而提高计算机系统的运行效率和性能。

通过合理设计Cache的结构和算法,可以进一步优化数据访问速度,提高计算机系统的整体性能。

Cache技术在现代计算机系统中扮演着重要的角色,对于提高系统的响应速度和处理能力具有重要意义。

c2000,c5000,c6000系列DSP编程方法

二、TI公司三大系列内部结构的简介 1、C2000系列的内部结构1,C2000系列基于改进的哈佛结构,支持分开的程序空间和数据空间。

还有第三个空间,即I/O空间,用于片外总线接口。

外设总线映射到数据空间,因此,运行在数据空间的所有指令,都可以运行于所有的外设寄存器。

C2000系列的CPU包括:一个32位的中心算术逻辑单元(CALU)、一个32位的累加器(ACC)、CALU具有输入和输出数据定标移位器、一个16x16位乘法器、一个乘积定标移位器、数据地址产生逻辑:包括8个辅助寄存器和1个辅助寄存器算术单元(ARAU)、程序地址产生单元C2000系列采用2xLPASIC核,其内部设有6组16位的数据与程序总线。

这6组总线是:PAB(ProgramAddr.Bus)程序地址总线DRAB(Data-ReadAddr.Bus)数据读地址总线; DWAB(Data-WriteAddr.Bus)数据写地址总线; PRDB(ProgramReadBus)程序读总线;DRDB(DataReadBus)数据读总线;DWEB(DataWriteBus)数据写总线。

将数据读地址总线(DRAB)和数据写地址总线(DWAB)分开,CPU就可以在同一个机器周期内读和写数据。

C2000系列具有以下类型的片内存储器:双访问RAM(DARAM),即一个机器周期内可以访问两次的存器;FlashEEPROM或工厂掩模的ROM。

C2000系列的存储器分为单独可选择的4个空间,总共的地址范围为224K字:程序存储器(64K字);局部数据存储器(32K字);全局数据存储器(64K字);输入/输出(64K字)。

2、C5000系列的内部结构C5000系列中央处理单元CPU包括算术逻辑单元、乘法器、累加器、移位寄存器、各种专门用途的寄存器、地址发生器、比较选择单元、指数编码器。

具体内容如下①先进的多总线结构,具有1条程序存储器数据总线、3条数据存储器数据总线和4条地址总线;②40位算术逻辑单元(ALU),包括40位的桶形移位寄存器和2个独立的40位的累加器;③17位乘17位的并行乘法器与一个40位的专用加法器结合在一起,用于单周期乘/累加操作;④比较、选择和存储单元(CSSU),用于Viterbi操作(一种通信的编码方式)中的加/比较选择;⑤指数编码器用于在单周期内计算40位累加器的指数值;⑥2个地址生成器,包括8个辅助寄存器和2个辅助寄存器算术单元[6]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

篇幅之一TI C64x+ DSP CACHE 一致性分析与维护作者:DSP 技术应用工程师陈永康摘要在各种数字信号处理系统中,CACHE被广泛用于弥补Core与存储器之间的速度差异。

在CACHE 的使用过程中,存在不同类型存储器之间数据是否一致的问题。

本文着重分析TI高性能C64x+ DSP系列中各级CACHE之间数据一致性问题以及如何进行一致性维护。

1. 概述CACHE作为Core和低速存储器之间的桥梁,基于代码和数据的时间和空间相关性,以块为单位由硬件控制器自动加载Core所需要的代码和数据。

如果所有程序和数据的存取都由Core完成,基于CACHE 的运行机制,Core始终能够得到存储器中最新的数据。

但是当有其它可以更改存储器内容的部件存在时,例如不需要Core干预的直接数据存取(DMA)引擎,就可能出现由于CACHE的存在而导致Core或者DMA不能够得到最新数据的现象,也就是CACHE一致性的问题。

2. C64x+ 存储器组织结构TI对高性能C64x核进行了改进,使其性能大大提升,称之为C64x+DSP核。

基于C64x+核开发的DSP芯片,所有部件都以交换网络(SCR)为核心连接起来。

SCR上的部件分为两类:Master和Slave。

Master包括Core、EDMA以及串行高速IO(sRIO),EMAC等外设。

Master可以直接通过SCR发起到Slave的数据传输。

Slave包括每一个Core的内存,DDR2外存以及其它不能直接发起数据传输的外设,Slave之间的数据传输,需要通过DMA协助完成。

各款基于C64x+DSP的数据手册上详细描述了SCR的配置和Master、Slave的情况。

C64x+系统的存储器框图如图1所示。

存储器被分成了三级:第一级是L1,包含数据存储器(L1D)和代码存储器(L1P);第二级是代码和数据共用存储器(L2);第三级是外部存储器,主要是DDR2存储器。

L1P、L1D和L2的CACHE功能分别由相应的L1P控制器、L1D控制器和L2控制器完成。

表1总结了C64x+平台上可用的CACHE情况。

图 1 C64x+存储器框图表 1 C64x+ CACHE特性类型大小Line 大小L1P 代码;直接映射;最大32K 字节32 字节L1D 数据;2路;读分配最大32K 字节64 字节L2 代码、数据;4路;读写分配最大256K 字节128 字节C64x+平台上L1P用来存储或者缓存代码;L1D用来存储或者缓存数据。

L1P和L1D大小都是32K 字节,可以分别配置0K、4KB、8KB、16KB或者32KB作为CACHE,其余作为代码或者数据RAM。

作为CACHE的部分,用来缓存L2和DDR2的数据或代码。

作为RAM的部分,可以存储关键的代码或者数据使得Core能够以很高的速度C64x+平台上L2 存储器可用于存储代码和数据。

L2上最大可以分配256K字节CACHE来缓存DDR2中的数据或代码。

L2中其余部分作为RAM存储代码和数据。

图2描述了Core访问存储器内容的操作流程。

在这个访问流程中,Core对于存储器的访问总是先从离Core最近的一级存储器开始,如果命中,Core可以直接得到代码/数据,否则代码/数据会被加载到前几级的CACHE中,从而Core可以得到要处理的代码/数据。

在这个动态访问过程中,各级CACHE中的内容和下一级存储器中的内容可能存在不一致,这种瞬态的不一致不会造成问题。

但是,如果Core或者其它Master不能得到另外一方对存储器内容更新后的内容,就会出现CACHE一致性问题。

图 2 Core访问存储器流程3. CACHE一致性问题分析在任何时刻,Core或者其它Master访问存储器中数据时,由于CACHE的存在造成不能够得到最近更新过的数据,就会出现CACHE一致性问题。

在一个特定的时间范围内,各级CACHE和它的下一级存储器中的内容不一致是正常的。

因为CACHE 的作用是在一段时间内将低速存储器中的内容自动搬运到高速的CACHE中重复使用。

当CACHE中的空间被后续的数据占用的时候,才将CACHE中的内容进行失效或者回写的操作。

在失效或者回写之前,CACHE中的内容可能与物理存储器中的内容是不一致的。

这种临时性的不一致是正常的,上述CACHE 一致性问题的描述不包含此类正常情况。

CACHE的引入是为了提高Core存取数据的效率,所以出现CACHE一致性问题一定与Core对存储器的访问有关。

Core对存储器的访问分为两类:1. Core读代码或者数据;2. Core写代码或者数据。

据此,CACHE的一致性问题分为两个大类:Core读一致性问题和Core写一致性问题。

在下面两个小节中,分别描述了这两种情况的模型:3.1 Core读一致性模型图3给出了Core读一致性的模型。

在这个模型中,CACHE一致性问题的存在取决于图中虚线箭头指示的第二步操作能否在Core从CACHE中重新读数据之前完成。

如果不能,则会造成Core读取的数据不是其它Master更新后的数据,而是原来CACHE中的内容,从而导致一致性的问题。

图 3 Core读一致性模型L1P CACHE对L2内存或者DDR2外存中的代码进行缓存。

当Core第一次对L2或者DDR2中的代码进行读操作的时候,由于代码不在L1P CACHE中,CAHCE硬件会将L2或者DDR2中的代码读到L1P CACHE中。

Core可以得到最新的代码,不存在一致性的问题。

此后,如果其它Master更新L2或者DDR2中的代码,然后Core再次读取此部分代码时,会发现相应的代码已经存在L1P CACHE中,此时Core会直接从L1P CACHE中读取代码。

由于Core不能得到最新的代码,就出现了Core读一致性的问题。

L1D Core读一致性问题的原理和L1P相同,只是L1D缓存的是L2或者DDR2中的数据。

L2 CACHE对DDR2中的代码/数据进行缓存,当Core第一次对DDR2中的代码/数据进行读操作,这时代码/数据不在L2 CACHE中,需要进行L2 CACHE的加载,Core可以得到最新的代码/数据。

之后,其它Master对DDR2中的代码/数据进行更改,Core重读此部分代码/数据的时候,Core读到的是L2 CACHE中的内容而不是DDR2中最新的代码/数据,因此也存在Core读一致性的问题。

3.2 Core写一致性模型图4给出了Core写一致性的模型。

在这个模型中,CACHE一致性问题的存在取决于图中虚线箭头指示的第二步操作能否在其它Master从存储器中读数据之前完成。

如果不能,会造成其它Master从存储器中读到的数据是原来的数据而不是Core更新过的数据,从而导致一致性的问题。

图 4 Core写一致性模型当Core对L2或者DDR2中的代码/数据进行写操作的时候,如果代码/数据已经在L1 CACHE中,新的代码/数据会被更新到L1 CACHE中。

当其它Master从L2或者DDR2中读代码/数据的时候,会直接从L2或者DDR2中读取相应的内容,如果L1 CACHE中新的代码/数据未被更新到L2或者DDR2中,则其它Master读取的不是更新后的内容,就会出现Core写一致性的问题。

同样,Core更新过的代码/数据有可能只是缓存在L2 CACHE中,其它Master从DDR2中读取的内容不是更新后的内容,同样会出现Core写一致性的问题。

3.3 C64x+一致性分析在C64x+上的CACHE一致性问题,需要根据放置代码/数据的相应位置进行分析。

由于在C64x+平台上,L1P、L1D和L2内存既可以作为CACHE又可以作为存储器使用,因此,在分析一致性问题的时候,需要考虑以下几种情况Case1. 代码在L1P存储器中;Case2. 代码在L2存储器中;Case3. 代码在DDR2存储器中;Case4. 数据在L1D存储器中;Case5. 数据在L2存储器中;Case6. 数据在DDR2存储器中。

对于Case1,由于代码直接在L1P存储器中,不需要进行CACHE,所以不会存在一致性的问题。

对于Case2和Case3,涉及到L1P CACHE,存在代码的更新能否被Core读到的问题。

代码的更新分成两种情况:一是Core在运行过程中对代码进行修改;二是其它Master对代码的修改。

这两种情况下,都会存在CACHE读一致性问题,需要由软件来维护。

对于Case4,数据直接在L1D存储器中,Core始终能够读到其它Master更新到L1D内存中的内容,Core写过的数据也能够被其它Master直接从L1D内存中读到。

所以不会存在一致性的问题。

对于Case5,数据在L2存储器,按照上面的分析,会存在CACHE读和写一致性的问题。

在C64x+平台上这种情况下的一致性问题会由硬件自动维护。

对于Case6,也会存在CACHE读和写一致性的问题,这种情况需要软件进行CACHE一致性的维护。

4. C64x+ CACHE一致性维护操作出现CACHE一致性问题时,为了保证Core或者其它Master在进行数据操作的时候能够得到最新的数据,需要进行CACHE的一致性维护操作。

CACHE一致性问题维护在设计中,有两种处理方式:硬件自动维护和应用程序进行维护。

下面具体分析以上几种情况在C64x+平台上如何进行CACHE一致性问题处理:4.1 硬件维护的CACHE一致性在C64x+平台上,硬件会对Case5的情况自动进行数据一致性维护。

分析需要分为读写两类操作进行,图5和图6分别描述了Core对L2上的数据进行读和写的情况。

图 5 Core读L2数据的情况图 6 Core写L2数据的情况其它Master要对L2中的内容进行更新操作时,L2控制器会根据被更新数据的地址判断相应的地址是否在L1D CACHE中,如果在L1D CACHE中,硬件会自动将更新的数据拷贝一份到L1D CACHE中。

当Core重新对L2中的这部分数据进行处理的时候,如果要读取的数据已经在L1D CACHE中,Core可以直接从L1D CACHE中得到更新过的数据。

如果要读取的数据不在L1D CACHE中,L1D控制器会自动从L2加载数据,Core也可以得到更新后的数据。

过程如图5中的1和2所示,这样就可以解决一致性的问题。

其它Master要对L2中的内容进行读操作的时候,L2控制器会判断要读取的数据地址是否在L1D CACHE中,对于在L1D CACHE中的数据,硬件会自动从L1D CACHE中读取最新的数据。

对于不在L1D CACHE中的数据,说明L2中的数据已经是最新的数据,可以直接从L2中读取。