IIR数字滤波器的设计毕业论文外文文献翻译及原文

毕业设计(论文)-基于MATLAB的IIR数字滤波器的设计

IIR数字滤波器的设计摘要数字滤波器是对数字信号进行滤波处理以得到期望的响应特性的离散时间系统。

作为一种电子滤波器,数字滤波器与完全工作在模拟信号域的模拟滤波器不同。

数字滤波器工作在数字信号域,它处理的对象是经由采样器件将模拟信号转换而得到的数字信号。

数字滤波器的工作方式与模拟滤波器也完全不同:后者完全依靠电阻、电容、晶体管等电子元件组成的物理网络实现滤波功能;而前者是通过数字运算器件对输入的数字信号进行运算和处理,从而实现设计要求的特性。

本文由数字滤波器的功能、应用及发展入手,介绍了数字滤波器的基本概念,其中包括系统的描述、系统的传递函数和IIR数字滤波器基本结构。

其次根据IIR数字滤波器的设计原理,在MA TLAB环境下分别采用脉冲响应不变法、双线性变换法和MA TLAB函数直接设计法对IIR数字滤波器进行了设计。

最后应用FDATool和Simulink工具对IIR数字滤波器进行了仿真。

关键词:IIR数字滤波器;MATLAB;脉冲响应不变法;双线性变换法;FDATool;SimulinkDesign of IIR digital filterAbstractDigital filters are the discrete-time systems that process to filter digital signal to get expected response characteristics. As an electronic filter, digital filters work differently from the analog signal filters who completely work in analogy signal domain. Digital filter work in the digital signal domain and its targets are digital signals that are received by sampling devices converting analog signals to digital signals. The working methods of digital filters and analog filters are completely different: the latter completely rely on the function of the physical network formed by resistors, capacitors, transistors and other electronic components of filtering ,while the former computes and processes digital signals with the help of digital computing devices to realize the characteristics of the design requirements.In this paper, the function, application and development of the digital filter are introduced followed by the introduction of the principle of digital filter design. The principle first includes the description of the system, the transfer function of the system and the basic structure of the IIR (Infinite Impulse Response) digital filter. Then, according to the design principle of IIR digital filter, the IIR digital filter is designed by the method of non-changing impulse response, the method of double linear transform and direct method using MATLAB functions. At last, the designed IIR digital filter is simulated by FDATool and MATLAB Simulink Tool.Key words:IIR digital filter;MATLAB;non-changing impulse response;double linear transformation;FDATool;Simulink目录第一章绪论 (1)1.1数字滤波器技术概述 (1)1.2滤波器及滤波方法的发展历程 (2)1.3滤波器的分类 (3)1.4数字滤波器的优越性 (4)1.5数字滤波器的实现方法 (5)1.6MATLAB软件简介 (6)1.7MATLAB的语言特点 (8)第二章数字滤波器基础 (10)2.1数字滤波器的基本概念 (10)2.2系统的描述 (11)2.3系统的传递函数 (12)2.4IIR数字滤波器的基本结构 (12)2.4.1直接Ⅰ型 (13)2.4.2直接Ⅱ型 (14)2.4.3级联型 (14)2.4.4并联型 (16)第三章IIR数字滤波器的设计方法及过程 (17)3.1基于脉冲响应不变法的IIR滤波器设计 (17)3.2基于双线性Z变换法的IIR滤波器设计 (20)3.3基于MATLAB函数直接设计IIR数字滤波器 (24)3.3.1巴特沃斯数字滤波器设计 (24)3.3.2切比雪夫Ⅰ型IIR数字滤波器设计 (27)3.3.3切比雪夫Ⅱ型IIR数字滤波器设计 (29)3.3.4基于椭圆法直接设计IIR数字滤波器 (30)3.4FDAT OOL设计法 (33)3.5S IMULINK建模设计法 (37)第四章结论 (41)参考文献 (42)致谢 (43)第一章绪论1.1 数字滤波器技术概述数字滤波器实际上就是一种数字信号处理系统的算法或设备,也可以说是一种运算过程。

IIR数字滤波器的设计外文文献以与翻译

IIRDigitaFilterDesignAn important step in the development of a digital filter is the determination of a realizable transfer function G(z) approximating the given frequency response specifications. If an IIR filter is desired,it is also necessary to ensure that G(z) is stable. The process of deriving the transfer function G(z) is called digital filter design. After G(z) has been obtained, the next step is to realize it in the form of a suitable filter structure. In chapter 8,we outlined a variety of basic structures for the realization of FIR and IIR transfer functions. In this chapter,we consider the IIR digital filter design problem. The design of FIR digital filters is treated in chapter 10.First we review some of the issues associated with the filter design problem. A widely used approach to IIR filter design based on the conversion of a prototype analog transfer function to a digital transfer function is discussed next. Typical design examples are included to illustrate this approach. We then consider the transformation of one type of IIR filter transfer function into another type, which is achieved by replacing the complex variable z by a function of z. Four commonly used transformations are summarized. Finally we consider the computer-aided design of IIR digital filter. To this end, we restrict our discussion to the use of matlab in determining the transfer functions.9.1 preliminary considerationsThere are two major issues that need to be answered before one can develop the digital transfer function G(z). The first and foremost issue is the development of a reasonable filter frequency response specification from the requirements of the overall system in which the digital filter is to be employed. The second issue is to determine whether an FIR or IIR digital filter is to be designed. In the section ,we examine these two issues first .Next we review the basic analytical approach to the design of IIR digital filters and then consider the determination of the filter order that meets the prescribed specifications. We also discuss appropriate scaling of the transfer function.9.1.1 Digital Filter SpecificationsAs in the case of the analog filter,either the magnitude and/or the phase(delay) response is specified for the design of a digital filter for most applications. In some situations, the unit sample response or step response may be specified. In most practical applications, the problem of interest is the development of a realizable approximation to a given magnitude response specification. As indicated in section 4.6.3, the phase response of the designed filter can be corrected by cascading it with an allpass section. The design of allpass phase equalizers has received a fair amount of attention in the last few years. We restrict our attention in this chapter to the magnitude approximation problem only. We pointed out in section 4.4.1 that there are four basic types of filters,whose magnitude responses are shown in Figure 4.10. Since the impulse response corresponding to each of these is noncausal and of infinite length, these ideal filters are not realizable. One way of developing a realizable approximation to these filter would be to truncate the impulse response as indicated in Eq.(4.72) for a lowpass filter. The magnitude response of the FIR lowpass filter obtained by truncating the impulse response of the ideal lowpass filter does not have a sharp transition from passband to stopband but, rather, exhibits a gradual "roll-off."Thus, as in the case of the analog filter design problem outlined in section 5.4.1, the magnitude response specifications of a digital filter in the passband and in the stopband are given with some acceptable tolerances. In addition, a transition band is specified between the passband and the stopband to permit the magnitude to drop off smoothly. For example, the magnitude )(j e G of a lowpass filter may be given as shown in Figure7.1. As indicated in the figure, in the passband defined by 0p ωω≤≤, we require that the magnitude approximates unity with an error of p δ±,i.e.,p p j p for e G ωωδδω≤+≤≤-,1)(1.In the stopband, defined by πωω≤≤s ,we require that the magnitude approximates zero with an error of i s ,δ.e.,,)(s j e G δω≤ forπωω≤≤s . The frequencies p ω and s ω are , respectively, called the passband edge frequency and the stopband edge frequency. The limits of the tolerances in the passband and stopband, p δ and s δ, are usually called the peak ripple values. Note that the frequency response )(ωj e G of a digital filter is a periodic function of ω,and the magnitude response of a real-coefficient digital filter is an even function ofω. As a result, the digital filter specifications are given only for the range πω≤≤0.Digital filter specifications are often given in terms of the loss function,)(log 20)(10ωωζj e G -=, in dB. Here the peak passband ripplep α and the minimum stopband attenuations α are given in dB,i.e., the loss specifications of a digitalfilter are given bydB p p )1(log 2010δα--=,dB s s )(log 2010δα-=.9.1 Preliminary ConsiderationsAs in the case of an analog lowpass filter, the specifications for a digital lowpass filter may alternatively be given in terms of its magnitude response, as in Figure 7.2. Here the maximum value of the magnitude in the passband is assumed to be unity, and themaximum passband deviation, denoted as 1/21ε+,is given by the minimum value of the magnitude in the passband. The maximum stopband magnitude is denoted by 1/A.For the normalized specification, the maximum value of the gain function or the minimum value of the loss function is therefore 0 dB. The quantity max α given bydB )1(log 20210max εα+=Is called the maximum passband attenuation. Forp δ<<1, as is typically the case, itcan be shown thatp p αδα2)21(log 2010max ≅--≅ The passband and stopband edge frequencies, in most applications, are specified in Hz, along with the sampling rate of the digital filter. Since all filter design techniques are developed in terms of normalized angular frequencies p ω and s ω,the sepcified critical frequencies need to be normalized before a specific filter design algorithm can be applied. Let T F denote the sampling frequency in Hz, and F P and F s denote, respectively,the passband and stopband edge frequencies in Hz. Then the normalized angular edge frequencies in radians are given byT F F F F p TpT p p ππω22==Ω= T F F F F s T s T s s ππω22==Ω= 9.1.2 Selection of the Filter TypeThe second issue of interest is the selection of the digital filter type,i.e.,whether an IIR or an FIR digital filter is to be employed. The objective of digital filter design is to develop a causal transfer function H(z) meeting the frequency response specifications. For IIR digital filter design, the IIR transfer function is a real rational function of 1-z . H(z)=N MdNzz d z d d pMz z p z p p ------++++++++ (2211022110)Moreover, H(z) must be a stable transfer function, and for reduced computational complexity, it must be of lowest order N. On the other hand, for FIR filter design, the FIR transfer function is a polynomial in 1-z:∑=-=Nnnz nhzH] [)(For reduced computational complexity, the degree N of H(z) must be as small as possible.In addition, if a linear phase is desired, then the FIR filter coefficients must satisfy the constraint:][][Nnhnh-±=T here are several advantages in using an FIR filter, since it can be designed with exact linear phase and the filter structure is always stable with quantized filter coefficients. However, in most cases, the order N FIR of an FIR filter is considerably higher than the order N IIR of an equivalent IIR filter meeting the same magnitude specifications. In general, the implementation of the FIR filter requires approximately N FIR multiplications per output sample, whereas the IIR filter requires 2N IIR+1 multiplications per output sample. In the former case, if the FIR filter is designed with a linear phase, then the number of multiplications per output sample reduces to approximately (N FIR+1)/2. Likewise, most IIR filter designs result in transfer functions with zeros on the unit circle,and the cascade realization of an IIR filter of orderIIRN with all of the zeros on the unitcircle requires [(3IIRN+3)/2] multiplications per output sample. It has been shown that for most practical filter specifications, the ratio N FIR/N IIR is typically of the order of tens or more and, as a result, the IIR filter usually is computationally more efficient[Rab75]. However ,if the group delay of the IIR filter is equalized by cascading it with an allpass equalizer, then the savings in computation may no longer be that significant [Rab75]. In many applications, the linearity of the phase response of the digital filter is not an issue,making the IIR filter preferable because of the lower computational requirements.9.1.3 Basic Approaches to Digital Filter DesignIn the case of IIR filter design, the most common practice is to convert the digital filter specifications into analog lowpass prototype filter specifications, and then to transform it into the desired digital filter transfer function G(z). This approach has been widely used for many reasons:(a) Analog approximation techniques are highly advanced.(b) They usually yield closed-form solutions.(c) Extensive tables are available for analog filter design.(d) Many applications require the digital simulation of analog filters.In the sequel, we denote an analog transfer function as)()()(s D s P s H a a a =, Where the subscript "a" specifically indicates the analog domain. The digital transfer function derived form H a (s) is denoted by)()()(z D z P z G = The basic idea behind the conversion of an analog prototype transfer function H a (s) into a digital IIR transfer function G(z) is to apply a mapping from the s-domain to the z-domain so that the essential properties of the analog frequency response are preserved. The implies that the mapping function should be such that(a) The imaginary(j Ω) axis in the s-plane be mapped onto the circle of the z-plane.(b) A stable analog transfer function be transformed into a stable digital transfer function.To this end,the most widely used transformation is the bilinear transformation described in Section 9.2.Unlike IIR digital filter design,the FIR filter design does not have any connection with the design of analog filters. The design of FIR filter design does not have anyconnection with the design of analog filters. The design of FIR filters is therefore based on a direct approximation of the specified magnitude response,with the often added requirement that the phase response be linear. As pointed out in Eq.(7.10), a causal FIR transfer function H(z) of length N+1 is a polynomial in z -1 of degree N. The corresponding frequency response is given by∑=-=N n n j j en h e H 0][)(ωω.It has been shown in Section 3.2.1 that any finite duration sequence x[n] of length N+1 is completely characterized by N+1 samples of its discrete-time Fourier transfer X(ωj e ). As a result, the design of an FIR filter of length N+1 may be accomplished by finding either the impulse response sequence {h[n]} or N+1 samples of its frequency response )H(e j ω. Also, to ensure a linear-phase design, the condition of Eq.(7.11) must be satisfied. Two direct approaches to the design of FIR filters are the windowed Fourier series approach and the frequency sampling approach. We describe the former approach in Section 7.6. The second approach is treated in Problem 7.6. In Section 7.7 we outline computer-based digital filter design methods.作者:Sanjit K.Mitra国籍:USA出处:Digital Signal Processing -A Computer-Based Approach 3eIIR数字滤波器的设计在一个数字滤波器发展的重要步骤是可实现的传递函数G(z)的接近给定的频率响应规格。

DSP滤波器中英文对照外文翻译文献

中英文对照外文翻译文献(文档含英文原文和中文翻译)译文:GA算法优化IIR滤波器的设计摘要本文提出了运用遗传算法(GA)来优化无限脉冲响应数字滤波器(IIR)的设计。

IIR滤波器本质上是一个递归响应的数字滤波器。

由于IIR 数字滤波器的表面误差通常是非线性的和多峰的,而全局优化技术需要避免局部最小值。

本文提出了启发式方式来设计IIR滤波器。

GA是组合优化问题中一种功能强大的全局优化算法,该论文发现IIR数字滤波器的最佳系数可以通过GA 优化。

该设计提出低通和高通IIR数字滤波器的设计,以提供过渡频带的估计值。

结果发现,所计算出的值比可用于过滤器的在MATLAB设计FDA工具更优化。

举个例子,采用的仿真结果表明在过渡带和均方误差(MSE)的改善。

零极点的位置也被提出来用来描述系统的的稳定性,以便将结果与模拟退火(SA)的方法相比较。

关键词:数字滤波器;无限冲激响应(IIR);遗传算法(GA);优化1.说明在过去的几十年中的数字信号处理(DSP)领域已经成长太重要的理论和技术。

在DSP中,有两个重要的类型系统。

第一类型的系统是执行信号滤波的时域,因此它被称为数字滤波器。

第二类型的系统提供的信号表示频域,被称为频谱分析仪。

数字滤波是DSP的最有力的工具之一。

数字滤波器能够性能规格,最好的同时也是极其困难的,而且不可能的是,先用模拟滤波器实现。

另外,数字滤波器的特性,可以很容易地在软件控制下发生变化。

数字滤波器被分类为有限持续时间脉冲响应(FIR)滤波器或无限持续时间脉冲响应(IIR)滤波器,这取决于该系统的脉冲响应的形式。

在FIR系统中,脉冲响应序列是有限的持续时间,即,它具有非零项的数量有限。

数字无限脉冲响应(IIR)滤波器通常可以提供比其等效有限脉冲响应(FIR)滤波器更好的性能和更少的计算成本,并已成为越来越感兴趣的目标。

但是,由于IIR滤波器的误差表面通常是非线性的,多式联运,传统的基于梯度的设计方法可以很容易地陷入错误的表面。

【最新推荐】基于DSP的IIR滤波器设计外文文献

学科分类号本科毕业设计题目(中文):基于DSP的IIR滤波器设计(英文):The Design of IIR Filter Basedon DSP Chip姓名学号院(系)专业、年级指导教师二〇年月目录摘要 (1)Abstract. (2)1 绪论 (2)1.1 认识数字信号处理和IIR数字滤波器 (3)1.2 数字滤波器的实现方法 (4)1.3 主要研究内容 (6)2 滤波器原理基础 (6)2.1 IIR数字滤波器的优缺点 (7)2.2 IIR数字滤波器的设计方法和原理 (9)2.2.1 脉冲响应不变法 (12)2.2.2 双线性变换法 (14)2.3 IIR滤波器的基本结构 (17)3 IIR滤波器的设计过程及DSP的实现 (21)3.1 IIR滤波器的设计过程 (21)3.2 DSP系统的设计流程 (22)3.3 IIR数字滤波器在DSP上的实现 (22)参考文献 (27)附录 (28)致谢 (31)外文文献译文......................................................................................... 1-3 外文文献原文基于DSP的IIR滤波器设计摘要:数字信号处理(Digital Signal Processing,DSP)是一门涉及许多学科而又广泛应用于众多领域的新兴学科。

早在20世纪60年代,数字信号处理(即信号的数字化及数字处理)理论已经被被提出,到20世纪70年代,DSP理论和算法基础才被人提出。

不久之后,1982年世界上第一枚DSP芯片诞生了。

这枚DSP芯片在当时运算速度很快,尤其是在编码解码和语音合成方面得到广泛应用。

随着科学技术的飞速发展,数字化硬件技术得到长足的发展,这就带动了数字信号处理的飞速发展,也使得它得到了很多的实际应用,由此奠定了DSP这一词的地位。

之后,DSP芯片的科研不断推陈出新,每一代的DSP芯片都向着使运算速度更快、精度更高的目标发展,应用于通信、语音、医疗、仪器仪表和家用电器等人类生产生活的各个领域。

digital-filter-design数字滤波器设计大学毕业论文英文文献翻译及原文

毕业设计(论文)外文文献翻译文献、资料中文题目:数字滤波器设计文献、资料英文题目:digital filter design文献、资料来源:文献、资料发表(出版)日期:院(部):专业:班级:姓名:学号:指导教师:翻译日期: 2017.02.14毕业设计(论文)外文文献翻译院系:电子与电气工程系年级专业:姓名:学号:附件:digital filter design外文文献:digital filter designAbstract:With the information age and the advent of the digital world, digital signal processing has become one of today's most important disciplines and door technology.Digital signal processing in communications, voice, images, automatic control, radar, military, aerospace, medical and household appliances, and many other fields widely applied. In the digital signal processing applications, the digital filter is important and has been widely applied.Keyword:SCM; Proteus, C language; Digital filter1、figures Unit on :Analog and digital filtersIn signal processing, the function of a filter is to remove unwanted parts of the signal, such as random noise, or to extract useful parts of the signal, such as the components lying within a certain frequency range.The following block diagram illustrates the basic idea.There are two main kinds of filter, analog and digital. They are quite different in their physical makeup and in how they work. An analog filter uses analog electronic circuits made up from components such as resistors, capacitors and op amps to produce the required filtering effect. Such filter circuits are widely used in such applications as noise reduction, video signal enhancement, graphic equalisers in hi-fi systems, and many other areas. There are well-established standard techniques for designing an analog filter circuit for a given requirement. At all stages, the signal being filtered is an electrical voltage or current which is the direct analogue of the physical quantity (e.g. a sound or video signal or transducer output) involved. A digital filter uses a digital processor to perform numerical calculations on sampled values of the signal. The processor may be a general-purpose computer such as a PC, or a specialised DSP (Digital Signal Processor) chip. The analog input signal must first be sampled and digitised using an ADC (analog to digital converter). The resulting binary numbers, representing successive sampled values of the input signal, are transferred to the processor, which carries out numerical calculations on them. These calculations typically involve multiplying the input values by constants and adding the products together. If necessary, the results of these calculations, which now represent sampled values of the filtered signal, are output through a DAC (digital to analog converter) to convert the signal back to analog form.Note that in a digital filter, the signal is represented by a sequence of numbers, rather than a voltage or current.The following diagram shows the basic setup of such a system.Unit refers to the input signals used to filter hardware or software. If the filter input, output signals are separated, they are bound to respond to the impact of the Unit is separated, such as digital filters filter definition. Digital filter function, which was to import sequences X transformation into export operations through a series Y.According to figures filter function 24-hour live response characteristics, digital filters can be divided into two, namely, unlimited long live long live the corresponding IIR filter and the limited response to FIR filters. IIR filters have the advantage of the digital filter design can use simulation results, and simulation filter design of a large number of tables may facilitate simple. It is the shortcomings of the nonlinear phase; Linear phase if required, will use the entire network phase-correction. Image processing and transmission of data collection is required with linear phase filters identity. And FIR linear phase digital filter to achieve, but an arbitrary margin characteristics. Impact from the digital filter response of the units can be divided into two broad categories : the impact of the limited response (FIR) filters, and unlimited number of shocks to (IIR) digital filters.FIR filters can be strictly linear phase, but because the system FIR filter function extremity fixed at the original point, it can only use the higher number of bands to achieve their high selectivity for the same filter design indicators FIR filter called band than a few high-IIR 5-10 times, the cost is higher, Signal delay is also larger. But if the same linear phase, IIR filters must be network-wide calibration phase, the same section also increase the number of filters and network complexity. FIR filters can be used to achieve non-Digui way, not in a limited precision of a shock, and into the homes and quantitative factors of uncertainty arising from the impact of errors than IIR filter small number, and FIR filter can be used FFT algorithms, the computational speed. But unlike IIR filter can filter through the simulation results, there is no ready-made formula FIR filter must use computer-aided design software (such as MATLAB) to calculate. So, a broader application of FIR filters, and IIR filters are not very strict requirements on occasions.Unit from sub-functions can be divided into the following four categories :(1)Low-filter (LPF);(2)high-filter (HPF);(3)belt-filter (BPF);(4)to prevent filter (BSF).The following chart dotted line for the ideals of the filter frequency characteristics :2、MATLAB introducedMATLAB is a matrix laboratory (Matrix Laboratory) is intended. In addition to an excellent value calculation capability, it also provides professional symbols terms, word processing, visualization modeling, simulation and real-time control functions. MATLAB as the world's top mathematical software applications, with a strong engineering computing, algorithms research, engineering drawings, applications development, data analysis and dynamic simulation, and other functions, in aerospace, mechanical manufacturing and construction fields playing an increasingly important role. And the C language function rich, the use of flexibility, high-efficiency goals procedures. High language both advantages as well as low level language features. Therefore, C language is the most widely used programming language. Although MATLAB is a complete, fully functional programming environment, but in some cases, data and procedures with the external environment of the world is very necessary and useful. Filter design using Matlab, could be adjusted with the design requirements and filter characteristics of the parameters, visual simple, greatly reducing the workload for the filter design optimization.In the electricity system protection and secondary computer control, many signal processing and analysis are based on are certain types Yeroskipou and the second harmonics of the system voltage and current signals (especially at D process), are mixed with a variety of complex components, the filter has been installed power system during the critical components. Current computer protection and the introduction of two digitalsignal processing software main filter. Digital filter design using traditional cumbersome formula, the need to change the parameters after recalculation, especially in high filters, filter design workload. Uses MATLAB signal processing boxes can achieve rapid and effective digital filter design and simulatioMATLAB is the basic unit of data matrix, with its directives Biaodashi mathematics, engineering, commonly used form is very similar, it is used to solve a problem than in MATLAB C, Fortran and other languages End precision much the same thing. The popular MATLAB 5.3/Simulink3.0 including hundreds of internal function with the main pack and 30 types of tool kits (Toolbox). kits can be divided into functional tool kits and disciplines toolkit. MA TLAB tool kit used to expand the functional symbols terms, visualization simulation modelling, word processing and real-time control functions. professional disciplines toolkit is a stronger tool kits, tool kits control, signal processing tool kit, tool kits, etc. belonging to such communicationsMATLAB users to open widely welcomed. In addition to the internal function, all the packages MATLAB tool kits are readable document and the document could be amended, modified or users through Yuanchengxu the construction of new procedures to prepare themselves for kits.3、Digital filter designDigital filter design of the basic requirementsDigital filter design must go through three steps :(1) Identification of indicators : In the design of a filter, there must be some indicators. These indicators should be determined on the basis of the application. In many practical applications, digital filters are often used to achieve the frequency operation. Therefore, indicators in the form of general jurisdiction given frequency range and phase response. Margins key indicators given in two ways. The first is absolute indicators. It provides a function to respond to the demands of the general application of FIR filter design. The second indicator is the relative indicators. Its value in the form of answers to decibels. In engineering practice, the most popular of such indicators. For phase response indicators forms, usually in the hope that the system with a linear phase frequency bands human. Using linear phase filter design with the following response to the indicators strengths:①it only contains a few algorithms, no plural operations;②there is delay distortion, onlya fixed amount of delay; ③the filter length N (number of bands for N-1), the volume calculation for N/2 magnitude.(2) Model approach : Once identified indicators can use a previous study of the basic principles and relationships, a filter model to be closer to the target system.(3) Achieved : the results of the above two filters, usually by differential equations, system function or pulse response to describe. According to this description of hardware or software used to achieve it.4、Introduced FPGAProgrammable logic device is a generic logic can use a variety of chips, which is to achieve ASIC ASIC (Application Specific Integrated Circuit) semi-customized device, Its emergence and development of electronic systems designers use CAD tools to designtheir own laboratory in the ASIC device. Especially FPGA (Field Programmable Gate Array) generated and development, as a microprocessor, memory, the figures for electronic system design and set a new industry standard (that is based on standard product sales catalogue in the market to buy). Is a digital system for microprocessors, memories, FPGA or three standard building blocks constitute their integration direction.Digital circuit design using FPGA devices, can not only simplify the design process and can reduce the size and cost of the entire system, increasing system reliability. They do not need to spend the traditional sense a lot of time and effort required to create integrated circuits, to avoid the investment risk and become the fastest-growing industries of electronic devices group. Digital circuit design system FPGA devices using the following main advantages(1) Design flexibleUse FPGA devices may not in the standard series device logic functional limitations. And changes in system design and the use of logic in any one stage of the process, and only through the use of re-programming the FPGA device can be completed, the system design provides for great flexibility.(2)Increased functional densityFunctional density in a given space refers to the number of functional integration logic. Programmable logic chip components doors several high, a FPGA can replace several films, film scores or even hundreds of small-scale digital IC chip illustrated in the film. FPGA devices using the chip to use digital systems in small numbers, thus reducing the number of chips used to reduce the number of printed size and printed, and will ultimately lead to a reduction in the overall size of the system.(3)Improve reliabilityPrinting plates and reduce the number of chips, not only can reduce system size, but it greatly enhanced system reliability. A higher degree of integration than systems in many low-standard integration components for the design of the same system, with much higher reliability. FPGA device used to reduce the number of chips required to achieve the system in the number printed on the cord and joints are reduced, the reliability of the system can be mproved.(4)Shortening the design cycleAs FPGA devices and the programmable flexibility, use it to design a system for longer than traditional methods greatly shortened. FPGA device master degrees high, use printed circuit layout wiring simple. At the same time, success in the prototype design, the development of advanced tools, a high degree of automation, their logic is very simple changes quickly. Therefore, the use of FPGA devices can significantly shorten the design cycle system, and speed up the pace of product into the market, improving product competitiveness.(5)Work fastFPGA/CPLD devices work fast, generally can reach several original Hertz, far larger than the DSP device. At the same time, the use of FPGA devices, the system needed to achieve circuit classes and small, and thus the pace of work of the entire system will be improved.(6)Increased system performance confidentialityMany FPGA devices have encryption functions in the system widely used FPGA devices can effectively prevent illegal copying products were others(7)To reduce costsFPGA device used to achieve digital system design, if only device itself into the price, sometimes you would not know it advantages, but there are many factors affecting the cost of the system, taken together, the cost advantages of using FPGA is obvious. First, the use of FPGA devices designed to facilitate change, shorten design cycles, reduce development costs for system development; Secondly, the size and FPGA devices allow automation needs plug-ins, reducing the manufacturing system to lower costs; Again, the use of FPGA devices can enhance system reliability, reduced maintenance workload, thereby lowering the cost of maintenance services for the system. In short, the use of FPGA devices for system design to save costs.FPGA design principles :FPGA design an important guiding principles : the balance and size and speed of exchange, the principles behind the design of the filter expression of a large number of certification.Here, "area" means a design exertion FPGA/CPLD logic resources of the FPGA can be used to the typical consumption (FF) and the search table (IUT) to measure more general measure can be used to design logic equivalence occupied by the door is measured. "pace" means stability operations in the chip design can achieve the highest frequency, the frequency of the time series design situation, and design to meet the clock cycle -- PADto pad, Clock Setup Time, Clock Hold Beijing, Clock-to-Output Delay, and other characteristics of many time series closely related. Area (area) and speed (speed) runs through the two targets FPGA design always is the ultimate design quality evaluation criteria. On the size and speed of the two basic concepts : balance of size and speed and size and speed of swap.One pair of size and speed is the unity of opposites contradictions body. Requirements for the design of a design while the smallest, highest frequency of operation is unrealistic. More scientific goal should be to meet the design requirements of the design time series (includes requirements for the design frequency) premise, the smallest chip area occupied. Or in the specified area, the design time series cushion greater frequency run higher. This fully embodies the goals of both size and speed balanced thinking. On the size and speed requirements should not be simply interpreted as raising the level and design engineers perfect sexual pursuit, and should recognize that they are products and the quality and cost of direct relevance. If time series cushion larger design, running relatively high frequency, that the design Jianzhuangxing stronger, more quality assurance system as a whole; On the other hand, the smaller size of consumption design is meant to achieve in chip unit more functional modules, the chip needs fewer, the entire system has been significantly reduced cost. As a contradiction of the two components, the size and speed is not the same status. In contrast, meet the timetables and work is more important for some frequency when both conflicts, the use of priority guidelines.Area and the exchange rate is an important FPGA design ideas. Theoretically, if a design time series cushion larger, can run much higher than the frequency designrequirements, then we can through the use of functional modules to reduce the consumption of the entire chip design area, which is used for space savings advantages of speed; Conversely, if the design of a time series demanding, less than ordinary methods of design frequency then generally flow through the string and data conversion, parallel reproduction of operational module, designed to take on the whole "string and conversion" and operate in the export module to chip in the data "and string conversion" from the macro point of view the whole chip meets the requirements of processing speed, which is equivalent to the area of reproduction - rate increase.For example. Assuming that the digital signal processing system is 350Mb/s input data flow rate, and in FPGA design, data processing modules for maximum processing speed of150Mb/s, because the data throughput processing module failed to meet requirements, it is impossible to achieve directly in the FPGA. Such circumstances, they should use "area-velocity" thinking, at least three processing modules from the first data sets will be imported and converted, and then use these three modules parallel processing of data distribution, then the results "and string conversion," we have complete data rate requirements. We look at both ends of the processing modules, data rate is 350Mb/s, and in view of the internal FPGA, each sub-module handles the data rate is 150Mb/s, in fact, all the data throughput is dependent on three security modules parallel processing subsidiary completed, that is used by more chip area achieve high-speed processing through "the area of reproduction for processing speed enhancement" and achieved design.FPGA is the English abbreviation Field of Programmable Gate Array for the site programmable gate array, which is in Pal, Gal, Epld, programmable device basis to further develop the product. It is as ASIC (ASIC) in the field of a semi-customized circuit and the emergence of both a customized solution to the shortage circuit, but overcome the original programmable devices doors circuit few limited shortcomings.FPGA logic module array adopted home (Logic Cell Array), a new concept of internal logic modules may include CLB (Configurable Logic Block), export import module IOB (Input Output Block) and internal links (Interconnect) 3. FPGA basic features are :(1)Using FPGA ASIC design ASIC using FPGA circuits, the chip can be used,while users do not need to vote films production.(2)FPGA do other customized or semi-customized ASIC circuits throughout the Chinese specimen films.(3)FPGA internal capability and rich I/O Yinjue.(4)FPGA is the ASIC design cycle, the shortest circuit, the lowest development costs, risks among the smallest device(5)FPGA using high-speed Chmos crafts, low consumption, with CMOS, TTL low-power compatibleIt can be said that the FPGA chip is for small-scale systems to improve system integration, reliability one of the bestCurrently FPGA many varieties, the Revenue software series, TI companies TPC series, the fiex ALTERA company seriesFPGA is stored in films from the internal RAM procedures for the establishment ofthe state of its work, therefore, need to programmed the internal Ram. Depending on the different configuration, users can use a different programming methodsPlus electricity, FPGA, EPROM chips will be read into the film, programming RAM 中data, configuration is completed, FPGA into working order. Diaodian, FPGA resume into white films, the internal logic of relations disappear, FPGA to repeated use. FPGA's programming is dedicated FPGA programming tool, using generic EPROM, prom programming device can. When the need to modify functional FPGA, EPROM can only change is. Thus, with a FPGA, different programming data to produce different circuit functions. Therefore, the use of FPGA very flexible.There are a variety of FPGA model : the main model for a parallel FPGA plus a EPROM manner; From the model can support a number of films FPGA; serial prom programming model could be used serial prom FPGA programming FPGA; The external model can be engineered as microprocessors from its programming microprocessors.Verilog HDL is a hardware description language for the algorithm level, doors at the level of abstract level to switch-level digital system design modelling. Modelling of the target figure by the complexity of the system can be something simple doors and integrity of electronic digital systems. Digital system to the levels described, and in the same manner described in Hin-time series modelling.Verilog HDL language with the following description of capacity : design behaviour characteristics, design data flow characteristics, composition and structure designed to control and contain the transmission and waveform design a certification mechanism. All this with the use of a modelling language. In addition, Verilog HDL language programming language interface provided by the interface in simulation, design certification from the external design of the visit, including specific simulation control and operation.Verilog HDL language grammar is not only a definition, but the definition of each grammar structure are clear simulation, simulation exercises. Therefore, the use of such language to use Verilog simulation models prepared by a certification. From the C programming language, the language inherited multiple operating sites and structures. Verilog HDL provides modelling capacity expansion, many of the initial expansion would be difficult to understand. However, the core subsets of Verilog HDL language very easy to learn and use, which is sufficient for most modelling applications. Of course, the integrity of the hardware description language is the most complex chips from the integrity of the electronic systems described.HistoryVerilog HDL language initially in 1983 by Gateway Design Automation companies for product development simulator hardware modelling language. Then it is only a dedicated language. Since their simulation, simulation devices widely used products, Verilog HDL as a user-friendly and practical language for many designers gradually accepted. In an effort to increase the popularity of the language activities, Verilog HDL language in 1990 was a public area. Open Verilog International (OVI) is to promote the development of Verilog international organizations. 1992, decided to promote OVI OVI standards as IEEE Verilog standards. The effort will ultimately succeed, a IEEE 1995 Verilog language standard, known as IEEE Std 1364-1995. Integrity standardsin Verilog hardware description language reference manual contains a detailed description.Main capacityListed below are the main Verilog hardware description language ability*Basic logic gate, and, for example, or have embedded in the language and nand* Users of the original definition of the term (UDP), the flexibility. Users can be defined in the original language combinations logic original language, the original language of logic could also be time series* Switches class infrastructure models, such as the nmos and pmos also be embedded in the language* Hin-language structure designated for the cost of printing the design and trails Shi Shi and design time series checks.* Available three different ways to design or mixed mode modelling. These methods include : acts described ways - use process of structural modelling; Data flow approach - use of a modelling approach Fuzhi expression; Structured way - using examples of words to describe modular doors and modelling.* Verilog HDL has two types of data : data types and sequence data line network types. Line network types that the physical links between components and sequence types that abstract data storage components.* To describe the level design, the structure can be used to describe any level module example* Design size can be arbitrary; Language is design size (size) impose any restrictions* And the machine can read Verilog language, it may as EDA tools and languages of the world between the designers* Verilog HDL language to describe capacity through the use of programming language interface (PLI) mechanism further expansion. PLI is to allow external functions of the visit Verilog module information, allowing designers and simulator world Licheng assembly* Design to be described at a number of levels, from the switch level, doors level, register transfer level (RTL) to the algorithm level, including the level of process and content* To use embedded switching level of the original language in class switch design integrity modelling * Same language can be used to generate simulated incentive and certification by the designated testing conditions, such as the value of imports of the designated*Verilog HDL simulation to monitor the implementation of certification, the certification process of implementing the simulation can be designed to monitor and demonstrate value. These values can be used to compare with the expectations that are not matched in the case of print news reports.* Acts described in the class, not only in the RTL level Verilog HDL design description, and to describe their level architecture design algorithm level behavioural description* Examples can use doors and modular structure of language in a class structure described* Verilog HDL mixed mode modelling capabilities in the design of a different design in each module can level modelling* Verilog HDL has built-in logic function, such as*Structure of high-level programming languages, such as conditions of expression, and the cycle of expression language, language can be used* To it and can display regular modelling * Provide a powerful document literacy* Language in the specific circumstances of non-certainty that in the simulator, different models can produce different results; For example, describing events in the standard sequence of events is not defined.5、In troduction of DSPToday, DSP is w idely used in the modern techno logy and it has been the key part of many p roducts and p layed more and mo re impo rtant ro le in our daily life.Recent ly, Northw estern Po lytechnica lUniversity Aviation Microelect ronic Center has comp leted the design of digital signal signal p rocesso r co re NDSP25, w h ich is aim ing at TM S320C25 digital signal p rocesso r of Texas Inst rument TM S320 series. By using top 2dow n design flow , NDSP25 is compat ible w ith inst ruct ion and interface t im ing of TM S320C25.Digital signal processors (DSP) is a fit for real-time digital signal processing for high-speed dedicated processors, the main variety used for real-time digital signal processing to achieve rapid algorithms. In today's digital age background, the DSP has become the communications, computer, and consumer electronics products, and other fields based device.Digital signal processors and digital signal processing is inseparably, we usually say "DSP" can also mean the digital signal processing (Digital Signal Processing), is that in this digital signal processors Lane. Digital signal processing is a cover many disciplines applied to many areas and disciplines, refers to the use of computers or specialized processing equipment, the signals in digital form for the collection, conversion, recovery, valuation, enhancement, compression, identification, processing, the signals are compliant form. Digital signal processors for digital signal processing devices, it is accompanied by a digital signal processing to produce. DSP development process is broadly divided into three phases : the 20th century to the 1970s theory that the 1980s and 1990s for the development of products. Before the emergence of the digital signal processing in the DSP can only rely on microprocessors (MPU) to complete. However, the advantage of lower high-speed real-time processing can not meet the requirements. Therefore, until the 1970s, a talent made based DSP theory and algorithms. With LSI technology development in 1982 was the first recipient of the world gave birth to the DSP chip. Years later, the second generation based on CMOS工艺DSP chips have emerged. The late 1980s, the advent of the third generation of DSP chips. DSP is the fastest-growing 1990s, there have been four successive five-generation and the generation DSP devices. After 20 years of development, the application of DSP products has been extended to people's learning, work and all aspects of life and gradually become electronics products determinants.REFERENCES1.Chan, D.S.K., Rabiner L.R.: Analysis of Quantization Errors in the Direct Form for Finite Impulse。

IIR数字滤波器中英文对照外文翻译文献

(文档含英文原文和中文翻译)中英文资料对照外文翻译IIR Digital Filter DesignAn important step in the development of a digital filter is the determination of a realizable transfer function G(z) approximating the given frequency response specifications. If an IIR filter is desired,it is also necessary to ensure that G(z) is stable. The process of deriving the transfer function G(z) is called digital filter design. After G(z) has been obtained, the next step is to realize it in the form of a suitable filter structure. In chapter 8,we outlined a variety of basic structures for the realization of FIR and IIRtransfer functions. In this chapter,we consider the IIR digital filter design problem. The design of FIR digital filters is treated in chapter 10.First we review some of the issues associated with the filter design problem. A widely used approach to IIR filter design based on the conversion of a prototype analog transfer function to a digital transfer function is discussed next. Typical design examples are included to illustrate this approach. We then consider the transformation of one type of IIR filter transfer function into another type, which is achieved by replacing the complex variable z by a function of z. Four commonly used transformations are summarized. Finally we consider the computer-aided design of IIR digital filter. To this end, we restrict our discussion to the use of matlab in determining the transfer functions.9.1 preliminary considerationsThere are two major issues that need to be answered before one can develop the digital transfer function G(z). The first and foremost issue is the development of a reasonable filter frequency response specification from the requirements of the overall system in which the digital filter is to be employed. The second issue is to determine whether an FIR or IIR digital filter is to be designed. In the section ,we examine these two issues first . Next we review the basic analytical approach to the design of IIR digital filters and then consider the determination of the filter order that meets the prescribed specifications. We also discuss appropriate scaling of the transfer function.9.1.1 Digital Filter SpecificationsAs in the case of the analog filter,either the magnitude and/or the phase(delay) response is specified for the design of a digital filter for most applications. In some situations, the unit sample response or step response may be specified. In most practical applications, the problem of interest is the development of a realizable approximation to a given magnitude response specification. As indicated in section 4.6.3, the phase response of the designed filter can be corrected by cascading it with an allpass section. The designof allpass phase equalizers has received a fair amount of attention in the last few years. We restrict our attention in this chapter to the magnitude approximation problem only. We pointed out in section 4.4.1 that there are four basic types of filters,whose magnitude responses are shown in Figure 4.10. Since the impulse response corresponding to each of these is noncausal and of infinite length, these ideal filters are not realizable. One way of developing a realizable approximation to these filter would be to truncate the impulse response as indicated in Eq.(4.72) for a lowpass filter. The magnitude response of the FIR lowpass filter obtained by truncating the impulse response of the ideal lowpass filter does not have a sharp transition from passband to stopband but, rather, exhibits a gradual "roll-off."Thus, as in the case of the analog filter design problem outlined in section 5.4.1, the magnitude response specifications of a digital filter in the passband and in the stopband are given with some acceptable tolerances. In addition, a transition band is specified between the passband and the stopband to permit the magnitude to drop off smoothly. For example, the magnitude )(ωj e G of a lowpass filter may be given as shown in Figure7.1. As indicated in the figure, in the passband defined by 0p ωω≤≤, we require that the magnitude approximates unity with an error of p δ±,i.e.,p p j p for e G ωωδδω≤+≤≤-,1)(1.In the stopband, defined byπωω≤≤s ,we require that the magnitude approximateszero with an error of i s ,δ.e., ,)(s j e G δω≤ for πωω≤≤s .The frequencies p ω and s ω are , respectively, called the passband edge frequency and the stopband edge frequency. The limits of the tolerances in the passband and stopband,p δ and s δ, are usually called the peak ripple values. Note that the frequency response )(ωj e G of a digital filter is a periodic function of ω,and the magnitude response of a real-coefficient digital filter is an even function ofω. As a result, the digital filter specifications are given only for the range πω≤≤0.Digital filter specifications are often given in terms of the loss function,)(log 20)(10ωωζj e G -=, in dB. Here the peak passband ripple p α and theminimum stopband attenuation s α are given in dB,i.e., the loss specifications of a digital filter are given bydB p p )1(log 2010δα--=,dB s s )(log 2010δα-=. 9.1 Preliminary ConsiderationsAs in the case of an analog lowpass filter, the specifications for a digital lowpass filter may alternatively be given in terms of its magnitude response, as in Figure 7.2. Here the maximum value of the magnitude in the passband is assumed to be unity, and the maximum passband deviation, denoted as 1/21ε+,is given by the minimum value of the magnitude in the passband. The maximum stopband magnitude is denoted by 1/A.For the normalized specification, the maximum value of the gain function or the minimum value of the loss function is therefore 0 dB. The quantitymax α given bydB )1(log 20210max εα+= Is called the maximum passband attenuation. Forp δ<<1, as is typically the case, it can be shown thatp p αδα2)21(log 2010max ≅--≅The passband and stopband edge frequencies, in most applications, are specified in Hz, along with the sampling rate of the digital filter. Since all filter design techniques are developed in terms of normalized angular frequencies p ω and s ω,the sepcified critical frequencies need to be normalized before a specific filter design algorithm can be applied. Let T F denote the sampling frequency in Hz, and F P and F s denote, respectively,the passband and stopband edge frequencies in Hz. Then the normalized angular edge frequencies in radians are given byT F F F F p Tp T p p ππω22==Ω=T F F F F s Ts T s s ππω22==Ω= 9.1.2 Selection of the Filter Type The second issue of interest is the selection of the digital filter type,i.e.,whether an IIR or an FIR digital filter is to be employed. The objective of digital filter design is to develop a causal transfer function H(z) meeting the frequency response specifications. ForIIR digital filter design, the IIR transfer function is a real rational function of 1-z .H(z)=NMdNz z d z d d pMz z p z p p ------++++++++......2211022110 Moreover, H(z) must be a stable transfer function, and for reduced computational complexity, it must be of lowest order N. On the other hand, for FIR filter design, the FIRtransfer function is a polynomial in 1-z :∑=-=N n n zn h z H 0][)(For reduced computational complexity, the degree N of H(z) must be as small as possible. In addition, if a linear phase is desired, then the FIR filter coefficients must satisfy the constraint:][][N n h n h -±=T here are several advantages in using an FIR filter, since it can be designed withexact linear phase and the filter structure is always stable with quantized filter coefficients. However, in most cases, the order N FIR of an FIR filter is considerably higher than the order N IIR of an equivalent IIR filter meeting the same magnitude specifications. In general, the implementation of the FIR filter requires approximately N FIR multiplications per output sample, whereas the IIR filter requires 2N IIR+1 multiplications per output sample. In the former case, if the FIR filter is designed with a linear phase, then the number of multiplications per output sample reduces to approximately (N FIR+1)/2. Likewise, most IIR filter designs result in transfer functions with zeros on the unit circle,N with all of the zeros on the unit and the cascade realization of an IIR filter of orderIIRN+3)/2] multiplications per output sample. It has been shown that circle requires [(3IIRfor most practical filter specifications, the ratio N FIR/N IIR is typically of the order of tens or more and, as a result, the IIR filter usually is computationally more efficient[Rab75]. However ,if the group delay of the IIR filter is equalized by cascading it with an allpass equalizer, then the savings in computation may no longer be that significant [Rab75]. In many applications, the linearity of the phase response of the digital filter is not an issue,making the IIR filter preferable because of the lower computational requirements.9.1.3 Basic Approaches to Digital Filter DesignIn the case of IIR filter design, the most common practice is to convert the digital filter specifications into analog lowpass prototype filter specifications, and then to transform it into the desired digital filter transfer function G(z). This approach has been widely used for many reasons:(a) Analog approximation techniques are highly advanced.(b) They usually yield closed-form solutions.(c) Extensive tables are available for analog filter design.(d) Many applications require the digital simulation of analog filters.In the sequel, we denote an analog transfer function as)()()(s D s P s H a a a =, Where the subscript "a" specifically indicates the analog domain. The digital transfer function derived form H a (s) is denoted by)()()(z D z P z G = The basic idea behind the conversion of an analog prototype transfer function H a (s) into a digital IIR transfer function G(z) is to apply a mapping from the s-domain to the z-domain so that the essential properties of the analog frequency response are preserved. The implies that the mapping function should be such that(a) The imaginary(j Ω) axis in the s-plane be mapped onto the circle of the z-plane.(b) A stable analog transfer function be transformed into a stable digital transfer function.To this end,the most widely used transformation is the bilinear transformation described in Section 9.2.Unlike IIR digital filter design,the FIR filter design does not have any connection with the design of analog filters. The design of FIR filter design does not have any connection with the design of analog filters. The design of FIR filters is therefore based on a direct approximation of the specified magnitude response,with the often added requirement that the phase response be linear. As pointed out in Eq.(7.10), a causal FIR transfer function H(z) of length N+1 is a polynomial in z -1 of degree N. The corresponding frequency response is given by∑=-=N n n j j en h e H 0][)(ωω.It has been shown in Section 3.2.1 that any finite duration sequence x[n] of length N+1 is completely characterized by N+1 samples of its discrete-time Fourier transfer X(ωj e ). As a result, the design of an FIR filter of length N+1 may be accomplished by finding either the impulse response sequence {h[n]} or N+1 samples of its frequency response )H(e j ω. Also,to ensure a linear-phase design, the condition of Eq.(7.11) must be satisfied. Two direct approaches to the design of FIR filters are the windowed Fourier series approach and the frequency sampling approach. We describe the former approach in Section 7.6. The second approach is treated in Problem 7.6. In Section 7.7 we outline computer-based digital filter design methods.作者:Sanjit K.Mitra国籍:USA出处:Digital Signal Processing -A Computer-Based Approach 3eIIR数字滤波器的设计在一个数字滤波器发展的重要步骤是可实现的传递函数G(z)的接近给定的频率响应规格。

毕业设计(论文)-iir数字滤波器的设计[管理资料]

![毕业设计(论文)-iir数字滤波器的设计[管理资料]](https://img.taocdn.com/s3/m/6a12f62a50e2524de5187ef9.png)

摘要在本文中,我们分别研究了在MATLAB环境下IIR数字滤波器的典型设计和完全设计等方法。

典型设计是先按一定规则将给出的数字滤波器的技术指标转换成模拟低通滤波器的技术指标,据此产生模拟滤波器原型,然后把模拟低通滤波器原型转换成模拟低通、高通、带通、带阻滤波器,最后再把模拟滤波器转换成数字滤波器。

完全设计方法中我们利用函数直接设计出低通、高通、带通和带阻滤波器,并分别用巴特沃斯(Butterworth )滤波器、切比雪夫( Chebyshev )滤波器、椭圆(Cauer )滤波器来实现,并比较了各自的频率响应曲线。

在FIR滤波器的设计中,我们用切比雪夫窗和海明窗设计的带通滤波器的频率响应进行对照,结果表面用海明窗设计的滤波器的频率特性几乎在任何频带上都比切比雪夫窗设计的滤波器的频率特性好,只是海明窗设计的滤波器下降斜度较小。

本文利用不同的滤波器研究了MATLAB环境下的图像处理技术。

对一张无锡马山园林的风景照片进行的二种修正,取得了不同的效果。

先对原图进行线性变换增加了对比度和亮度对这张图像,图像效果有了一定的改善。

后来我们用非锐化滤波器对修正后的图像再进行了处理,对图像的过渡失真进行了补偿。

本文还对一幅加噪声婚纱照片的去噪效果进行了研究。

比较去噪效果证明,用小波变换的方法进行去噪,图像处理效果更佳。

关键词:数字滤波器;图像处理;小波变换作者:王海楠指导教师:王婷婷AbstractIn this thesis, the typical and complete designs under MATLAB are studied.The typical design gets the technical parameters from digital filters that should be designed, and then transformed into the analog parameters of a low-pass analog filter prototype. The prototype is converted into the analog low-pass, high-pass, band-pass and the band-stop filters respectively, which are transformed into the digital ones.The complete design uses the given functions and releases the low-pass,high-pass,band-pass and the band-stop filters directly. Butterworth, Chebyshev and Caoer filters are used for the implementations.In the FIR filter designs, Chebyshev and Hamming windows are used for abmd-pass filter. Their frequency responses are compared. The advantage of Hamming window is shown on all bands.Finally, the image processing functions using filters under MATLAB are photo (Wuxi Garden) is modified with two different processes and the different effects can be seen. The linear transformation improved the contrast and brightness of the photo, while the un-sharpening filter compensated the transitions.Another photo is modified with the wavelet transformation, which shows the better effects on reducing noises.Keywords: digital filter; image processing; wavelet transformationAuthor: Wang HainanDirected by Wang Tingting第1章绪论数字滤波在通信、图像编码、语音编码、雷达等许多领域中有着十分广泛的应用。

本科毕设滤波器方面的中英文翻译

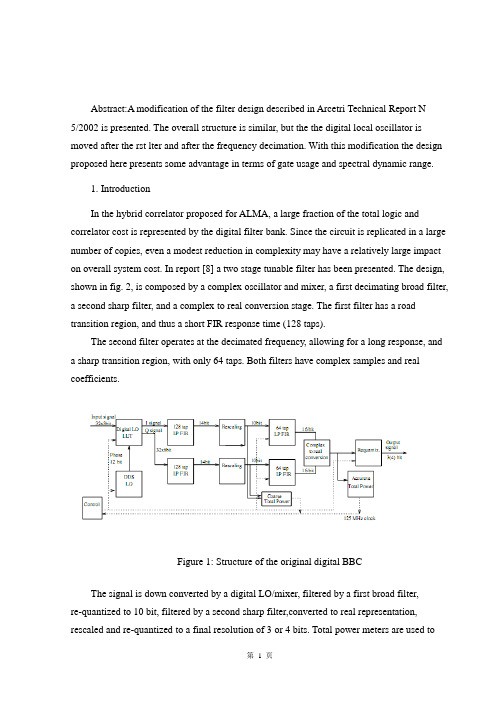

Abstract:A modification of the filter design described in Arcetri Technical Report N5/2002 is presented. The overall structure is similar, but the the digital local oscillator is moved after the rst lter and after the frequency decimation. With this modification the design proposed here presents some advantage in terms of gate usage and spectral dynamic range.1. IntroductionIn the hybrid correlator proposed for ALMA, a large fraction of the total logic and correlator cost is represented by the digital filter bank. Since the circuit is replicated in a large number of copies, even a modest reduction in complexity may have a relatively large impact on overall system cost. In report [8] a two stage tunable filter has been presented. The design, shown in fig. 2, is composed by a complex oscillator and mixer, a first decimating broad filter, a second sharp filter, and a complex to real conversion stage. The first filter has a road transition region, and thus a short FIR response time (128 taps).The second filter operates at the decimated frequency, allowing for a long response, and a sharp transition region, with only 64 taps. Both filters have complex samples and real coefficients.Figure 1: Structure of the original digital BBCThe signal is down converted by a digital LO/mixer, filtered by a first broad filter,re-quantized to 10 bit, filtered by a second sharp filter,converted to real representation, rescaled and re-quantized to a final resolution of 3 or 4 bits. Total power meters are used tomonitor signal level.A modified architecture (fig. 2), with almost identical performance and response, may be obtained moving the LO/mixer after the first filter. The first filter has a band pass corresponding to the desired portion of the input spectrum (without restrictions due to decimation), and is obtained from a the low pass prototype used in the previous approach, translated by a frequency equal to the LO setting.Figure 2: Structure of the modified digital BBCThe signal is first filtered by the broad filter, decimated, and then frequency converted by a full complex mixer. The second filter and output section is identical to the previous case. The filter is thus depending on the sub band position, and its coefficients must be reloaded every time the tuning change. To avoid aliasing, it must discriminate between positive and negative frequencies, It has therefore real input, complex (hermitian) tap coefficients, and complex output. The mixer/LO is fully complex, with 4 multipliers and 2 adders. The second filter and complex-to-real conversion stage is identical to the previous design.The main advantage of this design is that the mixer operates at the decimated frequency. Since a time multiplexed mixer is composed of 32 identical multipliers, even considering for the increased complexity in the multi-bit complex multiplier this results in a drastic simplification. It is possible to use a much better multiplier,thus increasing the global quantization efficiency (although by a small value, about 0.5%) and spurious free dynamic range.Another advantage is that the first filter operates on the 3-bit input data representation, instead of the 6-bit mixer output. This reduces the total filter size by a considerable amount (30-40%).A further advantage is that the mixer does not see any DC component that can beproduced by an offset in the sampler thresholds, as this is effectively filtered by the first filter. This DC component is equivalent to a strong monochromatic line, and may produce undesired spurs as it beats with the LO harmonics.2 Theory of operationFigure 3: Spectral processing exampleFor readability, a x8 multiplexing factor has been assumed, instead of x32. From top: (a) Input real signal, divided into 10 sub bands; (b) Undecimated and (c) decimated broad filter output; (d) Mixer output; (e) Sharp filter output.Signal processing for an hypothetical 1:8 decimated signal is shown in fig. 3 The real input, divided in 10 overlapped sub-bands, is shown in (a). The broad filter selects sub-band 6, with guard bands from sub-bands 5 and 7 (b). After decimation, (c) the band of interest occupies half the complex decimated bandwidth, with sub-bands 5 and 7 aliased in the remaining half. In the particular case, the band of interest folds from positive back to negative frequencies. After complex mixing the band of interest is centered on frequency zero (d), and the unwanted sub-bands are rejected by the sharp filter (e).The processing of a real simulated signal, with the desired 1:32 decimation factor, is shown in fig. 4 and 5.The signal is the same used in the previous report. The complex spectrum of the (real) input signal is shown in fig. 4a. The signal is composed of white noise, a strong out-of-band tone (-20dB), and a weaker (-30dB) in-band tone. The simulated signal is 2.5 ms long.After filtering, the signal is shown in fig. 4b. Only one side of the complex spectrum is preserved, thus avoiding undesired aliasing in the decimation operation.After decimation, the signal has the spectrum shown in fig. 4c. Even if the spectrum folds from positive to negative frequencies, no undesired alias of the strong input line can be seen.Figure 4: Spectral processing of a simulated signalFrom top: (a) Input real signal; (b) Undecimated and (c) decimated broad filter output Graphs have a logarithmic (dB) scale.The complex mixer rotates the filtered spectrum in order to present the desired passband to the sharp filter centered on frequency zero (fig. 5a). The low pass sharp filter then selects the desired passband and removes the undesired passbands (5b). This signal is then converted to real (5c), and re-quantized for correlation. The filter real output is exactly equal to that of the filter described in the previous report (apart from quantization effects).2.1 Broad band filterThe filter is a complex passband (real samples, complex coefficients) derived by the low pass prototype used in the previous design. The prototype has a bandpass equal to 1/64 the input bandwidth, and a guard region twice as large. After decimation, both the complexresponse and the two guard bands have a total width of 1/32 the initial band, or 1/2 the decimated complex band. The two guard bands fold in the same region of thedecimated band.The prototype is shifted by the desired center frequency. For 34 sub bands, the rotation for channel i(i =0,33) is (i-05)34*2 GHz, but arbitrary shift is possible. Thus, filter tuning is accomplished by calculation of a new set of coe?cients (no filter optimization is necessary) and reloading of the coe?cient memory.The real part of the filter is symmetric, while the complex one is antisymmetric. In both cases, filter structure may exploit this symmetry to reduce the number of multiplications. Filter conceptual schematic for the real (symmetric) branch is shown in fig 6. The demultiplexed inputs are fied to 32 identical groups of four taps each. Direct and inverse taps are summed together before multiplication. Folding and summing corresponding samples may present problems in a few-bit representation. The input samples are not actual values, but arbitrary codes. Summing the codes obviously does not work. The code is neither monotonic, nor equispaced. The signal must therefore be converted to a monotonic, equispaced code before the filter. This imposes a limitation on the possible quantization codes, resulting in a slightly reduction in quantization efficiency. A equispaced code (values 1, 3, 5, 7) has an quantization loss of 3.??%, against a loss.Figure 5: Spectral processing of a simulated signalFrom top: (a) mixer output; (b) Sharp filter output; (c)Real signal sent to the correlator.All plots are on a logarithmic vertical scale.The result of the sum of two codes (1, 3, 5, 7) can be any even number from -14 to 14, representable with a 4 bit, signed quantity. For 8 bit signed coe?cients, product size is 11 bit. Filter multipliers are therefore implemented with 16x11 bit RAM blocks.The filter has been designed using the filter from the previous design as a low-pass template, and multiplying each coefficient by the appropriate exponential.The same considerations about coefficient precision truncation apply for here. The actual filter shape,however, depends very much on the local oscillator setting. Truncation is an intrinsically nonlinear procedure, and only statistical properties of the filter shape can be anticipated. An alternative approach would be to use a nonlinear minimization program to adjust filter coefficients on the desired shape after filter rotation, instead of blindly truncate them. This approach would probably give a better stop band rejection (by 2-3 dB), at the expense of a much higher computational effort during filter reprogramming.2.2 Complex Local OscillatorThe local oscillator is greatly simpli?ed with respect to the previous approach. It is composed by a DDS.register, similar to the previous one, that generates a 10 bit phase value. No phase offset is needed, apart from the 90/180 degree phase switching. The 10 bit value is fed to asine/cosine lookup table, that produces a high resolution sine and cosine value. A complex multiplier, implemented with four hardwired multipliers and two adders, compute the expression y(t) = x(t)exp(2j t).The mixer does not select the bandwidth, it must only compensate for the unwanted rotation of the filtered band, and for its possible folding from positive to negative frequencies (as in the example shown in fig. 4). The complex mixing rotates the decimated band in order to have the frequency scale monotonically ordered from-625 MHz to +625 MHz. After conversion, the desired band is centered around frequency zero, and therefore.Figure 6: Coarse FIR schematicSignals from I and Q mixers are multiplied by coefficient taps in LUT tables. Input is from 32 time multiplexed streams, output is to 2 (I and Q) streams.can be filtered by alow-pass filter.The local oscillator value is programmed to the desired LO frequency modulus 125 MHz. The remaining part of the LO frequency affects only first filter coefficients, as bandwidth selection is done in this filter.The phase quantizationstep affects LO harmonicscontent. With 1024phase bins, the first harmonic appears Atharmonic number 1024,with an amplitude of approximately-60dB. Amplitude quantization in the sine/cosine table also generates harmonics, but with 8 bitsine/cosine representation the spur free dynamic range is around -70 dB.To reduce harmonic content, a small (few phase bins) pseudo-random noise can be added to the DDS phase.The resulting phase jitter is of the order of 1 degree, but is multiplied by the harmonic number, completely washing out the harmonics due to phase quantization.The lookup table can be simplified if only first quadrant values are stored, and the sign is treated separately. In this way, lookup table size is reduced to 1/4, and one more bit is available for the result.2.3 Sharp lter and output sectionThis section is identical to the design described in [8]Figure7: Complex localoscillator. A DDS register generatesa phasevalueSine andcosine values aregenerated in a lookup table. The complex multiplication is implemented in 4 hardwired multipliers and two adders.3 Considerations on FPGA resource usageImplementation of this filter require considerably less resources than the previous design. The broad filter has 3 bit input, instead of 6. This requires about half the resources in terms of configurable blocks, lookup tables. The saving in the adder chain is not so high, since most of the adder tree size is dictated by the coefficients size, not by the samples size. The lookup tables must be writable. This increases its complexity,especially in terms of routing resources. The mixer multiplier must be implemented using hard multipliers, not lookup tables. A single large look up table to hold sine/cosine values is still needed. Especially for Altera FPGAs, this is a large advantage, as these chips have smaller RAM blocks, but also one or two large RAMs.Re-tuning the band is relatively slower, the filter has no capability for frequency hopping. This is not a requirement, and tap reloading is in any case faster than for a full 1024 tap filter. Some intelligence is needed in the control processor to recalculate filter taps from thelow-pass prototype, but this is within the capabilities of any current microprocessor.摘要:它是一种Arcetri技术报告提出修改方案并设计的滤波器。

IIR数字滤波器设计有英文摘要

IIR数字滤波器设计摘要数字滤波器是具有一定传输选择特性的数字信号处理装置,其输入、输出均为数字信号,实质上是一个由有限精度算法实现的线性时不变离散系统。

它的基本工作原理是利用离散系统特性对系统输入信号进行加工和变换,改变输入序列的频谱或信号波形,让有用频率的信号分量通过,抑制无用的信号分量输出。

数字滤波器和模拟滤波器有着相同的滤波概念,根据其频率响应特性可分为低通、高通、带通、带阻等类型,与模拟滤波器相比,数字滤波器除了具有数字信号处理的固有优点外,还有滤波精度高(与系统字长有关)、稳定性好(仅运行在0与l 两个电平状态)、灵活性强等优点。

数字滤波器按单位脉冲响应的性质可分为无限长单位脉冲响应滤波器IIR和有限长单位脉冲响应滤波器(FIR)两种。

本文介绍IIR数字滤波器的设计[4]。

关键词:IIR FIRAbstractDigital filter is a digital filter has the certain transmission choicecharacteristic isdigital signal processing device, signal processing device has the certain transmission choicecharacteristic,Is essentially a realization by the finite precision arithmetic and linear time invariant discrete systems。

Its basic principle is to use the characteristics of discrete system for processing and transformation of system input signal,To change the input sequence spectrum or signal waveform,Let the signal components useful frequency by suppression of signal components, the output of useless。

毕业设计IIR滤波器的设计与实现

IIRdigitalfilterdigitalfilterisveryimportantforaclassoffilters,becauseoftheirlo werordertohigherfrequencyselectivepropertieshavebeenwidelyused.Inthispaper,theI IRdigitalfilterdesigntheoryandmethodsused,thatis,thesameimpulseresponsemethodan dbilineartransformationmethod.IntheanalysisofIIRstructure,basedontheoreticalana lysisandsimulationtoestablishthedesignofIIRdigitalfilterstructure,aswellasinter mediatedataaccuracy.Onthisbasis,theuseofGUItoolsprovidedbyMATLABtoachieveuser-f riendlyinterfaceofthedigitalfilterdevelopment,user-friendly.Goodscalabilityofth isdesign,easytoadjusttheperformancentsto beintherealizationofMATLAB.

1.2IIR 滤波器简介 首先认识滤波器的原理:数字滤波器的原理有多种,取平均值是其中的一种。取平均值 就是滤除任何有具有频率的变化分量的信号。数字滤波器还可根据不同原理编制专门的程 序,对采集的信号进行特殊的计算来滤除特定频率的信号。模拟滤波器的原理[1]主要是利 用电容器对高频信号的低阻抗、对低频信号的高阻抗和电感对对低频信号的低阻抗、对高频 信号的高阻抗的特性,滤除特定频率的信号。数字滤波器在各种数字信号处理中发挥着十分 重要的作用,数字滤波器设计一直是信号处理领域的重要研究课题。常用的数字滤波器有 FIR 滤波器和 IIR 滤波器,其中 IIR 数字滤波器因具有结构简单、占用存储空间少、运算速 度快、较高的计算精度和能够用较低的阶数实现、较好的选频特性等特点,得到了广泛应用。 IIR 数字滤波器具有无限宽的冲激响应,与模拟滤波器相匹配。所以 IIR 滤波器的设计可以 采取在模拟滤波器设计的基础上进一步变换的方法[5].滤波器是一种特别重要的线性时不 变系统。从广义上讲,任何对某些频率(相对于 1 长沙毕业设计(论文) 其他频率来说)进行修正的系统称为滤波器。严格的讲,滤波器是一个能让某些频率通 过而完全拒绝其他频率成分的系统。数字滤波器实际上是一个采用有限精度算法实现的线性 非时变离散系统,滤波器的功能实现实际上是通过大量的加法运算和乘法运算完成的。下面 从几个方面分别介绍 IIR 滤波器:⑴IIR 数字滤波器的基本结构:①。直接型:按给出的差 分方程直接实现。②。级联型:将系统函数 H(z)因式分解为较低的二阶节的乘积,每个 双二阶用一个直接型实现,整个系统用双二阶的级联实现。③。并联型:将系统函数 H(z) 因式分解为双二阶之和,每个双二阶用一个直接型实现,整个系统函数作为二阶节的并联网 络实现。⑵系统的传递函数对 IIR 数字滤波器的差分方程的一般形式 y(n)=∑aix(n?i)+∑biy(n?i) i=0i=1MN (ai、bi 为常数) (1.1)

IIR数字滤波器的设计外文翻译

IIR数字滤波器的设计数字滤波器发展一个重要步骤是可实现的传递函数G(z)的接近给定频率响应规格的测定,同时若要IIR稳定也有必要确定G(z)稳定性。

该推算传递函数G(z)的过程称为数字滤波器的设计。

获得G(z)函数参数值后,下一步就是实现一个合格的过滤器结构形式。

在第八章,我们概述一系列为实现FIR和IIR各种功能的实现基本结构。

在这一章中,首先考虑了IIR数字滤波器的设计问题,FIR 数字滤波器的设计是在第10章处理。

首先,我们回顾一些滤波器设计问题相关的问题,下文讨论了一种广泛使用的设计IIR滤波器的方法(基于原型模拟到数字的转换传递函数)。

并用典型的设计实例来说明这种方法,然后考虑到一种IIR滤波器的转换它是由一个函数代替复杂的变量Z达到类型转换,对四种常用的转换进行了总结,最后,考虑使用计算机辅助设计IIR数字滤波器,为此,我们限制MATLAB在确定传递函数的使用讨论。

9.1初步考虑在回答发展数字传递函数G(z)之前有两个需要回答的问题,首要的问题是一个合理的滤波器的频率响应规格从整个系统中数字滤波器将被使用的要求发展,第二个问题是要确定所设计的是FIR还是IIR数字滤波器。

在这一节中,我们首先诊察了这两个问题,接下来,我们回顾到的IIR滤波器设计的基本分析方法,然后再考虑过滤器符合规格测定的顺序,讨论了适当的传递函数缩放比例。

9.1.1数字过滤器的规格如模拟过滤器的例子中,无论是规模和/或相位(延迟)响应对于大多数应用数字滤波器都是需要指定的。

在某些情况下,可能被指定的是单位样值响应或跃阶响应,大多实际应用中,利益问题是由一个实现逼近到一个给定的幅度响应规范的发展。

如第4.6.3节,所设计的滤波器可以通过级联与全通网络纠正相位响应。

全通相位均衡器的设计最近几年接受了相当数量的关注。

在这一章节,限制讨论了幅度逼近问题,我们在第4.4.1节指出,有四种基本类型的过滤器,其幅度如图4.10所示,由于脉冲响应对应于所有这些都是非因果和无限长,这些理想过滤器并不是可以实现的,一种实现近似于这种过滤器的方法是截断的脉冲响应,如图所示。

数字滤波器外文翻译

中文5590字毕业设计(外文翻译材料)2009年6月学 院: 专 业: 学生姓名: 指导教师: 电气与电子工程学院 电子信息工程0503DIGITAL FILTERSDigital filtering is one of the most powerful tools of DSP. Apart from the obvious advantages of virtually eliminating errors in the filter associated with passive component fluctuations over time and temperature, op amp drift (active filters), etc., digital filters are capable of performance specifications that would, at best, be extremely difficult, if not impossible, to achieve with an analog implementation. In addition, the characteristics of a digital filter can be easily changed under software control. Therefore, they are widely used in adaptive filtering applications in communications such as echo cancellation in modems, noise cancellation, and speech recognition.The actual procedure for designing digital filters has the same fundamental elements as that for analog filters. First, the desired filter responses are characterized, and the filter parameters are then calculated. Characteristics such as amplitude and phase response are derived in the same way. The key difference between analog and digital filters is that instead of calculating resistor, capacitor, and inductor values for an analog filter, coefficient values are calculated for a digital filter. So for the digital filter, numbers replace the physical resistor and capacitor components of the analog filter. These numbers reside in a memory as filter coefficients and are used with the sampled data values from the ADC to perform the filter calculations.The real-time digital filter, because it is a discrete time function, works with digitized data as opposed to a continuous waveform, and a new data point is acquired each sampling period. Because of this discrete nature, data samples are referenced as numbers such as sample 1, sample 2, sample 3, etc. Figure 1 shows a low frequency signal containing higher frequency noise which must be filtered out. This waveform must be digitized with an ADC to produce samples x(n). These data values are fed to the digital filter, which in this case is a lowpass filter. The output data samples, y(n), are used to reconstruct an analog waveform using a low glitch DAC.Digital filters, however, are not the answer to all signal processing filtering requirements. In order to maintain real-time operation, the DSP processor must be able to execute all the steps in the filter routine within one sampling clock period1/f s.A fast general purpose fixed-point DSP such as the ADSP-2189M at 75MIPS can 。

数字滤波器外文翻译

数字滤波器数字滤波器是对数字信号进行滤波处理以得到期望的响应特性的离散时间系统。

作为一种电子滤波器,数位滤波器与完全工作在模拟信号域的模拟滤波器不同。

数字滤波器工作在数字信号域,它处理的对象是经由采样器件将模拟信号转换而得到的数字信号。

数字滤波器的工作方式与模拟滤波器也完全不同:后者完全依靠电阻、电容、晶体管等电子元件组成的物理网络实现滤波功能;而前者是通过数字运算器件对输入的数字信号进行运算和处理,从而实现设计要求的特性。

数字滤波器理论上可以实现任何可以用数学算法表示的滤波效果。

数字滤波器的两个主要限制条件是它们的速度和成本。

数字滤波器不可能比滤波器内部的计算机的运算速度更快。

但是随着集成电路成本的不断降低,数字滤波器变得越来越常见并且已经成为了如收音机、蜂窝电话、立体声接收机这样的日常用品的重要组成部分。

数字滤波器一般由寄存器、延时器、加法器和乘法器等基本数字电路实现。

随着集成电路技术的发展,其性能不断提高而成本却不断降低,数字滤波器的应用领域也因此越来越广。

按照数字滤波器的特性,它可以被分为线性与非线性、因果与非因果、无限脉冲响应(IIR)与有限脉冲响应(FIR)等等。

其中,线性时不变的数字滤波器是最基本的类型;而由于数字系统可以对延时器加以利用,因此可以引入一定程度的非因果性,获得比传统的因果滤波器更灵活强大的特性;相对于IIR滤波器,FIR滤波器有着易于实现和系统绝对稳定的优势,因此得到广泛的应用;对于时变系统滤波器的研究则导致了以卡尔曼滤波为代表的自适应滤波理论数字滤波器具有比模拟滤波器更高的精度,甚至能够实现后者在理论上也无法达到的性能。

例如,对于数字滤波器来说很容易就能够做到一个1000Hz 的低通滤波器允许999Hz 信号通过并且完全阻止1001Hz 的信号,模拟滤波器无法区分如此接近的信号。

数字滤波器相比模拟滤波器有更高的信噪比。

这主要是因为数字滤波器是以数字器件执行运算,从而避免了模拟电路中噪声(如电阻热噪声)的影响。

数字滤波器的仿真与实现_中英文翻译