封装流程介绍

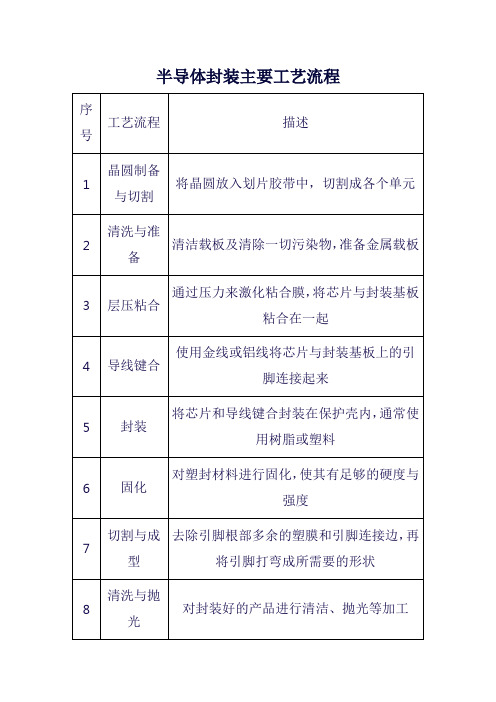

半导体封装主要工艺流程

序号

工艺流程

描述

1

晶圆制备与切割

将晶圆放入划片胶带中,切割成各个单元

2

清洗与准备

清洁载板及清除一切污染物,准备金属载板

3

层压粘合

通过压力来激化粘合膜,将芯片与封装基板粘合在一起

4

导线键合

使用金线或铝线将芯片与封装基板上的引脚连接起来

5

封装

将芯片和导线键合封装在保护壳内,通常使用树脂或塑料

6

固化

对塑封材料进行固化,使其有足够的硬度与强度

7

切割与成型

去除引脚根部多余的塑膜和引脚连接边,再将引脚打弯成所需要的形状

8

清洗与抛光

对封装好的产品进行清洁、抛光等加工

9

标识与打印

根据客户需要,在封装器件表面进行打印,用于识别

10

测试

对封装好的半导体器件进行测试,检验其性能和可靠性

第二章 封装工艺流程

封装工艺的基本流程:

硅片减薄 芯片切割 硅片贴装 芯片互连

打码

上焊锡 切筋成形

成型技术即 (塑料封装) 去飞边毛刺

尹小田

硅片的尺寸越来越大,为了方便制 造、测试和运送过程,厚度增加。

硅片减薄 芯片切割 硅片贴装 芯片互连

成型技术即

打码 上焊锡 切筋成形

(塑料封装) 去飞边毛刺

背面减薄技术有: 磨削、研磨、干式抛光(Dry Polishing)、 化学机械抛光(chemical mechanicai polishing,CMP)、 电化学腐蚀(Electrochemical Etching)、 湿法腐蚀(Wet Etching,WE)、 等离子增强化学腐蚀(Plasma-Enhanced Chemical Etching,PECE) 常压等离子腐蚀(Atmosphere Downstream Plasma

尹小田

(4)玻璃胶粘贴法

方法:用高分子材料聚合物玻璃胶进行芯片粘贴。 工艺:先以盖印、网印、点胶的技术把胶原料涂布在基

板的芯片座中,再把芯片置于玻璃胶上粘贴。

1、多用于陶瓷封装中 2、冷却过程谨慎控制降温的速度以免造成应力破 裂

优3、点增:加可热以、得点到传无导空性隙能、,热可稳以定加性金优属良如的:、箔低、结银合应力、 低湿气含量的芯片粘贴;

尹小田

4、芯片互连

硅片减薄 芯片切割 硅片贴装 芯 切筋成形

(塑料封装) 去飞边毛刺

定义:把电子外壳的I/O引线或基板上的金线焊区与芯片的 焊区相连。

涂布合适的厚度和轮廓的芯片焊盘上进行固化。

1、各向同性材料。

不精确会怎样?

2、导电硅橡胶。

3、各向异性导电聚合物。 导电胶的缺点:热稳定性不好、高温时容易劣化和引发导 目电用的胶于导是中高电:有可胶改机靠中善物度填胶气要充的体求银导充的颗热分封粒性泄装或,漏。银增而薄强降片散低,热产因能品此力的都。 可是靠是度导,电因的此。不

4.封装流程介绍

入出料主要是将导线架 ( Lead Frame)由物料 盘 ) (Magazine)送上输送架 ) (Bar or Bridge)进入模具 ) 内做冲切;在机台中, 内做冲切;在机台中,入出 料机构的夹具动作大多以气 压作动。 压作动 magazine

F/S入料机构和D/T的入料机构大致相同,均以 F/S入料机构和D/T的入料机构大致相同, 入料机构和D/T的入料机构大致相同 magazine作为入料盒 至于出料方式,D/T为 作为入料盒, magazine作为入料盒,至于出料方式,D/T为 magazine, F/S工作行程最后均将IC从导线架 工作行程最后均将IC magazine,而F/S工作行程最后均将IC从导线架 上取出所以,出料机构总共分为二个部份: 上取出所以,出料机构总共分为二个部份: 1.Tray盘 2.Tube管 1.Tray盘 2.Tube管

固化后取出。 固化后取出。

Epoxy Molding Compound

IC塑胶封装材料为热固性环氧树脂 塑胶封装材料为热固性环氧树脂 塑胶封装材料为 (EMC)其作用为填充模穴 其作用为填充模穴(Cavity) 其作用为填充模穴 将导线架(L/F)完全包覆,使銲线好 完全包覆, 将导线架 完全包覆 的芯片有所保护。 的芯片有所保护。

Tie Bar

4.成型(Forming) 4.成型(Forming) 成型 的目的: 的目的:

将已去框( 将已去框(Singulation) ) Package之Out Lead以连 之 以连 续冲模的方式, 续冲模的方式,将产品脚 弯曲成所要求之形状。 弯曲成所要求之形状。

海 鸥 型 引 脚 插 入 型

Heat Slug Attach

Molding

MD(封胶 封胶) 封胶 (Molding)

3d封装工艺流程

3d封装工艺流程3D封装工艺是一种先进的封装技术,可实现芯片堆叠和三维集成。

以下是3D 封装工艺流程的主要步骤:1. 芯片制备:首先,在硅片上制备出具有不同功能的有源芯片和无源芯片。

这些芯片可以是基于不同材料和工艺制作的,例如CMOS、EEPROM、MOSFET等等。

这些芯片将在后续的工艺流程中用于构建三维集成电路。

2. 基板制备:为了实现芯片的垂直连接,需要使用基板作为支撑和连接材料。

基板通常由高导热性和高电导率的材料制成,例如铜、铝等。

基板上需要制备出凸点和连接线路,以便后续的连接工艺。

3. 芯片贴装:将有源芯片和无源芯片贴装在基板上。

贴装方法可以采用传统的引线键合或倒装焊技术。

在贴装过程中,需要保证芯片的位置和角度精度,以确保后续的连接工艺能够顺利进行。

4. 连接工艺:在贴装完毕后,需要采用引线键合、倒装焊或凸点连接等方法,实现芯片与基板之间的连接。

这些连接方法需要根据不同的应用需求进行选择和优化。

5. 封装保护:在完成连接后,需要采用合适的封装材料和工艺,将整个三维集成电路进行封装保护。

常用的封装材料包括塑料、陶瓷和金属等。

在封装过程中,需要注意保护好内部电路,并确保封装后的可靠性和稳定性。

6. 测试与校准:完成封装后,需要对三维集成电路进行测试和校准。

测试内容可以包括电路性能、电气特性、热特性、机械性能等方面。

根据测试结果进行校准和调整,以保证电路的性能达到预期要求。

以上是3D封装工艺流程的主要步骤。

在实际应用中,根据不同的需求和设计要求,可能还需要进行其他优化和改进。

3D封装工艺的发展为芯片集成和三维集成提供了广阔的应用前景,可以应用于电子器件、通信设备、医疗设备等多个领域。

同时,随着技术的发展和创新,3D封装工艺也将不断得到优化和改进。

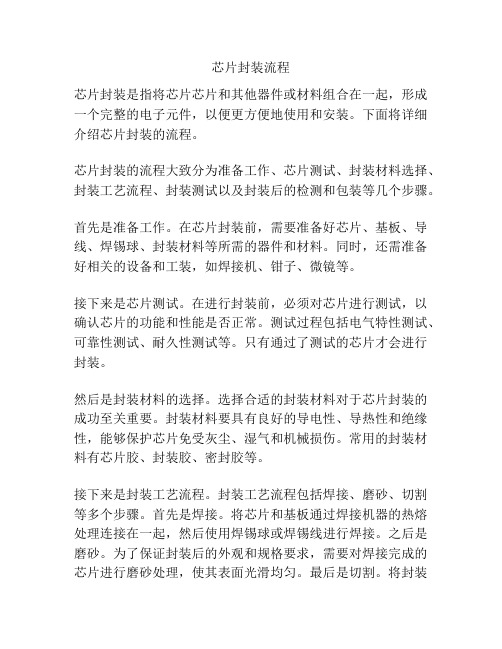

芯片封装流程

芯片封装流程芯片封装是指将芯片芯片和其他器件或材料组合在一起,形成一个完整的电子元件,以便更方便地使用和安装。

下面将详细介绍芯片封装的流程。

芯片封装的流程大致分为准备工作、芯片测试、封装材料选择、封装工艺流程、封装测试以及封装后的检测和包装等几个步骤。

首先是准备工作。

在芯片封装前,需要准备好芯片、基板、导线、焊锡球、封装材料等所需的器件和材料。

同时,还需准备好相关的设备和工装,如焊接机、钳子、微镜等。

接下来是芯片测试。

在进行封装前,必须对芯片进行测试,以确认芯片的功能和性能是否正常。

测试过程包括电气特性测试、可靠性测试、耐久性测试等。

只有通过了测试的芯片才会进行封装。

然后是封装材料的选择。

选择合适的封装材料对于芯片封装的成功至关重要。

封装材料要具有良好的导电性、导热性和绝缘性,能够保护芯片免受灰尘、湿气和机械损伤。

常用的封装材料有芯片胶、封装胶、密封胶等。

接下来是封装工艺流程。

封装工艺流程包括焊接、磨砂、切割等多个步骤。

首先是焊接。

将芯片和基板通过焊接机器的热熔处理连接在一起,然后使用焊锡球或焊锡线进行焊接。

之后是磨砂。

为了保证封装后的外观和规格要求,需要对焊接完成的芯片进行磨砂处理,使其表面光滑均匀。

最后是切割。

将封装后的芯片按照需要的尺寸进行切割。

紧接着是封装测试。

封装测试主要是对封装后的芯片进行功能测试、可靠性测试和外观检查。

通过这些测试,可以确保封装后的芯片达到设计要求,并且没有明显的缺陷或损坏。

最后是封装后的检测和包装。

这一步骤主要是对封装后的芯片进行一些必要的检查和包装工作。

检测包括外观检查、尺寸检查、性能检查等。

然后将芯片放入适当的包装盒或袋中,标明相关信息,便于存储和运输。

总结起来,芯片封装的流程包括准备工作、芯片测试、封装材料选择、封装工艺流程、封装测试以及封装后的检测和包装。

每个步骤都非常重要,需要精确操作和仔细检查,以确保封装后的芯片性能和质量达到要求。

芯片封装作为电子产业的重要环节,对于提高芯片的可靠性和稳定性具有重要意义。

qfn封装流程

qfn封装流程QFN封装流程QFN封装(Quad Flat No-leads Package)是一种常用于集成电路封装中的无引脚封装技术,具有体积小、重量轻、良好的散热性能等优点。

本文将介绍QFN封装的流程,包括设计、制造和测试等环节。

设计阶段是QFN封装流程的第一步。

在设计QFN封装时,需要考虑芯片的尺寸、引脚数量和布局,以及封装的材料和工艺要求等因素。

设计人员需要根据芯片的特性和要求,选取合适的封装规格,并进行引脚的布局设计。

同时,还需要设计封装的接触面和散热结构,以确保封装的可靠性和散热性能。

制造阶段是QFN封装流程的第二步。

在制造QFN封装时,首先需要制作封装模具。

模具制作完成后,将芯片放置在模具中,并使用封装材料进行封装。

封装材料通常为导电胶或导热胶,可以提供电气连接和散热功能。

在封装过程中,需要控制好温度和压力,以确保封装的质量和可靠性。

完成封装后,还需要进行外观检查和尺寸测量等工序,以确保封装的准确性和一致性。

测试阶段是QFN封装流程的最后一步。

在测试QFN封装时,需要进行外观检查、电气测试和可靠性测试等多个环节。

外观检查主要是检查封装的外观是否符合要求,包括尺寸、焊盘和引脚等。

电气测试是为了验证封装的电性能是否符合要求,包括输入输出特性、电阻和电容等。

可靠性测试是为了评估封装在不同环境和应力下的可靠性,包括温度循环、湿热循环和冲击等。

QFN封装流程包括设计、制造和测试三个阶段。

在设计阶段,需要考虑封装规格、引脚布局和散热结构等因素。

在制造阶段,需要制作封装模具,并使用封装材料进行封装。

在测试阶段,需要进行外观检查、电气测试和可靠性测试等环节。

通过这些流程,可以确保QFN封装的质量和可靠性,满足集成电路的需求。

封装流程介绍

二. IC各部份名称 三.产品加工流程

四. IC前段封装流程

五. IC后段封装流程

晶片封裝的目的

IC封装是属半导体产业的后段 加工制程,主要是将前制程加工 完成(即晶圆厂所生产)之晶圓 上IC予以分割,粘晶、并加上外 接引脚及包覆。而其成品(封装 体)主要是提供一個引接的介面, 內部电性讯号亦可透过封装材料 (引脚) 将之连接到系统,並提供 矽晶片免于受外力与水、湿气、 化学物之破坏与腐蚀等。

Dejunk/Trim (DT 去胶去纬)

Packing (PK 包装)

传统 IC 封裝流程

Production Technology Center

BGA 封裝流程

Production Technology Center

TE-BGA Process Flow(Thermal Enhanced- BGA)

空 模

放入L/F

合 模

离 模

开 模

注 胶

若以封装材料分类可分为: 1.陶瓷封裝 2.塑料封裝

1.陶瓷封装(CERAMIC PACKAGE):

适于特殊用途

的IC(例:高频

用、军事通讯 用 )。

2.塑料封裝(PLASTIC PACKAGE):

适用于大量生产、为目前主流(市场占有 率大约90 %)。

Wire Bond

焊线的目的是将晶粒上的接点以极细的焊线(15~75um)连接到导线架上 之内引脚,藉而将IC晶粒之电路讯号传输到外界。当导线架从弹匣内传 送至定位后,应用电子影像处理技术来确定晶粒上各个接点以及每一接点 所相对应之内引脚上之接点的位置,然后做焊线之动作。焊线时,以晶粒 上之接点为第一焊点,内接脚上之 接点为第二焊点。首先将金线之端点 烧结成小球,而后将小球压焊在第一焊点上(此称为第一焊,first bond)。 接着依设计好之路径拉金线,最后将金线压焊在第二焊点上(此称为第二 焊,second bond),同时并拉断第二焊点与钢嘴间之金线,而完成一条金 线之焊线动作。接着便又结成小球开始下一条金线之焊线动作。

IC封装流程介绍ppt课件

精选课件ppt

16

去胶/去纬 (Dejunk / Trimming)

去胶/去纬后

去胶/去纬前

精选课件ppt

17

去胶/ (Dejunk)

去胶(Dejunk)的目的:所谓去胶,是指利用机械模具将脚 尖的费胶去除;亦即利用冲压的刀具(Punch)去除掉介于胶 体(Package)与(Dam Bar)之間的多余的溢胶。

一. 二.IC内部结构

三.封装主要流程简介

四.产品加工流程

精选课件ppt

1

简介

In

Out

精选课件ppt

2

封装的目的

IC封装属于半导体产业的后段加工 制程,主要是将前制程加工完成

(即晶圆厂所生产)的晶圆上的IC 予以分割,黏晶、打线并加上塑封

及成型。

其成品(封装体)主要是提供一个

引接的接口,内部电性讯号可通过

Dam Bar

去胶位置

精选课件ppt

18

去纬 (Trimming)

去纬(Trimming)的目的: 去纬是指利用机械模具将脚间金属连接杆切除。

去纬位置

外腳位置

精选课件ppt

19

去框 (Singulation)

去框(Singulation)的目的: 將已完成盖印(Mark)制程 的Lead Frame,以沖模的方 式将Tie Bar切除,使 Package与Lead Frame分开, 方便下一个制程作业。

精选课件ppt

7

晶粒黏贴 (Die Bond)

目的:将晶粒置于框架(Lead Frame) 上,并用银胶(Epoxy)黏着固定。

导线架是提供晶粒一个黏着的位置 (称作晶粒座,Die Pad),并预设有 可延伸IC晶粒电路的延伸脚。黏晶完 成后之导线架则经由传输设备送至金 属匣(Magazine)内,以送至下一制 程进行焊线。

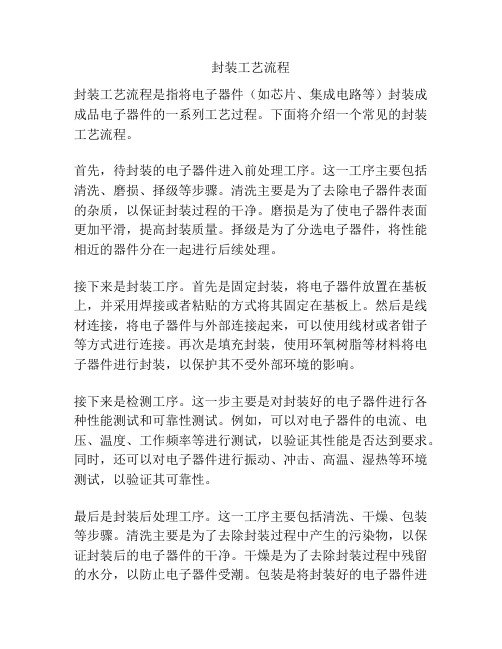

封装工艺流程

封装工艺流程封装工艺流程是指将电子器件(如芯片、集成电路等)封装成成品电子器件的一系列工艺过程。

下面将介绍一个常见的封装工艺流程。

首先,待封装的电子器件进入前处理工序。

这一工序主要包括清洗、磨损、择级等步骤。

清洗主要是为了去除电子器件表面的杂质,以保证封装过程的干净。

磨损是为了使电子器件表面更加平滑,提高封装质量。

择级是为了分选电子器件,将性能相近的器件分在一起进行后续处理。

接下来是封装工序。

首先是固定封装,将电子器件放置在基板上,并采用焊接或者粘贴的方式将其固定在基板上。

然后是线材连接,将电子器件与外部连接起来,可以使用线材或者钳子等方式进行连接。

再次是填充封装,使用环氧树脂等材料将电子器件进行封装,以保护其不受外部环境的影响。

接下来是检测工序。

这一步主要是对封装好的电子器件进行各种性能测试和可靠性测试。

例如,可以对电子器件的电流、电压、温度、工作频率等进行测试,以验证其性能是否达到要求。

同时,还可以对电子器件进行振动、冲击、高温、湿热等环境测试,以验证其可靠性。

最后是封装后处理工序。

这一工序主要包括清洗、干燥、包装等步骤。

清洗主要是为了去除封装过程中产生的污染物,以保证封装后的电子器件的干净。

干燥是为了去除封装过程中残留的水分,以防止电子器件受潮。

包装是将封装好的电子器件进行分类、包装和标识,以方便存储和运输。

以上就是一个常见的封装工艺流程。

需要注意的是,封装工艺流程可能因不同的电子器件种类和封装要求而有所差异。

因此,在实际生产中,还需根据具体情况进行细化和调整。

封装工艺的良好实施可以有效提高电子器件的性能和可靠性,以满足市场需求。

组件封装工艺流程图解

组件封装工艺流程图解

一、分选二、划片三、单焊

对电池片的电性能进行筛选,以及将电池片切割成所需要的将涂锡带〔行业称互联条〕焊接在

对电池片的色差、崩边、隐裂、缺尺寸规格。

单个电池片的负极主栅线上。

角等外不雅不良的筛选。

四、串焊五、叠层六、层压

将焊接好的假设干个〔按技术要求〕串焊好的电池串按图纸要求进行摆列,并将将叠层好的组件,放入已经调试、电池片从正极互相焊接成一个电池每个电池串的两头引线全部串联成一个回路,设定好温度、抽真空时间等参数的串。

将玻璃、EV A、TPT、电池串按序叠放。

层压机进行封装。

七、装框八、清洗九、测试

将符合要求的组件,进行铝合金边框对组件外表进行清洗。

对组件进行电性能的测试,并分档。

的安装,同时安装接线盒。

组件封装所用原材料

电池片EV A TPT

玻璃铝合金型材互联条硅胶接线盒电池组件

封装设备图片

全自动层压机半自动层压机

〔RDCY—Z系列〕〔RDC—Y系列〕

秦皇岛瑞晶太阳能科技出产的全自动和半自动层压机,可按照电池组件不同的工艺要求,设置不同的工艺参数,并采用了多点温度控制技术来包管温度的均匀性,降低了碎片率,能有效的提高层压组件的优质品率。

并在对设备进行了全面的布局调整,最大限度的便利组件放入和取出,橡胶板的更换极其便利。

激光划片机

单片测试仪

组件测试仪

单、串焊台〔RHT型〕叠层台〔RJT〕修复台〔RPT〕

装框机〔RZK—1〕待装框组件周转车〔RCZ〕待压组件周转车〔RCY〕。

SOP封装工艺流程介绍

目录

• SOP封装简介 • SOP封装工艺流程 • SOP封装材料 • SOP封装技术发展趋势 • SOP封装工艺问题与对策

01

SOP封装简介

SOP封装定义

SOP封装,全称为Small Outline Package,是一种常见的电子封装形 式,主要用于将集成电路(IC)封装 在印刷电路板(PCB)上。

微型化是指通过减小封装尺寸来减小整个电子设备的体积和重量。SOP封装技 术通过改进封装结构、减小引脚间距、采用薄型小尺寸封装等形式,实现了更 小的封装尺寸,满足了电子设备微型化的需求。

高集成度

总结词

随着集成电路技术的发展,SOP封装技术也呈现出高集成度 的发展趋势。

详细描述

高集成度是指通过在单一封装内集成更多的电子元件和功能 ,提高整个系统的性能和功能。SOP封装技术通过采用多芯 片组装、集成无源元件等方式,实现了更高的集成度,提高 了系统的性能和功能。

02

这一步骤中,需要检查产品是否有明显的缺陷、污渍或不良的

机械性能。

外观检查通常采用自动化设备进行,以提高检查效率和准确性。

03

测试与筛选

测试与筛选是对已完成的SOP封装产品进行电气 性能测试和筛选的过程。

这一步骤中,需要使用测试设备对产品的电气性 能进行检测,如电压、电流、电阻和电容等。

对于不合格的产品需要进行筛选和处理,以确保 最终产品的质量和可靠性。

VS

详细描述

引脚扭曲的原因可能包括引脚材料质量不 佳、加工精度不足、插装过程中受到外力 等。为了解决这个问题,可以加强引脚材 料的质量控制、提高加工精度、优化插装 工艺,并在插装过程中避免外力作用。

芯片破损

总结词

led封装工艺流程五大步骤

LED封装工艺流程五大步骤导言LED(Light Emitting Diode)是一种发光二极管,具有低能耗、长寿命和快速开关等优点,在各种照明和显示应用中得到广泛应用。

然而,要将LED芯片制成完整的LED产品,需要通过封装工艺来保护和增强其性能。

本文将介绍LED封装工艺的五个主要步骤。

步骤一:芯片分选在LED制造过程中,第一步是将制造好的芯片进行分选。

芯片是制造LED的核心组件,其质量和性能直接影响到最终产品的品质。

在芯片分选过程中,对芯片进行外观和电性能测试,以筛选出符合要求的高质量芯片。

只有通过严格的筛选,才能保证后续工艺步骤的顺利进行。

步骤二:球形封装经过芯片分选后,下一步是进行球形封装。

球形封装是LED封装工艺中的一项重要步骤,通过将LED芯片放置在金属支架上,并在芯片上方加上透明的球形塑料罩,形成一个球形封装结构。

球形封装不仅可以保护芯片免受外界环境的影响,还可以增强光的折射和发散效果,提高LED的亮度和视角。

步骤三:焊接电极在完成球形封装后,接下来是对球形封装LED进行焊接电极的步骤。

焊接电极是将LED芯片与电路板连接的重要环节,它决定了LED产品的电气性能和可靠性。

在焊接电极的过程中,首先将金属线与芯片上的金属电极焊接,并将焊接好的电极镶嵌在透明塑料罩的底部。

通过这一步骤,LED的电信号可以传输到芯片中,进而实现LED的发光功能。

步骤四:组装封装焊接电极完成后,便进行组装封装的步骤。

组装封装是将已经焊接好电极的LED芯片与电路板进行连接,并封装到外壳内的工艺过程。

在这一步骤中,需要将电路板上的电路与焊接好的LED芯片进行精密的对位,然后采用粘合剂将其黏合在一起,形成一个整体。

组装封装可以增强LED的机械强度和耐冲击性,保护内部结构,同时还能方便LED产品的安装和散热。

步骤五:测试和包装最后一个步骤是测试和包装。

在测试阶段,对已经封装好的LED产品进行电性能测试、光强度测试、色度测试等,以确保产品符合规定的标准和要求。

lga封装工艺流程步骤

LGA封装工艺流程步骤LGA(Land Grid Array)封装工艺是一种常用于集成电路芯片封装的技术,它通过一系列精密的工艺步骤,将芯片连接到印刷电路板上,并提供电气和机械的连接。

本文将详细介绍LGA封装工艺的流程步骤。

1. 芯片准备LGA封装工艺的第一步是准备芯片。

在这个步骤中,芯片通过精密的制造工艺被制造出来。

然后,芯片会经过测试来确保其质量和性能。

2. PCB准备在LGA封装过程中,需要使用印刷电路板(PCB)作为芯片的载体。

在这一步骤中,需要准备好符合特定要求的PCB,包括PCB的大小、材料和布局等。

3. 芯片粘贴在这一步骤中,使用适当的胶水或粘合剂将芯片粘贴到PCB上。

要确保芯片的位置和定位准确无误,以确保后续工艺步骤的顺利进行。

4. 焊接通过焊接技术将芯片与PCB上的焊盘连接起来。

焊接技术可分为手工焊接和机器焊接两种方式。

手工焊接需要经验丰富的操作人员,而机器焊接通常更快、更精确。

5. 清洗在焊接完成之后,需要对PCB进行清洗,以去除焊接过程中产生的残留物。

清洗可以使用特殊的清洗剂和设备进行,确保PCB表面干净无污染。

6. 封装在这一步骤中,使用封装材料将整个PCB封装起来,以保护芯片和其他电子元件免受外界环境的影响。

封装材料通常是一种高性能的绝缘材料,能够提供电气和机械连接功能。

7. 高温固化封装材料通常需要在高温下固化,以确保其能够提供良好的封装效果。

在高温固化过程中,需要控制好温度和时间,以避免过热或过度固化。

8. 检测与测试封装完成后,需要对封装后的芯片进行检测和测试,以确保其质量和性能。

这些测试可以包括外观检查、电气测试和功能测试等,以验证芯片的可靠性和稳定性。

9. 终检与包装在所有工艺步骤完成之后,进行终检与包装。

终检是最后一道工序,通过对封装好的芯片进行全面检测,确保其符合规定的标准和要求。

然后,芯片将被包装起来,以便运输和存储。

结论LGA封装工艺是一种常用的电子封装技术,通过精密的步骤将芯片连接到PCB 上,并提供电气和机械连接。

《LED封装流程简介》课件

封装材料包括粘合剂、热敏胶、塑料封装材料等,以及封装工艺所需的固化剂、抗剪强 度增强剂等。

封装流程步骤

1

准备工作

准备封装所需的基材、芯片、胶水等材

芯片固定

2

料,并检查设备的工作状态。

将芯片精确定位并固定在基材上,确保

芯片与基材之间的电连接畅通。

3

倒盖覆胶

在芯片上方的基材上倒覆胶水,形成保

《LED封装流程简介》PPT 课件

本PPT课件将介绍LED封装的流程、分类、材料以及产业现状和未来发展。欢 迎加入这个充满发展前景的领域!

封装流程介绍

1 封装定义

LED封装是指将裸露的LED芯片封装到套管中,以保护芯片并实现特定的电性能和光学性 能。

2 封装分类

根据封装方式和结构,LED封装可分为片式封装、芯片级封装和模组封装。

焊接

4

护层以及提Leabharlann 光学效果。进行电连接的焊接工序,确保芯片与基

材之间的可靠电性连接。

5

成品检测

通过光学检测和电学测试等手段对成品 进行质量检验,确保产品符合要求。

封装工艺流程图

封装材料介绍

封装材料分类

封装材料可分为粘合剂、热敏胶、塑料封装材 料等,每种材料都有不同的特性和用途。

热敏胶

热敏胶可以在封装过程中,通过温度的变化实 现不同的封装效果,如粘合、硬化和保护等。

粘合剂

粘合剂用于将芯片与基材粘合在一起,确保电 性连接和结构的稳定。

封装材料性能

封装材料应具有良好的导热性、抗高温性、防 潮性和阻燃性,以确保LED产品的长期稳定性和 可靠性。

LED封装及产业现状

封装工厂

LED封装工厂拥有先进的生产设 备和严格的质量控制标准,为 LED产业的发展提供关键支持。

集成电路封装技术-封装工艺流程介绍

〔4〕在芯片最终封装前可进行预测试和通电老化。这样可剔 除坏芯片,不使它流入下一道工序,从而节省了成本,提高了 可靠性。

〔5〕TAB工艺中引线的键合平面低,使器件薄化。

第二章 封装工艺流程

2.4.2 载带自动键合技术

TAB技术的关键材料

第二章 封装工艺流程

2.3.1共晶粘贴法 预型片法,此方法适用于较大面积的芯片粘贴。优点是

可以降低芯片粘贴时孔隙平整度不佳而造成的粘贴不完全 的影响。

第二章 封装工艺流程

2.3.2 焊接粘贴法

变形方式的不同,继而产生的各种应力。当材料在外力作用下不能产生位移时,它的几何形状和尺寸将发

在一点的集度焊称为接应粘力〔贴St法res是s〕利。物用体合由于金外反因而响变进形时行,芯在物片体粘内各贴局的部之方间法产生。相优互作点用是的内力, 应变方向平热行,传而导切应性力好的方。向与应变垂直。按照载荷〔Load〕作用的形式不同,应力又可以分为拉伸压

2.4.1 打线键合技术介绍 〔2〕热压键合

;然后再电子点火或氢焰将金属线烧断并利用熔融金属的外表张力作用使线的末端灼烧成球〔直径约为金

键合工具升起并引导金属线至第二键合点上进行楔形接合〔不需烧成金属球,而是将金属线直接压到焊区 状。 抗氧化性强〕。为降低成本有时也用铝线。铝线的2个焊接点是楔形的。原因是铝线不易在线的末端灼烧成

第二章 封装工艺流程

〔2〕影响打线键合可靠度因素

封胶和粘贴材料 与线材的反应

金属间化合物的形成

可靠度因素

可靠度常用拉力试验 和键合点的剪切试验 测试检查

第二章 封装工艺流程

2.4在.2其载载特带带定自的自动位动健置合键上技开合术出技是一在术个类窗似口于。1窗3口5胶为片蚀的刻柔出性一载定带的粘印结刷金线属路薄图片形,的〔金像属电箔影片

tfbga封装工艺流程

tfbga封装工艺流程

TFBGA封装工艺流程是一种常用的封装技术,TFBGA代表着Thin Fine Pitch Ball Grid Array。

下面是一个关于TFBGA封装工艺流程的详细描述:

1. 选取基片:首先,选择适合的基片材料用于封装。

常见的基片材料包括塑料、陶瓷和金属。

2. 材料准备:准备封装所需的材料,包括封装胶、导线、连接器等等。

3. 基片准备:将基片进行清洗和处理,以确保表面光洁、无尘和脏物。

4. 涂胶:将封装胶均匀涂覆在基片上,以提供粘接和保护作用。

5. 粘接芯片:将芯片粘接到涂有胶的基片上。

确保芯片与基片之间的粘接牢固。

6. 连接器安装:根据设计要求,安装连接器以实现芯片与外部电路的连接。

7. 金球键合:使用焊接机器或激光器将引线焊接到芯片芯片的金属焊盘上。

这

些引线将被用于芯片的信号传输。

8. 导线布线:通过导线连接芯片的不同引脚,形成内部电路。

9. 封装测试:对封装完成的芯片进行功能和可靠性测试以确保其完成封装后的

表现符合预期。

10. 成品封装:将已经通过测试的芯片进行整形、切割和包装,以便于后续的

使用和销售。

TFBGA封装工艺流程是一个复杂而精确的过程,通过以上步骤,可以实现对

芯片的封装和保护,以及与外部电路的连接。

这种封装方式被广泛应用于电子产品制造,如手机、电脑和通信设备等。

通过TFBGA封装工艺流程,芯片可以更好地

适应各种环境条件,并提供更好的性能和可靠性。

qfp封装工艺流程

qfp封装工艺流程QFP(Quad Flat Package)封装工艺流程是一种常用的集成电路封装工艺,能够满足高密度和高性能要求。

以下是一个典型的QFP封装工艺流程的步骤:1.基板准备:选择一个适当的基板材料,如FR4,根据设计要求剥离基板和切割到规定的尺寸。

必须确保基板平整、洁净。

2.焊膏印刷:将焊膏通过丝网印刷到基板上。

焊膏具有良好的粘附性,粘附在了希望焊接的引脚的上面。

丝网印刷是一个准确且重要的步骤,确保焊膏被均匀地分布在基板上。

3.贴装:在焊膏上面的基板上使用自动贴片机精确地贴上IC芯片。

芯片通过吸盘将其转移到基板上,并且定位到焊膏上使用引脚。

贴片机具有高速度和精度,能够快速且准确地将芯片贴装到基板上。

4.固化:将贴装好的基板送入回流炉中,通过控制温度和时间使焊膏固化。

这有助于焊膏发挥它的粘合力和导电性。

5.切割:使用切割机将基板切割成QFP封装的形状。

切割机通常使用高速旋转的切割刀具,轻易地将基板分割成封装的外形。

6.引脚整形:通过引脚整形机器对QFP封装的引脚进行整形,以确保其与钻孔或插座相匹配。

引脚整形也有助于最大程度地减少QFP封装的引脚之间的短接。

7.焊接:将QFP封装的基板通过波峰焊接机器进行波峰焊接。

这使得引脚与PCB焊盘之间形成可靠的焊接。

8.清洗:将封装后的基板放入清洗机,用适当的溶剂清洗基板,以去除焊接过程中产生的焊渣和其他污染物。

清洗过程有助于确保焊接质量和可靠性。

9.测试:进行电气测试,以确保封装后的QFP芯片正常工作。

测试通常包括耐压测试、功能测试、时序测试和环境测试等。

10.包装和交付:经过测试后,将QFP封装好的芯片进行包装,并进行必要的标识和记录。

最后,将封装好的芯片交付给客户或进一步生产中使用。

总结:QFP封装工艺流程经过多个步骤,从基板准备、焊膏印刷、贴装、固化、切割、引脚整形、焊接、清洗、测试直至最后的包装和交付。

每个步骤都需要精确和准确的控制,以确保最终制得的QFP芯片满足高质量、高可靠性的要求。

封装流程介绍范文

封装流程介绍范文封装是面向对象编程的核心概念之一,通过封装,我们可以将数据和操作数据的方法组合成一个整体,对外部提供接口进行使用,同时隐藏了内部的实现细节,提高了程序的安全性和可维护性。

在本文中,我们将详细介绍封装的流程和步骤。

第一步:识别类封装的第一步是识别需要封装的数据和相关的操作方法。

在面向对象编程中,类是封装的基本单位。

类定义了一组相关的属性和方法,用于描述一类对象的特征和行为。

需要封装的数据可以是类的属性,而相关的操作方法可以是类的方法。

第二步:设计类接口设计类的接口是封装的重要一步。

类的接口是指外部与类进行交互的方式,包括可以调用的方法和可以访问的属性。

接口应该明确描述类的功能和使用方法,同时考虑使用者的便利性,避免暴露内部实现细节。

第三步:定义属性和方法在类的设计中,需要定义类的属性和方法。

属性是类的状态信息,用于存储对象的数据;方法是类的行为信息,用于操作和处理对象的数据。

属性和方法应该根据类的功能和目的进行选择和设计,同时遵循高内聚、低耦合的设计原则。

第四步:封装属性和方法封装的关键是隐藏内部实现细节,使得外部只能通过类的接口来访问和操作数据。

在类内部,可以使用修饰符来限定属性和方法的访问权限,例如private、protected、public等。

通常,类的属性应该使用私有(private)修饰符进行封装,只能在类的内部访问和操作,而方法可以根据需要选择合适的访问权限。

第五步:提供访问接口封装的目的是为了隐藏内部实现细节,提供简洁的接口供外部访问和操作类的数据。

因此,在类的设计中,需要提供公共的访问接口,通过这些接口进行数据的读取和修改。

这些接口可以是类的公共方法,也可以是通过getters和setters方法实现的。

第六步:测试和调试封装的实现后,需要进行测试和调试,确保类的接口和功能正常工作。

测试可以通过编写测试用例来完成,对于各种情况和可能出现的异常情况进行测试,确保类的功能和接口的正确性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Material

Epoxy Molding Compound

IC塑膠封裝材料為熱固性環氧樹脂 (EMC)其作用為填充模穴(Cavity) 將導線架(L/F)完全包覆,使銲線好 的晶片有所保護。

Lead Frame

Lead Frame稱為導線架或釘架,其 目的是在承載晶片及銲金線用,使 信號得以順利傳遞,而達到系統的 需求。

2.塑膠封裝(PLASTIC PACKAGE):

適於大量生產、為目前主流(市佔率大 約90 %)。

黑膠-IC

透明膠-IC

IC封裝製程是採用轉移成型 ( TRANSFER MOLDING)之方法,以熱固性環氧樹脂 (EPOXY MOLDING COMPOUND:EMC)將黏晶 (DA)、銲線(W/B)後之導線架(L/F)包覆起來。 封膠製程類似塑膠射出成形( PLASTIC INJECTION MOLDING),是利用一立式射出機 (TRANSFER PRESS)將溶化的環氧樹脂(EPOXY) 壓入中間置放著L/F的模穴(CAVITY)內,待其

Wafer In

Wafer Grinding (WG研磨)

Wafer Saw (WS 切割)

Die Attach (DA 黏晶)

Epoxy Curing (EC 銀膠烘烤)

Wire Bond (WB 銲線)

Die Coating (DC 晶粒封膠)

Molding (MD 封膠)

Post Mold Cure

一.晶片封裝目的 二.IC後段流程 三.IC各部份名稱 四.產品加工流程 五.入出料機構

晶片封裝的目的

IC構裝係屬半導體產業的後段 加工製程,主要是將前製程加工 完成(即晶圓廠所生產)之晶圓 上IC予以分割,黏晶、並加上外 接引腳及包覆。而其成品(封裝 體)主要是提供一個引接的介面, 內部電性訊號亦可透過封裝材料 (引腳) 將之連接到系統,並提供 矽晶片免於受外力與水、濕氣、 化學物之破壞與腐蝕等。

空模

放入L/F

合模

離模

開模

灌膠

所謂IC封裝( IC PACKAGE )就是將IC晶 片(IC CHIP)包裝起來,其主要的功能與 目的有:

一、保護晶片避免受到外界機械或 化學力量的破壞與污染。

二、增加機械性質與可攜帶性。

IC 封裝成品構造圖

晶片托盤(DIE PAD)

晶片(CHIP)

L/F 內引腳 (INNER LEAD)

熱固性環氧樹脂 (EMC)

L/F 外引腳 (OUTER LEAD) 金線(WIRE)

產品轉角

產品表面 Ejector pin mark

產品前端

產品尾端 Pin 1 產品邊綠 釘腳 腳尖 釘架 肩部

1.去膠(Dejunk)的目的:

所謂去膠,是指利用機械模具將大腳間的廢膠去除; 亦即利用沖壓的刀具(Punch)去除掉介於膠體 (Package)與障礙槓(Dam Bar)之間的多餘膠體。

(PMC 封膠後烘烤)

Dejunk/Trim (DT 去膠去緯)

Solder Plating (SP 錫鉛電鍍)

Top Mark (TM 正面印碼)

Forming/Singular (FS 去框/成型)

Lead Scan (LS 檢測)

Packing (PK 包裝)

傳統 IC 封裝流程

Production Technology Center

Die Bond Plasma

Wire Bond

Epoxy Dispensing

Ball Placement

Plasma

Heat Slug Attach

Molding

MD(封膠) (Molding)

BM(背印) (Back Mark)

PMC(烘烤) (Post Mold Cure)

F/S(成型/去框)

去緯位置

外腳位置

3.去框(Singulation) 的目的:

將已完成蓋(Mark)製 程的Lead Frame,以沖 模的方式將聯結桿(Tie Bar)切除,使Package 與Lead Frame分開,方 便下一個製程。

Tie Bar

4.成型(Forming)

海

的目的:

鷗

將已去框(Singulation) 型

去膠/去緯 (Dejunk / Trimming)

去膠/去緯後

去膠/去緯前

海 鷗 型

插 入 引 腳 型 成型前 J 型

傳統IC 成型 Forming

Forming punch

Forming anvil

BGA 封裝流程

Production Technology Center

TE-BGA Process Flow(Th

2.去緯(Trimming)的目的:

去緯是指利用機械模具將大腳間金屬連接桿切除。由於導線架 (Lead Frame)內腳(Inner Lead)已被膠餅(Compound) 固定於Package裡,利用Punch將Dam Bar切斷,使外腳(Out Lead)與內部線路導通,成為單一通路而非相互連接。

(Form/Singulation)

TM(正印) (Top Mark)

MC(烘烤) (Mark Cure)

LS(檢測)

(lead Scan)

F/T(功能測試)

(Function/Test)

D/T(去膠/去緯) (Dejunk/Trim)

SP(電鍍)

(Solder Panting)

PK(包裝) (Packing)

Package之Out Lead以連

續沖模的方式,將產品腳

引 腳

彎曲成所要求之形狀。

插

入

型

J 型 成型前

F/S產品之分別,在傳統IC加工中,依照腳的 型狀來區分有以下幾種:

1. 引腳插入型:以P-DIP(P1)為主。

2.海鷗型:以QFP、TSOP、 TSSOP、 SOP 、 LQFP等產品為主。

3.J型腳:以PLCC、SOJ等產品為主。

入出料主要是將導線架 ( Lead Frame)由物料 盤 (Magazine)送上輸送架 (Bar or Bridge)進入模具 內做沖切;在機檯中,入出 料機構的夾具動作大多以氣 壓作動。

WIRE BOND (WB)

PREMOLD-BAKE (PB)

MOLDING (MD)

POST-MOLD-CURE (PMC)

DEJUNK/TRIM (DT)

若以封裝材料分類可分為:

1.陶瓷封裝

2.塑膠封裝

1.陶瓷封裝(CERAMIC PACKAGE):

適於特殊用途 之IC(例:高頻 用、軍事通訊 用)。