余三码计数器

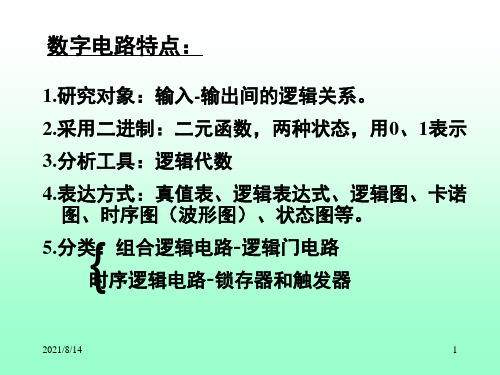

数字集成电路考试 知识点

数字集成电路考试知识点一、数字逻辑基础。

1. 数制与编码。

- 二进制、十进制、十六进制的相互转换。

例如,将十进制数转换为二进制数可以使用除2取余法;将二进制数转换为十六进制数,可以每4位二进制数转换为1位十六进制数。

- 常用编码,如BCD码(8421码、余3码等)。

BCD码是用4位二进制数来表示1位十进制数,8421码是一种有权码,各位的权值分别为8、4、2、1。

2. 逻辑代数基础。

- 基本逻辑运算(与、或、非)及其符号表示、真值表和逻辑表达式。

例如,与运算只有当所有输入为1时,输出才为1;或运算只要有一个输入为1,输出就为1;非运算则是输入和输出相反。

- 复合逻辑运算(与非、或非、异或、同或)。

异或运算的特点是当两个输入不同时输出为1,相同时输出为0;同或则相反。

- 逻辑代数的基本定理和规则,如代入规则、反演规则、对偶规则。

利用这些规则可以对逻辑表达式进行化简和变换。

- 逻辑函数的化简,包括公式化简法和卡诺图化简法。

卡诺图化简法是将逻辑函数以最小项的形式表示在卡诺图上,通过合并相邻的最小项来化简逻辑函数。

二、门电路。

1. 基本门电路。

- 与门、或门、非门的电路结构(以CMOS和TTL电路为例)、电气特性(如输入输出电平、噪声容限等)。

CMOS门电路具有功耗低、集成度高的优点;TTL门电路速度较快。

- 门电路的传输延迟时间,它反映了门电路的工作速度,从输入信号变化到输出信号稳定所需要的时间。

2. 复合门电路。

- 与非门、或非门、异或门等复合门电路的逻辑功能和实现方式。

这些复合门电路可以由基本门电路组合而成,也有专门的集成电路芯片实现其功能。

三、组合逻辑电路。

1. 组合逻辑电路的分析与设计。

- 组合逻辑电路的分析方法:根据给定的逻辑电路写出逻辑表达式,化简表达式,列出真值表,分析逻辑功能。

- 组合逻辑电路的设计方法:根据逻辑功能要求列出真值表,写出逻辑表达式,化简表达式,画出逻辑电路图。

2. 常用组合逻辑电路。

模拟信号与数字信号知识介绍

模拟信号

3V

模数转换器 0 000 001 1 数字输出

10

20

30

40

50

60

70

80

90

100

t/ms

0000 0100 0000 0011 0000 0010

1.1.4.数字信号的描述方法

1. 二值数字逻辑及其表示 二值数字逻辑 在数字电路中, 0、1组成二进制数可以表示数量大小,也 可以表示两种对立的逻辑状态。 0、1表示的两种对立逻辑状态的逻辑关系----二值数字逻辑 表示方式 (1) 在电路中用低、高电平表示0、1两种逻辑状态

常用方法是“按权相加”。 二、十进制数转换成二进制数: 小数部分 1. 整数部分用“辗转相除” 法: 将十进制数连续不断地除以2 , 直至商为零, 所得余数由低位到高位排列,即为所求二进制数 2 .小数部分用“辗转相乘”法:

整数部分

例如: (11)10==( ? )2

2 2 2 2 11 5 2 1 0

二、一般表达式:

系数

( N )10

i

K 10 ,

i i

位权

K i [0 9]

在数字电路中,计数的基本思想是要把电路的状 态与数码一一对应起来。显然,采用十进制是十分不 方便的。它需要十种电路状态与之对应。要想严格区 分这十种状态是很困难的。

1.2. 2

一、特点

二进制

六、优点 :

十六进制在数字电路中,尤其在计算机中得到广泛的应用, 因为:

第一、与二进制之间的转换容易

第二、计数容量较其它进制都大。假如同样采用四位数码, 二进制最多可计至 1111

B

= 15

《数字电路与逻辑设计》综合练习题及解答

《数字电路与逻辑设计》综合练习题及解答第一部分习题一、填空1.将十进制数转换成等值的二进制数、十六进制数。

10 = 2= 162.10= 余3BCD= 8421BCD 3.16= 24.一位二进制数只有2个数,四位二进制数有个数;为计64个数,需要位二进制数。

5.二进制数2的等值八进制数是8。

6.二进制数2的等值十进制数是10。

7.欲对100个对象进行二进制编码,则至少需要位二进制数。

8.二进制数为000000~111111能代表个十进制整数。

9.为将信息码10110010配成奇校验码,其配奇位的逻辑值为;为将信息码01101101配成偶校验码,其配偶位的逻辑值为。

10.格雷码的特点是。

11.n变量函数的每一个最小项有个相领项。

12.当ij时,同一逻辑函数的两个最小项mimj=。

2n113.n变量的逻辑函数,mi为最小项,则有mi=。

i014.逻辑函数FABCD的反函数F=。

15.逻辑函数FA(BC)的对偶函数F是。

16.多变量同或运算时,=0,则xi=0的个数必须为。

17.逻辑函数F(A,B,C)1C18. 逻辑函数F(A,B,C,D)( )。

19.逻辑函数F(A,B,C)(ABC)(ABC)的最简与或式为。

20.巳知函数的对偶式F(A,B,C,D)ABCDBC,则它的原函数F =。

* * * * * 21.正逻辑约定是、。

22.双极型三极管截止状态过渡到饱和状态所需的过渡时间称为时间,它时间和时间两部分组成,可用等式描述。

23.双极型三极管饱和状态过渡到截止状态所需的过渡时间称为时间,它时间和时间两部分组成,可用等式描述。

1。

AB的最小项表达式为F(A,B,C)=m(1,2,3,4,8,10)(0,12,14)的最简与或式为F=24.三极管反相器带灌电流负载时,负载电流的方向是从,此时反相器输出电平。

25.三极管反相器带拉电流负载时,负载电流的方向是从,此时反相器输出电平。

26.输入端的噪声容限说明。

《数字电路制作与测试》习题册(三)

《数字电路制作与测试》习题册(三)项⽬三计数器的设计与调试主要知识点:⼀、填空题1. 时序逻辑电路的输出不仅与有关,⽽且与有关。

2. 时序逻辑电路中的存储电路通常有两种形式:和。

3. 是构成时序逻辑电路中存储电路的主要元件。

4. 锁存器和触发器是构成时序逻辑电路中的主要元件。

5. 按逻辑功能分,触发器有、、、触发器等⼏种。

6. 触发器按照逻辑功能来分⼤致可分为种。

7. 触发器是构成逻辑电路的重要部分。

8. 触发器有两个互补的输出端Q 、Q ,定义触发器的0状态为,1状态为,可见触发器的状态指的是端的状态。

9. 触发器的两个输出端Q 、Q ,当0,1Q Q ==时,我们称触发器处于。

10. 触发器的状态指的是的状态,当1,0Q Q ==时,触发器处于。

11. 触发器有2个稳态,存储4位⼆进制信息要个触发器。

12. 因为触发器有个稳态,6个触发器最多能存储⼆进制信息。

13. ⼀个有与⾮门构成的基本RS 触发器,其约束条件是。

14. ⼀个基本R S 触发器在正常⼯作时,它的约束条件是R +S =1,则它不允许输⼊S = 且R = 的信号。

15. 与⾮门构成的基本RS 锁存器输⼊状态不允许同时出现R = S = 。

16. 与⾮门构成的基本RS 锁存器的特征⽅程是,约束条件是。

17. 由与⾮门构成的基本RS 锁存器其逻辑功能有种。

18. 由与⾮门构成的基本RS 锁存器正常⼯作时有三种状态,分别是01R S =输出为,10R S = 输出为,11R S =输出为。

(0状态/1状态/保持状态)。

19. 与⾮门构成的基本RS 锁存器当Q=1时,R = ,S = 。

20. 与⾮门构成的基本RS 锁存器当Q=0时,R = ,S = 。

21. 锁存器和触发器的区别在于其输出状态的变化是否取决于。

22. 触发器的输出状态变化除了由输⼊信号决定外还取决于。

23. 和共同决定了触发器输出状态的变化。

24. 钟控RS 触发器的约束条件是。

数字逻辑课程三套作业及答案资料

数字逻辑课程作业A、单选题。

1.(4 分)如图xl-229某一译码器的输出端共有臼种不的组颌U其输入端備几个输入线? (A)3;(B J4;(0)5; 1D16A.(A)B.(B)C.(C)D.(D)知识点:第五章解析第五章译码器2.(4 分)如图xl-82F图所示河一逻辑电路,八"是输入端,F是输出端,则其输出与输入关系式是,{AiiA+B}iC+ DiE; .B^A+B+C+p-FE); iC) (A +云)QO+童);(D)AB[CD+Ei(C )A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(A.NB.2NC.N2次方D.2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(B. B.2nC.C. 2n —1D. D . 2n-2n知识点:第九章解析第九章集成计数器5.(4 分)如图X1-293D )的计数器。

D )个。

在数字系统中其信号系仅貝E与即高电位与低电位两种: 迢】依电压犬小不等而定;依电流大小不等而定;①〕看需要而定A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述6.(4 分)如图X1-317和项#只式的基本架构矢何?| A A'A ND—MAXD • IB i A XD—OR;(Q AND ―A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4 分)EPROM 是指( C )A.A、随机读写存储器B. B、只读存储器C.C、光可擦除电可编程只读存储器R? (DiO罠一AND(D )D.D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4 分)如图xl-407属于近似的不连续表示法丸?〔A]模拟表示法;|空数字表示法;1匚凰寸数表示法;|=>线性系统)°A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使( A )A.J=D,K=D 非B. B. K=D,J=D 非C. C.J=K=DD. D.J=K=D 非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B )个触发器。

数字电路-复习大纲(四川大学)

包含2n个方格:2、4、8

包围的方格为矩形块

包围圈越大越好,越少越好

方格可以被重复包围,但每个包围圈内必需有新的方格

所有的1都要被包围住

充分考虑随意项

3.合并后的最小项之和即为最简与或表达式。 P37 习题1.2.2 1.4.2 1.6.1

2021/P8/1644 习题2.1.4 2.2.3 2.2.4

2一021位/8/1的4 权数(位权)是 Ri 。

3

②数制间的转换

二进制与十六进制数、八进制数之间的转换

24=16,四位二进制数对应一位十六进制数。 23=8, 三位二进制数对应一位八进制数。 举例:

3AF.2H = 0011 1010 1111.0010 = 1110101111.001B 3 A F2

2021/8/14

15

LA B A B A B

A

=1

L

B

用与非门实现

A& B

A& B

≥1

L

L A B A B A B A B A B • A B

2021/8/14

A& B

A& B

&

L

16

无反变量输入

LABA B A B A B A A B B

A A B B A B

1.变量值只有0和1,且只表示两种对立的逻辑状态,不表示 数量的大小。

2.表达方式:真值表--将输入变量的各种可能取值和相应函数

值排列在一起而组成的表格。

逻辑符号--规定的图形符号。

逻辑函数表达式--L=f(A、B…)

语句表、梯形图等。

2021/8/14

9

3.逻辑变量有原变量和反变量两类,普通代数中没有反变量。

8421BCD码格雷码余3码编码方法

8421BCD码格雷码余3码编码方法编码是信息处理领域中常见的一种技术,用于将数据转换为特定的编码形式,以便在传输或存储过程中更加高效地使用和处理数据。

在计算机科学和电子通信中,8521BCD码、格雷码和余3码是常用的编码方法之一、下面将详细介绍这三种编码方法。

1.8421BCD码:8421BCD码即二进制码-十进制码。

它使用4位二进制码(对应16进制的0-F)来表示一个十进制数。

8421BCD码的特点是具有固定的位权和容易进行十进制和二进制之间的转换。

其中,每一位的位权从右往左依次为8、4、2、1、例如,十进制数7的8421BCD码表示为01118421BCD码虽然具有固定的位权,但存在编码浪费问题。

由于每一位只能表示4位二进制数,因此在表示一个十进制数时需要使用更多的二进制位数。

例如,十进制数15的8421BCD码表示为00010101,占用了8位二进制数,而十进制数15在二进制中可以用4位数表示(即1111)。

因此,8421BCD码的编码效率较低。

2.格雷码:格雷码又称为反射码,它是一种二进制码的变形,相邻的两个码之间只有一个位数的差异。

格雷码的特点是编码过程中只有一位发生改变,这样在传输或存储过程中更加高效,避免了传统二进制码由于1位变化导致的多位错误。

例如,对于3位格雷码来说,它由000、001、011、010、110、111、101、100这样的序列组成。

格雷码在数字电路设计、数据通信和精确测量等领域具有广泛的应用。

例如,在数字电路设计中,格雷码可以用作计数器的输入,以避免计数器在计数过程中产生不稳定的状态。

3.余3码:余3码是一种类似于格雷码的编码形式,它的特点是相邻的两个码之间只有一位数的差异,并且不能存在三个连续的1或0。

余3码的编码过程通常使用状态转换表来确定。

例如,对于3位余3码来说,它由000、001、010、012、021、022、122、120、110、111、101、100这样的序列组成。

“编码与译码”三级工程项目体系的设计研究

“编码与译码”三级工程项目体系的设计研究作者:樊敏赵灿杨金汪海波鲁世斌来源:《电脑知识与技术》2024年第05期摘要:数字技术基础课程是大电类必修的专业基础课程,编码器与译码器是其中重要的教学内容。

传统的教学方案存在着知识点碎片化、理论与实践分离等问题,文章将编码器与译码器这两部分教学内容进行了融合,用“小-中-大”三级工程训练项目重构教学内容,由浅入深地培养学生形成“知识点-知识链-复杂系统”的工程思维模式,并通过对项目设计方案的不断改进、逐级优化,“螺旋递进”地培养学生解决复杂工程问题的能力,从而实现学以致用、知行合一的教学目标,提高教学效果与人才培养质量。

关键词:三级工程项目训练体系;编码器;译码器;Multisim;数字电路教学中图分类号:TP311 文献标识码:A文章编号:1009-3044(2024)05-0131-040 引言数字电子技术基础课程(以下简称“数电”)是大电类专业必修的专业基础课程,在专业培养课程体系中承上启下、举足轻重[1]。

然而,在传统的教学模式中,每门课都是一个独立的体系,强调的是知识体系的完备性,其中译码器与编码器是非常重要的教学内容[2]。

根据传统的教学方案,“编码器”讲授优先编码器74LS148的管脚功能和扩展[3]。

“译码器”讲授译码器的管脚功能、扩展和利用其实现一般组合逻辑函数的方法,并介绍七段显示译码器。

但是从学生的角度看,知识点繁多且零碎,不知道知识点之间的关联,更不知道学了“有什么用”“怎么用”[4-5]。

所以,本文对编码器与译码器这两个知识点进行了融合优化。

通过采用“小-中-大”三级工程项目训练体系重构教学内容,把零碎的知识点串联起来形成知识链,再由知识链组成复杂系统[6],并通过对项目设计方案的不断改进、逐级优化,“螺旋递进”地培养学生解决复杂工程问题的能力,实现“学以致用、知行合一”的教学目标,提高教学效果与人才培养质量[6]。

1 融合优化思路在传统的教学安排中,一般先讲编码器再讲译码器。

第四章 时序逻辑电路(2)

而译码器地址输入A2A1A0分别对应Q1Q2Q3(注意,不能 看成A2A1A0对应Q3Q2Q1),所以:

DIL A2 A1 A0 A2 A1 A0 A2 A1 A0 Q1Q2Q3 Q1Q2 Q3 Q1Q2 Q3

两个控制信号S1、S0实现对数据保持、左移、右移、 置数等四种功能的选择;这一选择是通过S1、S0会同四个 与或非门构成四个4选1数据选择器来实现的。

DIR为右移串行输入端,DIL为左移串行输入端;

D0、D1、D2和D3是并行输入端。

Q0和Q3分别是左移和右移时的串行输出端。

Q0、Q1、Q2和Q3为并行输出端。

图4.47给出了74LS194A的逻辑符号和引脚排列。

根据上述功能分析,可以得到其功能如表4.16所示。

【例4.8】试用二片74LS194A扩展成8位双向移位寄存器。

解,将低位片的Q3连接到高位片的DIR,同时将高位片的 Q0连接到低位片的DIL如图4.48,即可将二片74LS194A扩 展成8位双向移位寄存器。

【例4.4】用74LS160组成48进制计数器。 解:因为N=48,而74LS160为模10计数器,所以要 用两片74LS160构成此计数器。 先将两芯片采用同步级联方式连接成100进制计数器。

然后再借助74LS160异步清零功能,当计数值为48(十 进制)时,(此时计数器输出状态为0100 1000),即当高 位片(2)的Q2和低位片(1)的Q3同时为1,使两芯片异步 清零端有效,则计数器立即返回0000 0000状态。

(1)根据设计要求,设定逻辑状态,导出对应的原始状态 图或状态表。

数字电路逻辑设计 第六章2

(一)反馈清零法

74160是模10计数器,要实现模853计数,须用三片74160级联。 ⑴先设计模1000计数器: M = M1×M2 ×M3=10 × 10 × 10=1000 ☆ 利用各片间进位信号快速传递方法,组成计数模值为1000计数器。 ⑵ 用异步清0法,使计数器计数脉冲输入到第853个脉冲时产整体置0 信号 使计数器返回到初始状态0000。 计数范围:

画出逻辑图如图

D2 D1 D0 CTT D3 CTP CTRDIV16 CO CT161 CR

LD

1

Q 3 Q2 Q 1 Q 0

0

0

&

O

0

(二)同步预置法

例:用四位同步二进制计数器74161设计余3BCD码计数器。

解:余3BCD码计数器的状态转移图如图所示

0011 1100

LD Q3Q2

画出逻辑图

&

1 CTP CR CTT 1

74161(1)

D0D1D2D3

Q0Q1Q2Q3 CO

CTP CTT

CR

74161(2)

D0D1D2D3

Q0Q1Q2Q3 CO

LD

LD

CP

(二)同步预置法

方法三、整体同步反馈置数: (利用进位输出作为置数译码信号) 计数范围196-255,当计数器计到255时,CO=1,使 两片74161置数控制端 /LD=0,下一个CP到来时置数。 预置输入=256-60=196 (196)10=(11000100)2 低位片预置数:0100 高位片预置数:1100

工作波形图: 5 6 7 8

9

10

6.5采用中规模集成器件设计任意进制计数器

1. M<N,N为单片计数器的最大计数值

数字电路基础-期末考题

一.填空1.(11101.01)2 =( )10 =( )162.(10010101)8421BCD = ( )10 =( )余3码(12)10 =( )格雷码(143.375)10 = ( ) 2 = ( )16 3.( 110001 )补码= ( )原码 = ( ) 104.若两个2位二进制数A =A 1A 0和B =B 1B 0相等,则表明A 1⊕B 1= ;而A 0⊙B 0=________。

5.已知最小项ABC ,其对应同样编号的最大项是_7M A B C '''=++___。

6. 逻辑函数式为()B C D A B +⋅+⋅,由对偶定理和反演定理写出此函数对偶函数为( )、反函数为( )。

7.若逻辑函数)5,2,1(),,(∑=m C B A F ,则(,,)F A B C M =∏( )。

8.在TTL 的三态门、OC 门、与非门、异或门电路中,为实现“线与”逻辑功能应选 门;为实现总线系统,应选 门。

9.逻辑函数的两种标准形式是 和 。

10.目前我们所学的双极型集成门电路和单极型集成门电路的典型电路分别是 电路和 电路。

11.对8路数据进行选择传输,所用的数据选择器的地址最少 位。

12.设计一个365进制计数器最少需要 片74LS160。

13.JK 触发器的状态方程为*Q Q '=,则其驱动方程中J = ( ) ,K = ( )。

14.N 个触发器构成的扭环形计数器中,无效状态有 ( ) 个。

15.施密特触发器的主要用途是 、 、 。

16.施密特触发器有 个稳定状态,多谐振荡器有 个稳定状态。

17.在一个4位D/A 转换器中,若是权电阻型网络,则其电阻取值有____种;若是倒T 形网络,则其电阻取值有_________种。

18.具有双极性输出的三位D/A 转换器,其参考电压源为-8V ,当输出电压为-3V 时,其输入的数字量为 。

19.已知被转换的信号的上限截止频率为10kHz ,则A/D 转换器的采样频率应高于 Hz ;完成一次转换所用的时间应小于 。

《数字电子技术》黄瑞祥_第五章习题答案

第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。

解时序图:CPQ0Q1Q2Q35-2分析题5-2图所示电路,画出电路的状态图。

解5-3 JK触发器组成5-3图所示电路。

分析该电路为几进制计数器,并画出电路的状态图。

该电路为五进制计数器5-4JK触发器促成如图5-4图所示的电路。

(1)分析该电路为几进制计数器,画出状态图。

= 1,电路为几进制计数器,画出其状态图。

(2)若令K3解:(1为7进制计数器5-5 试画出题5-5图(a)所示电路中B,C端的波形。

输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。

1 5 6 123456789 10 11 12 13 14 15 16 17 18 19CPAQ0Q1BC5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。

该电路能够自启动5-7 分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。

由状态图可见,电路图能够自启动5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。

解:状态图:功能分析:根据状态图可知:电路为三位格雷码发生器。

5-9 画出题5-9图所示的状态图和时序图。

解:状态图:时序图:5-10 如题5-10图所示,FF0为下降沿触发的JK触发器,FF1为上升沿触发的D触发器,试对应给定的RD ,CP,J,K的波形,画出Q,Q1的波形。

5-11图所示。

解:电路图:态图如题5-12图所示。

解:电路图如下:5-13 试用下降沿触发的边沿型JK触发器和与非门,设计一个按自然态序进行的七进制同步加法计数器。

解:电路图:5-14 试用上升沿触发的边沿型D触发器和与非门,设计一个按自然态序进行计数的十进制同步加法计数器。

解:电路图:5-15 试用JK触发器设计一个同步十进制计数器,要实现的状态图如题5-15图所示。

解:电路图如下:5-16 试设计一个具有如题5-16图所示功能的计数器电路,图中M为控制变量。

昆明理工大学 数字电子技术 历年真题

昆明理工大学试卷(A)考试科目:数字电子技术A 考试日期:命题教师:集体学院:专业班级:学生姓名:学号:任课教师:课序号:考试座位号:一、填空题(每题3分,共计39分)1、完成把输入数据分配给2N路输出通道的逻辑器件叫。

2、普通编码器和优先编码器的主要区别是。

3、在逻辑代数中,已知X+Y=Z+Y,则X=Z。

这一命题对吗?答:。

在逻辑代数中,已知XY=ZY,则X=Z。

这一命题对吗?答:。

4、TTL触发器按结构不同可以分为四种,它们是,,和。

5、要实现把1KH Z的正弦波转换为同频率的矩形波,可选用电路完成。

6、设在74系列TTL门电路中,已知V OH≥3.2V, V OL≤0.4V ; I IL≤-1.6mA ,I IH≤40μA,I OL(max)=16mA,I OH(max)= -0.4mA 。

问该门的扇出系数N O=(设每个负载门只接一个输入端)。

若V ILmax=0.8V ,V IHmin=2V ,噪声容限V NL= 和V NH= 。

7、对COMS或非门电路多余输入端的处理办法有和等。

8、逻辑函数式)(DE A C B A Y ++=的对偶式为: 。

9、RAM 字扩展的方法是利用新增加的地址线去控制各片RAM 的 端,如果用容量为1K ×4的芯片组成16K ×8存储器,所需的片数为 。

10 、由555定时器组成的施密特触发器,在5脚接入6V 电压后,其上限阈值电压和下限阈值电压分别为 和 。

11、试分析计数器在1=M 和M=0时各为几进制( )、( )。

12、在4位权电阻网络D/A 转换器中,若取V REF =5V ,当输入数字量为d 3d 2d 1d 0=0101时输出电压为( )。

13、某模/数转换器的输入为0~10V 模拟电压,输出为8位二进制数字信号(D 7 ~ D 0)。

若输入电压是2V ,则输出的二进制数字信号为 。

二、化简下列逻辑函数(方法不限,每题6分,共18分) 1、Y=C B A +A +B+C2、D C A D C A C B A D C ABD ABC Y +++++=3、Y(A,B,C,D)=∑m(2,3,7,8,11,14),给定约束条件为m0+m5+m10+m15=0三、某医院有一、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

74LS系列功能表

74ls01 2输入四与非门 (oc)74ls02 2输入四或非门74ls03 2输入四与非门 (oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc)74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展) 74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展) 74ls53 四路2-2-3-2输入与或非门(可扩展) 74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端)74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出) 74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步) 74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步) 74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制) 74ls191 同步可逆计数器(bcd,二进制) 74ls192 同步可逆计数器(bcd,二进制) 74ls193 同步可逆计数器(bcd,二进制) 74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制) 74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出) 74ls241 八缓冲器/线驱动器/线接收器(原码三态输出) 74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出) 74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器。

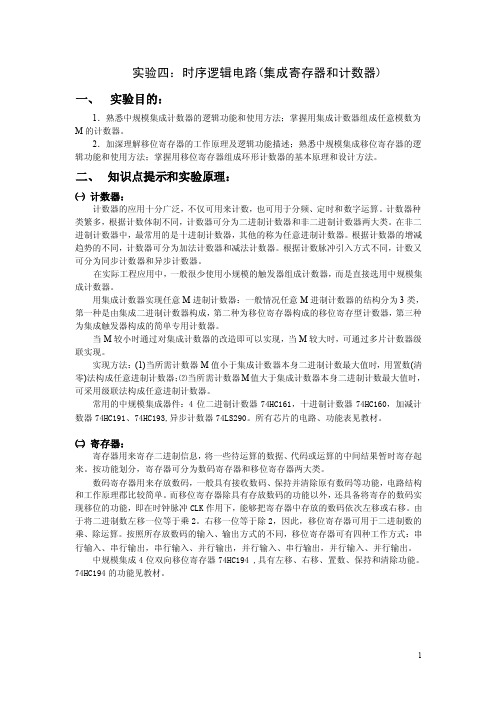

数电实验四——精选推荐

实验四:时序逻辑电路(集成寄存器和计数器)一、实验目的:1.熟悉中规模集成计数器的逻辑功能和使用方法;掌握用集成计数器组成任意模数为M的计数器。

2.加深理解移位寄存器的工作原理及逻辑功能描述;熟悉中规模集成移位寄存器的逻辑功能和使用方法;掌握用移位寄存器组成环形计数器的基本原理和设计方法。

二、知识点提示和实验原理:㈠计数器:计数器的应用十分广泛,不仅可用来计数,也可用于分频、定时和数字运算。

计数器种类繁多,根据计数体制不同,计数器可分为二进制计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其他的称为任意进制计数器。

根据计数器的增减趋势的不同,计数器可分为加法计数器和减法计数器。

根据计数脉冲引入方式不同,计数又可分为同步计数器和异步计数器。

在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。

用集成计数器实现任意M进制计数器:一般情况任意M进制计数器的结构分为3类,第一种是由集成二进制计数器构成,第二种为移位寄存器构成的移位寄存型计数器,第三种为集成触发器构成的简单专用计数器。

当M较小时通过对集成计数器的改造即可以实现,当M较大时,可通过多片计数器级联实现。

实现方法:(1)当所需计数器M值小于集成计数器本身二进制计数最大值时,用置数(清零)法构成任意进制计数器;⑵当所需计数器M值大于集成计数器本身二进制计数最大值时,可采用级联法构成任意进制计数器。

常用的中规模集成器件:4位二进制计数器74HC161,十进制计数器74HC160,加减计数器74HC191、74HC193,异步计数器74LS290。

所有芯片的电路、功能表见教材。

㈡寄存器:寄存器用来寄存二进制信息,将一些待运算的数据、代码或运算的中间结果暂时寄存起来。

按功能划分,寄存器可分为数码寄存器和移位寄存器两大类。

数码寄存器用来存放数码,一般具有接收数码、保持并清除原有数码等功能,电路结构和工作原理郡比较简单。

8253实验

浙江工业大学计算机学院实验报告一实验名称8253实验教师雷艳静日期2014、12、15一、实验内容与要求1、1实验内容(1)计数器0方式2实验将计数器0设置为方式2,计数器初值为任意数(二进制8位,实验中我们就是24),将计数初值通过编程实现逐个得输出显示在屏幕上,而编程当中字符就是ASCII码,我们要将其转换成十进制输出显示.手动开关输入单脉冲,通过编程计数初值就可以显示了,而且每输入一次单脉冲计数初值就减1。

(2)计数器方式3将计数器0、计数器1分别设置为方式3,计数初值设为1000。

实际上就就是实现了8253得分频实验。

实验内容相对简单,我们分别设置计数初值为16位,分两次读写,计数器0、计数器1工作于方式3,再用二进制格式计数,因为方式3得功能即为周期性输出方波,随着方波周期性得变化,引起电流得变化,实验中LED灯得闪烁变化就可以体现计数器0、计数器1分别写入时8253分频功能。

1、2实验要求(1)实验效果:程序执行后应该在屏幕上显示出我们事先在程序里写好得计数初值,手动每按一次单脉冲开关,计数初值就在屏幕上减1显示一次,而且显示得就是十进制数。

(2)实验效果:程序执行后我们可以观察事先在硬件上连接得好LED灯,LED灯一闪一灭变化。

二、实验原理与硬件连线2、1实验原理TPC-USB平台上有一块8253定时/计数芯片,除了片选引脚,其她信号都已接好。

可编程得定时/计数器8253在硬件组成、外形引脚上都就是兼容得.8253得内部有6个模块:数据总线缓冲、读/写控制逻辑、控制字寄存器与3个结构相同且完全独立得计数器。

①数据缓冲器:就是8253与系统数据总线连接得接口电路,它能寄存3个数据:CPU 向8253写入工作方式得命令字;CPU向计数寄存器写入得计数初值;从计数器读出得当前计数值。

②读/写控制逻辑:用来接收CPU发出得读/写信号、片选信号与内部端口地址信号,选择读出或写入寄存器,并且确定数据传输得方向.③控制字寄存器:用来暂存CPU送来得控制字,用来选择计数器并确定该计数器得工作方式、读写格式与计数得数制。

项目七--脉冲计数器(葛中海)

项目七脉冲计数器一、教学目标● 认识CD40192、CD4511,熟悉它们逻辑功能。

● 认识七段数码管的结构和电路控制方式。

● 理解BCD码的概念及七段译码的含意。

● 掌握整个电路的工作原理,了解脉冲计数器的应用。

二、电路结构本电路可分为几大部分,它们分别为时钟电路、BCD码计数电路、译码驱动电路和七段数码显示电路。

1.时钟电路:由555定时器和外围阻容元件组成;2.BCD码计数电路:由四片CD40192组成;3.译码驱动电路:由四片CD4511组成;4.七段数码显示电路:由四片七段数码管组成。

三、认识特殊器件1.七段数码管a~和如图7.1是七段数码管原理图符号,图7.2是七段数码管印制板图符号。

它由七段g逗点dp共八只发光二极管组成,而这八只发光二极管又可接成“共阴极”(如图7.a)和“共阳极”(如图7.2b)。

图7.1a 数码管原理图符号图7.2b 数码管电路板图符号对于“共阳极”数码管来说,若在任意阴极接低电平,相应段划点亮。

对于“共阴极”数码管来说施加电压正好相反。

a)共阳极 b)共阴极图7.2 数码管内部接线图2.CD40192CD40192是COMS可预置递增/递减BCD码计数器(COMS Presettable Up/Down Counters)。

它的管脚可以根据功能分成几部分,图7.3为引脚图,图7.4为逻辑图。

①.预置部分J为预置当CD40192处于递减计数状态,首先需要预置数据,即递减开始的起始数。

1J-4 PRE (逻辑图为ENABLE)是预置使能端,上划线代表低电平有效;如果接高数据端,EN电平就是禁止预置功能,本项目制作就采用禁止预置模式。

②.递增/递减时钟输入:U CP /(Up CP /)递增时钟输入,D CP /(Down CP /)递减时钟输入,也就是说CD40192需要在递增时钟U CP /或递减时钟D CP /的控制下实现计数,递增/递减计数在信号下降沿有效。

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛/b bs/反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门74LS08│1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门74LS10│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ 8输入与非门74LS30│ 1 2 3 4 5 6 7│ ________└┬—┬—┬—┬—┬—┬—┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或门74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或非门74LS02│14 13 12 11 10 9 8│___)│Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴—┴—┴—┴—┴—┴—┴┐双与或非门74S51│14 13 12 11 10 9 8│_____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│_______└┬—┬—┬—┬—┬—┬—┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴—┴—┴—┴—┴—┴—┴┐ 4-2-3-2与或非门74S64 74S65(OC门)│14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬—┬—┬—┬—┬—┬—┬—┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬—┬—┬—┬—┬—┬—┬—┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴—┴—┴—┴—┴—┴—┴┐双D触发器74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位锁存器74LS373 │20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND等.下面介绍一下常用的74芯片,以便大家在电路中遇到了查询----------------------------------------------------型号内容----------------------------------------------------74ls00 2输入四与非门74ls01 2输入四与非门(oc)74ls02 2输入四或非门74ls03 2输入四与非门(oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门(oc)74ls13 4输入双与非门(斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门(oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门(斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展) 74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展) 74ls53 四路2-2-3-2输入与或非门(可扩展) 74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端) 74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出) 74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步) 74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步) 74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制) 74ls191 同步可逆计数器(bcd,二进制) 74ls192 同步可逆计数器(bcd,二进制) 74ls193 同步可逆计数器(bcd,二进制) 74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制) 74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出) 74ls241 八缓冲器/线驱动器/线接收器(原码三态输出) 74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出) 74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器【发表评论】【告诉好友】【收藏此文】【关闭窗口】上一篇:74LS74引脚图(双D触发器)下一篇:DAC0832引脚图及接口电路。

余三码转换成2421码课程设计

学号:课程设计题目数字逻辑设计题目余三码转换成2421码学院计算机科学与技术专业计算机科学与技术班级姓名指导教师年月日目录一、课程设计任务书 (2)(一)课程设计题目 (2)(二)要求完成设计的主要任务 (2)(三)课程设计进度安排 (2)二、课程设计正文 (3)1设计目的 (3)2 题目理解和功能描述 (3)3 逻辑电路设计具体步骤 (4)3.1 第1步,根据余3码与2421码得具体组合,写出输出函数 (4)3.2 第2步,化简输出函数表达式 (5)3.3 第3步,根据激励函数表达式,画出逻辑电路图 (5)4设计中使用的集成电路名称及引脚编号 (6)4.1 集成电路74 LS 04 引脚编号 (6)4.2集成电路74 LS 08 引脚编号 (6)4.3集成电路74 LS 32引脚编号 (6)4.4 集成电路74LS 86 引脚编号 (7)5 电路图的连接、调试和测试 (7)5.1 电路图的连接 (7)5.2 电路图的调试和测试 (7)5.3 测试中出现的问题及分析解决 (7)5.4 调试和测试组合逻辑电路个人体会 (8)6 电路连接实物图和现象 (9)6.1集成电路连接图 (9)6.2实验现象 (10)7 余三码转成2421码电路设计总结和心得 (10)7.1余3码转成2421码电路设计总结 (10)7.2 课程设计心得 (11)三、本科生课程设计成绩评定表 (12)课程设计任务书学生姓名专业班级指导教师学院名称计算机科学与技术学院一、题目:余3码转换成2421 BCD 码原始条件:使用“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计余3码转换成8421 BCD 码。

二、要求完成设计的主要任务如下:1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计余3码转换成2421 BCD 码。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

--底层设计实体计数器163

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity v74hc163 is

port( clk,clr_l,ld_l,ctp,ctt : in std_logic;

d: in unsigned (3 downto 0); --置数输入

q : out unsigned (3 downto 0); --计数输出

rco : buffer std_logic); --进位输出end v74hc163 ;

architecture behave of v74hc163 is

signal iq : unsigned (3 downto 0);

begin

process(clk, ctt, iq)

begin

if clk'event and clk='1' then

if clr_l = '0' then

iq <= (others =>'0'); --同步清0

elsif ld_l ='0' then iq<=d; --同步置数

elsif rco ='1' then iq <= d; --计数满重新计数

elsif (ctt and ctp) ='1' then iq<= iq+1 ; --计数end if;

end if;

if (iq=15) and (ctt='1') then rco<='1'; --计到15进位else rco<='0';

end if;

q<=iq;

end process;

end behave ;

--底层设计实体与非门

library ieee;

use ieee.std_logic_1164.all;

entity nand_gate is

port

( a,b:in std_logic;

nand_result:out std_logic);

end nand_gate;

architecture behave of nand_gate is

begin

nand_result<=not(a and b);

end behave;

--底层设计实体非门

library ieee;

use ieee.std_logic_1164.all;

entity not_gate is

port( c:in std_logic;

not_result:out std_logic);

end not_gate;

architecture behave of not_gate is

begin

not_result<=not c;

end behave;

--底层设计实体与门

library ieee;

use ieee.std_logic_1164.all;

entity and_gate is

port( m,n: in std_logic;

and_result: out std_logic);

end and_gate;

architecture behave of and_gate is

begin

and_result<= m and n;

end behave;

--顶层设计实体

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity excess_3_code is --顶层实体

port( cp,ctto,ctpo,clr_lo,lb:in std_logic;

qo:buffer std_logic_vector(3 downto 0);

co:out std_logic);

end excess_3_code;

architecture behave of excess_3_code is

component v74hc163 is --component v74hc163 port(

clk,clr_l,ld_l,ctp,ctt:in std_logic;

d: in unsigned(3 downto 0);

q: buffer unsigned(3 downto 0);

rco: out std_logic);

end component;

component nand_gate is --component 与非port( a,b:in std_logic;

nand_result:out std_logic);

end component;

component not_gate is --component 非port( c:in std_logic;

not_result:out std_logic);

end component;

component and_gate is --component 与port( m,n:in std_logic;

and_result: out std_logic);

end component;

signal c1,c2:std_logic;

begin

G1:v74hc163 port map

(clk=>cp,clr_l=>clr_lo,ctp=>ctpo,ctt=>ctto,

ld_l=>c2,

d(0)=>'1',

d(1)=>'1',

d(2)=>'0',

d(3)=>'0',

q(0)=>qo(0),

q(1)=>qo(1),

q(2)=>qo(2),

q(3)=>qo(3));

G2:nand_gate port map

( a=>qo(2),b=>qo(3),nand_result=>c1);

G3:not_gate port map

( c=>c1, not_result=>co);

G4: and_gate port map

(m=>c1,n=>lb,and_result=>c2);

end behave;。