基于JTAG的ARM芯片系统调试

小板H—JTAG调试

ARM程序用小板H—JTAG在SRAM中调试程序:1.用ADS1.2打开程序,点击Options,选Configure Target,按下Add按钮,添加H-JTAG目录中的H-JTAG.dll文件。

2.启动H-JTAG程序,点Flasher选Stat H-Flash选项,在H-Flash菜单中点击Flash Selection,选择硬件的CPU型号,然后再点击Programming,按下Check按钮,如检测到CPU型号,则ARM板和PC建立通信。

3.选择ADS1.2中的片内SRAM项(DebugInExSRAM)编译程序,程序编译结束后如没有错误,按下Make按钮,再按RUN按钮,自动进入AXD软件程序。

4.如没有进入AXD软件,而是出现“The session……could not beloaded”的提示,点击确定并关闭ses文件路径选择菜单。

这时AXD 软件会自动运行,点击Options,进入Configure Target菜单,选择H-JTAG项按OK。

在File下拉菜单中选择load Image项,在弹出的路径选择菜单中添加程序目录下DebugInExSRAM目录下的*.asf文件。

5.在工具栏中,点击两次run键,SRAM程序调试OK。

ARM程序用小板H—JTAG在片内Flash中调试程序:1.用ADS1.2打开程序,点击Options,选Configure Target,按下Add 按钮,添加H-JTAG目录中的H-JTAG.dll文件。

2.启动H-JTAG程序,点Flasher选Stat H-Flash选项,在H-Flash菜单中点击Flash Selection,选择硬件的CPU型号,然后再点击Programming,按下Check按钮,如检测到CPU型号,则ARM板和PC 建立通信。

3.选择ADS1.2中的片内FLASH项(DebugInChipFlash)编译程序,程序编译结束后如没有错误,按下Make按钮,再按RUN按钮,自动进入AXD软件程序。

基于JTAG接口实现ARM的FPGA在线配置.

基于JTAG接口实现ARM的FPGA在线配置引言随着通信技术的发展,出现越来越多的无线接人技术,为了解决不同标准间的互通和兼容,人们提出了软件无线电(SoftwareDefinedRadio,SDR)技术。

SDR技术要求通信终端具有可重配置能力,根据特定通信网络情况,动态地改变调制/解调、编解码、交织/解交织等方案。

SDR终端的实现往往都是基于可重配置的硬件环境,如现场可编程逻辑阵列(FieldProgrammableGateArray,FPGA)、数字信号处理器(DigitalSignalProcessor,DSP),而不是专引言随着通信技术的发展,出现越来越多的无线接人技术,为了解决不同标准间的互通和兼容,人们提出了软件无线电(Sof tware Defined Radio,SDR)技术。

SDR技术要求通信终端具有可重配置能力,根据特定通信网络情况,动态地改变调制/解调、编解码、交织/解交织等方案。

SDR终端的实现往往都是基于可重配置的硬件环境,如现场可编程逻辑阵列(Field Programmable Gate Array,FPGA)、数字信号处理器(Digital Signal Processor,DSP),而不是专用集成电路(Application Specific Integrated Circuit,AS IC)等特定的硬件电路和芯片。

在线配置(In Sys—tem Programming,ISP)或者动态配置FPGA就是一种重要的SDR实现技术。

本文介绍作者开发实现的一种基于ARM的嵌入式Linux下通过JTAG接口动态配置FPGA的方法。

系统使用三星公司基于ARM9的S3C2410处理器芯片,Altera公司CycloneII系列的EP2C70 FPGA芯片,ARM处理器上运行基于S3C2410裁剪后的嵌入式Linux系统,内核版本为2.4.18。

1 FPGA的配置方式及配置文件Altera公司CycloneII系列FPGA芯片,是Altera公司推出的基于90 nm工艺制造、低成本的FPGA,主要面向数字终端、手持设备等对成本敏感的应用领域。

基于ARM开发的JTAG仿真器的调试设计.

基于ARM开发的JTAG仿真器的调试设计基于JTAG仿真器的调试是目前ARM开发中采用最多的一种方式。

大多数ARM设计采用了片上JTAG接口,并将其作为测试、调试方法的重要组成。

JTAG仿真器通过ARM芯片的JTAG边界扫描口与ARMCPU核通信,实现了完全非插入式调试,不使用片上资源,不需要目标存储器,不占用目标系统的任何端口。

由于JTAG调试的目标程序是在目标板上执行,使得仿真更加接近于目标硬件[1]。

目前针对嵌入式系统开发的调试工具品种繁多,如ARM公司的AXDdebugger软件基于JTAG仿真器的调试是目前ARM开发中采用最多的一种方式。

大多数ARM设计采用了片上JTAG接口,并将其作为测试、调试方法的重要组成。

JTAG仿真器通过ARM芯片的JTAG边界扫描口与ARM CPU核通信,实现了完全非插入式调试,不使用片上资源,不需要目标存储器,不占用目标系统的任何端口。

由于JTAG调试的目标程序是在目标板上执行,使得仿真更加接近于目标硬件[1]。

目前针对嵌入式系统开发的调试工具品种繁多,如ARM公司的AXD debugger软件与Mutil-ICE仿真器等。

但是大部分嵌入式调试工具价格过高,因此设计实现一种速度快、性能稳定、价格低廉、易于实现的ARM调试工具是十分必要的。

1 ARM JTAG调试原理ARM典型的调试系统结构如图1所示。

调试系统包括调试主机、仿真器和调试目标。

调试主机是一台运行调试软件(例如ADS)的计算机。

调试主机可以发出高层的调试命令,例如设置断点、访问内存等[2]。

仿真器用来将调试主机发出的高层调试命令转换为底层的ARM JTAG调试命令。

因为目标机无法识别调试主机发送来的高级命令,因此就需要仿真器将调试主机发出的高层调试命令转换为底层的ARM JTAG调试命令[3]。

在整个调试系统中起到重要的作用,其性能也决定了整个调试系统性能。

2 方案设计本文提出了一种采用PHILIPS公司的ARM7芯片LPC2148设计,具有USB2.0通信方式、高速稳定的ARM仿真器实现方案,如图2所示。

基于JTAG的ARM7TDMI处理器调试原理及实现

基于JTAG 的ARM7TDMI 处理器调试原理及实现刘文超,潘永才(湖北大学 湖北武汉 430062)摘 要:针对如何使用J TA G 接口对ARM7TDMI 处理器进行调试,介绍了J TA G 边界扫描结构及基本协议标准、ICE 2breaker 模块等与调试接口相关的内容,给出了两个运用J TA G 接口对ARM7TDMI 进行调试的实例加以验证。

在由计算机、WIGG L ER J TA G 和SmartArm2200组成的实际调试系统中,成功读取了ARM7TDMI 处理器的ID ,实现了程序的下载和调试。

实验结果表明,通过简单的J TA G 接口可以实现对基于ARM7TDMI 处理器的嵌入式系统的调试。

关键词:ARM ;J TA G;调试;ICE breaker中图分类号:TP36811 文献标识码:B 文章编号:1004-373X (2007)06-009-03Principle and R ealization of ARM7T DMI Processor Debug B ased on JTAGL IU Wenchao ,PAN Y ongcai(Hubei University ,Wuhan ,430062,China )Abstract :In order to explain how to use J T A G interface for debugging ,this paper introduces some information about the debug in 2terface ,such as the conception of J T A G boundary scan architecture and the ICE breaker module and so on.The paper offers two exam 2ples to explicate how to apply J T A G debug technique.The examples get correct results in the debug system.The results show that it is easy and efficiency to use J T A G interface in debugging embedded system based on ARM processor.K eywords :ARM ;J TA G;debug ;ICE breaker收稿日期:2006-08-08 J TA G 边界扫描即IEEE114911标准,全称为标准测试访问接口与边界扫描结构(standard test access port andboundary scan architecture ),该测试标准的优点在于将极其复杂的印制电路板测试变为具有良好结构性、可以通过软件简单而灵活地进行处理。

基于JTAG的ARM调试器实现

第24卷第2期 计算机应用与软件Vol 124,No .22007年2月 Computer App licati ons and Soft w are Feb .2007基于JTAG 的AR M 调试器实现陆 晗 潘雪增 平玲娣(浙江大学计算机学院 浙江杭州310027)收稿日期:2004-09-22。

国家863资助项目(编号:20022AA I Z1050)。

陆晗,硕士生,主研领域:嵌入式系统开发工具研究及开发。

摘 要 随着uClinux 应用与普及,移植uClinux 和在L inux 开发平台上设计嵌入式应用系统都迫切需要好的调试工具,而现有的W indows 下的调试工具很难用于L inux 系统。

介绍如何在G DB 的基础上,低成本实现嵌入式板的JT AG 调试。

关键词 AR M JT AG G DBAR M D EBUGGER BASED O N JTAGLu Han Pan Xuezeng Ping L ingdi(School of Co m puter Science,Zhejiang U niversity,Hangzhou Zhejiang 310027,China )Abstract W ith the popularity of the uClinux system,it beca me very i m portant t o port and debug the uClinux system on L inux .I n this pa 2per,we will intr oduce a cheap res olvent based on JT AG and G DB,which can give better support f or porting and debugging the uClinux system.Keywords AR M JT AG G DB0 前 言为了提高自主知识产权,打破技术垄断,开放源码的G NU 工程越来越受到重视。

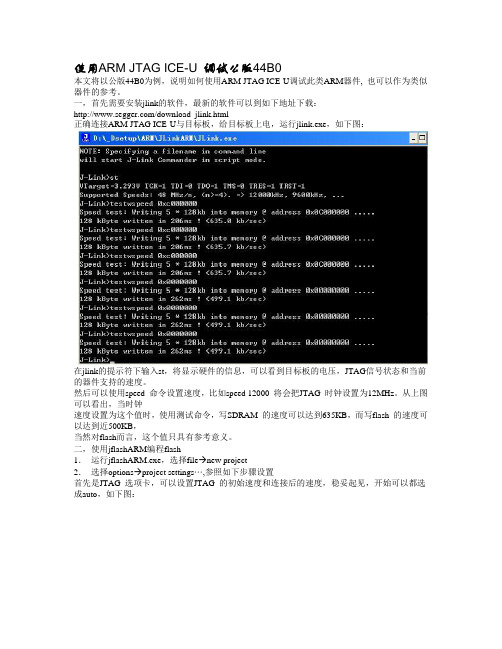

使用ARM JTAG ICE-U 调试公版44B0

使用ARM JTAG ICE-U 调试公版44B0本文将以公版44B0为例,说明如何使用ARM JTAG ICE-U调试此类ARM器件, 也可以作为类似器件的参考。

一,首先需要安装jlink的软件,最新的软件可以到如下地址下载:/download_jlink.html正确连接ARM JTAG ICE-U与目标板,给目标板上电,运行jlink.exe,如下图:在jlink的提示符下输入st,将显示硬件的信息,可以看到目标板的电压,JTAG信号状态和当前的器件支持的速度。

然后可以使用speed 命令设置速度,比如speed 12000 将会把JTAG 时钟设置为12MHz。

从上图可以看出,当时钟速度设置为这个值时,使用测试命令,写SDRAM 的速度可以达到635KB,而写flash 的速度可以达到近500KB,当然对flash而言,这个值只具有参考意义。

二,使用jflashARM编程flash1.运行jflashARM.exe,选择file→new project2.选择options→project settings…,参照如下步骤设置首先是JTAG 选项卡,可以设置JTAG 的初始速度和连接后的速度,稳妥起见,开始可以都选成auto,如下图:其次是CPU,由于44B0不在直接支持的器件列表中,所以应该选择ARM7/ARM9。

重点在于,使用ARM JTAGICE-U下载程序的时候,需要目标器件有一定的RAM,这里设置为器件内部的cache,然后在下方的初始化中,需要向系统配置寄存器写入一个值,禁用cache的功能,而把片上cache当作ram使用。

具体的可以参考44B0的数据手册。

Flash选项卡中需要选择flash的类型,一般其它的会自动设置3.选择target connect,如果连接无问题,信息栏将显示下方的状态栏会显示连接状态,连接速度等信息。

从上图可以看到连接成功,器件ID 和flash ID 将显示,同时会验证flash id。

基于JTAG协议的ARM调试接口设计

第2 6卷第 2期

Vo . 6, 12 No. 2

西 华 大 学 学 报 ・ 自 然 科 学 版

J u a o h aUn v ri ’Nau a ce c o m l fXiu ies y t tr l in e S

20 0 7年 3月

通用 端 口。通 用 TA P包 括 5个 信 号 ( K, DI TC T , T) T I O,MS, R T) T S 。本 设 计 只提 供 了这 五 个 通 用 信 号线 , 体 设计 时 可根 据 不 同 AR 芯 片 的要 求 具 M

收 稿 日期 :060 .3 2 0 —40 作者简介 : 婧 (9 1 , 湖北省天门市人 , 胡 18 一)女, 硕士研究生 , 主要研究方向: 测控技术与仪器。

个 典 型 的 AR 调试 系统 , 图 1所 示 。 调 M 如

试主机 一般是 一 台运行 调 试 软 件 ( 如 A S,D 例 D S T) 的计算 机 , 过 主机发 出高层调 试命令 , 如设置 断 通 例 点 、 测 点 以 及 访 问 内存 等 ; 试 目标 一 般 就 是 观 调

文献 标 识 码 : B

随着 嵌 入 式 应 用 领 域 的 发 展 , R 芯 片得 到 A M 广泛 的重视 和应 用 , 而在 A M 产 品 的 开发 中 系 统 R

AR 目标 板 。调 试 接 口衔 接 着 调试 主机上 的调 试 M 软件 与调试 目标 , 过调 试 接 口主 机上 运行 的调 试 通

本文设 计 的 调 试 接 口 由 两 个 部 分 组 成 : 易 简 J A 下载线 和调试 代理 软 件 。简 易 J A 下 载线 T G T G 是调 试接 口的硬 件部 分 , 图 1所 示 它连 接 主 机并 如

arm调试内核寄存器的方法

arm调试内核寄存器的方法使用ARM调试内核寄存器的方法引言:在软件开发和调试过程中,经常需要查看和修改CPU的寄存器值。

而对于ARM架构的处理器,了解如何调试内核寄存器值是非常重要的。

本文将介绍一些常用的方法和工具,帮助开发者在ARM平台上进行内核寄存器的调试。

一、使用GDB调试器GDB是一款功能强大的开源调试器,可以用于调试多种编程语言和平台。

在ARM架构上,可以使用GDB调试器来查看和修改内核寄存器的值。

1. 准备工作需要安装GDB工具链,并将其添加到系统的环境变量中。

然后,在编译内核时,需要在配置文件中启用GDB调试支持选项,以生成可调试的内核映像。

2. 连接调试器将目标设备与主机通过调试接口(如JTAG、SWD)连接起来。

然后,在主机上运行GDB,并使用以下命令连接到目标设备:```$ gdb <kernel_image>```3. 设置断点在GDB中,可以使用`break`命令设置断点。

例如,要在内核函数`foo`的入口处设置断点,可以使用以下命令:```(gdb) break foo```4. 运行程序使用`run`命令启动目标设备上的程序,并让其执行到断点处。

当程序停止时,可以使用`info registers`命令查看所有寄存器的值。

5. 查看寄存器值使用`info registers`命令可以列出所有寄存器的值。

例如,要查看R0寄存器的值,可以使用以下命令:```(gdb) info registers r0```6. 修改寄存器值使用`set`命令可以修改寄存器的值。

例如,要将R0寄存器的值修改为0x1234,可以使用以下命令:```(gdb) set $r0 = 0x1234```二、使用JTAG调试器JTAG调试器是一种常用的硬件调试工具,也可以用于调试ARM架构的处理器。

它可以提供更低层次的访问权限,可以直接读写寄存器的值。

1. 准备工作需要将目标设备与JTAG调试器连接起来,并确保JTAG调试器的驱动程序已正确安装。

ARMJTAG调试原理

ARMJTAG调试原理1.JTAG接口与信号线:JTAG接口是一种五线接口,包括TCK(时钟),TMS(状态),TDI(数据输入),TDO(数据输出)和nTRST(复位)线。

其中,TCK是由调试器提供的时钟信号,TMS用于控制状态转移,TDI用于向调试目标芯片发送调试数据,TDO用于从芯片读取调试数据,nTRST用于复位芯片。

2.JTAG状态机:JTAG调试使用的是一种状态机来控制和驱动芯片的调试操作。

状态机包括IDLE(空闲)、DRSELECT(数据寄存器选择)、DRCAPTURE(数据寄存器捕捉)、DRSHIFT(数据寄存器移位)、DREXIT1(数据寄存器退出1)、DRPAUSE(数据寄存器暂停)、DREXIT2(数据寄存器退出2)和DRUPDATE(数据寄存器更新)等状态。

3.JTAG链:JTAG链是由多个JTAG设备组成的链式结构,每个设备都有一个唯一的识别码,称为设备ID。

调试时可以通过JTAG链,逐个选中目标芯片进行调试。

JTAG链的顺序由TMS信号行控制。

4.JTAG指令和数据:JTAG指令用于控制芯片进行特定的操作,如读/写寄存器、设置断点等。

JTAG数据用于传输调试数据,如程序代码、寄存器数据等。

指令和数据的传输是通过TMS和TDI信号行实现的。

5.调试器和调试目标芯片之间的通信:调试器通过JTAG接口与目标芯片进行通信,通过命令和数据传输来控制芯片进行调试操作。

调试器可以向芯片发送指令,读取和写入芯片的寄存器数据,加载和执行程序代码等。

在进行ARM芯片的JTAG调试时,通常包括以下步骤:1.连接JTAG调试器和目标芯片:将JTAG调试器通过JTAG接口与目标芯片进行连接,并确保连接稳定可靠。

2.识别与配置芯片:通过JTAG链识别和配置目标芯片,选择要调试的芯片。

调试器可以读取芯片的设备ID和其他信息,并为芯片配置合适的调试模式。

3.设定调试模式:通过JTAG指令设置芯片的调试模式,如停止模式、单步模式等。

基于JTAG的ARM7TDMI调试系统

片上可 以通过 T AP 访问芯片 提供 的所有数据寄存器( R 和 D )

指令寄存器( ) A I 。T P包括 4 强制信 号 T K MS T I R 个 C 、T 、 D 、

T O和 1 D 个可选信号 T T。 RS ()C T sC okIp t,为 T P 的操作提供 了一个独 1T K(et lc u) n A

AR M、D P等处理器中 ,其主要用于软件调试 ;在 C L S P D, F GA开发 中,其主要用来配置 P O P R M。

DC K Deu lc) L ( bg Co k驱动 。在运 行状态下 ,A M7 DMI由 R T MC K( moyCok驱动 。DC K比 MC K慢 。 L Me r lc) J L L

d b g ig AR T e u gn M7 DMI T e e s T s it d c d t o t lT s Ac e sP r(AP y c mp t aall o . e s f re i tr el e . h a y J AG i n o u e O c n o e t c s ot r r T )b o ue p rl r T o t r e pt h wa s he — v l e

接 1,通过 计算机 并1控制测试访 问端 1 。该软件采用 3 7 1 7 1 7 1 层结构 ,共有 7 个模块 。该文分析层次、模块的划分及接 口的定义和实现过程 。 实验测试 结果表 明,该软件具有 良好 的实用性 、可调试性 。

关糊

:边界扫描 ;测试 访问端 口;嵌入式系统

基于JTAG的ARM调试器实现

( 浙江大学计算机学院 浙江 杭 州 30 2 ) 10 7

摘

要

随着 u l u Ci x应用 与普及 , n 移植 u l u Ci x和在 Ln x开发平 台上设计嵌入式应用 系统都迫切 需要好 的调试 工具 , n iu 而现有 的

Wi o s 的调试 工具很难用 于 Lnx系统。介绍如何在 G B的基础上 , n w下 d iu D 低成 本实现嵌入式板 的J A T G调试 。

如下 :

・ 取指

・ 译码

从存储器 中取 出指令 , 放人指令流水线。

指令被译码 , 并为 下一周期 准备数据 通路的控制

A M处理器也提供 了典 型的 m G调试 方法 ( R 用户可 以添 加观察点 和断点) 目标 系统 与主机 之间通 过扩 展 的 J A T G测 试

为 了提高 自主知识产 权 , 破技术 垄 断 , 打 开放 源码 的 G U N

工程越来越受到重视。在嵌 人式领域 , u l u 以 Ci x为代表 的应用 n

考虑 , 而通常应 用 , 编译 器 和链接 器都 屏蔽 了这 些 差别 。另 外

A M的P R c值在 因为不 同原 因进人调试模式时 , 判断也有不 同 , 恢复断点时要根据不 同的中断原 因来恢 复不同的 P c值 。

1 A M 的体 系结构 R

A M( da cdR S ahns , 可 以 认 为 是 一 个 公 司 的 R A v e IC M c i ) 既 n e

国际标准测试 协 议 (E E 19 1 容 ) 主 要用 于 芯片 内部 测 IE 14 . 兼 ,

试 。标准 的 J A T G接 口是 5线 :MS T K、D 、 D T S , 别 T 、C T IT O、 R T 分

基于JTAG的ARM嵌入式系统调试技术实现及应用

基于JTAG的ARM嵌入式系统调试技术实现及应用

殷伟凤

【期刊名称】《浙江万里学院学报》

【年(卷),期】2009(22)2

【摘要】文章介绍了JTAG结构及其TAP控制器的控制机制,描述了ARM芯片的JTAG调试原理,给出了一种基于JTAG接口协议的ARM调试设计方案及其软硬件实现,并利用JTAG接口进行硬件设备的远程调试.

【总页数】6页(P17-21,30)

【作者】殷伟凤

【作者单位】浙江万里学院,浙江,宁波,315100

【正文语种】中文

【中图分类】I210.6

【相关文献】

1.基于ARM嵌入式系统和GPRS无线通讯技术的新型汽车故障诊断仪的实现 [J], 黄伟

2.基于JTAG的54xDSP并行自举实现方法及应用 [J], 陈迪楼

3.基于EmJTAG的ARM嵌入式系统调试工具 [J], 姜立娣;沈建华

4.基于JTAG的ARM芯片系统调试 [J], 杨峰;张根宝;田泽;万永波

5.基于JTAG的ARM芯片系统调试 [J], 杨峰;张根宝;田泽;万永波

因版权原因,仅展示原文概要,查看原文内容请购买。

arm jtag 调试原理

arm jtag 调试原理嗨,小伙伴!今天咱们来唠唠ARM JTAG调试原理这个超有趣的事儿。

JTAG呢,就像是给ARM芯片开的一个特殊小后门。

想象一下,ARM芯片就像一个神秘的小城堡,里面有好多好多的小房间(各种寄存器、功能模块啥的),但是这个城堡外面围着高高的城墙,我们平常很难直接看到里面到底发生了什么。

这时候JTAG 就闪亮登场啦。

JTAG有几个特别的线,就像是几根魔法绳索。

其中有TMS(测试模式选择)线,这根线就像是一个指挥棒。

你看啊,当我们在调试的时候,通过在这根线上发送不同的高低电平信号,就像是在给芯片里的调试模块打暗号呢。

比如说,高电平可能表示“咱们要进入这个特定的测试模式啦”,低电平可能就是“现在先停一停这个操作”。

还有TCK(测试时钟)线,这可是整个调试的节奏大师哦。

它就像一个小鼓手,不停地打着节拍。

芯片里的调试操作都得按照这个节拍来进行。

就像我们跳舞得跟着音乐的节奏一样,芯片里的各种测试和数据传输都要和TCK的节奏同步。

如果TCK这个小鼓手乱了节奏,那整个调试可就乱套啦,就像一群舞者突然找不到音乐的节奏,乱成一锅粥了呢。

TDI(测试数据输入)线呢,这是往芯片里送宝贝(数据)的通道。

我们想要查看芯片里某个寄存器的值,或者给某个模块设置一个初始状态,就可以通过TDI把这些数据送进去。

这就好比我们通过一个小管道,把我们想要的东西送进城堡里的各个小房间。

而TDO(测试数据输出)线呢,它是把芯片里的信息反馈出来的通道。

就像是城堡里的小信使,把城堡里各个房间的情况给我们带出来。

比如说我们想知道某个寄存器现在存的是什么数,芯片就会通过TDO把这个数给我们送出来,就像小信使把房间里的小纸条递给我们一样。

那这个JTAG到底是怎么在ARM芯片里工作的呢?当我们把JTAG接口连接到ARM 芯片上,就相当于把我们的魔法绳索系到了城堡上。

然后我们通过外部的调试工具,像是JTAG调试器之类的。

这个调试器就像是一个超级管家,它知道怎么摆弄那些魔法绳索。

ARM JTAG调试常见问题

ARM JTAG 调试常见问题1 - 检测不到目标系统调试前,请把目标板连接好,然后用调试软件检测目标系统。

如果检测不到目标系统,请做以下的检查。

A - 确定你的连接是正确的;B - 确定你使用的仿真器是被调试软件支持的C - 对WIGGLER 而言,因为没有固定的电路图,所以需要在软件里做相应的设置;D - 对LPC2000 系列而言,RTCK 管脚一般是用来控制是否使能JTAG 接口的,请查阅数据手册;E - 如果你用的芯片比较特殊,例如STR91X,因为内部扫描链是串接的,请设置好TAP,以让仿真器知道扫描链的长度;2 - 程序下载不正确,程序跑飞一般的用户,刚开始调试的时候,编译好程序,就直接点击调试。

但结果发现调试根本没有按照预期的进行。

发生这种问题一个最常见的原因是程序根本没有正确下载到目标系统中去。

对SDRAM 而言,上电后一般都是不可以使用的,需要进行相应的配置才可以使用。

所以如果是在SDRAM 里进行调试,请先对SDRAM 进行配置,或者确定SDRAM 已经初始化好了。

如果是内部SRAM,一般来说,可以直接使用。

所以,做一般的测试,最简单的办法是使用片内SRAM。

在调试的时候,最好是自己通过内存观察窗口判断一下,程序是否是下载到期望的地址去了,下载是否正确。

以免出现调试跑飞的问题。

3 - 软件断点和硬件断点的区别和数量限制所有的ARM7/ARM9 芯片,内部有2 个断点单元。

断点单元可以用于设置硬件断点或是软件断点。

先说说硬件断点和软件断点的区别。

硬件断点是通过监测地址来触发断点的。

所以,硬件断点可以设置在任何地方,不管是FLASH,ROM 还是RAM,只要给定地址就可以了。

而软件断点是通过监测特定的指令来触发断点的。

在某个地址设置软件断点的时候,仿真器会将这个地址的数据/指令替换成一个特殊格式的指令。

断点单元通过监测这个特殊格式的指令来触发断点。

因为需要执行替换操作,所以软件。

基于JTAG的ARM调试器实现

基于JTAG的ARM调试器实现

基于JTAG的ARM调试器实现

基于JTAG的ARM调试器实现

陆晗;潘雪增;平玲娣

【期刊名称】《计算机应用与软件》

【年(卷),期】2007(024)002

【摘要】随着uClinux应用与普及,移植uClinux和在Linux开发平台上设计嵌入式应用系统都迫切需要好的调试工具,而现有的Windows下的调试工具很难用于Linux系统.将介绍如何在GDB的基础上,低成本实现嵌入式板的JTAG调试.

【总页数】3页(P137-139)

【作者】陆晗;潘雪增;平玲娣

【作者单位】浙江大学计算机学院,浙江,杭州,310027;浙江大学计算机学院,浙江,杭州,310027;浙江大学计算机学院,浙江,杭州,310027 【正文语种】中文

【中图分类】TP3

【相关文献】

1.一种基于CPLD的高速JTAG调试器的设计与实现 [J], 张红;余建

2.基于JTAG的ARM7TDMI处理器调试原理及实现 [J], 刘文超;潘永才

3.基于JTAG接口实现ARM的FPGA在线配置 [J], 黄志海;周小会;糜正琨

4.基于JTAG的片上调试器与调试系统的设计实现 [J], 常志恒;肖铁军;史顺波

5.基于JTAG的ARM嵌入式系统调试技术实现及应用 [J], 殷伟凤

因版权原因,仅展示原文概要,查看原文内容请购买。

ARM+JTAG调试教程

2.1.2 寻址.....................................................................................................................................................5

4 并口...........................................................................................................................................................................20

3 JTAG协议 .................................................................................................................................................................12

3.1.1 边界扫描...........................................................................................................................................12

目录 ....................................................................................................................................................................................3

基于JTAG的ARM芯片系统调试.

基于JTAG的ARM芯片系统调试1 引言随着嵌入式处理器性能的逐步提高,运算速度越来越快、处理的数据量越来越大,传统的调试方法如ROM驻留监控程序以及串口调试工具已经不能满足要求。

ARM处理器采用一种基于JTAG的ARM的内核调试通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在线仿真器)模块的系统芯片通过JTAG端口与主计算机连接。

通过配置支持正常的断点、观察点以及处理器和系统状态访问,完成调试。

为了对代码进行实时跟踪,ARM的提供了嵌入式跟踪单元(Embedded Trace Macrocell),对应用程序的调试将更加全面。

2 JTAG边界扫描原理“JTAG边界扫描”或IEEE1149标准[1]是由“测试联合行动组”(Joint Test Action Group,简称JTAG)开发的针对PCB的“标准测试访问接口和边界扫描结构”的标准。

这个标准是ARM处理器调试的基础。

2.1 硬件电路JTAG边界扫描测试接口的一般结构[2]如图1所示。

JTAG边界扫描硬件电路主要由三部分构成:1) TAP控制器。

测试访问端口(TAP)控制器,是由TMS控制状态转换的状态机。

2) 指令寄存器。

用于存储JTAG边界扫描指令,通过它可以串行的输入并执行各种操作指令。

3) 数据寄存器。

特定芯片的行为由测试指令寄存器的内容决定。

测试指令寄存器可用来选择各种不同的数据寄存器。

2.2 边界扫描测试信号支持这个测试标准的芯片必须提供5个专用信号接口:? TRST:测试复位输入信号,低电平有效,为TAP控制器提供异步初始化信号。

? TCK:JTAG测试时钟,独立于任何系统时钟,为TAP控制器和寄存器提供测试参考。

? TMS:TAP控制器的测试模式选择信号,控制测试接口状态机的操作。

? TDI:JTAG指令和数据寄存器的串行输入端,给边界扫描链或指令寄存器提供数据。

? TDO:TAG指令和数据寄存器的串行输出。

ARM的JTAG调试构造原理

ARM的JTAG调试构造原理ARM的JTAG调试构造原理一、JTAG的底子常识JTAG是JointTestActionGroup的缩写,是IEEE1149.1规范。

运用JTAG的利益:JTAG的树立使得集成电路固定在PCB上,只经过鸿沟扫描便能够被测验。

在ARM7TDMI处理器中,能够经过JTAG直接操控ARM的内部总线、I/O口等信息,然后抵达调试的意图。

二、ARM的JTAG调试构造(1)Debug主控(Host)通常是作业有ARM公司或许第三方供应的调试软件的PC机,常用的调试软件有ARMSDT中的ARMDebugforWindows(ADW)、Linux下的arm-elf-gdb等。

经过这些调试软件,能够发送高档的ARM调试指令,如设置断点、读写存储器、单步盯梢、全速作业等。

(2)协议改换器(ProtocolConverter)担任改换Debug主控端宣告的高档ARM调试指令为底层的和ARM内核通讯的JTAG指令。

Debug主控端和协议改换器之间的介质能够有许多种,比方以太网、USB、RS-232、并口等。

Debug主控端和协议改换器之间的通讯协议最典型的即是ARM公司供应的Angel规范,也可所以第三方厂家自个界说的规范。

对于Angel的协议,可参看ARMSDT和ADS的有关文档。

典型的协议改换器有:ARM公司的Multi-ICE、Abatron 公司的BDI、aiji公司的OpenlCE32、EPI公司的Jeeni等。

(3)ARM7TDMI的JTAG宏单元(Macrocell)首要包含3条JTAG扫描链(ScanChain)和1个JTAG的操控TAP状况机。

三、ARM7TDMI内核的JTAG扫描链构造ARM7TDMI内核的JTAG扫描链构造首要包含3条JTAG扫描链:ScanChain0、ScanChain1、ScanChain2。

四、ARM7TDMI中经过JTAG对外设的拜访作为ARM典型的调试办法,JTAG除了能够设置ARM的断点以外,还能够对ARM的内核进行操控,然后结束对外围设备的读/写(比方下载程序到RAM或许FLASH空间)。

ARMJTAG调试器全攻略

ARM JTAG 调试器全攻略学习ARM ,JTAG 这一关是必须要过的。

但是似乎对应于不同的调试软件有不同的电路,又有可否烧写flash 之分。

这对初学者未免造成一些困惑,其实这层窗纸太薄了,一点即透。

我们首先来看Jtag 几条线的作用:;Test Clock Input (TCK)TCK 为TAP 的操作提供了一个独立的、基本的时钟信号,TAP 的所有操作都是通过这个时钟信号来驱动的。

TCK 在IEEE 1149.1 标准里是强制要求的。

;Test Mode Selection Input (TMS)TMS 信号用来控制TAP 状态机的转换。

通过TMS 信号,可以控制TAP 在不同的状态间相互转换。

T MS 信号在TCK 的上升沿有效。

TMS 在IEEE 1149.1 标准里是强制要求的。

;Test Data Input (TDI)TDI 是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI 接口一位一位串行输入的(由T CK 驱动)。

TDI 在IEEE 1149.1 标准里是强制要求的。

;Test Data Output (TDO)TDO 是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO 接口一位一位串行输出的 (由TCK 驱动)。

TDO 在IEEE 1149.1 标准里是强制要求的。

;Test Reset Input (TRST)TRST 可以用来对TAP Controller 进行复位(初始化)。

不过这个信号接口在IEEE 1149.1 标准里是可选的,并不是强制要求的。

因为通过TMS 也可以对TAP Controll 进行复位(初始化)。

-- 所以有四线J TAG 与五线JTAG 之分。

其实对JTAG 来说有着几根线就够了,再算上电源和地最多才7 根线啊,可常见的接口方式是20 针的插座啊;多出来的几根线适用于高级一点的用途,对于新手来说是不需要的。

;(VTREF)接口信号电平参考电压一般直接连接Vsupply 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要:嵌入式ARM软、硬件调试技术依赖于ARM处理器调试硬件,本文在分析JTAG边界扫描结构的基础上,介绍了EmbeddedICE、嵌入式跟踪等实时调试技术,并给出了一个嵌入式调试开发系统的实例。

关键词:ARM JTAG EmbeddedICE 嵌入式跟踪1 引言32位ARM处理器是英国先进RISC机器公司(Advanced RISC Machines,ARM)的产品。

随着嵌入式处理器性能的逐步提高,运算速度越来越快、处理的数据量越来越大,传统的调试方法如ROM驻留监控程序以及串口调试工具已经不能满足要求。

ARM处理器采用一种基于JTAG的ARM的内核调试通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在线仿真器)模块的系统芯片通过JTAG端口与主计算机连接。

通过配置支持正常的断点、观察点以及处理器和系统状态访问,完成调试。

为了对代码进行实时跟踪,ARM的提供了嵌入式跟踪单元(Embedded Trace Macrocell),对应用程序的调试将更加全面。

2 JTAG边界扫描原理“JTAG边界扫描”或IEEE1149标准[1]是由“测试联合行动组”(Joint Test Action Group,简称JTAG)开发的针对PCB的“标准测试访问接口和边界扫描结构”的标准。

这个标准是ARM处理器调试的基础。

2.1 硬件电路JTAG边界扫描测试接口的一般结构[2]如图1所示。

JTAG边界扫描硬件电路主要由三部分构成:1) TAP控制器。

测试访问端口(TAP)控制器,是由TMS控制状态转换的状态机。

2) 指令寄存器。

用于存储JTAG边界扫描指令,通过它可以串行的输入并执行各种操作指令。

3) 数据寄存器。

特定芯片的行为由测试指令寄存器的内容决定。

测试指令寄存器可用来选择各种不同的数据寄存器。

2.2 边界扫描测试信号支持这个测试标准的芯片必须提供5个专用信号接口:TRST:测试复位输入信号,低电平有效,为TAP控制器提供异步初始化信号。

TCK:JTAG测试时钟,独立于任何系统时钟,为TAP控制器和寄存器提供测试参考。

TMS:TAP控制器的测试模式选择信号,控制测试接口状态机的操作。

TDI:JTAG指令和数据寄存器的串行输入端,给边界扫描链或指令寄存器提供数据。

TDO:TAG指令和数据寄存器的串行输出。

2.3 指令JTAG测试系统是通过向指令寄存器送入指令,然后使用数据寄存器进行测试。

测试指令说明要进行的测试种类及测试要使用的数据寄存器。

测试指令分为公开指令和私有指令。

公开指令已经定义且用于通用测试。

私用指令用于片上的专用测试,测试标准没有规定如何使用私有指令。

测试标准支持的最小集的公开指令有:BYPASS:器件将TDI经一个时钟延时连接到TDO,用于同一个测试环中其它器件的测试。

EXTEST:将边界扫描寄存器连接到TDI和TDO之间,用于支持板级连接测试。

IDCODE:将ID寄存器连接到TDI和TDO之间。

通过它可以读出器件ID(厂家赋与的固定标识,包括产品编号及版本码)。

INTEST:将边界扫描寄存器连接到TDI和TDO之间。

3 EmbeddedICEARM的EmbeddedICE调试结构[3]是一种基于JTAG的ARM的内核调试通道,它是基于JTAG测试端口的扩展,引入了附加的断点和观测点寄存器,这些数据寄存器可以通过专用JTAG 指令来访问,一个跟踪缓冲器也可用相似的方法访问。

ARM核周围的扫描路径可以将指令加入ARM流水线并且不会干扰系统的其它部分。

这些指令可以访问及修改ARM和系统的状态。

由于EmbeddedICE条件断点,单步运行等功能的实现是基于片上JTAG测试访问端口进行调试,芯片不需要增加额外的引脚,避免使用笨重的、不可靠的探针接插设备完成调试。

芯片中的调试模块与外部的系统时序分开,可以直接运行在芯片内部的独立时钟速度。

3.1 硬件结构EmbeddedICE模块包括两个观察点寄存器和控制与状态寄存器,还包括一个Debug comms 端口。

当地址、数据和控制信号与观察点寄存器的编程数据相匹配时,也就是触发条件满足时,观察点寄存器可以中止处理器。

由于比较是在屏蔽控制下进行的,因此当ROM或RAM中的一条指令执行时,任何一个观察点寄存器可配置为能够中止处理器的断点寄存器。

1) 观察点每个观察点皆可以观察ARM地址总线、数据总线、和等信号的特定组合值。

任何一个组合值与观察点寄存器值匹配则中止处理器。

另外一种方式是把两个观察点链接起来,只有第一个观察点先匹配了,当第二个观察点再匹配时将使处理器中止。

2) 寄存器EmbeddedICE寄存器通过JTAG测试端口使用专用扫描链编程。

扫描链38位长,包括32个数据位,5个地址位和一个控制寄存器是读还是写的位。

地址位指定特定的寄存器,地址和寄存器一一对应。

3) Debug comms端口debug comms端口运行在目标系统上的软件可以通过这个端口与主机通信。

运行在目标系统上的软件将comms端口视为一个6位控制寄存器和32位可读写寄存器,可以使用对协处理器14的MRC和MCR指令访问。

主机将这些寄存器视为EmbeddedICE寄存器。

3.2 实现原理1) 访问状态EmbeddedICE模块允许程序在指定点中止,但不允许直接观测、修改处理器或系统状态。

这可以通过属于JTAG端口访问的扫描路径实现。

访问处理器状态的方法是中止处理器,再在处理器指令序列中强制插入一条多寄存器存取指令。

然后通过扫描链向处理器加入时钟,使处理器将寄存器内容送到数据端口。

每个寄存器的值都可以被扫描链采样并移出。

2) 调试基于ARM的包括EmbeddedICE模块的系统芯片通过JTAG端口和协议转换器与主计算机连接。

这种配置支持正常的断点、观察点以及处理器和系统状态访问,(除上面介绍的comms 端口以外)这是程序设计人员在本地或基于ICE的调试中习惯采用的方式。

采用适当的主机调试软件,以较少的硬件代价得到完全的源代码级调试功能。

4 ARM的嵌入式跟踪EmbeddedICE提供的断点及观察点将使处理器偏离正常执行序列,破坏了软件的实时行为,它不能完成实时操作调试功能。

ARM结构的处理器采用嵌入式跟踪宏单元ETM很好的解决了系统实时调试的问题。

4.1 硬件电路EmbeddedICE单元支持断点和观察点功能并提供主机和目标软件的通信通道。

ETM单元[5]压缩处理器接口信息并通过跟踪端口送到片外。

这两个单元都由JTAG端口控制。

SoC外部的EmbeddedICE控制器用于将主机系统连接到JTAG端口,跟踪端口分析器使主机系统与跟踪端口对接。

主机通过一个网络可以与跟踪端口分析器和EmbeddedICE二者连接。

4.2 实现原理由调试软件配置并通过标准JTAG接口传输到ETM上。

在程序执行时ETM可以通过产生对处理器地址、数据及控制总线活动的追踪(Trace)来获得处理器的全速操作情况。

在实时仿真时外设和中断程序依然能够继续运行。

用户控制断点和观察点的设置并可以配置各种跟踪功能。

跟踪触发条件可以指定,跟踪采集可以在触发之前、之后或以触发为中心可以选择跟踪是否包括数据访问。

跟踪采集可以是数据访问的地址、数据本身,也可以是两者兼有。

ETM是使用软件通过JTAG端口进行配置的,所使用的软件是ARM软件开发工具的一个扩展。

跟踪数据从跟踪端口分析仪下载并解压,最终反链接到源代码。

5 应用实例下面以S3CEV40开发板[4]为例,介绍ARM调试结构应用。

S3CEV40采用的CPU为Samsung 公司的S3C44B0X,是国内应用广泛的基于ARM7TDMI内核的SoC。

其调试系统的硬件结构如图2:计算机的并行口和Embest PowerICE for ARM仿真器的DB25接口通过标准的DB25公、母转换电缆连接。

Embest PowerICE for ARM仿真器通过一个的IDC头的直通电缆(1-1,2-2,… 20-20)与目标板的JTAG接口相连接。

20芯的Embest PowerICE for ARM仿真器接口的定义如图3所示:S3CEV40所用到的调试软件为EmbestIDE集成开发环境,它提供源码级调试,提供了图形和命令行两种调试方式,可进行断点设置、单步执行、异常处理,可查看修改内存、寄存器、变量等,可查看函数栈,可进行反汇编等。

它为用户提供2种调试方法:脱机调试:Embest IDE for ARM带ARM指令集模拟器,用户能在PC上调试ARM应用软件下载调试:Embest IDE将程序通过仿真器下载到开发板,直接进行调试。

Embest IDE的调试功能包括:断点功能;程序的单步执行;变量监视功能,随程序运行同步更新变量,变量值即时修改;寄存器即时查看与修改;存储器查看与修改,存储器内容显示格式定制;堆栈显示;同时提供图形界面操作和命令行操作方式;支持被调试代码的多种显示模式,能以源码、汇编、混合等形式来显示程序;具有与MS Visual Studio类似的调试菜单功能:Go,Stop,Reset,Step into,Run to Cursor等;程序的上载和下载。

6 结束语本文介绍了32位ARM嵌入式处理器的调试技术。

在JTAG边界扫描技术的基础上介绍了ARM的EmbeddedICE及嵌入式跟踪并在此基础上介绍了一个系统调试实例。

嵌入式调试技术是嵌入式软硬件开发中必要的一环,掌握了它能在开发中起到事半功倍的作用。

嵌入式技术正在日新月异的发展着,嵌入式调试技术也不是一成不变的,它必将随着高速、低功耗Soc的发展而进步。