电路图及PCB设计规范之元件命名原则

PCB板的命名及拼版方式规范

PCB板的命名及拼版方式规范目的:为了文件名称能够更加规范的编写,为了文件名称对外时的统一,为了不让其他部门或供应商对文件名称的疑惑。

满足SMT或AI等自动化生产机台的合理生产效率及PCB厂商开模最高性价比方式。

原则:PCB板上的丝印、K3系统内的规格描述、日期、PCB板的文件名,三者命名必须要求一致。

拼版尺寸符合规范基本要求。

要求:1.如果客人没有明确要求情况下,芯阳公司自行设计的PCB板命名规则是:客户名、产品名、规格、版本+日期如:客户名(ES)、产品名(292)、类别(以为准)、-、规格(GS)、空格、版本()另外一行写明日期格式为:yy/mm/dd。

如12/01/10代表2012年1月10日。

上述各个命名之间不要增加任何符号。

日期命名年月日之间用“/”隔开。

“ES292PWR-GS V1.0”首样命名为,第二版样品命名为(.1~.9)。

如果有重大修改如尺寸完全变化的话命名为,以此类推。

如果预知共用UL、GS规格基板或预知LED灯颜色不同等等信息的话,命名方式第一选择在丝印好客户名和产品名称之后增加□然后写可能更改的内容,以备后续使用油性笔点点区分。

第二选择命名不要描述规格,量产第一版本依K3系统,后续如果要有共用用贴纸区分。

如果客人有要求自己的命名规则按照客人命名要求。

如量产后的机种需要更改PCB图纸,但是不想让客人知晓的话,如ES292-GS.如客人要求更高不能有任何体现的话可以在图纸其他不起眼位置“。

”体现!如果更改版本更多的在同心圆上增加圈数;K3新建料号,规格描述进行修改增加备注!基板类别区分规则:电源板PWR(依据电源电路);显示板DIS;按键板KEY;控制板(主板)CTL(依据是IC),其他特殊功能板以物料命名。

无特殊要求以上述优先级命名。

如果只有一个板的话不做区分。

2.所有拼板的命名规则是:客户名、产品名、类别、规格、版本、拼、PCB板2.1如:客户名(ES)、产品名(292)、-、规格(GS)、版本()、拼(PIN).PCB板ES292PWR-GS 命名规则是丝印内容完全保留的情况下+2.2开发部外发确认或打样的图纸原则上一定要求是拼好板的图纸。

电路图及PCB设计规范之元件命名原则

4.4.2走线时应注意:先走电源,关键信号(如:时钟、复位、高速信号线),强电的线,

以便有足够的空间满足其布线要求。

4.4.3 IC 的去耦电容与IC 连接时,线路应先经过电容再走向IC ,并保证其回路最短。

4.4.4 地线的走线

4.4.4.1采用单点接地或星形接地来降低各子系统间的互相干扰,即各个子系统应直接接电源、 地线,而不是各子系统串联,尤其是大电流、继电器、开关元件,

其电流不能经过MCU ,再流回电源。

如图:

单点接地

4.4.4.2因电流最终要流回电源,回路越大,易受干扰。

故地线回路应尽量小,如: 信号线与地

信号线地线 地线

差 佳

4.4.4.3高速信号线、时钟线应该用地线包围起来,以免受到干扰。

4.4.4.4模拟电路的地要与数字电路的地分开,如RC 滤波回路的电源与地应直接连到电源与地 上,而不是与其它子系统的电源.地直接串联。

4.4.4.5在高频电路中,模拟电路地不能有回路,防止出现共地噪声。

4.4.4.6在高频电路中,若双面板上电源、地需进行板层切换时,须放置多个贯孔,以减少阻抗。

4.4.5高频线路走线不能用900直角,建议用450角,这样可避免传输反射。

4.4.6在双面板中,电解电容, 发热元件,导体元件下面不能走线,以防止短路现象。

4.4.7在双面板中,两层的信号线要垂直走线。

4.4.8线离板边≥0.5mm ,以便与外壳隔离,距离金属外壳要≥4mm 。

4.4.9在高频电路中,高速信号线上尽量不要放贯孔。

原理图PCB图元器件标注规范

原理图和PCB中元器件标注规范画原理图时,只能使用中海达元件库(ZHD.LIB)中的元件和对应封装,开始项目前从硬件项目主管处获取最新的库。

如有新添加的元件,应创建原理图符号和对应的封装,及时向硬件项目主管汇报整理归库。

特殊封装应以ZHD_X_NNN的格式命名,其中X电容类为C,电阻类为R,电感类为L等(类型命名表格),NNN为序号,从000开始,向上增加。

芯片、GPS模块、GPRS 模块等模块型元件可以按模块名称命名封装。

对外发出制作PCB前必须在硬件项目主管和采购处记录备案,由硬件项目主管分配PCB年份序号,并且按格式标注到PCB显眼位置上。

原理图标注规则:1)、通用元件只标注序号和标称值,如R1 100K, C1 0.1UF等。

2)、特殊要求在标称值后用括号标注,如R1 100K(1%), C1 10UF(50V)等。

3)、一个项目中同类元件序号从1开始增加,中间不应有跳空。

4)、单位全部用大写,如K,UF,MH,UH等。

5)、原理图必须标有日期和版本,便于升级和管理。

6)、原理图必须使用审核框,图纸应由硬件主管或总工审核。

1、电阻类电阻在电路图中的流水号统一以Rx标注(x表示1,2,3,4……);元器件类型以电阻阻值大小为标注,如:1000Ω标注为1K,100Ω标注为100,1000 000Ω标注为1M。

以此类推。

2、电容类电容在电路图中的流水号统一以Cx标注(x表示1,2,3,4……);元器件类型以电容容量大小为标注,如:105 标为1UF,104标为0.1UF。

3、电感类电感在电路图中的流水号统一以Lx标注(x表示1,2,3,4……);元器件类型以电感大小为标注。

4、二极管类电感在电路图中的流水号统一以Dx标注(x表示1,2,3,4……);元器件类型以二极管型号为标注。

5、三极管类电感在电路图中的流水号统一以Qx标注(x表示1,2,3,4……);元器件类型以三极管型号为标注。

如:Q1 90126、晶振类晶振在电路图中的流水号统一以Xx标注(x表示1,2,3,4……);元器件类型以晶振频率为标注。

PCB和线路板命名规则

PCB和线路板命名规则

1、PCB命名规则:

板号顺序号:000-999

线路板类别:K-控制板;

P-电源板;

D-灯板;

Z-综合控制板

2、线路板命名规则:

顺序号:00-99

线路板工艺标识:D-直插工艺;

S-贴片工艺;

C-混装工艺

控制方式标识:S-可控硅控制;

R-继电器控制;

板号顺序号:000-999;

线路板类别:K-控制板;

P-电源板;

D-灯板;

Z-综合控制板

举例:花系列的PCB和线路板命名如下:

K100标识控制板PCB板号;新申请从100开始;P019表示电源板PCB板号;新申请从100开始;K100-FSS00表示花的一种控制板板号

P019-FSD00标识花的一种电源板板号

Z016-FRC00表示16#BZB的一种新线路板板板号注:PCB编码规则执行:线路板类别加顺序号。

PCB设计中制作元件库遵循的命名规则

PCB设计中制作元件库遵循的命名规则1.集成电路1.1 集成电路(直插)用DIP引脚数量+尾缀来表示双列直插封装。

尾缀有N和W两种,用来表示器件的体宽。

N为体窄的封装,体宽为300mil ,引脚间距2.54mm。

W为体宽的封装,体宽为600mil,引脚间距2.54mm。

如:DIP16N表示是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装。

1.2 集成电路贴片用SO引脚数量+尾缀来表示小外形贴片封装。

尾缀有N、M和W三种,用来表示器件的体宽。

N为体窄的封装,体宽为150mil ,引脚间距1.27mm。

M为介于N和W之间的封装,体宽为208mil ,引脚间距1.27mm。

W为体宽的封装,体宽为300mil,引脚间距1.27mm。

如:SO16N表示是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装。

若SO前面跟M则表示为微型封装,体宽为118mil,引脚间距0.65mm。

2.电阻SMD贴片电阻命名方法为:封装+R。

如:1812R 表示封装大小为1812的电阻封装。

2.2 碳膜电阻命名方法为R-封装。

如:R-AXIAL0.6 表示焊盘间距为0.6英寸的电阻封装。

2.3 水泥电阻命名方法为:R-型号。

如:R-SQP5W表示功率为5W的水泥电阻封装。

3.电容3.1 无极性电容和钽电容命名方法为:封装+C。

如:6032C表示封装为6032的电容封装。

3.2 SMT独石电容命名方法为:RAD+引脚间距。

如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装。

3.3 电解电容命名方法为:RB+引脚间距/外径。

如RB.2/.4表示的是引脚间距为200mil,外径为400mil的电解电容封装。

4.二极管整流器件命名方法按照元件实际封装其中BAT54和1N4148封装为1N41485.晶体管命名方法按照元件实际封装,其中SQT-23Q封装加了Q以区别集成电路的SQT-23封装,另外几个场效应管为了调用元件不致用错元件名。

PCB元件及封装库命名规则

PCB元件封装库命名规则简介1、集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mmW为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm3、电阻3.1 SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装3.3 水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容4.1 无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装4.2 SMT独石电容命名方法为:RAD+引脚间距如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N41486 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件9.1 贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管9.2 直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管9.3 数码管使用器件自有名称命名10、接插10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm如:DIP10-2.54表示针脚间距为2.54mm的10针脚双排插针10.3 其他接插件均按E3命名封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在AD7.1元器件封装库中的命名含义。

PCB封装库命名规则

封装库的管理规范修订履历表版本号变更日期变更内容简述修订者审核人V1.00 初次制定杨春萍一。

元件库的组成1.1 原理图Symbol库原理图Symbol库分为STANDARD_LIB.OLB和TEMPORARY_LIB.OLB,用于标准库和临时库的区分;1.2 PCB的Footprint库PCB封装库只有一个文件夹,里面包括所有的封装和焊盘。

二、元件Ref缩写列表常用器件的名称缩写作如下规定:集成芯片 U电阻 R排阻 RN电位器 RP压敏电阻 RV热敏电阻RT无极性电容、大片容C铝电解CD钽电容CT可变电容 CP二极管 D三极管 QESD器件(单通道)DMOS管 MQ滤波器 Z电感L磁珠 FB霍尔传感器 SH温度传感器 ST晶体Y晶振 X连接器J接插件 JP变压器 T继电器 K保险丝 F过压保护器 FV电池 GB蜂鸣器 B开关 S散热架 HS生产测试点:TP/TP_WX1信号测试点:TS螺丝孔 HOLE定位孔:H基标:BASE三、元件属性说明为了能够将元件信息完全可以录入ORCAD的元件信息系统(CIS)中,根据器件的特性,建库申请人还应将相应的信息(但不仅限于以下信息)提供给库管理员。

元件属性如下:Value:器件的值,主要是电阻、电容、电感;Tolerance:公差,主要指电阻、电容的精度等级;晶体、钟振的频偏范围;C_Voltage:电压,主要指电容的额定电压,晶体、钟振的供电电压;Wattage:功率,主要是电阻的额定功率;Dielectric:电容介质种类,如NPO、X7R、Y5V等等Temperature:使用温度Life:使用寿命CL:容性负载,主要针对晶体来说Current:电流,电感、磁珠的额定电流Resonace frequency:电感的谐振频率Part_Number:器件料号Footprint:指PCB封装Price:价格Description:元件简单描述,主要引用S6ERP品名。

史上最全的pcb封装命名规范

史上最全的pcb封装命名规范篇一:PCB封装库命名规则资料PCB封装库命名1、集成电路(直插):用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mmW为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm3、电阻3.1 SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装 3.3 水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容4.1 无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装4.2 SMT独石电容命名方法为:RAD+引脚间距如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N4148 6 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装 8、电感、变压器件电感封封装采用TDK公司封装9、光电器件9.1 贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管9.2 直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管9.3 数码管使用器件自有名称命名10、接插10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm10.3如:DIP10-2.54表示针脚间距为2.54mm的10针脚双排插针10.4封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在AD7.1元器件封装库中的命名含义。

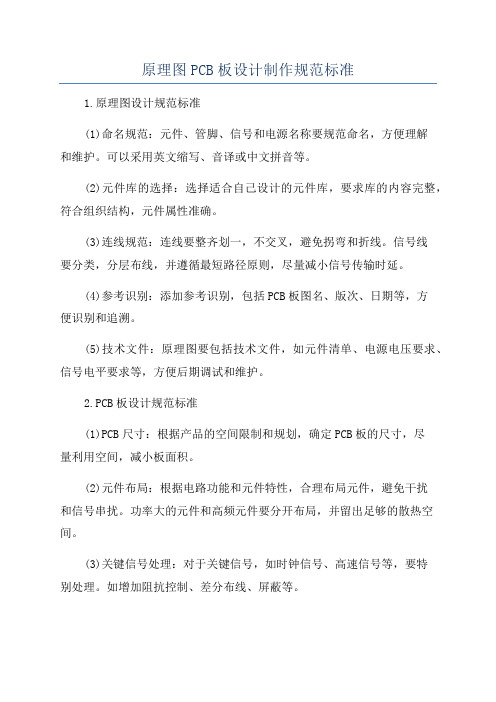

原理图PCB板设计制作规范标准

原理图PCB板设计制作规范标准1.原理图设计规范标准(1)命名规范:元件、管脚、信号和电源名称要规范命名,方便理解和维护。

可以采用英文缩写、音译或中文拼音等。

(2)元件库的选择:选择适合自己设计的元件库,要求库的内容完整,符合组织结构,元件属性准确。

(3)连线规范:连线要整齐划一,不交叉,避免拐弯和折线。

信号线要分类,分层布线,并遵循最短路径原则,尽量减小信号传输时延。

(4)参考识别:添加参考识别,包括PCB板图名、版次、日期等,方便识别和追溯。

(5)技术文件:原理图要包括技术文件,如元件清单、电源电压要求、信号电平要求等,方便后期调试和维护。

2.PCB板设计规范标准(1)PCB尺寸:根据产品的空间限制和规划,确定PCB板的尺寸,尽量利用空间,减小板面积。

(2)元件布局:根据电路功能和元件特性,合理布局元件,避免干扰和信号串扰。

功率大的元件和高频元件要分开布局,并留出足够的散热空间。

(3)关键信号处理:对于关键信号,如时钟信号、高速信号等,要特别处理。

如增加阻抗控制、差分布线、屏蔽等。

(4)电源和地线:电源和地线要分层布局,减小干扰。

同时要考虑电源电流的分布和供电稳定性,合理设计电源网络。

(5)线宽和间距:根据电流和信号传输要求,选择适当的线宽和间距。

高速信号要考虑传输线的阻抗匹配。

(6)引脚和焊盘:确定元件的引脚和焊盘布局,要考虑元件安装和焊接时的易用性和可靠性。

(1)层数和堆叠:根据电路复杂度和性能要求,确定PCB板的层数和堆叠方式。

(2)板材选择:根据电路功率、频率等要求,选择适合的板材,如FR4、高TG板等。

(3)焊接工艺:确定焊接工艺和焊接方式,如SMT、DIP等。

要考虑焊点的可靠性和焊接质量。

(4)表面处理:根据焊接方式和要求,选择适当的表面处理方式,如HASL、ENIG等,保证焊点的可靠性。

(5)丝印和标识:在PCB板上添加丝印和标识,包括元件位置、极性标识、工艺信息等,方便组装和维护。

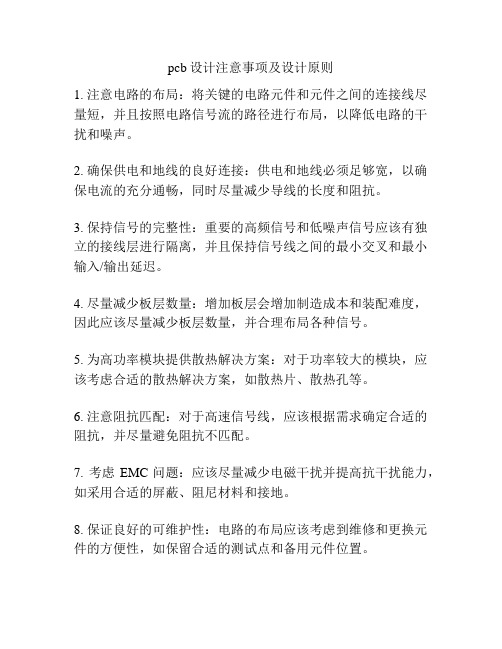

pcb设计注意事项及设计原则

pcb设计注意事项及设计原则

1. 注意电路的布局:将关键的电路元件和元件之间的连接线尽量短,并且按照电路信号流的路径进行布局,以降低电路的干扰和噪声。

2. 确保供电和地线的良好连接:供电和地线必须足够宽,以确保电流的充分通畅,同时尽量减少导线的长度和阻抗。

3. 保持信号的完整性:重要的高频信号和低噪声信号应该有独立的接线层进行隔离,并且保持信号线之间的最小交叉和最小输入/输出延迟。

4. 尽量减少板层数量:增加板层会增加制造成本和装配难度,因此应该尽量减少板层数量,并合理布局各种信号。

5. 为高功率模块提供散热解决方案:对于功率较大的模块,应该考虑合适的散热解决方案,如散热片、散热孔等。

6. 注意阻抗匹配:对于高速信号线,应该根据需求确定合适的阻抗,并尽量避免阻抗不匹配。

7. 考虑EMC问题:应该尽量减少电磁干扰并提高抗干扰能力,如采用合适的屏蔽、阻尼材料和接地。

8. 保证良好的可维护性:电路的布局应该考虑到维修和更换元件的方便性,如保留合适的测试点和备用元件位置。

9. 注意元器件的热分布:对于容易发热的元件,应该注意合适的散热和降温措施。

10. 使用规范的命名和标记:为了方便阅读和维护,应该使用规范的元件命名和标记方法,并为电路板添加清晰的标签和说明。

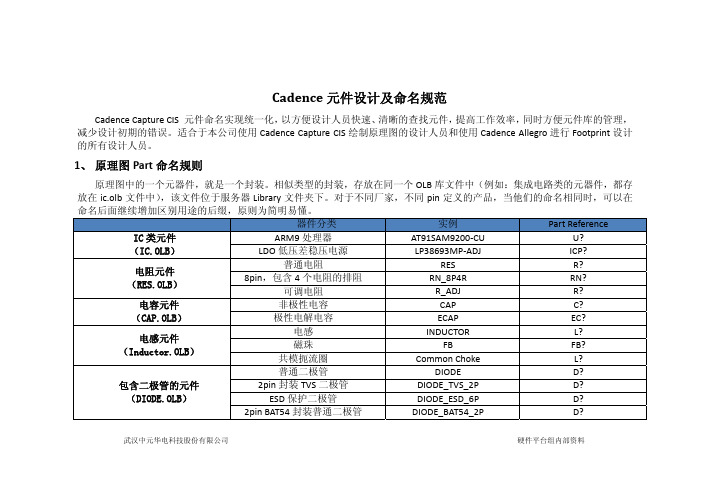

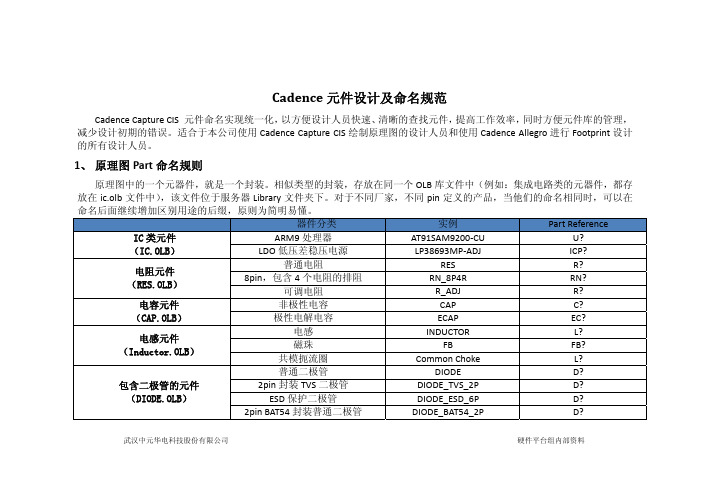

cadence元件设计及命名规范

竭诚为您提供优质文档/双击可除cadence元件设计及命名规范篇一:allegro_建库和封装命名规则前言器件封装是逻辑和物理的连接体。

所有的设计都是通过pcb来进行连接的。

封装的正确是正确pcb的第一步。

现在的实物封装有很多种,例如我们常见的bga、qFp、plcc等。

不同的封装有不同的作用和有缺点。

不同的eda工具有不同的封装建立保存方法和封装类型。

在cadence的设计软件allegRo种主要存在以下五种封装类型文件,每种类型有不同的用处。

1、packagesymbol、一般元器件封装,例如电阻电容、芯片icbga等。

他要求和逻辑设计中的项目标号一一对应。

是逻辑设计在物理设计中的反映。

包含:焊盘文件.pad,图形文件.dra、符号文件.psm和device.txt文件。

2、mechanicalsymbol、主要是结构方面的封装类型。

由板外框及螺丝孔等结构定位器件所组成的结构符号。

包含:图形文件.dra,和符号文件.bsm有时有必要添加device.txtfile。

有时我们设计pcb的外框及螺丝孔位置都是一样的,比如显卡,电脑主板、服务器和同一插筐的不同单板。

每次设计pcb时要画一次板外框及确定螺丝孔位置,显得较麻烦。

这时我们可以将pcb 的外框及螺丝孔建成一个mechanicalsymbol,在设计pcb时,将此mechanicalsymbol调出即可,这样就节约了时间。

3、Formatsymbol、辅助类型的封装(用来处理图形)。

例如:静电标识、常用的标注表格、logo等。

主要由图形文件.dra,和符号文件.osm组成。

是我们设计中不可缺少的一种封装。

4、shapesymbol、建立特殊焊盘所用的符号。

例如不规则焊盘、金手指焊盘的建立都要将不规则的形状建成个shapesymbol,然后在建立焊盘中调用此shapesymbol。

避免了在焊盘编辑中无法编辑不规则焊盘的局限。

这样,通过allegRo,我们可以设计任何你想要的焊盘形状。

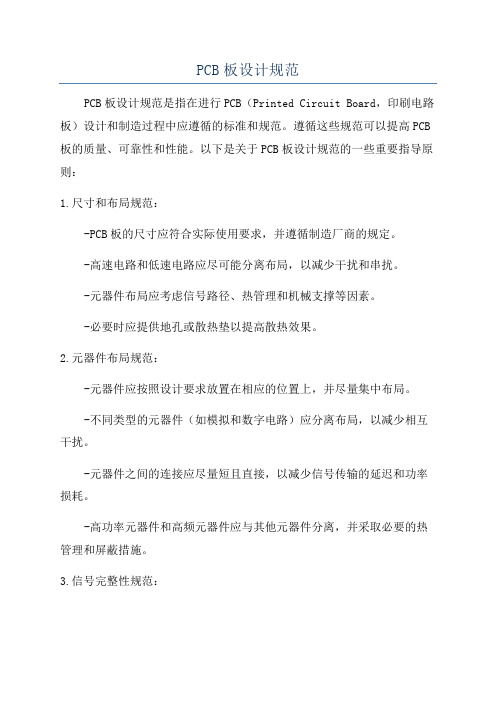

PCB板设计规范

PCB板设计规范PCB板设计规范是指在进行PCB(Printed Circuit Board,印刷电路板)设计和制造过程中应遵循的标准和规范。

遵循这些规范可以提高PCB 板的质量、可靠性和性能。

以下是关于PCB板设计规范的一些重要指导原则:1.尺寸和布局规范:-PCB板的尺寸应符合实际使用要求,并遵循制造厂商的规定。

-高速电路和低速电路应尽可能分离布局,以减少干扰和串扰。

-元器件布局应考虑信号路径、热管理和机械支撑等因素。

-必要时应提供地孔或散热垫以提高散热效果。

2.元器件布局规范:-元器件应按照设计要求放置在相应的位置上,并尽量集中布局。

-不同类型的元器件(如模拟和数字电路)应分离布局,以减少相互干扰。

-元器件之间的连接应尽量短且直接,以减少信号传输的延迟和功率损耗。

-高功率元器件和高频元器件应与其他元器件分离,并采取必要的热管理和屏蔽措施。

3.信号完整性规范:-控制线、时钟线和高速信号线应尽可能短,且避免平行走线,以减少串扰和时钟抖动。

-高速信号线应采用阻抗匹配技术,以确保信号的正确传输和减少反射。

-高速差分信号线应保持恒定的差分阻抗,并采用差分匹配技术,以减少干扰和降低功耗。

4.电源和接地规范:-电源线和地线应尽可能粗,以降低电阻和电压降。

-电源和地线应尽量采用平面形式,以减少电磁干扰和提供良好的电源和接地路径。

-多层PCB板应设有专用层用于电源和接地,以提高板层的抗干扰能力和电源噪声的影响。

5.焊接规范:-设计带有相应的焊接垫和焊盘,以便于元器件的焊接和可靠连接。

-焊盘和焊接垫的尺寸应符合元器件和制造工艺的要求,并考虑到热膨胀和热应力等因素。

-导线和焊盘间的间距应符合焊接工艺的要求,以确保焊接质量和可靠性。

6.标记和文档规范:-PCB板应有清晰的标记,包括元器件名称、值和位置、网络名称等。

-为了提供必要的参考和维护,应有详细的PCB设计文档,包括原理图、布线图和尺寸图等。

总的来说,遵循PCB板设计规范可以提高PCB板的可靠性、性能和一致性,减少制造和调试过程中的问题和风险。

PCB命名规则详解

焊盘类型简称标准图示命名S M D | P A D 表面贴装方焊盘SMDS命名方法:SMDS + 边长命名举例:SMDS30表面贴装长方焊盘SMDR命名方法:SMDR + 宽(Y) X 长(X)(mil)命名举例:SMDR21X27, SMDR10X40表面贴装圆焊盘SMDC命名方法:SMDC + 焊盘直径C(mil)命名举例:SMDC20,SMDC18,SMDC14表面贴装椭圆焊盘SMDO命名方法:SMDO + 宽(Y)X长(X)命名举例:SMDO28X165, SMDO37X280 ,SMDO50X280P T H | P A D 金属化通孔圆焊盘PADC命名方法:PADC +焊盘外径C(mil)+ D +孔径(mil)+(P)P表示压接孔,公差为+/-0.05mm命名举例:PADC45D30, PADC60D37金属化通孔方焊盘PADS命名方法:PADS+焊盘边长(P)(mil)+D+孔径(mil)命名举例:PADS45D30, PADS80D60金属化通孔椭圆焊盘PADO命名方法:PADO + 宽(Y)(mil)X长(X)(mil)-焊环宽度(mil)命名举例:PADO70X100-10金属化矩形焊盘椭圆通孔PADOS命名方法:PADOS+盘宽(Y)(mil)X长(X)(mil)-椭圆的宽(Y)(mil)X长(X)(mil)命名举例:PADOS100X120-70X100N P T H | P A D非金属化通孔圆焊盘PADNC命名方法:PADNC + 孔径(mil)命名举例:PADNC122, PADNC62非金属化方孔PADNS命名方法:PADNS + 边长(mil)命名举例:PADNS60非金属化长方孔PADNR命名方法:PADNR + 宽(mil)X长(mil命名举例:PADNR100X200非金属化通孔椭圆焊盘PADNo命名方法:PADNo + 宽(mil)X长(mil)命名举例:PADNo71X96热焊盘TH圆热焊盘命名方法:TH + 孔环外径命名举例:TH68椭圆热焊盘命名方法:TH +宽(mil)X长(mil)命名举例:TH68X96不规则焊盘PADSPD 命名方法:PADSPD+宽(mil)X长(mil)X高(mil)过孔VIA命名方法:VIA+孔径(mil)X焊盘外径(mil)命名举例:VIA10X20C_TH 插装瓷片电容C_TH_Pin间距C_TH_5r08C_TH_22r5TH=插装CE_SM 贴片电解电容CE_SM_Pin边距_元件主体直径单位:mmCE_SM_2r5_8CE_SM_4_10常用直径:6.3,8,10,12.5,16,18等CE_RA 径向引线插装电解电容CE_RA_Pin间距_元件体直径单位:mmCE_RA_2_5CE_RA_3r5_8CE_RA_2_5r5RA: Radial径向引脚常用直径:6.3,8,10,12.5,16,等CE_AX (暂不用) 轴向引线插装电解电容CE_AX_Pin间距_元件体直径单位:mmCE_AX_2_5CE_AX_5_10CE_AX_2_5r5常用直径:6.3,8,10,12.5,16,18等5.7.3 IC类(见表8)分类封装图示中文名称实例实体图及备注O PSOP小外形封装集成电路SOP5_50_173SOP6_50_300SOP16_50_150SOP20_50_200标准脚间距= 1.27mm SSOP 缩小外形封装集成电路SSOP8_25_100SSOP24_25_150SSOP28_25_150Pin间距< 1.27mm TSOP 薄小外形封装集成电路TSOP6_39_66TSOP28_22_450TSOP48_20_700装配高度≤ 1.27mm分类封装图示中文名称实例实体图及备注SOJ “J”形引脚小外形集成电路SOJ32_50_300SOJ32_50_400SOJ42_50_400标准脚间距= 1.27mmSEN 集成传感器电路SEN8_100_THSEN14_50_SM_TOPSEN14_50_SM_BOTTH: 插件SM:表贴DIP 双列直插式封装DIP6_100_300SIP 单列直插式封装SIP7_100SIP7_100_DOWN(卧装)Q F PQFP四侧引脚方形扁平封装命名规则:QFP+Pin数_Pin间距_实体面积_补充描述(L=Left,M=Mid)QFP44_r8_10X10QFP64_1_20X26MP5=中间带有五个孔的散热Pin封装本体厚度:(2.0~3.6mm)LQFP四侧引脚薄方形扁平封装命名规则:QFP+Pin数_Pin间距_实体面积_补充描述(L=Left,M=Mid)LQFP100_r65_20X26MLQFP40P5_r5_6r5X6r5封装本体厚度:(1.4mm)TQFP四侧引脚超簿方形扁平封装命名规则:QFP+Pin数_Pin间距_实体面积_补充描述(L=Left,M=Mid)TQFP128_r5_19X25MTQFP216_r5_34X34M封装本体厚度:(1.0mm)QFN方形扁平无引脚封装命名规则:QFN+Pin数_Pin间距_实体面积_补充描述QFN48P1_r5_8r2X8r2 P1特指带散热盘L PLCC塑封有引线芯片载体命名规则:PLCC+Pin数_Pin间距_实体面积_补充描述PLCC84_1r27_26X26PLCC32_1r27_18X20r5_BIOS含插座CCCLCC无引线陶瓷芯片载体命名原则:CLCC+Pin数_Pin间距_实体面积_补充描述CLCC16_r5_3X3(目前还未用到)JLCC“J”形引线陶瓷芯片载体命名规则:JLCC+Pin数_Pin间距_实体面积_补充描述JLCC16_r5_3X3(目前还未用到)BGA球形栅格触点阵列命名原则:BGA+Pin数_Pin间距_阵列大小_补充描述BGA160_40_1414BGA92_32_0921BGA300对于Pin不是按规则排列的则用封装代号直接加Pin CBGA陶瓷球形栅格触点阵列命名原则:CBGA+Pin数_Pin间距_阵列大小_补充描述CBGA256_40_1616CBGA350PGA塑封插针栅格触点阵列命名原则:PGA+Pin数_Pin间距_阵列大小_补充描述PGA370_32_3737PGA370_50_2626PGA400。

Cadence元件设计及命名规范

ssop

EP:exposed thermal pad

(pitch 一般 0.5 或 0.65mm,height 一

*TSOP 的引脚在芯片的短边,而 TSOP II 的引脚在芯片的 般 1.55mm)

长边

tssop86_050_1016

(pitch 一般 0.5 或 0.65mm,height 一

般 1.00mm)

其他连接器命名:

(类型标示)

类型标识的尽量详细

3.4、 插装类器件(存放于 DIP 文件夹)

1

插件晶体管零件命名方式:

(封装)_[pin 顺序]

此类封装为标准库

2

插件电容、电阻、电感、Diode 命名方式:

c(直径)_(pitch)_(孔名称)

l(Dx 或 Dy)_(pitch)_(孔名称)

c‐capacitor; l‐ inductor; DxDy‐长宽

3pin

2

TO 零件命名方式:

TO(类型)_[pin]_[pin 顺序]

例如: to252_gds

TO-252(DPAK)

to252_5

TO-263(D2PAK)

to263_3

如图从左下脚逆时针开始计算脚位顺序

3

SOIC(小外形集成电路)零件命名方式:

例如:

(封装)(pin)_(pitch)_(Body 长 x 宽)_[EP]

Q? Q? Q? Q? Q? LED? LED? OC? XL? XL? OSC? OSC? J? J? J? CN? CN? XS? XS?

2、 焊盘(PADSTACK)命名规则

PADSTACK 设计使用工具 Pad Designer,生成文件为:*.pad,存放于 PAD 文件夹。单位为:mil,所有字母使用英文小写,有效 位至少 3 位,不足 3 位使用 0 补足。

PCB封装命名规范V1

定义

电阻

电阻(Resistor)是所有电子电路中使用最多的元件,单位是“欧姆”,用字母“R”表示。

电容

电容(capacitor)是表征两个导电体和导电体间的电介质在单位电压作用下,储藏电荷能力的参量,单位是“法拉”,用字母“C”表示。

电感

电感(inductor)是表征一个载流线圈及其周围导磁物质性能的参量,是与电路中电磁感应现象相关的。电感是“自感”和“互感”的总称,单位是“亨利”,简称“亨”,自感用字母“L”表示,互感用字母“M”表示。

表示60mil×30mil的长方形表贴焊盘,阻焊层尺寸为64mil×34mil。

椭圆/圆形

① 焊盘类型:smd表示表面贴焊盘。

② (W):焊盘的标准长度。

③ 焊盘形状:椭圆焊盘取GE为obl,圆形焊盘取GE为cir。

④ (H):焊盘标准宽度。

⑤ _s:焊盘SolБайду номын сангаасer Mask标识。

⑥ (M):Solder Mask外扩的尺寸。

电子元器件零件PCB封装命名规范V1.2

11

本规范规定了印制电路板(简称PCB-Print Circuit Board)设计中, 制作电子元器件封装库时,电子元器件封装名称命名应遵守的基本规范和要求。

本规范适用于中国XXXX集团公司第XXX研究所所有电路设计项目。

12

IPC-7351B:Generic Requirements for SurfaceMountDesignand Land Pattern Standard

b) 命名形式里的宽度和高度的说法,参考cadence软件焊盘制作中的width和height。

c) 为避免相同焊盘由于方向不同而重复制作,规定图1中(W)≥(H)。

PCB命名规则

PCB元件封装库命名规则文章发表于:2010-09-15 08:301、集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mmW为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm3、电阻3.1 SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装3.3 水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容4.1 无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装4.2 SMT独石电容命名方法为:RAD+引脚间距如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N41486 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件9.1 贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管9.2 直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管9.3 数码管使用器件自有名称命名10、接插10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm如:DIP10-2.54表示针脚间距为2.54mm的10针脚双排插针10.3 其他接插件均按E3命名。

Cadence元件设计及命名规范

武汉中元华电科技股份有限公司

备注 例如: c0805;r0603;l1206;d1206;

例如: c7343‐31 7.3*4.3*3.1mm 或 cta、ctb…… 例如: ce43x43x52 4.3*4.3*5.2mm 例如: ck120x120x78 12*12*7.8mm ck132x99x64 13.2*9.9*6.4mm 例如: 8p4r_0603 8pin 包含 4 个电阻,单个封装为 0603 10p8r_0402 10pin 包含 8 个电阻,单个封装为 0402 例如: xtl2_49smd 49smd 无源晶体 osc4_7050 7*5mm 有源晶振

例如:

bga780‐100_28X28 28*28 行,间距 1mm,780 个焊点 BGA 封装

3.3、 连接器元件(存放于 CONNECTOR 文件夹)

1

header 类连接器命名:

hs(X)x(Y)_(pitch) _[shield]_[direction]_[n?]_[补充]

hd(X)x(Y)_(pitch)_[shield]_[direction]_[n?]_[补充]

ssop

EP:exposed thermal pad

(pitch 一般 0.5 或 0.65mm,height 一

*TSOP 的引脚在芯片的短边,而 TSOP II 的引脚在芯片的 般 1.55mm)

长边

tssop86_050_1016

(pitch 一般 0.5 或 0.65mm,height 一

般 1.00mm)

ck(长 x 宽 x 高)或(_器件厂家命名)

5

SMD 排阻命名方式:

(类型)_(封装大小)

6

SMD 频率元件命名方式:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.4.2走线时应注意:先走电源,关键信号(如:时钟、复位、高速信号线),强电的线,

以便有足够的空间满足其布线要求。

4.4.3 IC 的去耦电容与IC 连接时,线路应先经过电容再走向IC ,并保证其回路最短。

4.4.4 地线的走线

4.4.4.1采用单点接地或星形接地来降低各子系统间的互相干扰,即各个子系统应直接接电源、 地线,而不是各子系统串联,尤其是大电流、继电器、开关元件,

其电流不能经过MCU ,再流回电源。

如图:

单点接地

4.4.4.2因电流最终要流回电源,回路越大,易受干扰。

故地线回路应尽量小,如: 信号线与地

信号线地线 地线

差 佳

4.4.4.3高速信号线、时钟线应该用地线包围起来,以免受到干扰。

4.4.4.4模拟电路的地要与数字电路的地分开,如RC 滤波回路的电源与地应直接连到电源与地 上,而不是与其它子系统的电源.地直接串联。

4.4.4.5在高频电路中,模拟电路地不能有回路,防止出现共地噪声。

4.4.4.6在高频电路中,若双面板上电源、地需进行板层切换时,须放置多个贯孔,以减少阻抗。

4.4.5高频线路走线不能用900直角,建议用450角,这样可避免传输反射。

4.4.6在双面板中,电解电容, 发热元件,导体元件下面不能走线,以防止短路现象。

4.4.7在双面板中,两层的信号线要垂直走线。

4.4.8线离板边≥0.5mm ,以便与外壳隔离,距离金属外壳要≥4mm 。

4.4.9在高频电路中,高速信号线上尽量不要放贯孔。