简单分频时序电路的设计(三分频)

三分频电路设计

三分频电路设计你们有没有见过那种能把一种东西分成好几部分的小发明呀?就像把一个大蛋糕切成三块一样,三分频电路呢,就是把电信号分成三个不同部分的神奇电路。

我给你们讲个故事吧。

有一次我在听音乐,发现音响里发出来的声音有高音、中音和低音,特别好听。

后来我才知道,这里面就可能用到了类似三分频电路的东西。

就好比有三个小伙伴在唱歌,一个小伙伴负责高音部分,声音清脆响亮,像小鸟在枝头欢快地叫;一个小伙伴负责中音部分,声音圆润动听,就像我们平常说话那样舒服;还有一个小伙伴负责低音部分,声音低沉有力,就像是大笨钟敲响时的那种嗡嗡声。

而三分频电路就像是一个聪明的指挥家,把电信号按照不同的高低音要求,准确地分配给不同的“小歌手”,这样我们听到的音乐才会这么美妙。

那这个三分频电路是怎么做到的呢?咱们可以想象一下电路就像一条条小马路,电信号就是在路上跑的小汽车。

在三分频电路里,有一些特殊的“交通标志”和“岔路口”。

这些“交通标志”和“岔路口”就像一个个小关卡,它们可以让一部分电信号走这条“路”,另一部分走另一条“路”。

比如说,有一个“关卡”专门拦住那些高音的电信号,让它们从一条特定的“小路”通过,这就成了高音部分的电路;还有一个“关卡”拦住低音的电信号,让它们从另外的“小路”走,就形成了低音部分的电路;剩下的那些电信号就成了中音部分的电路啦。

咱们再举个例子吧。

假如我们有一个装满彩色珠子的盒子,我们想把珠子按照颜色分成三堆,红色一堆、蓝色一堆、绿色一堆。

我们可以用一些有小缝隙的板子,缝隙的大小刚好能让一种颜色的珠子通过,这样就能把珠子分开啦。

三分频电路里的那些小元件就像是这些有缝隙的板子,把不同的电信号分开。

虽然三分频电路听起来有点复杂,但是只要我们发挥想象,把它想象成生活里熟悉的东西,就会觉得很有趣。

而且它在我们生活中的很多地方都能用到呢,就像我们的音响、收音机这些能发出不同声音的东西里面,可能都藏着这个神奇的三分频电路。

网上下载的一个三分频电路说明

always@( negedge resetn or posedge clk or negedge clk) beginif (resetn==1'b0)begincounter[2:0]<=3'd0;out_clk<=1'b0;endelsebeginif (counter[2:0]==3'd5)begincounter[2:0]<=3'd0;endelsebeigncounter[2:0]<= counter[2:0]+1;end////////////////////////////////////////////////////if (counter[2:0]==3'd5 || counter[2:0]==3'd2)beginout_clk<=~out_clk;endendend其仿真结果是正确的这个逻辑无法综合。

存在半导体工艺问题。

2.下面给出一个逻辑图。

逻辑是用器件画出来的,保证不存在物理上的实现问题。

仿真图如下:也许有人要问,既然仿真都是对的,那么为什么要说实际中是80%工作呢?看到波形图上的clk1(黄色)上的那些毛刺了么,毛刺并不可怕,但是这个电路工作的基础却是那些毛刺,准确地说,那些毛刺是必须有的,是工作过程的比不可少的部份。

这样的电路是否能正常工作就很让人匪夷所思了。

我们能不能让电路的正常功能不依赖于毛刺呢?小结一下:以上的思路都是试图在输入的clk上做改造,试图在恰当的地方取正沿,恰当的地方取反沿。

但是要知道,这一定会导致竞争和冒险。

虽然逻辑上是可性的,但是实践中却没有那么简单。

这个时候,我们需要调整一下思路了:能不能营造一个安全的时机来切换时钟沿的选择?显然,这需要在切换时钟沿时,强制时钟输出固定电平,当切换完成后,在取消这个强制条件。

对么?我们来试试看。

3. 看看以下的代码,也是一段有趣的东西。

三分频代码

三分频代码三分频器的代码可以根据不同的编程语言和开发环境有所不同。

下面是一个简单的三分频器代码示例,使用Arduino开发环境编写:arduinoint clockPin = 13; // 连接系统时钟的引脚int outputPin1 = 12; // 第一个输出引脚int outputPin2 = 11; // 第二个输出引脚int outputPin3 = 10; // 第三个输出引脚void setup() {pinMode(clockPin, INPUT); // 将系统时钟引脚设置为输入模式pinMode(outputPin1, OUTPUT); // 将第一个输出引脚设置为输出模式pinMode(outputPin2, OUTPUT); // 将第二个输出引脚设置为输出模式pinMode(outputPin3, OUTPUT); // 将第三个输出引脚设置为输出模式}void loop() {int clockState = digitalRead(clockPin); // 读取系统时钟引脚的电平状态if (clockState == HIGH) { // 如果系统时钟为高电平,则进入以下分支digitalWrite(outputPin1, HIGH); // 第一个输出引脚为高电平digitalWrite(outputPin2, LOW); // 第二个输出引脚为低电平digitalWrite(outputPin3, LOW); // 第三个输出引脚为低电平} else { // 如果系统时钟为低电平,则进入以下分支digitalWrite(outputPin1, LOW); // 第一个输出引脚为低电平digitalWrite(outputPin2, HIGH); // 第二个输出引脚为高电平digitalWrite(outputPin3, LOW); // 第三个输出引脚为低电平}}在上述代码中,我们使用了三个引脚来分别输出三分频的三个信号。

3分频电路

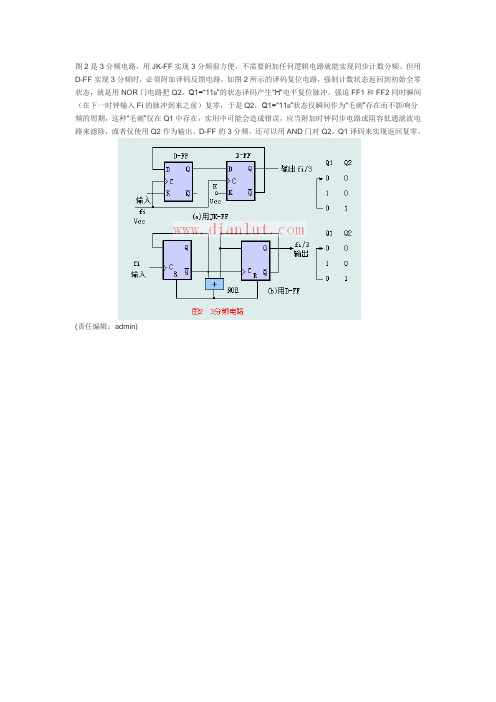

图2是3分频电路,用JK-FF实现3分频很方便,不需要附加任何逻辑电路就能实现同步计数分频。

但用D-FF实现3分频时,必须附加译码反馈电路,如图2所示的译码复位电路,强制计数状态返回到初始全零状态,就是用NOR门电路把Q2,Q1=“11B”的状态译码产生“H”电平复位脉冲,强迫FF1和FF2同时瞬间(在下一时钟输入Fi的脉冲到来之前)复零,于是Q2,Q1=“11B”状态仅瞬间作为“毛刺”存在而不影响分频的周期,这种“毛刺”仅在Q1中存在,实用中可能会造成错误,应当附加时钟同步电路或阻容低通滤波电路来滤除,或者仅使用Q2作为输出。

D-FF的3分频,还可以用AND门对Q2,Q1译码来实现返回复零。

(责任编辑:admin)。

最新三分频扬声器系统分频器电感的精确设计

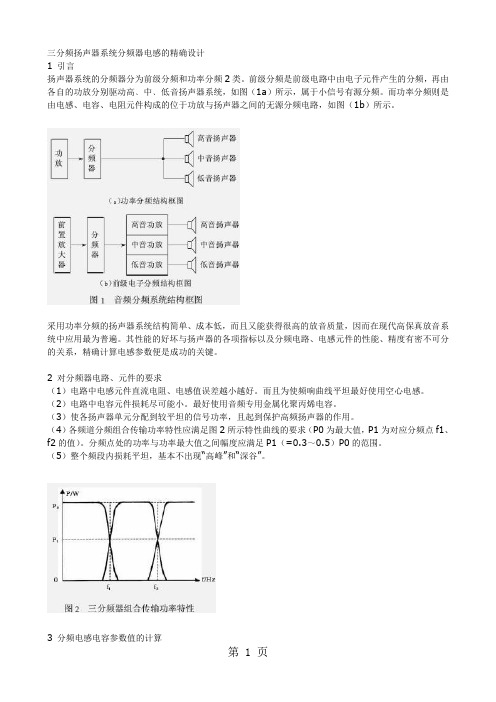

三分频扬声器系统分频器电感的精确设计三分频扬声器系统分频器电感的精确设计1 引言扬声器系统的分频器分为前级分频和功率分频2类。

前级分频是前级电路中由电子元件产生的分频,再由各自的功放分别驱动高﹑中﹑低音扬声器系统,如图(1a)所示,属于小信号有源分频。

而功率分频则是由电感、电容、电阻元件构成的位于功放与扬声器之间的无源分频电路,如图(1b)所示。

采用功率分频的扬声器系统结构简单、成本低,而且又能获得很高的放音质量,因而在现代高保真放音系统中应用最为普遍。

其性能的好坏与扬声器的各项指标以及分频电路、电感元件的性能、精度有密不可分的关系,精确计算电感参数便是成功的关键。

2 对分频器电路、元件的要求(1)电路中电感元件直流电阻、电感值误差越小越好。

而且为使频响曲线平坦最好使用空心电感。

(2)电路中电容元件损耗尽可能小。

最好使用音频专用金属化聚丙烯电容。

(3)使各扬声器单元分配到较平坦的信号功率,且起到保护高频扬声器的作用。

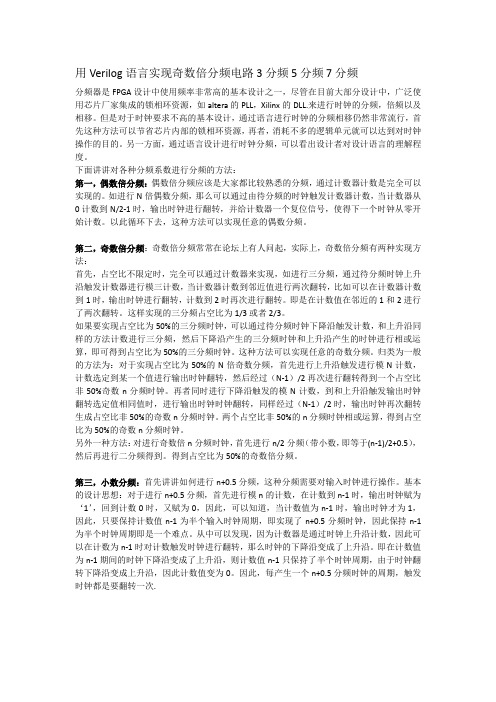

(4)各频道分频组合传输功率特性应满足图2所示特性曲线的要求(P0为最大值,P1为对应分频点f1、f2的值)。

分频点处的功率与功率最大值之间幅度应满足P1(=0.3~0.5)P0的范围。

(5)整个频段内损耗平坦,基本不出现“高峰”和“深谷”。

3 分频电感电容参数值的计算下面以三分频分频器为例说明其参数的计算,如图3所示。

1)计算分频电感L1,L2,L3,L4和分频电容C1,C2,C3,C4。

为了得到理想的频谱特性曲线,理论计算时可取:C1=C4,C3=C2,L1=L3,L4=L2,分频点频率为f1,(f2见图2),则分频点ω1=2πf0,ω2=2πf2。

并设想高、中、低扬声器阻抗均相同为RL。

每倍频程衰减12 dB。

2)实验修正C1,C2,C3,C4,L1,L2,L3,L4的值为精确起见,可用实验方法稍微调整C1,C2,C3,C4,L1,L2,L3,L4的值,以满足设计曲线﹙见图2﹚的要求。

简单分频时序逻辑电路的设计

电子信息工程学系实验报告课程名称:微机原理与接口技术实验项目名:简单分频时序逻辑电路的设计实验时间:2012.10.9班级:通信姓名:陈小凡学号:实验目的:1、熟悉ALTERA公司EDA设计工具软件max+plusII的安装和工作环境。

2、熟练的使用max+plusII软件中的各按钮的操作和原理。

3、学习和掌握使用max+plusII软件进行文本设计(二分频的设计为例)。

实验环境:max+plusII软件Windows7系统实验内容及步骤:一、clk-in的二分频clk-out的文本设计1、打开实验的工作环境,界面如下:图(一)工作环境界面2、按屏幕上方的“新建文件”按钮,或选择菜单“File”→“New”,出现如图4.13所示的对话框,在框中选中“Text Editor file”,按“OK”按钮,即选中了文本编辑方式。

其界面如图(二):图(二)选择文本3、在编辑窗口中输入在文本编辑窗口,输入Verilog语言,代码如下图(三)所示:其中字体的格式和大小均可在以上界面的上方的状态栏来改变。

成绩:指导教师(签名):图(三)二分频的always语句编辑代码4、在 File Name 对话框内输入设计文件名(如half-clk.v),然后选择 OK 即可保存文件。

在 File 菜单中选择 Save & Check项,检查设计是否有错误。

如果没有,在 File菜单中选择 Create Default Symbol 项,即可创建一个设计的符号。

在 MAX+PLUS II 菜单内选择Compiler 项。

则出现编译器窗口,如图(四)所示:图(四)检查文件显示可行选择 Start即可开始编译, MAX+PLUS II 编译器将检查项目是否有错,并对项目进行逻辑综合,然后配置到一个 Altera 器件中,同时将产生报告文件、编程文件和用于时间仿真用的输出文件。

5、选择菜单“File”→“New”,在出现的“New”对话框中选择“Waveform Editor File”按“OK”后将出现波形编辑器,选择菜单“Node ”→“Enter Nodes from SNF”,出现如图所示的选择信号结点对话框。

50%占空比三分频器地设计方法

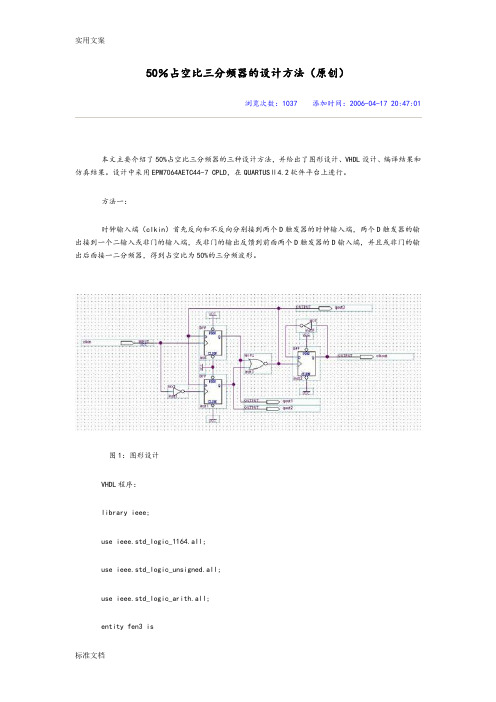

50%占空比三分频器的设计方法(原创)浏览次数:1037 添加时间:2006-04-17 20:47:01本文主要介绍了50%占空比三分频器的三种设计方法,并给出了图形设计、VHDL设计、编译结果和仿真结果。

设计中采用EPM7064AETC44-7 CPLD,在QUARTUSⅡ4.2软件平台上进行。

方法一:时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。

图1:图形设计VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen3 isport(clkin : in std_logic; --时钟输入qout1 : buffer std_logic;qout2 : buffer std_logic;qout3 : buffer std_logic;clkout : out std_logic --占空比为1/2的三分频输出 );end fen3;architecture behave of fen3 isbeginqout3<=qout1 nor qout2;process(clkin)beginif clkin'event and clkin='1' then --在上升沿触发qout1<=qout3;end if;end process;process(clkin)beginif clkin'event and clkin='0' then --在下降沿触发qout2<=qout3;end if;end process;process(qout3)variable tem:std_logic;beginif qout3'event and qout3='1' then --二分频 tem:=not tem;end if;clkout<=tem;end process;end behave;图2:编译结果图3:仿真结果方法二:设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

三分频时钟电路

三分频时钟电路

三分频时钟电路是一种将输入的时钟信号进行分频,得到三个不同频率的输出时钟信号的电路。

其输出频率是输入频率的1/3。

三分频时钟电路通常由双上升沿JK触发器和双下降沿JK触发器构成的三分频电路,这种电路可以实现对称的输出波形。

具体的实现方法是:在时钟上升沿触发时,将输入时钟信号的频率降低到1/3,得到第一个输出时钟信号;在时钟下降沿触发时,同样将输入时钟信号的频率降低到1/3,得到第二个输出时钟信号;在第二个输出时钟信号的下降沿触发时,再将输入时钟信号的频率降低到1/3,得到第三个输出时钟信号。

这样,就可以得到三个不同频率的输出时钟信号。

在实际应用中,三分频时钟电路可以用作芯片内部的多个不同频率的时钟源,提高芯片的性能和可靠性。

同时,三分频时钟电路还可以应用于其他需要不同频率时钟信号的场合。

三分频扬声器系统分频器电感的精确设计精品文档5页

三分频扬声器系统分频器电感的精确设计1 引言扬声器系统的分频器分为前级分频和功率分频2类。

前级分频是前级电路中由电子元件产生的分频,再由各自的功放分别驱动高﹑中﹑低音扬声器系统,如图(1a)所示,属于小信号有源分频。

而功率分频则是由电感、电容、电阻元件构成的位于功放与扬声器之间的无源分频电路,如图(1b)所示。

采用功率分频的扬声器系统结构简单、成本低,而且又能获得很高的放音质量,因而在现代高保真放音系统中应用最为普遍。

其性能的好坏与扬声器的各项指标以及分频电路、电感元件的性能、精度有密不可分的关系,精确计算电感参数便是成功的关键。

2 对分频器电路、元件的要求(1)电路中电感元件直流电阻、电感值误差越小越好。

而且为使频响曲线平坦最好使用空心电感。

(2)电路中电容元件损耗尽可能小。

最好使用音频专用金属化聚丙烯电容。

(3)使各扬声器单元分配到较平坦的信号功率,且起到保护高频扬声器的作用。

(4)各频道分频组合传输功率特性应满足图2所示特性曲线的要求(P0为最大值,P1为对应分频点f1、f2的值)。

分频点处的功率与功率最大值之间幅度应满足P1(=0.3~0.5)P0的范围。

(5)整个频段内损耗平坦,基本不出现“高峰”和“深谷”。

3 分频电感电容参数值的计算下面以三分频分频器为例说明其参数的计算,如图3所示。

1)计算分频电感L1,L2,L3,L4和分频电容C1,C2,C3,C4。

为了得到理想的频谱特性曲线,理论计算时可取:C1=C4,C3=C2,L1=L3,L4=L2,分频点频率为f1,(f2见图2),则分频点ω1=2πf0,ω2=2πf2。

并设想高、中、低扬声器阻抗均相同为RL。

每倍频程衰减12 dB。

2)实验修正C1,C2,C3,C4,L1,L2,L3,L4的值为精确起见,可用实验方法稍微调整C1,C2,C3,C4,L1,L2,L3,L4的值,以满足设计曲线﹙见图2﹚的要求。

即通过实验描绘频响曲线,从而得到C1,C2,C3,C4,L1,L2,L3,L4的最佳值。

50%占空比三分频器的设计方法.

50%占空比三分频器的设计方法(原创)浏览次数:1037 添加时间:2006-04-17 20:47:01本文主要介绍了50%占空比三分频器的三种设计方法,并给出了图形设计、VHDL设计、编译结果和仿真结果。

设计中采用EPM7064AETC44-7 CPLD,在QUARTUSⅡ4.2软件平台上进行。

方法一:时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。

图1:图形设计VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen3 isport(clkin : in std_logic; --时钟输入qout1 : buffer std_logic;qout2 : buffer std_logic;qout3 : buffer std_logic;clkout : out std_logic --占空比为1/2的三分频输出);end fen3;architecture behave of fen3 isbeginqout3<=qout1 nor qout2;process(clkin)beginif clkin'event and clkin='1' then --在上升沿触发qout1<=qout3;end if;end process;process(clkin)beginif clkin'event and clkin='0' then --在下降沿触发qout2<=qout3;end if;end process;process(qout3)variable tem:std_logic;beginif qout3'event and qout3='1' then --二分频tem:=not tem;end if;clkout<=tem;end process;end behave;图2:编译结果图3:仿真结果方法二:设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

Verilog实现三分频的多种方法(附有代码)

用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去,这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,占空比不限定时,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

[转载]分频电路,二分频、三分频和四分频

![[转载]分频电路,二分频、三分频和四分频](https://img.taocdn.com/s3/m/f1aace0c640e52ea551810a6f524ccbff121caac.png)

[转载]分频电路,⼆分频、三分频和四分频原⽂地址:分频电路,⼆分频、三分频和四分频作者:davis⾳箱的⾼中低频主要靠分频器来区分。

分频器按分频频段可分⼆分频、三分频和四分频。

⼆分频是将⾳频信号的整个频带划分为⾼频和低频两个频段;三分频是将整个频带划分成⾼频、中频和低频三个频段;四分频将三分频多划分出⼀个超低频段。

分频点与分频斜率是直接影响分频品质分频频率(交*频率)。

分频点是指两个相邻扬声器(如⼆分频中的⾼⾳与低⾳,三分频中的⾼⾳与中⾳,中⾳与低⾳)的频响曲线在某⼀频率上的相交点,通常为两个扬声器中功率输出的⼀半处(即-3dB点)的频率,要根据⾳箱和每个扬声器的频率特性和失真度等参数决定。

通常⼆分选购上,建议您在购买的时候⼀定要多加⼩⼼,不要盲⽬地听店主的推荐和介绍,买这种东西绝对不可以⼼急。

最好之前楼主多去⼀些⾳响论坛先去具体了解些⾳响知识。

个⼈建议楼主去⾼级别的钻⽯卖家购买,与卖家多聊聊,还可以通过聊天软件向曾经购买者在⼀个扬声器系统⾥,⼈们把箱体、分频电路、扬声器单元称为扬声器系统的三⼤件,⽽分频电路对扬声器系统能否⾼质量地还原电声信号起着极其重要的作⽤。

尤其在中、⾼频部分,分频电路所起到的作⽤就更为明显。

编辑摘要⽬录[隐藏 ]1 作⽤2 分频点3 分频⽅式4 优点5 挑选分频电路 - 作⽤分频电路作⽤如下:1、合理地分割各单元的⼯作频段;2、合理地进⾏各单元功率分配;3、使各单元之间具有恰当的相位关系以减少各单元在⼯作中出现的声⼲涉失真;4、利⽤分频电路的特性以弥补单元在某频段⾥的声缺陷;5、将各频段圆滑平顺地对接起来。

显然,分频电路的这些作⽤已被⼈们所认识和接受。

分频电路 - 分频点脉冲分频电路1·分频点指分频器⾼通、带通和低通滤波器之间的分界点,常⽤频率来表⽰,单位为赫兹。

分频点应根据各频段扬声器单元或⾳箱的频率特性和功率分配来具体确定。

2·分频点的选择:1)、考虑中低单元指向性实⽤边界频率f=345/d(d=单元振膜有效直径)。

Verilog实现三分频的多种方法(附有代码)

用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去,这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,占空比不限定时,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

三分频选频电路

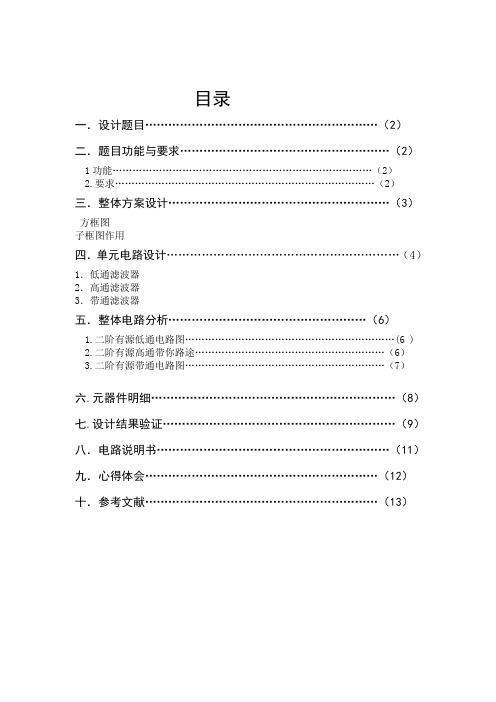

目录一.设计题目 (2)二.题目功能与要求 (2)1功能 (2)2.要求 (2)三.整体方案设计 (3)方框图子框图作用四.单元电路设计 (4)1.低通滤波器2.高通滤波器3.带通滤波器五.整体电路分析 (6)1.二阶有源低通电路图………………………………………………………(6 )2.二阶有源高通带你路途 (6)3.二阶有源带通电路图 (7)六.元器件明细 (8)七.设计结果验证 (9)八.电路说明书 (11)九.心得体会 (12)十.参考文献 (13)一.设计题目:三分频选频电路二.设计功能与要求功能:由RC元件与运算放大器组成的滤波器称为RC有源滤波器,其功能是让必然频率范围内的信号通过,抑制或急剧衰减此频率范围之外的信号,因受运算放大器带宽限制,这种滤波器仅适用于低频范围,依照频率范围可将其分为低通、高通、带通与带阻四种滤波器要求:(1)别离设计二阶RC低通、高通、带通滤波器电路,计算电路元件参数,拟定测试方案和步骤;(2)在面包板或全能板上安装好电路,测量并调整静态工作点;(3)测量技术指标参数。

三.总体方案设计1.方案框图RC有源滤波总框图2.子框图的作用1.RC网络的作用在电路中RC网络起着滤波的作用,滤掉不需要的信号,如此在对波形的选取上起着相当重要的作用,通常要紧由电阻和电容组成。

2 . 放大器的作用电路中运用了同相输入运放,其闭环增益 RVF=1+R4/R3同相放大器具有输入阻抗超级高,输出阻抗很低的特点,普遍用于前置放大级。

3.反馈网络的作用将输出信号的一部份或全数通过牧电路印象输入端,称为反馈,其中的电路称为反馈网络,反馈网络分为正、负反馈。

四.单元电路设计1. 低通滤波器低通滤波器电路图 传输函数依照202200/)()()(ωωω++==Q s s A s U s U s H i () f0=有 R1=Rf Rc= 取 R1=1K C=因此RF=1K,R=.2 . 高通滤波器高通滤波器电路图 传输函数二阶高通滤波器参数的确信:依照202200/)()()(ωωω++==Q s s A s U s U s H i f0=得 RF=4R1 RC= 取 R1= C=1UF 因此 RF= R=3. 带通滤波器带通滤波器电路图 传输函数二阶带通滤波器参数的确信:依照202000//)()()(ωωω++==Q s s Qs A s U s U s H i f0=得 RC= R0=取 R1=R2=R3=R C=1UF R0= 因此 R1=R2=R3= RF= C1=C2=C=1UF.五.整体电路分析依照上面的参数,用EWB 设计出如下的电路图1).二阶低通滤波器电路图图其中R1=1 k Ω R=300Ω RF= k Ω C=μ 电源电压为100Mv/60 Hz 其上限截止频率为12H f RCπ==1690 Hz 仿真波形仿真后取得幅频特性曲线为2).二阶高通滤波器电路图其中R1=200Ω R2=R3=570Ω RF=800Ω C=1μF电源电压为100Mv/60Hz 其上限中心频率为12H f RCπ==77 Hz 仿真波形:仿真后取得幅频特性曲线为3).二阶带通滤波器电路图其R1=R2=R3=200ΩR0=300ΩRf=500ΩC=1μF 电源电压为100Mv/60Hz仿真波形:仿真后取得幅频特性曲线为六.元器件明细名称数量名称数量1 kΩ电阻 3 2kΩ电阻 2 1UF 4 kΩ电阻 1 741芯片 3 kΩ电阻 4 万能板 1kΩ电阻 1 电烙铁 1kΩ电阻 2 电脑 1 七.设计结果验证实践说明,一个电子装置,即便依照设计的电路参数进行安装往往也难于达到预期成效。

EDA三分频器设计

EDA课程设计实验题目:占空比可调节的三分频器班级:电子081学号:***姓名:**1:实验要求:实现一个占空比可调节的三分频器,占空比可调节为1:3和1:2,时钟信号输入为CLK,带使能输入ENABLEBLE,输出信号分别为CLK1和CLK2对应两种占空比信号频率,设计实体统一为div.vhd。

2:源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity div isport(clk,enable:in std_logic;qout1,qout2:buffer std_logic;clk1,clk2:out std_logic) ;end entity div;architecture behave of div isbeginprocess(clk,enable)isvariable cnt:integer range 0 to 2;beginif clk'event and clk='1' thenif enable='1' thenif cnt=2 thencnt:=0;qout1<='1';elsecnt:=cnt+1;qout1<='0';end if;clk1<=qout1;end if;end if;end process;process(clk,enable)isvariable cnt:integer range 0 to 2;beginif clk'event and clk='0' then if enable='0' thenif cnt=2 thencnt:=0;qout2<='1';elsecnt:=cnt+1;qout2<='0';end if;end if;end if;end process;clk2<= qout1 or qout2;end behave;3:仿真波形:图(1)clk1为1:2占空比、clk2为1:3的占空比:4:结果分析:为了实现三分频,必需保证输出波形周期是原信号周期的三倍。

简单分频时序逻辑电路设计

always@(reset or ugf2ugc_sop_ff0 or wr_curr_state or ugf2ugc_eop_ff0 or drop_fra or fra_cnt or ugf2ugc_eop_ff1 ) begin if(reset==1'b0) wr_next_state = WR_IDLE; else begin case(wr_curr_state) WR_IDLE:begin if(ugf2ugc_sop_ff0==1'b1)begin if(drop_fra==1'b0) wr_next_state = WR_STATE; else wr_next_state = WR_DROP_STATE; end else wr_next_state = WR_IDLE; end WR_STATE:begin if((drop_fra==1'b1)||(fra_cnt>11'h7cf)) wr_next_state = WR_DROP_STATE; else if(ugf2ugc_eop_ff0==1'b1) wr_next_state = WR_LAST_STATE; else wr_next_state = WR_STATE; end WR_LAST_STATE:begin if(ugf2ugc_eop_ff1==1'b1)begin if((ugf2ugc_sop_ff0==1'b1)&&(drop_fra==1'b0)) wr_next_state = WR_STATE; else if((ugf2ugc_sop_ff0==1'b1)&&(drop_fra==1'b1)) wr_next_state = WR_DROP_STATE; else wr_next_state = WR_IDLE; end else wr_next_state = WR_LAST_STATE; end WR_DROP_STATE:begin if(ugf2ugc_eop_ff1==1'b1)begin if((ugf2ugc_sop_ff0==1'b1)&&(drop_fra==1'b0)) wr_next_state = WR_STATE; else if(ugf2ugc_sop_ff0==1'b0) wr_next_state = WR_IDLE; else wr_next_state = WR_DROP_STATE; end else wr_next_state = WR_DROP_STATE; end default: wr_next_state = WR_IDLE;

3分频器的设计

三分频器的设计时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。

图1:图形设计VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen3 isport(clkin : in std_logic; --时钟输入qout1 : buffer std_logic;qout2 : buffer std_logic;qout3 : buffer std_logic;clkout : out std_logic --占空比为1/2的三分频输出);end fen3;architecture behave of fen3 isbeginqout3<=qout1 nor qout2;process(clkin)beginif clkin'event and clkin='1' then --在上升沿触发qout1<=qout3;end if;end process;process(clkin)beginif clkin'event and clkin='0' then --在下降沿触发qout2<=qout3;end if;end process;process(qout3)variable tem:std_logic;beginif qout3'event and qout3='1' then --二分频tem:=not tem;end if;clkout<=tem;end process;end behave;图3:仿真结果方法二:设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。