Virtuosocadence教程轻松学(PPT课件)

合集下载

学习使用Cadence设计原理图共31页PPT

学习使用Cadence设计原理 图

41、实际上,我们想要的不是针对犯 罪的法 律,而 是针对 疯狂的 法律。 ——马 克·吐温 42、法律的力量应当跟随着公民,就 像影子 跟随着 身体一 样。— —贝卡 利亚 43、法律和制度必须跟上人类思想进 步。— —杰弗 逊 44、人类受制于法律,法律受制于情 理。— —托·富 勒

44、卓越的人一大优点是:在不利与艰 难的遭遇里百折不饶。——贝多芬

45、自己的饭量自己知道。——苏联

45、法律的制定是为了保证每一个人 自由发 挥自己 的才能 ,而不 是为了 束缚他 的才能 。—— 罗伯斯 庇尔

41、学问是异常珍贵的东西,从任何源泉吸 收都不可耻。——阿卜·日·法拉兹

42、只有在人群中间,才能认识自 己。——德国

43、重复别人所需要头脑。—— 玛丽·佩蒂博恩·普尔

41、实际上,我们想要的不是针对犯 罪的法 律,而 是针对 疯狂的 法律。 ——马 克·吐温 42、法律的力量应当跟随着公民,就 像影子 跟随着 身体一 样。— —贝卡 利亚 43、法律和制度必须跟上人类思想进 步。— —杰弗 逊 44、人类受制于法律,法律受制于情 理。— —托·富 勒

44、卓越的人一大优点是:在不利与艰 难的遭遇里百折不饶。——贝多芬

45、自己的饭量自己知道。——苏联

45、法律的制定是为了保证每一个人 自由发 挥自己 的才能 ,而不 是为了 束缚他 的才能 。—— 罗伯斯 庇尔

41、学问是异常珍贵的东西,从任何源泉吸 收都不可耻。——阿卜·日·法拉兹

42、只有在人群中间,才能认识自 己。——德国

43、重复别人所需要头脑。—— 玛丽·佩蒂博恩·普尔

Virtuoso软件的使用技巧ppt课件

45

• 版图的设计错误可以分成两类: 违反几何设计规则的错误——检查工具

DRC(Design Rules Check)。 版图与原理图一致性的错误——检查工具

LVS(Layout versus Schematic)。

46

Calibre →Run DRC

47

Rules →Run DRC

48

查找错误

Options→Display →Minor spacing

42

LSW

• AV (all visible) ;NV (non visible) ; • AS (all selectable) ;NS (non selectable) 。 43

常用的快捷键

• r:绘制长方形 • c:copy • F4:part/full • s:stretch • o:添加contact或via • i:调用模块 • q:修改属性 • k:尺 • shift+k:取消所有尺 • l:加label

57

Calibre →Run PEX

58

59

60

61

62

63

21

管脚命名必须与电路图中一致

22

23

24

调用生成的模块

25

常用的快捷键

i (instance):插入元件 f (full screen):全屏幕 w (wire) :连线 p (pin):加管脚 q (quality):编辑属性

e:进入下一层模块 ctrl+e:返回上一层模块 [ : 缩小两倍 ] :放大两倍

• Virtuoso的主要功能有: 1、绘制电路图 2、绘制版图 3、模拟电路的仿真分析(specture)

• Virtuoso其他功能:Verilog-Editor、 VerilogAEditor、 VHDL-Editor、 VHDLAMS-Editor、 Graphics-Editor、Text-Editor

• 版图的设计错误可以分成两类: 违反几何设计规则的错误——检查工具

DRC(Design Rules Check)。 版图与原理图一致性的错误——检查工具

LVS(Layout versus Schematic)。

46

Calibre →Run DRC

47

Rules →Run DRC

48

查找错误

Options→Display →Minor spacing

42

LSW

• AV (all visible) ;NV (non visible) ; • AS (all selectable) ;NS (non selectable) 。 43

常用的快捷键

• r:绘制长方形 • c:copy • F4:part/full • s:stretch • o:添加contact或via • i:调用模块 • q:修改属性 • k:尺 • shift+k:取消所有尺 • l:加label

57

Calibre →Run PEX

58

59

60

61

62

63

21

管脚命名必须与电路图中一致

22

23

24

调用生成的模块

25

常用的快捷键

i (instance):插入元件 f (full screen):全屏幕 w (wire) :连线 p (pin):加管脚 q (quality):编辑属性

e:进入下一层模块 ctrl+e:返回上一层模块 [ : 缩小两倍 ] :放大两倍

• Virtuoso的主要功能有: 1、绘制电路图 2、绘制版图 3、模拟电路的仿真分析(specture)

• Virtuoso其他功能:Verilog-Editor、 VerilogAEditor、 VHDL-Editor、 VHDLAMS-Editor、 Graphics-Editor、Text-Editor

培训资料Virtuoso软件使用技巧

Tool:Composer-Schematic

.精品课件.

14

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、幅员的绘制 • 6、幅员的验证DRC/LVS • 7、幅员后仿真

.精品课件.

15

添加元件

.精品课件.

e:进入下一层模块 ctrl+e:返回上一层模块 [ : 缩小两倍 ] :放大两倍

.精品课件.

26

主要ห้องสมุดไป่ตู้容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、幅员的绘制 • 6、幅员的验证DRC/LVS • 7、幅员后仿真

.精品课件.

Options→Display →Minor spacing

.精品课件.

42

LSW

• AV (all visible) ;NV (non visible) ; • AS (all selectable) ;.精N品课S件.(non selectable) 。 43

常用的快捷键

• r:绘制长方形 • c:copy • F4:part/full • s:stretch • o:添加contact或via • i:调用模块 • q:修改属性 • k:尺 • shift+k:取消所有尺 • l:加label

.精品课件.

50

由幅员生

成.gds文件

there is no

errors and

warning

messages

.精品课件.

51

LVS-1

.精品课件.

cadence教程轻松学

波形输入 PCB设计:原理图输入

25

EDA概述

CADENCE

• EDA设计方法:

(1)行为描述法 (2)IP设计与复用技术 (3)ASIC设计方法 (4)SoC设计方法 (5)软硬件协同设计方法

26

EDA概述

CADENCE

• IC设计工具按其用途分类:

(1)设计输入与仿真工具 (Cadence公司的Virtuoso composer、Verilog-XL、NC-verilog )

• 缺点:由于对工艺的依赖性使得其灵活性和可 移植性都较差。

17

EDA概述

CADENCE

• 固核IP(Firm IP)是已经基于一般工艺库进行 了综合和布局IP核,通常以网表的形式提交客 户使用。

• 固核IP在结构、面积以及性能的安排上都已进 行了优化。固核IP提供了介于软和IP和硬核IP 之间的一个折中方案,比起硬核IP,具有较好 的灵活性和可移植性,比起软和IP在性能和面 积上有较好的可预知性。

物理工具主要实现物理布局布线。 逻辑工具基于网表、布尔逻辑、传输时序等概念。 该两部分由不同工具承担,利用标准化的网表文件进行 数据交换。

22

EDA概述

CADENCE

• EDA应用于三方面: 印制电路板的设计(PCB) 可编程数字系统设计(CPLD、 FPGA、SOPC) IC设计(ASIC, Soc)

• 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

16

EDA概述

CADENCE

• 硬核IP(Hard IP)是经过布局、布线并针对某 一特定工艺库优化过的网表或物理级版图,通 常是GDSⅡ-Stream的文件形式。

25

EDA概述

CADENCE

• EDA设计方法:

(1)行为描述法 (2)IP设计与复用技术 (3)ASIC设计方法 (4)SoC设计方法 (5)软硬件协同设计方法

26

EDA概述

CADENCE

• IC设计工具按其用途分类:

(1)设计输入与仿真工具 (Cadence公司的Virtuoso composer、Verilog-XL、NC-verilog )

• 缺点:由于对工艺的依赖性使得其灵活性和可 移植性都较差。

17

EDA概述

CADENCE

• 固核IP(Firm IP)是已经基于一般工艺库进行 了综合和布局IP核,通常以网表的形式提交客 户使用。

• 固核IP在结构、面积以及性能的安排上都已进 行了优化。固核IP提供了介于软和IP和硬核IP 之间的一个折中方案,比起硬核IP,具有较好 的灵活性和可移植性,比起软和IP在性能和面 积上有较好的可预知性。

物理工具主要实现物理布局布线。 逻辑工具基于网表、布尔逻辑、传输时序等概念。 该两部分由不同工具承担,利用标准化的网表文件进行 数据交换。

22

EDA概述

CADENCE

• EDA应用于三方面: 印制电路板的设计(PCB) 可编程数字系统设计(CPLD、 FPGA、SOPC) IC设计(ASIC, Soc)

• 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

16

EDA概述

CADENCE

• 硬核IP(Hard IP)是经过布局、布线并针对某 一特定工艺库优化过的网表或物理级版图,通 常是GDSⅡ-Stream的文件形式。

(汇总)Virtuoso软件的使用技巧.ppt

最新.课件

3

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

最新.课件

4

• Exceed Broadcast →选择用户

最新.课件

5

设置环境变量:setenv DISPLAY IP:0

最新.课件

6

打开icfb

使icfb和终端可以同时使用

最新.课件

7

Tools →Library Manager

最新.课件

8

最新.课件

9

新建库: File→New →Library

最新.课件

10

最新.课件

11

最新.课件

12

File→New →Cell View

最新.课件

13

Tool:Composer-Schematic

• Virtuoso的主要功能有: 1、绘制电路图 2、绘制版图 3、模拟电路的仿真分析(specture)

• Virtuoso其他功能:Verilog-Editor、 VerilogAEditor、 VHDL-Editor、 VHDLAMS-Editor、 Graphics-Editor、Text-Editor

Virtuoso软件的使用技巧

最新.课件

1

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

最新.课件

2

• Cadence公司的Virtuoso是一个适用于高级模拟、 混合信号、射频和定制数字设计的定制设计平台, 并可以提供深亚微米(45nm)的数字元件特性验证.

Cadence新手简明教程精品PPT课件

8

9

10

11

需要填这两项

12

里面不需要 snap to grid

边框和引脚必须 snap to grid, 保证电气属性

13

14

15

如果需要更改原理图页大小,可以在工程文 件目录中选择相应的原理图页,右键选择 schematic page property

16

17

18

按p调出右侧的 place part窗口 从中选取需要的 元件,双击或 enter或点击面板 上的放置按钮摆 放该元件,可放 任意多个,放完 按ESC退出。

35

36

37

元器件的坐标 报告复合封装中没有使 用的元件

38

39

40

41

42

勾选了inter tool communication之后,在PCB 布局模式下,选中原理图页的一个元件, PCB中对应的封装就会高亮,并且可以移动

43

44

Allegro是Cadence公司推出的先进 PCB 设计 布线工具。 Allegro 提供了良好且交互的工 作接口和强大完善的功能,和它前端产品 Capture的结合,为当前高速、高密度、多 层的复杂 PCB 设计布线提供了最完美解决方 案。

45

制作pad 布线 检查、修改

制作symbol 设置规则 铺铜

导入网表 开摆件

删除孤岛 后处理

46

47

不要忘记这里

48

单层模式

49

50

菜单栏

工具栏

命令窗口

状态栏

标题栏 控制面板 整体视图

51

F3(开始走线) F4(显示属性) F6(完成) F8(oops,取消上一步操作) F9(cancel,取消本次命令) SF3(推挤走线)SF6(移动)SF4(测距) Ctrl+F5(color选项卡)ctrl+d(删除) 滚轮上下(或F11、F12)放大缩小

9

10

11

需要填这两项

12

里面不需要 snap to grid

边框和引脚必须 snap to grid, 保证电气属性

13

14

15

如果需要更改原理图页大小,可以在工程文 件目录中选择相应的原理图页,右键选择 schematic page property

16

17

18

按p调出右侧的 place part窗口 从中选取需要的 元件,双击或 enter或点击面板 上的放置按钮摆 放该元件,可放 任意多个,放完 按ESC退出。

35

36

37

元器件的坐标 报告复合封装中没有使 用的元件

38

39

40

41

42

勾选了inter tool communication之后,在PCB 布局模式下,选中原理图页的一个元件, PCB中对应的封装就会高亮,并且可以移动

43

44

Allegro是Cadence公司推出的先进 PCB 设计 布线工具。 Allegro 提供了良好且交互的工 作接口和强大完善的功能,和它前端产品 Capture的结合,为当前高速、高密度、多 层的复杂 PCB 设计布线提供了最完美解决方 案。

45

制作pad 布线 检查、修改

制作symbol 设置规则 铺铜

导入网表 开摆件

删除孤岛 后处理

46

47

不要忘记这里

48

单层模式

49

50

菜单栏

工具栏

命令窗口

状态栏

标题栏 控制面板 整体视图

51

F3(开始走线) F4(显示属性) F6(完成) F8(oops,取消上一步操作) F9(cancel,取消本次命令) SF3(推挤走线)SF6(移动)SF4(测距) Ctrl+F5(color选项卡)ctrl+d(删除) 滚轮上下(或F11、F12)放大缩小

最新文档-cadence精简教程-PPT精品文档

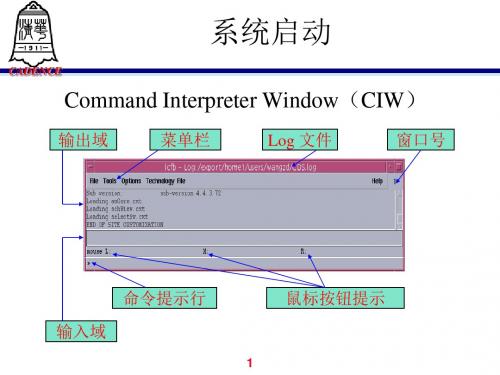

系统启动

CADENCE

Command Interpreter Window(CIW)

输出域

菜单栏

Log 文件

窗口号

命令提示行 输入域

鼠标按钮提示

1

帮助系统

CADENCE

两种方式寻求帮助 1 openbook

在UNIX提示符下输入命令 openbook: host >openbook &

2 工具在线帮助

22

版图设计工具-Virtuoso LE

CADENCE

主要创建命令

Rectangle-矩形 Polygon-多边形 Path-互联 Label-标签 Instance-例元 Contact-通孔

现在LSW中选中层,然后点击 创建命令,在画相应图形

23

绘制反相器版图

CADENCE

8

Virtuoso LE 使用介绍

CADENCE

第三步:建立版图单元

执行:LM->File->New->Cell View…

9

Virtuoso LE 使用介绍

CADENCE

第四步:打开版图单元

执行:CIW->File->Open…

选择库 选择视图

10

选择单元

版图设计工具-Virtuoso LE

46

版图验证

CADENCE

IC 后端流程图:

47

Cadence 版图验证工具

CADENCE

Diva

Diva 是 Cadence 的版图编辑大师Virtuoso集成 的交互式版图验证工具,具有使用方便、操作 快捷的特点,非常适合中小规模单元的版图验 证。

Dracula

CADENCE

Command Interpreter Window(CIW)

输出域

菜单栏

Log 文件

窗口号

命令提示行 输入域

鼠标按钮提示

1

帮助系统

CADENCE

两种方式寻求帮助 1 openbook

在UNIX提示符下输入命令 openbook: host >openbook &

2 工具在线帮助

22

版图设计工具-Virtuoso LE

CADENCE

主要创建命令

Rectangle-矩形 Polygon-多边形 Path-互联 Label-标签 Instance-例元 Contact-通孔

现在LSW中选中层,然后点击 创建命令,在画相应图形

23

绘制反相器版图

CADENCE

8

Virtuoso LE 使用介绍

CADENCE

第三步:建立版图单元

执行:LM->File->New->Cell View…

9

Virtuoso LE 使用介绍

CADENCE

第四步:打开版图单元

执行:CIW->File->Open…

选择库 选择视图

10

选择单元

版图设计工具-Virtuoso LE

46

版图验证

CADENCE

IC 后端流程图:

47

Cadence 版图验证工具

CADENCE

Diva

Diva 是 Cadence 的版图编辑大师Virtuoso集成 的交互式版图验证工具,具有使用方便、操作 快捷的特点,非常适合中小规模单元的版图验 证。

Dracula

Cadence软件使用教程 ppt课件

Allegro Constraint Manager Allegro约束管理器,布局布线约束规则的创建、管理、评估、检 查等,如物理间距、线长、线宽等。可以与Allegro PCB Editor和 Allegro PCB SI等完美集成,非常方便进行交互设计。

Allegro PCB Router 自动布线工具,对于有复杂设计规则的高密度电路板处理能力很强, 可以在Allegro PCB Editor中用自动布线命令调出来。这个布线工 具名气很大,对于简单的电路板,布线很美观,布通率很高。

Cadence软件使用教程

Cadence软件使用教程

1、利用OrCAD Capture CIS进行原理图设计 2、利用Cadence PCB Editor进行PCB布局布线 3、光绘文件(Artwork)制作,如何生成Gerber文件

Cadence软件使用教程

Cadence软件使用教程

1、系统的原理图工程文件 2、系统的PCB图工程文件 3、原件库、封装库文件 4、板上芯片的datasheet 5、给PCB厂商的Gerber文件(Artwork) 6、DSP6713程序的C语言源代码

Padstack Designer 创建及修改焊盘padstacks Allegro在创建零件封装时,焊盘需要单独设计,必须使用这个工具先创建焊盘。 DB Doctor 用于检查设计数据中的错误,在设计的每一个阶段执行,可以部分修复数据错误。 在生成光绘文件前必须进行DBDoctor检查。

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Allegro PCB Router 自动布线工具,对于有复杂设计规则的高密度电路板处理能力很强, 可以在Allegro PCB Editor中用自动布线命令调出来。这个布线工 具名气很大,对于简单的电路板,布线很美观,布通率很高。

Cadence软件使用教程

Cadence软件使用教程

1、利用OrCAD Capture CIS进行原理图设计 2、利用Cadence PCB Editor进行PCB布局布线 3、光绘文件(Artwork)制作,如何生成Gerber文件

Cadence软件使用教程

Cadence软件使用教程

1、系统的原理图工程文件 2、系统的PCB图工程文件 3、原件库、封装库文件 4、板上芯片的datasheet 5、给PCB厂商的Gerber文件(Artwork) 6、DSP6713程序的C语言源代码

Padstack Designer 创建及修改焊盘padstacks Allegro在创建零件封装时,焊盘需要单独设计,必须使用这个工具先创建焊盘。 DB Doctor 用于检查设计数据中的错误,在设计的每一个阶段执行,可以部分修复数据错误。 在生成光绘文件前必须进行DBDoctor检查。

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Virtuosocadence教程轻松学

EDA概述

• 软核IP(soft IP)是用可综合的硬件描述语言描述的 RTL级电路功能块,不涉及用与什么工艺相关的电路 和电路元件实现这些描述。

• 优点:设计周期短,设计投入少,不涉及物理实现, 为后续设计留有很大发挥空间,增大了IP的灵活性和 适应性。

• 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

• EDA设计方法:

(1)行为描述法 (2)IP设计与复用技术 (3)ASIC设计方法 (4)SoC设计方法 (5)软硬件协同设计方法

EDA概述

• IC设计工具按其用途分类:

(1)设计输入与仿真工具 (Cadence公司的Virtuoso poser、 Verilog-XL、NC-verilog )

EDA概述

• Cadence 公司简介:

成立于1988年,公司总部位于美国加利福 尼亚州的San Jose,是全球最大的EDA供应商。

• 产品涵盖领域:

包括系统顶层设计与仿真、信号处理、电 路设计与仿真、PCB设计与分析、FPGA及ASIC 设计以及深亚微米IC设计等。

EDA概述

• Cadence EDA工具分类:

• 集成电路制造过程示意图:

IC设计基础

• 集成电路设计域主要包括三个方面: 行为设计(集成电路的功能设计) 结构设计(逻辑和电路设计) 物理设计(光刻掩模版的几何特性和物 理特性的具体实现)

IC设计基础

• 集成电路设计层次主要包括五个层次:

(1)系统级 (2)算法级 (3)寄存器传输级(RTL级) (4)逻辑级 (5)电路级

• 固核IP在结构、面积以及性能的安排上都已进 行了优化。固核IP提供了介于软和IP和硬核IP 之间的一个折中方案,比起硬核IP,具有较好 的灵活性和可移植性,比起软和IP在性能和面 积上有较好的可预知性。

Virtuoso软件的使用技巧模板.ppt

优选文档

29

Browse →Add

优选文档

30

设定仿真参数:Analyses →Choose

优选文档

31

优选文档

32

优选文档

33

节点电流:Outputs →To Be Saved Select On Schematic

优选文档

34

保存仿真参数:Session → Save state

优选文档

优选文档

40

必须确保绘制版图需要的工艺文件与 版图所在的库是优在选文档同一个目录下的41

Options→Display →Minor spacing

优选文档

42

LSW

• AV (all visible) ;NV (non visible) ; • AS (all selectable) ;优N选文S档(non selectable) 。 43

优选文档

14

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

优选文档

15

添加元件

优选文档

16

修改元件属性

优选文档

每次 重新 打开 电路 图都 要进 行设 置。

优选文档

26

主要内容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

优选文档

27

仿真环境:Tools →Analog Environment