LVDS-VGA信号转换器说明书101020

VGA系列矩阵切换器使用说明书

设备箱盖和箱底可能有散热用的开孔,不要堵塞这些开孔,以防热量积聚,损坏设备。

设备固定 ——

合理固定设备,确保设备放置合适并且稳固,防止设备跌落。

环境 ——

设备工作的环境要注意防尘、防潮。

维修 ——

所有的维修应交给专业维修人员完成,不要尝试自己维修设备。为防止电击危险,不要擅自打开箱盖。

第 3 页 共 23 页

故障检修在发生下列问题时请先作相应的检查常见问题可能的原因解决方案某一路视频存在网纹低频干扰信号线的地线接触不良把地线接好多路视频存在网纹低频干扰系统的地线存在干扰把系统的地线接到大地上保险丝熔断更换熔断丝电源指示灯不亮电源插头接触不良或电源线断路把电源插头插好或更换电源线操作失灵lock指示灯亮把lock指示灯按灭无信号输出行或场输入输出信号线存在接触不良短路断路请检查行或场输入输出信号线某一路输入存在缺色输入rgb信号线接触不良请把缺色路的输入信号线接好系统的地线接触不良把系统地线接到大地上图像不稳定信号地线接触不良把该路地线接好黑白溢出显示设备亮度或对比度调节不合把设备亮度或对比度调至正常黑边图像变形信号地线接触不良接好地线电源电压低调高电源电压指示灯非正常闪烁电源线接触不良接好电源如果还有问题请与销售商联系

D

FE G

AB

D

C

VGA16x16

FG E

AB

C

VGA32x16

D

FG E

第 8 页 共 23 页

AB VGA32x32

VGA 系列矩阵切换器使用说明书 FG E

AB

FG E

A. VGA 输入接口。 B. VGA 输出接口。 C. 音频输入接口。 D. 音频输出接口。 E. 电源接口。 F. RS232 输入接口(公头)。和计算机通信的上行线连接口。 G. RS232 环出接口(母头)。和其它设备级联的下行线连接口。

ADI CN-0282:USB供电的DVI HDMI至VGA转换器(HDMI2VGA) 使用手册说明

ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

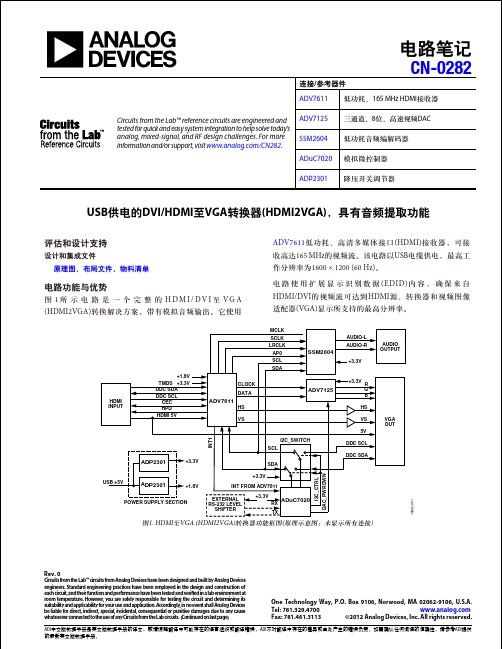

CN-0282Circuits from the Lab™ reference circuits are engineered and tested for quick and easy system integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit /CN282.ADV7611低功耗、165 MHz HDMI 接收器 ADV7125 三通道、8位、高速视频DACSSM2604 低功耗音频编解码器ADuC7020 模拟微控制器ADP2301降压开关调节器USB 供电的DVI/HDMI 至VGA 转换器(HDMI2VGA),具有音频提取功能Rev. 0Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devicesengineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and veri ed in a lab environment at room temperature. However , you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly , in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113©2012 Analog Devices, Inc. All rights reserved. HDMI INPUTTMDS DDC SDA DDC SCL CEC ADV7611CLOCK DATAHS VSADV7125R VGA OUTDDC SDADDC SCL ADuC7020SDASCLSSM2604MCLK SCLK LRCLK AP0AUDIO-L AUDIO OUTPUTAUDIO-RHPD I2C_SWITCH G BHS VS HDMI 5V5VSCL SDAI 2C _C T R LD A C _P W R D W NI N T 1INT FROM ADV7611EXTERNAL RS-232 LEVEL SHIFTERRX TXADP2301ADP2301USB +5VPOWER SUPPLY SECTION+1.8V+3.3V +3.3V+1.8V +3.3V+3.3V+3.3V+3.3V10892-001图1. HDMI 至VGA (HDMI2VGA)转换器功能框图(原理示意图:未显示所有连接)电路笔记连接/参考器件评估和设计支持设计和集成文件原理图、布局文件、物料清单电路功能与优势图1所示电路是一个完整的H D M I /D V I 至V G A (HDMI2VGA)转换解决方案,带有模拟音频输出。

矩阵VGA用户手册(通用)

VGA矩阵切换器16系列用户手册目录一.矩阵系统描述: (3)1.1矩阵系统功能说明 (3)1.2矩阵系统系列 (3)二、矩阵安装说明: (4)2.1矩阵面板及接口: (4)2.2串口通讯端口及连线方法 (4)三、矩阵的控制方式说明 (5)3.1面板按键输入操作方式: (5)3.2遥控控制操作方式 (6)3.3后台终端软件操作 (7)四、串口通讯协议: (10)五、矩阵设备电气计数参数 (11)六、常见故障及维护 (12)一.矩阵系统描述:1.1 矩阵系统功能说明VGA矩阵切换系统,是全交叉高性能的设备,应用于VGA信号切换。

主要应用于电视广播系统信号切换和交换,多功能媒体会议厅,大屏幕显示工程政府会议厅,医院医疗讨论会议厅,电视台转播信号切换,交互式多媒体教室,及军队指挥视频会议厅。

VGA系列矩阵切换器优良品质来自我们雄厚的技术实力,我们选用业界性能最好的芯片,对切换器的电路的每一个细节进行精心的设计,以确保切换器的优良品质。

经严格测试,VGA切换器的信号带宽为500MHz(-3db),能支持分辨率为2048x1536 60hz的刷新频率和1024x768 200Hz的刷新频率,完全能满足各种严要求,高品质的场合;视频为200MHz (-3db),不仅能支持现在的各种制式的视频信号,也能满足将来的高清析电视(HDTV)的带宽要求。

VGA系列矩阵切换器为用户提供了很好的人机接口,方便用户使用。

VGA系列矩阵切换器带有单色或彩色中文液晶显示,RS232通讯接口,RS422通讯接口(可选),带有断电现场保护功能,能读取和存储多达100个用户场景,还有专门的配套控制软件。

可以与计算机、遥控系统或各种远端控制设备配合使用。

系统配备了多套串口指令,兼容主流矩阵的串口指令集。

此说明书适于16系列全部VGA矩阵切换器,根据规模不同,略有差异。

1.2 矩阵系统系列➢矩阵命名规则: VGAXXYY;➢VGA:代表VGA矩阵;➢XX代表输入端口输: 如08 代表输入端口数为8;➢yy代表输出端口输: 如04 代表输入端口数为4;二、矩阵安装说明:2.1 矩阵面板及接口:前面板示意图:红外接收口成功指示灯电源指示灯操作灯嗡鸣器口LED)前面板由按键和液晶显示及状态灯组成,按键用于操作命令的输入;2U设备配置由128*32点阵组成,可显示两行共32个汉字的中文液晶,设备配置由128*64点阵组成的中文液晶,用于设备的操作和运行状态的显示,状态灯显示用户的操作状态。

VGA网线网络传输器(1080p)说明书

高清视频传输及高清编解码专业厂商VGA网络传输器产品说明书VGA网络传输器说明书一、设备简介VGA-B3/J3网络传输器是由VGA编码器(VGA-B3)和VGA解码器(VGA-J3)组成,通过局域网或网线来传输VGA、Audio、RS232信号。

在多媒体应用系统中,往往需要把VGA数字视频信号、音视频信号、RS232控制信号进行远距离传输。

但使用普通的电缆长距离传输时,总会出现输出信号差,容易受干扰,显示出来的图像会出现模糊、拖尾、分色等现象。

同时传输距离短,要多条电缆才能同时传输这些信号,不能满足多媒体信息发布、高清摄像机等场合长距离传输的要求,使用VGA-B3/J3网络传输进行传输,完全解决了此类问题,由于VGA接收器设置有二个网络接口,可以进行级联传输,解决一个编码器带多台解码器的问题。

同时,网络传输具有衰减小、抗干扰性能强、安全性能高、体积小、重量轻等优点,所以在长距离传输和特殊环境等方面具有无法比拟优势。

此外, VGA-B3/J3可以同时传输RS232串口信号,用于与液晶屏通讯、摄像机云台,也可作为触模屏的远距离传输。

此款VGA网络传输器支持HDCP功能,可直接传输蓝光高清光盘机播放的节目。

VGA 网络传输器设备在多媒体系统中应用,即节省施工成本及走线的复杂性,又能保证高品质的目标为可能。

VGA-B3是编码器, VGA- J3是解码器,二设备配合使用可实现经VGA-B3编码器把VGA、Audio、RS232信号经网络发送给多台ZY-VGA- J3解码器,特别适用于列车站台内高清视频信号的传输,军事演习、高清摄像机等各种长距离的应用。

注意:开机时间约20秒二、装箱清单当您打开包装,请确保符合以下设备及配件的使用。

·VGA编码器一台·VGA解码器一台·电源变换器二只·使用说明书、合格证、质保卡各一份三、连接设备介绍如何连接VGA-B3编码器和VGA-J3解码器VGA-B3是编码器,连接到您的电脑或媒体播放或高清摄像机等设备。

3代LVDS-VGA信号转换器说明书V1.1

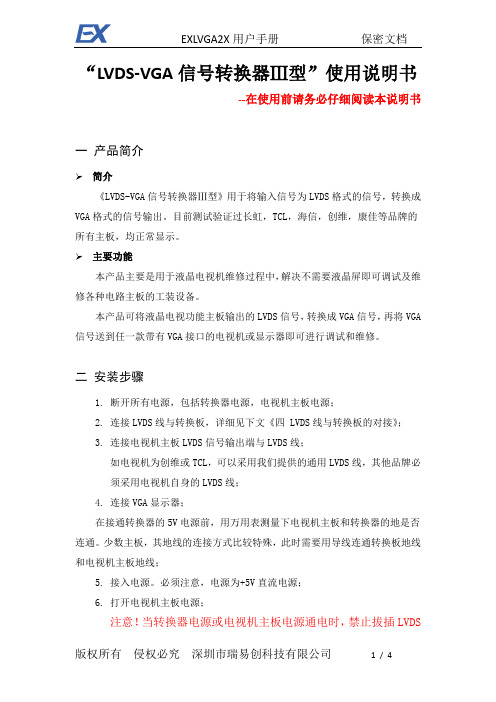

“LVDS-VGA信号转换器Ⅲ型”使用说明书--在使用前请务必仔细阅读本说明书一产品简介简介《LVDS-VGA信号转换器Ⅲ型》用于将输入信号为LVDS格式的信号,转换成VGA格式的信号输出。

目前测试验证过长虹,TCL,海信,创维,康佳等品牌的所有主板,均正常显示。

主要功能本产品主要是用于液晶电视机维修过程中,解决不需要液晶屏即可调试及维修各种电路主板的工装设备。

本产品可将液晶电视功能主板输出的LVDS信号,转换成VGA信号,再将VGA 信号送到任一款带有VGA接口的电视机或显示器即可进行调试和维修。

二安装步骤1.断开所有电源,包括转换器电源,电视机主板电源;2.连接LVDS线与转换板,详细见下文《四 LVDS线与转换板的对接》;3.连接电视机主板LVDS信号输出端与LVDS线;如电视机为创维或TCL,可以采用我们提供的通用LVDS线,其他品牌必须采用电视机自身的LVDS线;4.连接VGA显示器;在接通转换器的5V电源前,用万用表测量下电视机主板和转换器的地是否连通。

少数主板,其地线的连接方式比较特殊,此时需要用导线连通转换板地线和电视机主板地线;5.接入电源。

必须注意,电源为+5V直流电源;6.打开电视机主板电源;注意!当转换器电源或电视机主板电源通电时,禁止拔插LVDS线和转换板!下图分别为标清主板和高清主板完成安装的示意图三关机步骤1.关闭电视机主板电源;2.关闭转换器5V电源;3.拔开LVDS线或者转接板;四 LVDS线与转换板的对接4.1 创维和TCL液晶电视主板与转换板的对接由于创维及TCL电视机主板的LVDS输出端的线序是一致的,因此,我们可以采用通用的LVDS线加上转换板进行连接;通用LVDS线的一端必须接到转接板的P1端口,另一端的第一脚与电视机主板LVDS插座的第1脚对齐,插入即可。

4.2 其他品牌液晶电视主板与转换板的对接除创维与TCL 外的液晶电视,由于电视主板的LVDS 接口的线序种类较多,此时,采用待维修的电视主板原配的LVDS 线进行连接。

LVDS转VGA(DVI)使用手册书

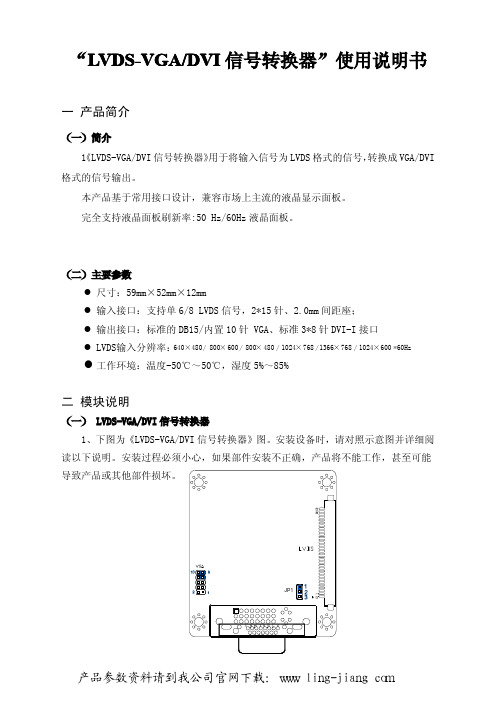

(二)主要参数 � 尺寸:59mm×52mm×12mm � 输入接口:支持单 6/8 LVDS 信号,2*15 针、2.0mm 间距座; � 输出接口:标准的 DB15/内置 10 针 VGA、标准 3*8 针 DVI-I 接口

640×480 / � LVDS输入分辨率: 800× 600 / 800× 480 / 1024× 768 / 1366× 768 / 1024× 600 *60Hz

VGA1

11 15

ห้องสมุดไป่ตู้

6

10

1

5

Setting Function

1Pin 2Pin 3Pin 4Pin 5Pin CRT_R GND CRT_G GND CRT_B

Setting Function

6Pin 7Pin 8Pin 9Pin 10Pin GND CRT_HSYNC GND CRT_VSYNC GND

� 工作环境:温度-50℃~50℃,湿度 5%~85% 二 模块说明

(一) LVDS-VGA/DVI 信号转换器 1、下图为《LVDS-VGA/DVI 信号转换器》图。安装设备时,请对照示意图并详细阅 读以下说明。安装过程必须小心,如果部件安装不正确,产品将不能工作,甚至可能 导致产品或其他部件损坏。

VGA2

DVI-I

/DVI 信号转换器”使用说明书 “LVDS-VGA LVDS-VGA/DVI

一 产品简介

(一)简介 《LVDS-VGA/DVI 信号转换器》 1 用于将输入信号为 LVDS 格式的信号, 转换成 VGA/DVI 格式的信号输出。 本产品基于常用接口设计,兼容市场上主流的液晶显示面板。 完全支持液晶面板刷新率:50 Hz/60Hz 液晶面板。

JP1

VGA 系列矩阵说明书 (1)

TMX-VGA系列使用手册注意一.产品简介1.1关于VGA系列矩阵切换器VGA系列矩阵切换器, 是一款高性能的专业PC信号切换设备, 用于多个PC信号输入输出交叉切换。

提供复合VGA信号的输入输出端子,每路分量信号单独传输,单独切换,使信号传输衰减降至最低,同时在每一路信号上增加长线增益模块,保证图像信号高保真输出40米以上。

VGA系列矩阵切换器,主要应用于广播电视工程、多媒体会议厅、大屏幕显示工程,电视教学、指挥控制中心等场合。

VGA系列矩阵切换器,采用性能极高的处理芯片。

信号频宽达350MHz,带有断电现场保护,LCD液晶显示,内嵌智能控制及管理软件,提供RS232通讯接口, 可以与PC、遥控系统或各种远端控制设备,(如快思聪,AMX, CR-PGM等控制系统)配合使用。

VGA系列矩阵提供连网接口,可以让多台VGA矩阵串联使用,以扩充多路端口。

本说明书以VGA8x8矩阵为例,其它型号矩阵使用方法,参照VGA8x8的使用说明即可。

1.2 VGA矩阵切换器的分类根据不同场合及不同用户的需求,VGA矩阵系列分为以下几个型号:VGA4X2 4路VGA输入2路VGA输出VGA4X4 4路VGA输入4路VGA输出VGA8X1 8路VGA输入1路VGA输出VGA8X8 8路VGA输入8路VGA输出VGA16X1 16路VGA输入1路VGA输出VGA16X8 16路VGA输入8路VGA输出VGA16X1616路VGA输入16路VGA输出VGA24X824路VGA输入8路VGA输出VGA24X1624路VGA输入16路VGA输出VGA32X132路VGA输入1路VGA输出VGA32X832路VGA输入8路VGA输出VGA32X1632路VGA输入16路VGA输出VGA48X2448路VGA输入24路VGA输出VGA48X4848路VGA输入48路VGA输出VGA64X6464路VGA输入64路VGA输出1.3远端计算机输入、远端控制及通讯端口说明VGA 矩阵的接口分为电脑输入\输出接口, 接口为标准15VGA HDF 接头 VGA 系列矩阵均提供标准 RS-232通讯接口, 遥控接收接口, 允许用户使用各种,远端控制设备(如个人电脑、Crestron 中央控制系统、AMX 中央控制系统、CR-PGM 中央控制系统等)以及遥控器对 VGA 矩阵系统进行控制。

VGA 延长器 用户手册说明书

VGA 延长器(本地端)(远端)(VGA-E80)用户手册 V1.0包装盒内包括 —1个VGA-L80(本地端) 1个VGA-R80(远端) 1本用户手册1个DC 12V/600mA 电源1条VGA 1.2米长的线材(HD-15公头对公头) 以上如有缺少,请与经销商联系。

特性通过VGA 延长器, 可以将一台主机的信号显示在远处的一台显示器上并且可以将VGA 信号传输至80米远处的显示器。

失真补偿是可调的。

VGA 信号增益是可调的。

支持单边供电,本地端或远端其中之一须连接电源。

本地端或远端两者皆可作为供电来源装置。

规格功能VGA-L80VGA-R80VGA 输入/输出接口HD-15母头 x 1RJ-45 接口 1最大分辨率1280x1024 60Hz 线材长度 80米(Max.) 电源 (Min.)DC 12V 600mA外壳 金属壳重量135g 140g尺寸(长x 宽x 高)92x34x22 mm本地端前视图1. 电源接口2. 电源灯3. CAT.5 (RJ-45接口)本地端后视图1. VGA 输入(HD-15母头接口)-1-远端前视图1. 电源接口2. 电源灯3. CAT.5 (RJ-45接口)远端后视图1. VGA 输出(HD-15母头接口)远端背视图1. EQ – 调节补偿因线材长度而产生的失真(调节它可以让影像更清晰)2. GAIN – 调节亮度安装1. 关闭主机。

2. 用HD-15公头对公头的线材将VGA-E80延长器本地端的HD-15输入母头连接到主机上。

3. 用CAT.5 线材将VGA-E80延长器本地端和远端连接起来。

4. 用HD-15公头对公头的线材将VGA-E80延长器远端的HD-15母头连接到显示器上。

5. 打开显示器和主机。

注:建议使用远端连接电源,以获得较佳视讯品质。

若使用本地端连接电源,则传输距离可能缩短。

-2-CAT.5/5E 与CAT.6线材的距离和分辨率50米2048x1536 1280x10241024x768CAT.5/5E80米 800x60030米 1920x144050米 1280x1024CAT.6 80米 800x600PS.建议使用CAT.5 线材,因为它的性能更优越。

杭州瑞盟科技有限公司MS90C104 30bit平板显示器LVDS信号接收器说明书

2013.08.12

共9页 第6页

图 4.锁相环设置时间

MS90C104

图 5.接收器状态

Vdiff=(RxIN+)-(RxIN-),……(RxCLKIN+)-(RxCLKIN-)

图 6.并行 TTL 输出数据与 LVDS 输入数据匹配关系

Previous Cycle

Next Cycle

RCLK RL4

1.4W

电学特性

符号 VIH VIL VOH

VOL

IIN IOS

参数 输入高电平 输入低电平 输出高电平

输出低电平

输入电流 输出短路电流

条件

Min

2.0

GND

IOH = -4mA(data) 2.4 IOH = -8mA(clock) IOL = 4mA(data) IOL = 8mA(clock)

-3-

版本号:1.2

2013.08.12

共9页 第3页

MS90C104

推荐工作条件

电源电压(VCC) CMOS/TTL 输入电压 CMOS/TTL 输出电压 LVDS 接收输入电压 结点温度 温度范围 瞬间耐温(焊接,4 秒) 最大功耗(25℃) MS90C104

-0.3V - 4.0V -0.3V - (VCC+0.3V) -0.3V - (VCC+0.3V) -0.3V - (VCC+0.3V) +150℃ -40℃ - 100℃ +260℃

RX0/7/14/21/28

RX1/8/15/22/29

RX2/9/16/23/30 RX3/10/17/24/31 RX4/11/18/25/32 RX5/12/19/26/33 RX6/13/20/27/34

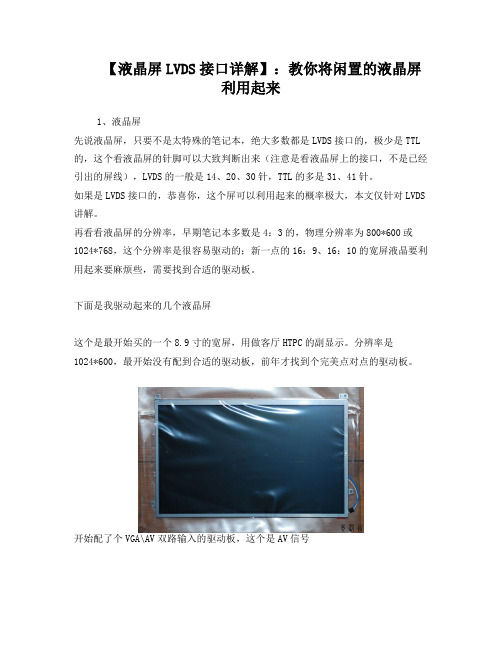

【液晶屏LVDS接口详解】:教你将闲置的液晶屏利用起来

【液晶屏LVDS接口详解】:教你将闲置的液晶屏利用起来1、液晶屏先说液晶屏,只要不是太特殊的笔记本,绝大多数都是LVDS接口的,极少是TTL 的,这个看液晶屏的针脚可以大致判断出来(注意是看液晶屏上的接口,不是已经引出的屏线),LVDS的一般是14、20、30针,TTL的多是31、41针。

如果是LVDS接口的,恭喜你,这个屏可以利用起来的概率极大,本文仅针对LVDS 讲解。

再看看液晶屏的分辨率,早期笔记本多数是4:3的,物理分辨率为800*600或1024*768,这个分辨率是很容易驱动的;新一点的16:9、16:10的宽屏液晶要利用起来要麻烦些,需要找到合适的驱动板。

下面是我驱动起来的几个液晶屏这个是最开始买的一个8.9寸的宽屏,用做客厅HTPC的副显示。

分辨率是1024*600,最开始没有配到合适的驱动板,前年才找到个完美点对点的驱动板。

开始配了个VGA\AV双路输入的驱动板,这个是AV信号这个是富士通触摸笔记本拆出来的12寸屏幕,有两块,一块是800*600,一块是1024*768,也做了个一体电控:一体电控的帖子:刚驱动起来的样子这个是现在做的雕刻机用的屏幕,清华同方的笔记本拆出来的,分辨率是1024*7682013-3-23 22:08 上传下载附件 (85.94 KB)这个是唯一一块没驱动起来的笔记本液晶屏,是SHARP笔记本拆出来的,屏也是SHARP的,800*600,5V的。

2、驱动板要使液晶屏能显示,需要接入LVDS信号,这有两个来源:一是常规的,将VGA信号转为LVDS信号连接液晶屏、二是工控主板上常常集成了LVDS接口,只要将对应针脚连接起来即可。

需要注意的是,不同分辨率的液晶屏,需要在驱动板中写入相应的程序,否则不能正常显示,这个可以在买液晶驱动板的时候给商家说明,现在也有一些通过跳线选择分辨率的驱动板,如果再烧点,就买个液晶烧录器自己玩;而工控主板常常是在BIOS里设置LVDS输出的分辨率。

微塞米电子LVDS高速时钟转换器说明书

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination and biasing for AC coupled inputs•Six precision LVDS outputs •Operating frequency up to 750 MHzPower •Option for 2.5 V or 3.3 V power supply •Current consumption of 97 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply noise rejectionPerformance •Ultra low additive jitter of 135 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40217Precision 1:6 LVDS Fanout Buffer with On-Chip Input TerminationData SheetOrdering InformationZL40217LDG1 32 Pin QFN TraysZL40217LDF132 Pin QFNTape and ReelMatte TinPackage size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197.0 Package Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Figure 3 - Simplified Diagram of input stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 12 - Simplified LVDS Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 13 - LVDS DC Coupled Termination (Internal Receiver Termination). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 14 - LVDS DC Coupled Termination (External Receiver Termination) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 15 - LVDS AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16 - LVDS AC Output Termination for CML Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 17 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Differential Voltage Parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 20 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Change SummaryBelow are the changes from the February 2013 issue to the April 2014 issue:Page Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.7Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. Theseresistor are not required; however there is no impact toperformance if the resistors are included.15Power supply filtering Corrected typo of 0.3 ohm to 0.15 ohm.17Figure 19Clarification of V ID and V ODBelow are the changes from the November 2012 issue to the February 2013 issue:Page Item Change7Figure 4Changed text to indicate the circuit is not recommended forVDD_driver=2.5V.11Figure 12Changed gate values to +/+ on the left and -/- on the right.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0Pin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 628, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.Pin Description3.0 Functional Descriptionhe ZL40217 is an LVDS clock fanout buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40217 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40217 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40217 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is "1" and the Vt pin is not connected, the Vt pin can be instead connected to V DD with a capacitor. A capacitor can also help in Figure 4 between Vt and V DD . This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Clock Input - LVPECL - DC CoupledFigure 4 -Figure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVDS has lower signal swing than LVPECL which results in a low power consumption. A simplified diagram for the LVDS output stage is shown in Figure 12.Figure 12 - Simplified LVDS Output DriverFigure 15 - LVDS AC Coupled TerminationFigure 16 - LVDS AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40217 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40217 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40217 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 17.Figure 17 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40217 is equipped with a low drop out (LDO) linear power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure •. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 ohm resistor is recommendedZL402171891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 18 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power nets in Figure 18 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.4.0 AC and DC Electrical CharacteristicsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 3Soldering temperature T260 °C 4Storage temperature T ST-55125 °C 5Junction temperature T j125 °C 6Voltage on input pin V input V DD V 7Input capacitance each pin C p500fF * Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVDS drivers -I dd_load97mAloaded (all outputs are active)DC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes 1CMOS control logic high-level input V CIH0.7*V DD V2CMOS control logic low-level input V CIL0.3*V DD VI IL1µA V I = V DD or 0 V3CMOS control logic Input leakagecurrentV ICM 1.1 1.6V for 2.5 V 4Differential input common modevoltageV ICM 1.1 2.0V for 3.3 V 5Differential input common modevoltage6Differential input voltage difference V ID0.251V7Differential input resistance V IR80100120ohm* The VOD parameter was measured between 125 and 750 MHzFigure 19 - Differential Voltage ParameterAC Electrical Characteristics* - Inputs and Outputs (see Figure 20) - for 2.5/3.3 V Supply.CharacteristicsSym.Min.Typ.Max.Units Notes1Maximum Operating Frequency 1/t p 750MHz 2Input to output clock propagation delay t pd 012ns 3Output to output skew t out2out 80150ps 4Part to part output skewt part2part 120300ps 5Output clock Duty Cycle degradation t PWH / t PWL-505%6LVDS Output slew rater SL0.55V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWLt pdt PWHOutputFigure 20 - Input To Output Timing8LVDS output differential voltage*V OD 0.250.300.40V 9LVDS Common Mode voltageV CM1.11.251.375VDC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes5.0 Performance Characterization Additive Jitter at 2.5 V*Output Frequency (MHz)JitterMeasurementFilterTypicalRMS (fs)Notes112512 kHz - 20 MHz184 2212.512 kHz - 20 MHz174 3311.0412 kHz - 20 MHz157 442512 kHz - 20 MHz152 550012 kHz - 20 MHz139 6622.0812 kHz - 20 MHz138 775012 kHz - 20 MHz135 *The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter at 3.3 V*Output Frequency (MHz)JitterMeasurementFilterTypicalRMS (fs)Notes112512 kHz - 20 MHz1872212.512 kHz - 20 MHz1763311.0412 kHz - 20 MHz156442512 kHz - 20 MHz153550012 kHz - 20 MHz1406622.0812 kHz - 20 MHz139775012 kHz - 20 MHz137*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*CarrierfrequencyParameter Typical Units Notes125MHz25 mVat 100 kHz33fs RMS750MHz25 mVat 100 kHz33fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Waveform at 155.52 MHz V OD vs FrequencyPower Supply Tone Frequency versus PSRR Power Supply Tone Magnitude versus PSRRPropagation Delay versus TemperatureNote:This is for a single device. For more details, see thecharacterization section.7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C8.0 Mechanical DrawingInformation relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any suchinformation, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.Purchase of Microsemi’s I 2C components conveys a license under the Philips I 2C Patent rights to use these components in an I 2C System, provided that the system conforms to the I 2C Standard Specification as defined by Philips.Microsemi, ZL, and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Microsemi Corporation.TECHNICAL DOCUMENTATION - NOT FOR RESALEFor more information about all Microsemi productsvisit our Web Site at。

NI 6589 1 Gbps, 20 Channel, LVDS数字I O适配器模块商品说明说明书

GETTING STARTED GUIDENI 65891 Gbps, 20 Channel, LVDS Digital I/O Adapter ModuleNote Before you begin, complete the software and hardware installationinstructions in the getting started guide for your FlexRIO FPGA module orController for FlexRIO.The NI 6589 is a FlexRIO adapter module designed to work in conjunction with FlexRIO FPGA modules and Controllers for FlexRIO.The NI 6589 features 20 LVDS channels (16 data and 4 PFI), and sample rates up to 1 Gbit/s on LVDS channelsThis document explains how to install and configure the NI 6589.ContentsElectromagnetic Compatibility Guidelines (1)FlexRIO Documentation (2)Verifying the System Requirements (4)Unpacking (4)Preparing the Environment (4)Installing the NI 6589 (5)Confirming that Measurement & Automation Explorer (MAX) Recognizes the Device (5)Cables (5)Accessories (6)Front Panel and Connector Pinouts (8)Block Diagrams (10)Component-Level Intellectual Property (CLIP) (12)NI 6589 CLIP (13)Clocking (18)Where to Go Next (20)Worldwide Support and Services (20)Electromagnetic Compatibility GuidelinesThis product was tested and complies with the regulatory requirements and limits for electromagnetic compatibility (EMC) stated in the product specifications. These requirements and limits are designed to provide reasonable protection against harmful interference when the product is operated in the intended operational electromagnetic environment.This product is intended for use in industrial locations. However, harmful interference may occur in some installations, when the product is connected to a peripheral device or test object,or if the product is used in residential or commercial areas. To minimize interference with radio and television reception and prevent unacceptable performance degradation, install and use this product in strict accordance with the instructions in the product documentation.Furthermore, any modifications to the product not expressly approved by National Instrumentscould void your authority to operate it under your local regulatory rules.Caution To ensure the specified EMC performance, operate this product only withshielded cables and accessories.Caution To ensure the specified EMC performance, you must attach EMI gaskets(NI part number 746228-01) to both sides of your NI 6589 before using.Caution To ensure the specified EMC performance, you must install PXI EMCFiller Panels (NI part number 778700-01) in all open chassis slots.FlexRIO DocumentationTable 1. FlexRIO Documentation Locations and Descriptions2 | | NI 6589 Getting Started GuideTable 1. FlexRIO Documentation Locations and Descriptions (Continued)NI 6589 Getting Started Guide| © National Instruments| 3Verifying the System RequirementsTo use the FlexRIO Support instrument driver, your system must meet certain requirements. For more information about minimum system requirements, recommended system, and supported application development environments (ADEs), refer to the FlexRIO Support Readme, which is available on the FlexRIO Support software DVD or online at / updates.UnpackingCaution To prevent ESD from damaging the devices, ground yourself using agrounding strap or by holding a grounded object, such as your computer chassis.1.Touch the antistatic package to a metal part of the computer chassis.2.Remove each module from the package and inspect it for loose components or any othersign of damage.Caution Never touch the exposed pins of connectors.Note Do not install a device if it appears damaged in any way.3.Unpack any other items and documentation from the kit.Store the devices in the antistatic package when they are not in use.Preparing the EnvironmentEnsure that the environment you are using the NI 6589 in meets the following specifications.0 °C to 55 °COperating temperature (IEC 60068-2-1,IEC 60068-2-2)Operating humidity (IEC 60068-2-56)10% to 90% RH, noncondensingPollution Degree2Maximum altitude2,000 m at 25 °C ambient temperature Indoor use only.Note Refer to the NI 6589 Specifications at /manuals for completespecifications.Caution Clean the hardware with a soft, nonmetallic brush. Make sure that thehardware is completely dry and free from contaminants before returning it toservice.4| | NI 6589 Getting Started GuideInstalling the NI 6589Refer to the getting started guide for your FlexRIO FPGA module or Controller for FlexRIO for instructions about how to install your FlexRIO system, including the NI 6589. Confirming that Measurement & Automation Explorer (MAX) Recognizes the DeviceUse Measurement & Automation Explorer (MAX) to configure your NI hardware. MAX informs other programs about which devices reside in the system and how they are configured. MAX is automatically installed with FlexRIO Support.unch MAX by navigating to Start»All Programs»National Instruments»NI MAX orby clicking the NI MAX desktop icon.2.In the Configuration pane, double-click Devices and Interfaces to see the list of installeddevices. Installed devices appear under the name of their associated chassis.3.(PXI and PXI Express devices only) Expand your Chassis tree item. MAX lists alldevices installed in the chassis. Your default device names may vary.Note If you do not see your hardware listed, press <F5> to refresh the list ofinstalled devices. If the device is still not listed, power off the system, ensurethe device is correctly installed, and restart.4.(Controllers for FlexRIO only) Your device appears under the Remote Devices section.CablesCaution You must operate the NI 6589 with shielded cables and shieldedaccessories to ensure compliance with the EMC requirements defined in the NI 6589Specifications. Do not use unshielded cables or accessories unless they are installedin a shielded enclosure with properly designed and shielded input/output ports andare connected to the NI 6589 using a shielded cable. If unshielded cables oraccessories are not properly installed and shielded, the EMC specifications for theNI 6589 are no longer guaranteed.Use a shielded 50 Ω coaxial cable with an SMA plug end to connect to the PFI 0 and CLOCK IN connectors on the NI 6589 front panel. Use the NI SHB12X-B12X shielded cable (NI part number 192344-01) or the NI SHB12X-H3X24 differential flying-lead cable (NI part number 196236-1R5) to connect to the DDC connector. You can also connect theNI SMA-2164 accessory to the NI 6589 through the SHB12X-B12X shielded cable for testing and debugging.Note If you design a custom cabling solution with the DDC connector (779157-01)and SHB12X-B12X shielded cable (192344-01), the NI 6589 pinout is reversed atNI 6589 Getting Started Guide| © National Instruments| 5the end connector. For example, the signal shown on pin 1 maps to pin 73 at the end connector.The following NI cables and accessories are not properly shielded for EMC-compliant use with the NI 6589:•NI SMA-2164 accessory •NI SHB12X-H3X24 differential flying-lead cableNote Whether you use NI cables and accessories or design your own, terminatecables properly to avoid improper measurements caused by signal reflections,overshoot, and undershoot.AccessoriesThe NI SMA-2164 test fixture is a breakout box for differential signals. This fixture provides an easy way to connect to other devices for testing and debugging.The following figure shows how to connect the differential DDC connector to theNI SMA-2164, using the NI SHB12X-B12X cable. For more information about using the NI SMA-2164, refer to the NI SMA-2164/2165 Test Fixture User Guide .Figure 1. Connecting the NI SMA-2164 Accessory1.PXI/PXIe Chassis with an NI 6589R2.NI SHB12-B12X Cable3.NI SMA-2164A flying lead cable, the NI SHB12X-H3X24, is also available for differential signals. This cable offers connectivity similar to that found on a typical logic analyzer, so you can use it in logic analyzer-type applications. This cable is shown in the following figure.6 | | NI 6589 Getting Started GuideFigure 2. NI SHB12X-H3X24 Flying Lead Cable1.Leads (1 × 3 Header Receptacle)2.DDC Connector3.Removeable SleevingCustom AccessoriesIf you are creating a custom accessory to use with a DUT with a VHDCI DDC connector, you can purchase the mating connector for the VHDCI cable from NI. For more information about creating these custom accessories, refer to the Interfacing to the NI Digital Waveform Generator/Analyzer using the VHDCI Connector application note.Visit /info and enter the Info Code rdinwa to download this note.If you are designing a custom accessory to use with a device that uses an InfiniBand connector, you can also purchase this connector from NI.Note If you design a custom cabling solution with the DDC connector (779157-01)and SHB12X-B12X shielded cable (192344-01), the NI 6589 pinout is reversed atthe end connector. For example, the signal shown on pin 1 maps to pin 73 at the endconnector.For more information about connecting I/O signals on your device, refer to the NI 6589 Specifications.NI 6589 Getting Started Guide| © National Instruments| 7Front Panel and Connector PinoutsThe NI 6589 provides one PFI signal and one clock signal through the two SMA connectors on the device front panel. Additionally, the NI 6589 provides sixteen LVDS signals, four LVDS PFI signals, three single-ended PFI signals, and an LVDS clock out signal on the Digital Data & Control (DDC) connector. The following figure shows the front panel connector and signal descriptions for the NI 6589.Figure 3. NI 6589 Front Panel and Connector PinoutCaution To avoid permanent damage to the NI 6589, disconnect all signalsconnected to the NI 6589 before powering down the module, and connect signalsonly after the adapter module has been powered on by the FlexRIO FPGA module orController for FlexRIO.8| | NI 6589 Getting Started GuideCaution Connections that exceed any of the maximum ratings of any connector onthe NI 6589 can damage the device and the chassis. NI is not liable for any damageresulting from such connections.Note If you design a custom cabling solution with the Infiniband connector(779157-01) and the SHB12X-B12X LVDS shielded cable (192344-01), the NI 6589pinout is reversed at the end connector. For example, the signal shown on pin 1 mapsto pin 73 in the pinout at the end connector.The following table contains SMA pin location information and signal information for theNI 6589. The signal names listed in this table refer to the signals shown in the front panel pinout.Table 2. SMA Connector Names and DescriptionsThe following table contains DDC pin location information for the NI 6589. The signal names listed in this table refer to the signals shown in the front panel pinout.NI 6589 Getting Started Guide| © National Instruments| 9Table 3. NI 6589 DDC Connector Names and Descriptions (Continued)For more detailed information about the NI 6589 front panel connectors, refer to the NI 6589Specifications.Block DiagramsThe following figures show the data flow through the NI 6589. Single-ended data lines use standard clock levels to interpret data as either a binary zero or a one in high-speed digital data transfers. Differential data lines provide a low-noise, low-power, low-amplitude differential method for high-speed digital data transfer.Figure 4. Clock Input SignalCLOCK INNI FlexRIO FPGA Module(UserGclkLvttl)10 | | NI 6589 Getting Started GuideFigure 5. LVDS Data and PFI LinesData fromNI FlexRIO FPGA Module(GPIO Output)NI FlexRIO FPGA Module(GPIO Input)DIO <0..15>DIO <0..15>+ and PFI <1..4>+Direction Control from NI FlexRIO FPGA Module(GPIO Direction)and PFI <1..4>Figure 6. Single-Ended PFI LinesData fromNI FlexRIO FPGA Module(GPIO Output)Output Enable from NI FlexRIO FPGA Module(GPIO Direction)Data toNI FlexRIO FPGA Module(GPIO Input)SE_PFI <1..3>and PFI 0Figure 7. Clock Output SignalsClock fromNI FlexRIO FPGA Module(GPIO Output)Output Enable from NI FlexRIO FPGA Module(GPIO Direction)DDC CLK OUT+DDC CLK OUTFigure 8. Crosspoint SwitchSTROBEStrobe Bypass Controlfrom NI FlexRIO FPGA Module(GPIO_8_n)Generation Bank I/O Clockto NI FlexRIO FPGA ModuleGPIO_26_CCGPIO_26_n_CCPFI Bank I/O Clockto NI FlexRIO FPGA ModuleGPIO_38_CCGPIO_38_n_CCGlobal Clockto NI FlexRIO FPGA ModuleUserGclkLvdsUserGclkLvds_nGPIO_56_CCGPIO_56_n_CCCrosspointSwitchRelated InformationComponent-Level Intellectual Property (CLIP) on page 12The LabVIEW FPGA Module includes component-level intellectual property (CLIP) for HDL IP integration. FlexRIO devices support two types of CLIP: user-defined andsocketed.Component-Level Intellectual Property (CLIP)The LabVIEW FPGA Module includes component-level intellectual property (CLIP) for HDL IP integration. FlexRIO devices support two types of CLIP: user-defined and socketed.•User-defined CLIP allows you to insert HDL IP into an FPGA target, enabling VHDL code to communicate directly with an FPGA VI.•Socketed CLIP provides the same IP integration of the user-defined CLIP, but it also allows the CLIP to communicate directly with circuitry external to the FPGA. Adaptermodule socketed CLIP allows your IP to communicate directly with both the FPGA VI and the external adapter module connector interface.The FlexRIO adapter module ships with socketed CLIP items that add module I/O to the LabVIEW project.Related InformationBlock Diagrams on page 10NI 6589 CLIPRefer to the following table for the available NI 6589 CLIP items, and each CLIP item's function and available signals.Note All NI 6589 CLIP items allow individual clock output inversion.Table 4. NI 6589 CLIP ItemsTable 4. NI 6589 CLIP Items (Continued)The following table lists the NI 6589 SMA connector signals and corresponding FlexRIO FPGA module signals necessary for designing custom component-level IP (CLIP).The following table lists the NI 6589 DDC connector signals and corresponding FlexRIO FPGA module signals necessary for designing custom component-level IP (CLIP). The _CC suffix on signals identifies channels that can receive a regional clock.Table 6. NI 6589 DDC Signals and FlexRIO FPGA Module SignalsRefer to the FlexRIO Help for more information about FlexRIO CLIP items, configuring the NI 6589 with a socketed CLIP, and a list of available socketed CLIP signals. ClockingThe clocks on the NI 6589 control the sample rate and other timing functions on your FlexRIO system. The following figure shows the NI 6589 clock sources routed through the crosspoint switch. The Generation Bank I/O clock, PFI Bank I/O clock, and Global clock are all sourced by the crosspoint switch. The Acquisition Bank I/O clock can be sourced from the crosspoint switch or accessed directly through the Strobe Bypass path.Note Only the Acq_IO_Clock_Source signal can use the STROBE Bypass path. IfAcq_IO_Clock_Source is set to Strobe Bypass, then Gen_IO_Clock_Source,PFI_IO_Clock_Source, and IO_Module_Clock_1_Source cannot be set to StrobeFrom Crosspoint Switch.Figure 9. Crosspoint SwitchSTROBEStrobe Bypass Controlfrom NI FlexRIO FPGA Module(GPIO_8_n)Generation Bank I/O Clockto NI FlexRIO FPGA ModuleGPIO_26_CCGPIO_26_n_CCPFI Bank I/O Clockto NI FlexRIO FPGA ModuleGPIO_38_CCGPIO_38_n_CCGlobal Clockto NI FlexRIO FPGA ModuleUserGclkLvdsUserGclkLvds_nGPIO_56_CCGPIO_56_n_CCCrosspointSwitchIn software, each clock output terminal is accessed with a U8 data type. The following table shows the values of the crosspoint switch clock options.Table 7. Clock ValuesWhere to Go NextRefer to the following figure for information about other product tasks and associated resources for those tasks.Worldwide Support and ServicesThe NI website is your complete resource for technical support. At /support, you have access to everything from troubleshooting and application development self-help resources to email and phone assistance from NI Application Engineers.Visit /services for NI Factory Installation Services, repairs, extended warranty, and other services.Visit /register to register your NI product. Product registration facilitates technical support and ensures that you receive important information updates from NI.A Declaration of Conformity (DoC) is our claim of compliance with the Council of the European Communities using the manufacturer’s declaration of conformity. This system affords the user protection for electromagnetic compatibility (EMC) and product safety. Youcan obtain the DoC for your product by visiting /certification. If your product supports calibration, you can obtain the calibration certificate for your product at /calibration. NI corporate headquarters is located at 11500 North Mopac Expressway, Austin, Texas, 78759-3504. NI also has offices located around the world. For telephone support in the United States, create your service request at /support or dial 1 866 ASK MYNI (275 6964). For telephone support outside the United States, visit the Worldwide Offices section of / niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.NI 6589 Getting Started Guide| © National Instruments| 21Refer to the NI Trademarks and Logo Guidelines at /trademarks for information on NI trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering NI products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the National Instruments Patent Notice at /patents. Y ou can find information about end-user license agreements (EULAs) and third-party legal notices in the readme file for your NI product. Refer to the Export Compliance Information at /legal/export-compliance for the NI global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data. NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMA TION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS. U.S. Government Customers: The data contained in this manual was developed at private expense and is subject to the applicable limited rights and restricted data rights as set forth in FAR 52.227-14, DFAR 252.227-7014, and DFAR 252.227-7015.© 2016 National Instruments. All rights reserved.374729B-01Apr16。

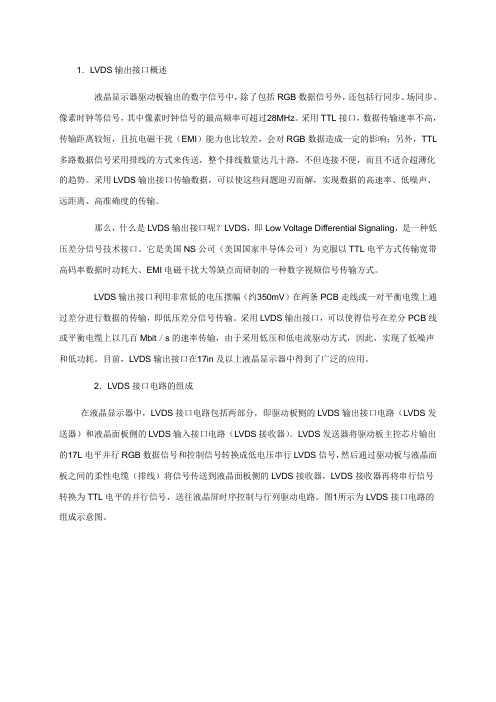

LVDS接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

vga转hdmi转换器连接使用方法解析

vga转hdmi转换器连接使用方法解析

vga转hdmi转换器连接使用方法解析

HDMI

HDMI是(High DefiniTIon MulTImedia Interface)的缩写,意思是高清晰度多媒体接口,是一种数字化视频/音频接口技术,适合影像传输的专用型数字化接口,可同时传送音频和影像信号,最高数据传输速度为48Gbps (2.1版)。

同时无需在信号传送前进行数/模或者模/数转换。

HDMI可搭配宽带数字内容保护(HDCP),以防止具有着作权的影音内容遭到未经授权的复制。

HDMI所具备的额外空间可应用在日后升级的音视频格式中。

而因为一个1080p的视频和一个8声道的音频信号需求少于

0.5GB/s,因此HDMI还有很大余量。

这允许它可以用一个电缆分别连接DVD播放器,接收器和PRR。

VGA。

VGA-DVI转换器用户手册

用户手册

VGA转DVI转换器

在许多多媒体应用系统中,往往需要把一个VGA格式的信号转换

为DVI格式的信号,同时又需要在本地显示该信号。

VGA转DVI转换

器专为解决这类工程问题而设计的,VGA转DVI转换器能够把模拟显

示器显示的RGBHV(红绿蓝行场)格式的信号转换为高分辨率和高刷

新率的DVI信号。

图一:转换器后背板图

技术性能及指标

输入接口: ·1路HD15(VGA)

输出接口: ·DVI-I型接口

监视口:· 1路HD15(VGA)

RGB通道: ·带宽:350MHz(-3dB) ·输入阻抗:75Ω ·输出阻抗:75Ω

同步通道:·输入阻抗:75Ω ·输入电平:5V p-p

·输出阻抗:75Ω ·输出电平:5V p-p 支持分辨率: ·最高到1600*1200*60hz

电源:·5V / DC

外形尺寸 :·185×125×50mm(D×W×H)

重量:·0.3Kg。

星科VGA2HDPRO2 VGA到HDMI视频转换器及放大器说明书

For the most up-to-date information, please visit: DE: Bedienungsanleitung - FR: Guide de l'utilisateur - ES: Guía del usuario - IT: Guida per l'uso - NL: Gebruiksaanwijzing - PT: Guia do usuário - VGA2HDPRO2VGA to HDMI® video converter with scaler *actual product may vary from photosFCC Compliance StatementThis equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:• Reorient or relocate the receiving antenna.• Increase the separation between the equipment and receiver.• Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.• Consult the dealer or an experienced radio/TV technician for helpThis device complies with part 15 of the FCC Rules. Operation is subject to the followingtwo conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation. Changes or modifications not expressly approved by could void the user’s authority to operate the equipment.Industry Canada StatementThis Class B digital apparatus complies with Canadian ICES-003.Cet appareil numérique de la classe [B] est conforme à la norme NMB-003 du Canada.CAN ICES-3 (B)/NMB-3(B)Use of Trademarks, Registered Trademarks, and other Protected Names and Symbols This manual may make reference to trademarks, registered trademarks, and other protected names and/or symbols of third-party companies not related in any way to . Where they occur these references are for illustrative purposes only and do not represent an endorsement of a product or service by , or an endorsement of the product(s) to which this manual applies by the third-party company in question. Regardless of any direct acknowledgement elsewhere in the body of this document, hereby acknowledges that all trademarks, registered trademarks, service marks, and other protected names and/or symbols contained in this manual and related documents are the property of their respective holders.Table of ContentsProduct Diagram (1)Front View (1)Rear View (1)Introduction (2)Packaging Contents (2)System Requirements (2)Hardware Installation (2)Operation (4)Technical Support (5)Warranty Information (5)Product DiagramFront View Rear View1. VGA input2. 3.5mm analog audio input3. SPDIF digital optical audio input4. USB service port (only required for firmware updates)5. Power adapter port1. HDMI output2. SPDIF digital optical audio output3. 3.5mm analog audio output4. On screen display menu button5.On screen display operation buttonsIntroductionPackaging Contents• 1x VGA to HDMI converter & scaler• 1x 4ft (1.2m) VGA cable• 1x 6ft (1.8m) 3.5mm to RCA cable• 1x Universal power adapter (US/UK/EU/AUS)• 1x Quick install guideSystem Requirements• VGA source device (i.e. computer system)• HDMI display device (i.e. monitor or projector) with cabling Hardware InstallationNote: Please ensure all devices are powered off before you begin installation.1. Connect the VGA output on your VGA source device to the VGA input on the VGA to HDMI converter using the included VGA cable.2. (optional) If you would like to include audio on your HDMI output signal, connect an audio cable from your source device to either the3.5mm audio input (analog) or the SPDIF input (digital), depending on your available or desired audio output on your source device.Note: An RCA to 3.5mm audio cable is included for RCA audio sources. If your audio source is anything different (i.e. 3.5mm or SPDIF) additional cabling is required.3. Connect the HDMI output on the VGA to HDMI converter to the HDMI input on your HDMI display device using an HDMI cable (not included).4. Connect the VGA to HDMI converter to an available electrical outlet using the included power adapter.OperationOn screen displayThe HDMI to VGA converter and scaler features an on screen display (OSD) menu that enables you to adjust various picture settings to customize your output based on your specific application. To access the OSD menu, press the on screen display menu button, on the back of the VGA to HDMI converter.To navigate the OSD menu, use the menu operation buttons (+ up) and (- down) on the back of the VGA to HDMI converter, and the menu button to select each option on the menu.For complete OSD operation instructions please download the full product menu at .Factory default settingsFollow the below steps to restore the VGA to HDMI converter to the default settings.1. Ensure the VGA to HDMI converter is powered on.2. Hold down both the + and – operation buttons at the same time for three seconds.3. The VGA to HDMI converter has now been restored to default settings. Download the complete instruction manual at /supportTechnical Support’s lifetime technical support is an integral part of our commitment to provide industry-leading solutions. If you ever need help with your product, visit /support and access our comprehensive selection of online tools, documentation, and downloads.For the latest drivers/software, please visit /downloads Warranty InformationThis product is backed by a two year warranty.In addition, warrants its products against defects in materials and workmanship for the periods noted, following the initial date of purchase. During this period, the products may be returned for repair, or replacement with equivalent products at our discretion. The warranty covers parts and labor costs only. does not warrant its products from defects or damages arising from misuse, abuse, alteration, or normal wear and tear.Limitation of LiabilityIn no event shall the liability of Ltd. and USA LLP (or their officers, directors, employees or agents) for any damages (whether direct or indirect, special, punitive, incidental, consequential, or otherwise), loss of profits, loss of business, or any pecuniary loss, arising out of or related to the use of the product exceed the actual price paid for the product. Some states do not allow the exclusion or limitation of incidental or consequential damages. If such laws apply, the limitations or exclusions contained in this statement may not apply to you.Hard-to-find made easy. At , that isn’t a slogan. It’s a promise. is your one-stop source for every connectivity part you need. From the latest technology to legacy products — and all the parts that bridge the old and new — we can help you find the parts that connect your solutions.We make it easy to locate the parts, and we quickly deliver them wherever they need to go. Just talk to one of our tech advisors or visit our website. You’ll be connected to the products you need in no time.Visit for complete information on all products and to access exclusive resources and time-saving tools. is an ISO 9001 Registered manufacturer of connectivity and technology parts. was founded in 1985 and has operations in the United States,。

信号转换器——开机显示窗数值说明

信号转换器—开机显示说明

矿用信号转换器作为连接各种传感器、执行器和控制系统的关键部件,它实现了无线信号与数字信号总线信号的相互转换,并通过电缆线传输到分站级设备,不仅提高了生产效率,还促进了矿业产业的技术进步和产业升级。

它在矿井应用的意义重大,但是在使用过程中,很多人对它开机时显示的数值有疑惑?别着急往下看..........

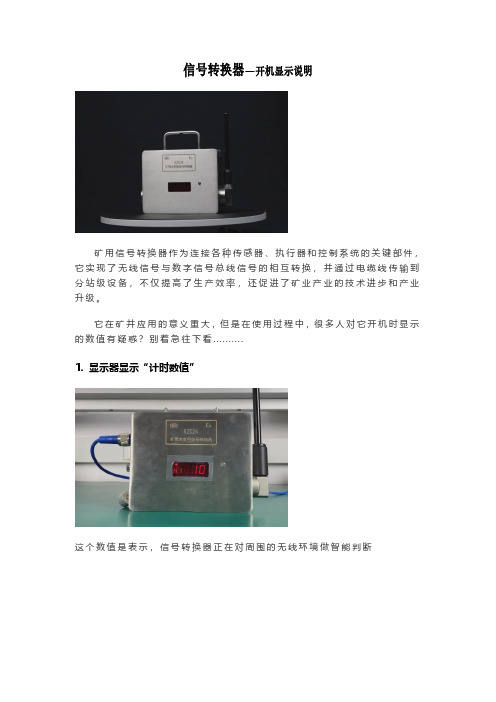

1.显示器显示“计时数值”

这个数值是表示,信号转换器正在对周围的无线环境做智能判断

2.显示器显示“P OX”

这个数值是表示,信号转换器的通讯协议类型3.显示器显示“b0.54X”

这个数值是软件的版本号

4.显示器显示“C01”

这是转换器的无线信道号,有01~08八个数值,需要根据现场实际情况来进行调试

5.显示器显示“1-32”传感器的值

当转换器为掘进模式或者回采主机模式时,显示窗轮换显示“1-32”号无线传感器的值

6.回采从机模式

当转换器为回采从机模式时,会短暂显示接受到无线传感器的值,未接收时显示“---”

7.左上角的两个小灯含义

左边指示灯亮,代表与上级正常通讯

右边指示灯亮,代表无线发射。

ABLE Design GmbH LVDS接收器简明用户手册说明书

ABLE Design GmbHTrimburgstr. 2D-81249 MünchenTel.: +49 (0)89 897032 0Tel.: +49 (0)89 897032 32Short Form ManualEL-LVDS ReceiverRev. 1.0Release: 0Revision: 1.0Date: 25.07.07Name: Jörg BühseName Date Signature Composed:Jörg Bühse27.07.2007Approved:Released:1. HardwareConnector:X1: EL640.480 connectorX2: for internal useX3: EL320.240 connectorX4: Power supplyX5: LVDS inputJ1: Jumper for configurationTest Pin:TP1: Link with TP2 = test picture for EL320.240.36 TP2: +5V for EL320.240 test pictureTP3: internal useTP4: Link with TP5 = internal generated test picture TP5: GNDTP6: Link with TP7 = reset Xilinx FPGATP7: GNDTP8: internal useTP9: Link with TP10 = reprogramming XilinxTP10: GNDFuseF1: 12V protection 4A (Littelfuse 0452004.MRL)F2: 5V protection 4A (Littelfuse 0452004.MRL)Configuration (Jumper)open close Grayscale 4 steps 5 steps (default)Display Type320x240640x480 (default)LVDS Select Jeda standard Vesa standard (default)Colour Scaling:Red R-scal0 open; R-scal1 open (default)No colour scaling for redR-scal0 close; R-scal1 open Colour value = 1/2R-scal0 open; R-scal1 close Colour value = 1/4R-scal0 close; R-scal1 close Colour value = 1/8Green G-scal0 open; G-scal1 open (default)No colour scaling for green G-scal0 close; G-scal1 open Colour value = 1/2G-scal0 open; G-scal1 close Colour value = 1/4G-scal0 close; G-scal1 close Colour value = 1/8Blue B-scal0 open; B-scal1 open (default)No colour scaling for blueB-scal0 close; B-scal1 open Colour value = 1/2B-scal0 open; B-scal1 close Colour value = 1/4B-scal0 close; B-scal1 close Colour value = 1/82. Pin-OutX1: E640.480 DisplayconnectorSamtec EHT-110-01-S-DVideo Data UD112Video Data UD0Video Data UD334Video Data UD2Video Data LD156Video Data LD0Video DataLD378Video Data LD2Data input Clock CP2910GroundInput data latch CP11112GroundScan Start-up signal1314GroundGround1516Ground+5V1718+5V+12V1920+12VX3: EL320.240.36 DisplayyonnectorSamtec EHT-110-01-S-D+12V12+12VSelftest input34Reserved+5V56GroundVertical Sync78GroundHorizontal Sync910GroundVideo Clock1112GroundVideo data VID01314GroundVideo data VID11516GroundVideo data VID21718GroundVideo data VID31920GroundX4: Power connectorHirose DF1-4P-2,5DSA+5V1GND2GND3+12V4X5: LVDS inputSamtec EHT-110-01-S-DLVDS Data 0-12LVDS Data 0+GND34LVDS Data 1-LVDS Data 1+56GNDLVDS Data 2-78LVDS Data 2+GND910LVDS Clk-LVDS Clk+1112GNDLVDS Data 3-1314LVDS Data 3+GND1516GND+5V1718+5V+12V1920+12VInput timing640x480 timing with 60Hz like the NEC nl6448bc33 in Fixed mode.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Vcc

30

Vcc

P4接口线序说明:

1

Vcc

2

Vcc

3

Vcc

4

Vcc

5

GND

6

GND

7

GND

8

GND

9

NC

10

NC

11

GND

12

LVDS0-

13

LVDS0+

14

GND

15

LVDS1-

16

LVDS1+

17

GND

18

LVDS2-

19

LVDS2+

20

GND

21

LVDSC-

22

LVDSC+

23

GND

24

LVDS3-

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

本产品 LVDS线序转换板 输入接口所兼容液晶屏接口对照表:

LVDS接口(P1) LVDS接口(P2) LVDS接口(P3) LVDS接口(P4)

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

25

GND

26

Vcc

27

Vcc

28

Vcc

29

Vcc

30

Vcc

25

LVDS3+

26

GND

27

NC

换器 对接,以匹配各种不同液晶面板所需的 LVDS信号的线序。(正反面图)

2、 LVDS线序转换板 各接口线序说明:

P1接口线序说明

1

NC

1

2

NC

2

3

NC

3

4

GND

4

5

LVDS0-

5

6

LVDS0+

6

7

GND

7

8

LVDS1-

8

9

LVDS1+

9

10

GND

10

11

LVDS2-

11

12

LVDS2+

12

13

GND

LZ315T3LA24

V260B2-L03

M190MWW3

V320B1-L04

T260XW02-V5

V315B1-L01

M236MWF1

V315B3-L01

V315B3-L04 SVA190WX01TB

LC320W01-SL05

T260XW02V2

T370XW01V.1

T315XW01V5

LC420W02-SLA1

五) 由于本产品关键器件都是高集成度芯片,使用时请做好以下准备: 1、保证电源处于断电状态; 2、全过程,请采用防静电操作。

四 针对高清主板的维修方法

(一)针对双组 LVDS 输出主板的维修办法 对于双组 LVDS 输出的主板,在接驳维修时,只采集一组 LVDS 信号进行转换。

(二)针对带倍频板的主板维修办法 1、维修时,直接使主板与 LVDS-VGA信号转换器 相连接,不再使用倍频电路; 2、采集主板 LVDS 信号时,可使用单组 LVDS 输出插座(如下图,规格 2.0的插

V470H1-L02

LC370WX1-SL02

T260XW02V.5

LC260WX2-SLB3

T315XW02V1

LC420W02-SLA2

V260B1-L01

LC420W02-SLA1(G34F)

SVA201VG01TB

LC320WX3-SLA1

T230XW01V0

T420XW01V5

LC370WXN-SAB1

创维 8M86 机芯主板连接示意图

五 附注

因创维产品中的 LVDS 信号为满足国家质量标准而做出了部分改动。所以我们在 维修的过程中有部分机芯需要进行适当的程序更改,说明如下:

1、 若接驳 LVDS-VGA 信号转换器 时,出现 像暗、图像抖动、字符拖影 等 现象,请进入总线,若机芯程序中 SSC 与 LVDS ENABLE 选项为 ON 或者 1 的状态,请将其设置为 OFF 或者 0 的状态,即可正常;

1

Vcc

2

Vcc

3

Vcc

4

Vcc

5

GND

6

GND

7

GND

8

GND

9

10

11

LVDS3+

12

LVDS3-

3

LVDSC+

14

LVDSC-

15

LVDS2+

16

LVDS2-

17

LVDS1+

18

LVDS1-

19

LVDS0+

20

LVDS0-

21

GND

22

GND

23

24

25

26

27

GND

28

GND

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

2.2VGA接口(VGA1)线序说明:

5 GND 10 GND 15 GND

4 NC 9 NC 14 VSYNC

3 BLUE 8 GND 13 HSYNC

2 GREEN 7 GND 12 GND

1 RED 6 GND 11 NC

(二) LVDS线序转换板 1、下图为 LVDS线序转换板 实物图, LVDS线序转换板 与 LVDS-VGA信号转

(二) 将 LVDS线序转换板 与 LVDS-VGA信号转换器 连接,如图:

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

(三) LVDS-VGA信号转换器 输出连接 将 LVDS-VGA信号转换器 ,通过 VGA信号线,接驳至合适的 VGA显示器或支持

12

LVDS1+

13

LVDS2-

14

LVDS2+

15

LVDSC-

16

LVDSC+

17

LVDS3-

18

LVDS3+

19

GND

20

NC

21

NC

22

NC

23

GND

24

GND

14

GND

15

NC

16

NC

17

GND

18

NC

19

NC

20

NC

21

NC

22

NC

23

NC

24

GND

25

GND

26

NC

27

GND

28

Vcc

29

(三)主要参数 l 尺寸:25mm 60mm 100mm l 输入接口:24bitLVDS差分信号,28针 2mm间距双排针 l 输出接口:标准的 DB15VGA接口 l 电源支持:5、12V(5V主板、12V主板) l 显示支持:最高分辨率 1920 1080 l 工作环境:温度-10℃~50℃,湿度 5%~85%

28

NC

29

NC

30

NC

三 安装步骤

(一) 液晶主板与 LVDS线序转换板 的对接 将液晶产品主板输出的 LVDS转换电缆与 LVDS线序转换板 上对应液晶面板接口

连接(屏幕种类及对应接口说明详见 LVDS线序转换板 接口定义)(注意:由于 LVDS 扁平插座易损,连接时请用手按紧 LVDS扁平插座,先将驱动线和线序转换板连接好后 再把线序转换板与 LVDS转换器连接),如图:

VGA信号的电视机。

(四) 接入匹配的主板电源,即可开展主板故障的排查与维修了(效果图如下)。

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

14

LVDSC-

15

LVDSC+

16

GND

17

LVDS3-

18

LVDS3+

19

GND

20

NC

21

NC

22

NC

23

GND

24

GND

25

GND

26

Vcc

2cc

30

Vcc

P3接口线序说明:

1

NC

2

NC

3

NC

4

NC

5

NC

6

NC

7

NC

8

GND

9

LVDS0-

10

LVDS0+

11

LVDS1-

座双排 28针),便于接驳;

单组 LVDS输出插座

Create PDF with GO2PDF for free, if you wish to remove this line, click here to buy Virtual PDF Printer

3、取与单组 LVDS 输出插座相匹配的 LVDS 信号传输线,与主板进行连接(如下 图),以采集单组 LVDS 信号源。(一般要采集的一组 LVDS 信号都以主板输出时离屏 供电近的一组为首选)。