PCB-Layout Checklist

数字板PCB设计检查check_list

接口电路一般使用专用芯片,是否注意采用光器件或变压器进行隔离、传输匹配、过压过流保护、防雷击等措施。

芯片如有PGND引脚或要求接PGND时,在单板上是否设计了相应的PGND地,并在电源接口处与电源地相连,以防雷击并泄放一次保安单元剩余的电荷。

是否考虑到单板与RF模块接口的输入/输出信号的电平隔离及匹配。

高速并行总线接口是否统一采用推荐优选接口芯片单板上的调试串口是否采用RS232终端并联匹配电阻是否尽可能靠近接收电路,串联匹配电阻是否靠近始端。

输出信号应是否考虑有足够的驱动能力在设计中,正确使用数字地(DGND),模拟地(AGND),电源地(BGND),保护地(PGND)。

单板上电后能否进行自检,并进行一些必要的自环收发、内存读写、芯片测试等功能性的测试,如有异常,指示灯是否指示自检失败,否则开始正常运行。

单板自检故障时,能否将故障原因送主机及调试口在单板上是否有必要的测试点单独引出,以TP1、TP2···等来命名测试点是否包括电源、时钟等。

具有Boundary-Scan的器件,其测试访问端的四个管脚TDI、TDO、TMS 、TCK是否留有测试孔。

CPU的晶振应尽量排布在晶振输入引脚附近。

无源晶振要加几十皮法的电容;有源晶振可直接将信号引至CPU的晶振输入脚。

如果CPU内部自带Watchdog电路,则采用内部的Watchdog,对于系统来说更为安全可靠。

对于CPU的中断输入脚,无论使用与否,应接有上拉或下拉电阻,尽量不要悬空。

对于不用的输入脚,也应尽量照此处理。

专用芯片的应用是否参考了厂家资料给出的推荐电路。

在总线达到产生传输线效应的长度后,是否考虑了匹配关键信号是否引到接插件或预留了测试点PCB、单板软件的版本信息是否都在各自范围内设计,并可上报单板的关键芯片是否支持自测试功能单板、扣板的机械尺寸与信号位置设计是否统一考虑;单板上电后的芯片的初始状态是否固定单板上接插件的间距和位置是否参考同类成熟单板单板所有器件选型是否通过品质和商务清单评审。

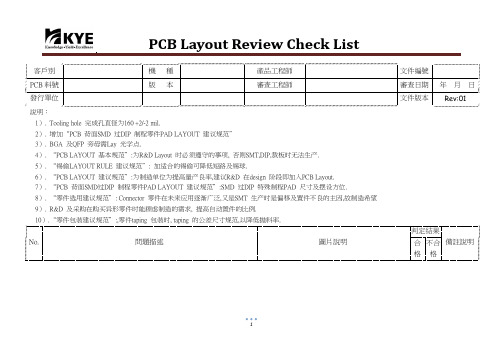

PCBLayoutReviewCheckList-V03

[鍵入文件標題]客戶別機種產品工程師文件編號PCB料號版本審查工程師審查日期年月日發行單位文件版本Rev:01 說明:1).Tooling hole 完成孔直径为160 +2/-2 mil.2).增加“PCB 背面SMD 过DIP 制程零件PAD LAYOUT 建议规范”3).BGA 及QFP 旁毋需Lay 光学点.4).“PCB LAYOUT 基本规范”:为R&D Layout 时必须遵守的事项, 否则SMT,DIP,裁板时无法生产.5).“锡偷LAYOUT RULE 建议规范”: 加适合的锡偷可降低短路及锡球.6).“PCB LAYOUT 建议规范”:为制造单位为提高量产良率,建议R&D 在design 阶段即加入PCB Layout.7).“PCB 背面SMD过DIP 制程零件PAD LAYOUT 建议规范”:SMD 过DIP 特殊制程PAD 尺寸及摆设方位.8).“零件选用建议规范”: Connector 零件在未来应用逐渐广泛,又是SMT 生产时是偏移及置件不良的主因,故制造希望9).R&D 及采购在购买异形零件时能顾虑制造的需求, 提高自动置件的比例.10).“零件包装建议规范”:,零件taping 包装时, taping 的公差尺寸规范,以降低抛料率.No. 問題描述圖片說明判定結果備註說明合格不合格[鍵入文件標題]01一般PCB 过板方向定义:➢PCB 在SMT 生产方向为短边过回焊炉(Reflow), PCB 长边为SMT 输送带夹持边.➢PCB 在DIP 生产方向为I/O Port 朝前过波焊炉(Wave Solder), PCB 与I/O 垂直的两边为DIP 输送带夹持边.02金手指过板方向定义:➢SMT: 金手指边与SMT 输送带夹持边垂直.➢DIP: 金手指边与DIP 输送带夹持边一致.03➢SMD 零件文字框外缘距SMT 输送带夹持边L1 需≧150 mil.➢SMD 及DIP 零件(I/O 零件除外)文字框外缘距板边L2 需≧100 mil.[鍵入文件標題]04➢PCB 板边至PCB 板边的螺丝孔(精灵孔)PAD 的中心, 直径3mm的范围内不得有SMD 或DIP 零件(如右图虚线所示)05➢V-Cut 或邮票孔须距正上方平行板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧80 mil.06➢V-Cut 或邮票孔须距正上方垂直板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧200 mil.[鍵入文件標題]07➢V-Cut 或邮票孔须距左右方平行板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧140 mil.08➢V-Cut 或邮票孔须距左右方垂直板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧180 mil.09 ➢邮票孔与周围突出板边零件的文字框须距离L≧40 mil.10 ➢本体厚度跨越PCB 的零件,其跨越部份的V-CUT 必须挖空.[鍵入文件標題]11➢如有邮票孔或V-cut 时, trace 距邮票孔或V-cut 的距离L1 边须≧50 mil;其余TRACE 的距离L2 须距板边≧25 mil. (此项规范顾虑到外包厂在手折版时会将trace 拉断, 请LAYOUT 务必配合) 12➢URM 及BGA Heat Sink 的定位孔(Non-PTH 孔)旁的trace 须与定位孔缘相隔L≧40 mil, 以避免组装时将trace 压坏.13 所有PCB 厂邮票孔及V-CUT 的机构图必须一致.14PCB 之某一长边上需有两个TOOLING HOLES, 其中心距PCB 板边需等于(X,Y)=(200, 200) mil﹐Tooling hole 完成孔直径为160 +2/-2 mil.[鍵入文件標題]15(1) Pitch = 50 mil 的BGA PAD LAYOUT:✓BGA PAD 直径= 20 mil✓BGA PAD 的绿漆直径= 26 mil(2) Pitch = 39.37 mil 的BGA PAD LAYOUT:✓BGA PAD 直径= 16 mil✓BGA PAD 的绿漆直径= 22 mil16各类金手指长度及附近之Via Hole Layout Rule:✓Cards 底部需距金手指顶部距离为Y; 金手指顶部绿漆可覆盖宽度=W; Via✓Hole 落在金手指顶部L 内必须盖绿漆, 并不能有锡珠残留在此区域的ViaHole 内.✓AGP / NLX / SLOT 1 转接卡的零件面: L=600, W=20, Y=284✓AGP / NLX / SLOT 1 转接卡的锡面: L=200, W=20, Y=284✓PCI 的零件面: L=600, W=20, Y=260✓PCI 的锡面: L=200, W=20, Y=260✓Via Hole 锡面与零件面皆要盖绿漆[鍵入文件標題]17多联板标示白点:(1) 联板为双面板, 在V-cut 正面及背面各标示一个φ100mil 的白点.(2) 联板为单面板, 在V-cut 零件面标示一个φ100mil 的白点.(3) 所有PCB 厂白点标示的位置皆一致.18若PCB 短边(非SMT 输送带挟持边)L 需≧4800 mil (≒120 mm); 若无法满足, 请以联板方式排版,使L≧4800 mil,以提高SMT 生产效率.19ICT 测试点基本规范:✓测试点不可覆盖防焊漆.✓测试点为正方形, 其边长L = 30 mil. (图一)✓相邻测试点中心距D 须≧75 mil. (图二)✓测试点不可置于零件文字框内.✓DIMM, RIMM Connector 的Latch 搬开后须与AGP 文字框距离≧40 mil.20 电解电容三孔共享layout,负极两孔需采漏锡方式,使其相通[鍵入文件標題]21 所有零件皆须有文字框, 其文字框外缘不可互相接触、重迭及共享.22线圈孔径layout 尺寸:✓三线缠绕线圈的孔径为91 mil✓单线线圈的孔径为60 mil✓零件三线缠绕立式线圈脚距为9.0± 1.0 mm✓零件三线缠绕卧式线圈脚距为16.0± 1.5 mm[鍵入文件標題]23若PCB 零件面及锡面皆须过SMT, 且DIP 零件皆集中在零件面: ✓锡面: SMD 零件最好集中在某些区域, 且与DIP 零件集中区域有所区隔.✓锡面: 改版时, 变动的SMD 零件最好只是在SMD 零件集中区挪动; 变动的DIP 零件最好只是在DIP零件集中区挪动.✓Through Hole 零件在过DIP 制程时须做治具, 治具会保护住锡面SMD 零件以防止其过锡波时沾锡; 治具会露出DIP 零件脚让锡波沾锡:(图一)✧若锡面SMD 最高的零件高度max(H)为Hmax, 则选用的治具厚度T 须比Hmax 大2 mm 以上.✧DIP可选用的治具厚度T与Through Hole Ring 边缘必须距离D以上, 方可使DIP 零件脚吃锡.T (mm) 3 5 8 10D (mm) 1.5 1.5 2 2✧治具成型时, 其导脚θ=45°.✧治具成型后, 其厚度L 须≧1.5 mm, 以增加治具寿命.✧根据以上原则, 锡面SMD PAD 边缘须与Through Hole Ring 边缘相距X 的简易原则: (图二)T (mm) ≦5 > 5X (mm) 4.2 4.7[鍵入文件標題]24Short Body 型的VGA 15 Pin 的最后一排零件脚在LAYOUT 时须在锡面LAY 锡偷.Ps: DIP 过板方向为I/O Port 朝前.25Socket 7 及Socket 370 的角落朝后的位置在LAYOUT 时须在锡面LAY 锡偷.26其余零件在台北工厂SAMPLE RUN 或ENG RUN 时会标出易短路的Pin 位置,R&D 改版时请加入锡偷.27 若零件长方向与过板方向垂直, 则锡偷的位置及尺寸如右图:[鍵入文件標題]28➢X=1.3~1.8, Y=1.3~1.7 皆可有助于提升良率.➢ X=1.8 且Y=1.5 为最佳组合.➢板长1/4 长度的中央区域,且P1 或P2 有一个≦48mil, 为最须LAY 锡偷的位置.(如图a)➢若无法LAY 连续长条的锡偷,则Pin 与Pin 的中心点必须LAY 满锡偷. (如图b)29 单排排针长边Layout 方向与PCI 长边平行.30 单排排针Drill/Pad 孔径Layout:大孔ψdrill / ψpad = 48 / 64 mil;31 锡面测试点的边缘距过板前方的大铜箔距离d 须≧60 mil.[鍵入文件標題]3233若此零件各种sources 间尺寸差异太大,大小PADs 之间以绿漆分开(较佳选择),绿漆宽度W 须≧10 mil. 或Layout 成本垒板型式.34➢未覆盖SOLDER MASK 的PTH 孔或VIA HOLE 边缘须与SMD PAD 边缘距离L ≧12 mil.➢Via Hole 不能落在PAD 内部.35若此零件有多种sources, 则W,H , L max 选用所用sources 最大的值max(W,H , L max )代入(Equation 1)的X ,Y,R .36[鍵入文件標題]3738若此零件有多种sources,则W, Z 选用所用sources 最大的值max(W, Z )代入(Equation 2)的X ,Y,S .39 线圈的PAD 及零件文字框LAYOUT 尺寸如右图:40 ZIF 的游戏杆长方向与PCI 平行.41 ZIF 的摆设位置请勿摆在PCB 中央1/4 板长的区域.[鍵入文件標題]42Through Hole 零件的与接大铜箔时, 须:✓锡面:PTH 可与邻近大铜箔相接.✓零件面及内层线路:法一:Thermal Relief 型式, PTH 与其余大铜箔不可完全相接, 需用PCB 基材隔开.法二:过锡炉前方(PTH 中心点的前180 度)的大铜箔可与PTH 直接相接; 过锡炉后方(PTH 中心点的后180 度)的大铜箔则不可与PTH 直接相接, 需间隔W ≧60 mil.43若同一片板子有两种机种名称, 但其LAYOUT 皆相同, 为避免SMT 生产时混板, 须在某一角落的光学点, 用不同的喷锡样式辨别. 例如:✓OEM 客户: 用圆形喷锡(直径= 40 mil)光学点.✓用正方形喷锡(长*宽= 25*25 mil)光学点.Ps: 由于R&D在LAYOUT时不知道哪些机种会有不同名称, 故制造单位在生产时帮忙check, 反应时填写技术中心制订的”修改建议”表格, pass 给技术中心, 由技术中心跟LAYOUT 沟通修改. OEM 机种光学点修改必须经过业务同意.[鍵入文件標題]44多联板CAD 文件排列顺序:✓单版排列编号采取逆时针方向, 并将第零片放置在左下角(由左而右, 由下而上).✓白点标示固在离第零片较远的板边上.45大颗BGA(长*宽=35*35 mm)加Heat Sink 后, 附耳文字框宽W=274mil, 附耳文字框长度L=2606 mil, 附耳底部零件限高H 须≦50 mil.46所有零件文字框内缘须距”零件最大本体的最外缘或PAD 最外缘”≧10 mil; 亦即双边≧20 mil.零件公差:L +a/-b Lmax=L+a, Lmin=L-bW +c/-d Wmax=W+c, Wmin=W-d∴文字框Layout: 长≧Lmax+20, 宽≧Wmax+20 47若”零件最大本体的最外缘与PAD 最外缘”外形比例不符合,则零件文字框依两者最大值而变化.48 文字框线宽≧6 mil.[鍵入文件標題]49SMD 零件极性标示:(1) QFP: 以第一pin 缺角表示.(图a) (2) SOIC: 以三角框表示. (图b)(3) 钽质电容: 以粗线标示在文字框的极性端. (图c)50 零件标示极性后文字框外缘不可互相接触、重迭. 51 用来标示极性的文字框线宽≧12 mil.52 螺丝孔规格:✓ Through Hole 为Non-PTH 孔.✓ Non-PTH 孔Ring 周围均匀分布精灵孔.✓ 防焊漆在Component Side 全不覆盖.✓ 防焊漆在Solder Side 仅露出精灵孔吃锡, 其余覆盖防焊漆.53 当机种变更版本时, 其对角线之一个或二个光学点位置必须挪动, 其间距(a i ’,b I ’)与前一版本(a i , b i )必须 | a i -a i ’ | ≧200 mil 或 | b i -b i ’ | ≧200 mil ; 但若改版幅度不大时, 可在对角线光学点的其中一个旁标示直径100mil 的白点, 白点位置随版本变化而改变, 以利辨别.Ps. ai, ai’, bi, bi’ 定义请参阅附件一.54ICT 测试点建议规范:✓ 尽量将所有测试点置于Solder Side. ✓ 测试点应平均分布, 以防测试时板翘.✓ 测试点中心应距板边或V-CUT 折断边≧ 100 mil. ✓ Slot1, AGP 长边与邻近的电解电容垂直摆放.✓Slot1, AGP, Socket 7, Socket 370, IC 的文字框与邻近的电解电[鍵入文件標題]容须距L≧100 mil, 以防测试时Test Jet 及金手指撞击电解电容.55BGA LAYOUT 如”PCB 基本规范”项次13 完成后, 除BGA PAD 外, 皆须加印白文字漆于绿漆上, 以防止绿漆覆盖VIA HOLES 不佳时而造成BGA 空焊, 并在BGA 本体外缘W = 30 mil 标示三角形极性.56PCB 零件面上须印刷白色文字框, 此白框可摆在任何位置, 但不可被零件置件后压住, 其白框长L*宽W = 1654 *276 mil; 此文字框乃为Shop Flow 贴条形码,以利计算机化管理.[鍵入文件標題]57PCB 背面上SMD 零件过DIP 制程,其制程吃锡较不易, 需有特殊PAD Layout,各类零件(Chip、IC、SOT、MELF) PAD 尺寸大小建议如下:零件摆设位置与过板方向关系如右图所示.58过SMT 的零件, 其塑料材质的热变形温度(Td)须≧240℃, 或其塑料能承受Resistance to Soldering Heat 在240℃, 10 秒钟而不变形, 塑料材质如全部LCP、PPS, 及部份PCT、PA6T.但Nylon46 及Nylon66 含水率太高,不适合SMT reflow.59 零件的Shielding Plate 不可选用镀全锡.60SMD 零件的包装须为(1)TAPE & REEL (2)硬TRAY 盘包装(3) Tube 包装,TAPE & REEL 为最佳选择, 包装规范请参阅”零件包装建议规范”.61过DIP 零件的包装须为硬TRAY 盘包装, 或Tube 包装为最佳选择, 包装尺寸则无硬性规范. 其中DIMM, RIMM 及各式Slots 如有Board Lock 设计则必须以硬TRAY 盘包装.[鍵入文件標題]62SMD TYPE 的Connectors,其零件塑料顶部正中央须有一平坦区域(贴上一平坦胶片)W*L 以利置件机吸取.,其面积建议如下(单位mm):(1) Y<5 且X<20:平坦区域面积W*L≧1.8*1.8.(2) Y<5 且X≧20:平坦区域面积W*L≧3*3.(3) 5≦Y<10:平坦区域面积W*L≧3*3.(4) Y≧10:平坦区域面积W*L≧6*6.(5) 贴胶片面积不可大于零件本体.63PCB无防呆孔但Connector 却有极性要求, 其插入的DIP Connectors 须有一个定位防呆Post, 以防插件极反.64 若SMD Connector 有极性, 则在Connector 本体顶部标示极性.65因SMT 机器高度限制,选用的SMD 零件其PCB 底部至零件顶部的最大高度H须≦13.5mm.66 于零件本体或Housing 打上厂商Logo.[鍵入文件標題]67DIP Connector 其Board Lock 与PCB Through Hole 干涉量以8~10 mil 为最佳,且组装时须平稳顺畅,避免PCB 上其它零件跳脱.[鍵入文件標題]68Through Hole 一般零件:1. StandOff Hc: Through Hole 零件其StandOff 高度Hc 须≧0.2 mm.2. StandOff 须置于Housing 周围,以便检查浮件问题.(图(b))3. Solder Tail 脚长Tc(图(c)):(1) 若min(Pr, Pc)<1mm 时, 则Tc= 2.3 +0.15/–0.10 mm.(2) 若min(Pr, Pc)=1mm 时, 则Tc= 2.6±0.2 mm.(3) 若min(Pr, Pc)>1mm 时, 则Tc= 2.9±0.3 mm.4. Kink 脚长Yc 须: Tc ≦Yc ≦3.6 mm. (图(a))Through Hole 特殊零件Solder Tail 脚长:✓Short Boby D-SUB 零件, Tc= 2.35 +0.15/–0.10 mm.✓Phone Jack, Tc= 3.0±0.2 mm.✓Game/Audio, Tc= 2.6±0.2mm5. 脚间距定义以减少Solder Bridge:(1) 3.2mm<Pr<4.2mm(2) 3.5mm<Pc<4.5mm如 Pr Pc 不在此范围内需Layout 锡偷。

PCB设计检查表-PCB-checklist

4.4.12

148

PAD与线的SPACING:最小要5mil(最好把线与SPACING平分成三等份)

149

PAD与PAD的SPACING:最小要8mil

150

BGA SOCKET(Through Hole TYPE)

151 4.4.13 Hole size:1.27mm pitch 用0.5mm(20mil)

133 4.4.4 Via Hole 尺寸为20mil

134 4.4.5 POWER 及 GROUND ACCESS 为32mil

135 4.4.6 GRID HOLE及其他ACCESS为45mil

136

GUIDE PIN HOLE(非镀通孔)

137 4.4.7 如图纸有提供HOLE SIZE ,按图纸做

128 4.3 与电原理图网络匹配检查

129 4.4 元件焊盘过孔尺寸检查

130 4.4.1 板厚度≤125mil时,VIA孔(过孔)为25mil

131 4.4.2 板厚度>125mil时,VIA孔(过孔)为32mil

132 4.4.3 对于长方形的PAD ,长的每边15mil ,短的每边有4mil

26 2.19 含贴片器件的PCB,贴片器件所在面的板任选2角各放置一个定位光标

27 2.20 MOUNTING孔(安装孔)是否镀铜(要镀铜)

28 2.21 GUIDE PIN孔(定位孔)是否没镀铜(除另有说明,不要镀铜)

29 2.22 元器件的1脚是否为方PAD

30 2.23 POWER PLANE 分割时是否出现瓶颈

9 2.2 所有器件已经放置到板面

10 2.3 整体布局参照原理功能框图,兼顾美观及电源、地的分割

11 2.4 高、中、低分开放置

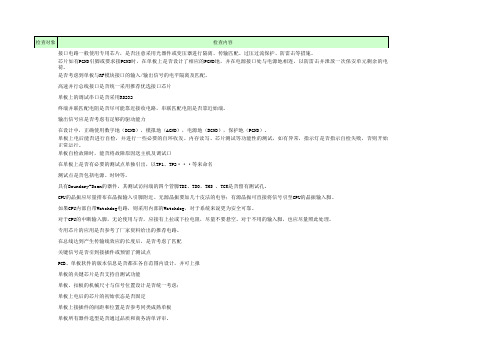

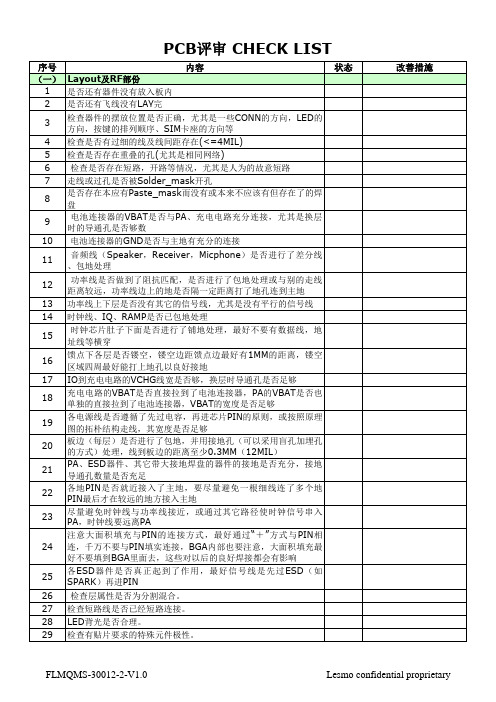

手机PCB评审CHECK LIST

序号 及 部份 (一) Layout及RF部份 1 是否还有器件没有放入板内 2 是否还有飞线没有LAY完

3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

内容

状态

改善措施

检查器件的摆放位置是否正确,尤其是一些CONN的方向,LED的 方向,按键的排列顺序、SIM卡座的方向等 检查是否有过细的线及线间距存在(<=4MIL) 检查是否存在重叠的孔(尤其是相同网络) 检查是否存在短路,开路等情况,尤其是人为的故意短路 走线或过孔是否被Solder_mask开孔 是否存在本应有Paste_mask而没有或本来不应该有但存在了的焊 盘 电池连接器的VBAT是否与PA、充电电路充分连接,尤其是换层 时的导通孔是否够数 电池连接器的GND是否与主地有充分的连接 音频线(Speaker,Receiver,Micphone)是否进行了差分线 、包地处理 功率线是否做到了阻抗匹配,是否进行了包地处理或与别的走线 距离较远,功率线边上的地是否隔一定距离打了地孔连到主地 功率线上下层是否没有其它的信号线,尤其是没有平行的信号线 时钟线、IQ、RAMP是否已包地处理 时钟芯片肚子下面是否进行了铺地处理,最好不要有数据线,地 址线等横穿 馈点下各层是否镂空,镂空边距馈点边最好有1MM的距离,镂空 区域四周最好能打上地孔以良好接地 IO到充电电路的VCHG线宽是否够,换层时导通孔是否足够 充电电路的VBAT是否直接拉到了电池连接器,PA的VBAT是否也 单独的直接拉到了电池连接器,VBAT的宽度是否足够 各电源线是否遵循了先过电容,再进芯片PIN的原则,或按照原理 图的拓朴结构走线,其宽度是否足够 板边(每层)是否进行了包地,并用接地孔(可以采用盲孔加埋孔 的方式)处理,线到板边的距离至少0.3MM(12MIL) PA、ESD器件、其它带大接地焊盘的器件的接地是否充分,接地 导通孔数量是否充足 各地PIN是否就近接入了主地,要尽量避免一根细线连了多个地 PIN最后才在较远的地方接入主地 尽量避免时钟线与功率线接近,或通过其它路径使时钟信号串入 PA,时钟线要远离PA 注意大面积填充与PIN的连接方式,最好通过“+”方式与PIN相 连,千万不要与PIN填实连接,BGA内部也要注意,大面积填充最 好不要填到BGA里面去,这些对以后的良好焊接都会有影响 各ESD器件是否真正起到了作用,最好信号线是先过ESD(如 SPARK)再进PIN 检查层属性是否为分割混合。 检查短路线是否已经短路连接。 LED背光是否合理。 检查有贴片要求的特殊元件极性。

PCB LAYOUT检查项列表(试用版)

基带/射频/EDA

28

带极性器件,如IC、钽电容、有极性区分的连接器、二极管、单向TVS管 要在位号图上标出极性,多数标注第1Pin的位置。

Байду номын сангаас

基带/EDA

29 Gebar归档前需要检查露铜是否符合要求,以及基本工艺处理

基带/射频/EDA

6 连接器部分的地,Vbat,Vcharge换层的时候,是否打了足够数量的孔以保 基带/EDA

证性能。Vbat主线的宽度是否不小于2mm,VCHG宽度0.8mm以上

7

检查系统主电源如VCORE,VMEM,VRF,VDD等的走线,主线一般不少于 0.25mm,线宽、走向分支、过孔数量等。子系统也需要检查,如GPS、TV

基带/EDA

LCD下面必须有露铜,PCB上的焊盘要比FPC上的焊盘长0.5mm以上保证可

13 焊接性,固定PIN的焊盘要做成热焊盘以方便焊接。为保护ESD可能存的 基带/EDA

问题,是否有需要其它露铜处理。

14 注意一些特殊线的处理,如USB数据线差分等。

基带/EDA

15 检查键盘DOME定位孔、天线支持定位孔、LCD定位孔是否正确

基带/EDA/结构

16 测试点Vbat,GND,PWR_ON/OFF,RXD,TXD是否留出,是否有丝印标示

基带/EDA

17 Mic,Speaker,Vibrator,电池连接器等元件要由丝印标示正、负极

基带/EDA

18 RF PA等地分割是否满足要求;RF、蓝牙晶体下方一、二层挖空

射频/EDA

19 IQ、AFC、APC上下左右要包地,周围要多打地孔,换层的孔周围包地 射频/EDA

/EDA/结构

3

检查原理图和PCB图同步的时候产生的网络报告内容,确认没有连接关系 的网络

Layout Checklist V1.5

检查项项目分类序号检查内容需求结果检查结果(OK/NG/NA)备注板中是否采用新封装,若有请在下面注明位号及封装名称(PCB文件评审重点关注)。

a. b. c. d.e. f. g. h.2是否按《元件封装建立手册及PART命名规则 》制作新元件封装。

通用需求3新封装审核:第1脚标识、焊盘大小、外形尺寸、封装命名是否符合封装制作标准(注:外观对称的插件元件是否有做防呆)。

通用需求4丝印不能上焊盘,丝印与焊盘间距≥0.1mm。

通用需求管脚5极性元件,如:电解电容、二极管、稳压管、三极管、MOS管等管脚顺序是否与元件规格书相同。

通用需求6插件元件过孔制作标准:元件规格书标识脚径为0.8-1.0mm ,双面板:脚径+0.3mm /单面板:脚径+0.2(要求:规格书中脚径为实物实际脚径)。

通用需求7元件脚需沾锡或误差太大元件脚径1.0-1.2mm,双面板:脚径+0.5mm /单面板:脚径+0.3(要求:规格书中脚径为实物实际脚径)。

通用需求8是否调用新设计模板。

重点检查:COPPER 与PAD 、SMD 的安全间距为8MIL ,COPPER 与TRACE 、VIA 、COPPER 安全间距为6MIL。

通用需求9各项LAYOUT规则、PCB叠层、过孔设置是否正确合理。

通用需求10是否按要求填写模板中的各项信息。

通用需求11参考LAYOUT GUIDE进行元件布局。

通用需求12PCB设计坐标原点放置在PCB板左下角。

通用需求13元件摆放的格点是否为0.1mm。

通用需求14极性元件(电解电容、二极管、稳压二极管)不多于两个方向放置。

通用需求15SMD与SMD,SMD与插件元件之间的距离大于0.6mm以上(特别关注有高度差的两个元件)。

通用需求16贴片元件本体(含顶层、底层)与PCB传送板边的距离是为5mm以上,若不能满足需要加5mm假边。

通用需求17插件元件焊盘中心离板边大于3.5MM。

通用需求18双面贴工艺,底层贴片器件与插件器件的脚位距离≥3mm(夹具工艺)。

PCB原理图Checklist检查表

PCB原理图Checklist检查表类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P 和N 与网络命令的P 和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol 。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU 点灭的指示灯,便于故障时直观判断电源问题还是MCU 问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE 按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD 门芯片的OD 门或者OC 门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO 、IIC 、PCI 、Local bus 仿真电路中使用电感、电容使用合适Q 值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

PCB LAYOUT CHECK LIST

检查电气特性连接是否完备,检查间距是否完 全正确 所有的BGA器件和手焊件的pad上不允许有激光 孔, 检查PCB板上是否有MARK点 检查电源线是否够粗,并且尽可能的加粗,在 电源的输入输出端等有大电流的情况下要铺铜 并增加一些过孔来连接 检查所有的差分走线对、音频信号线、时钟线 是否全部包地;并且尽量做到在每层都能包地 完全 检查地线网络的铺铜,每层中除了一些必须隔 离的线之外,一些不重要的信号线尽量靠近, 保证地网络的铺铜不要太破碎。 固定位于RF路径上的零组件,并调整其方位使 RF路径的长度减到最小。并使RF输入远离RF 输出,并尽可能远离高功率电路和低噪音电路 将RF路径上的过孔数量尽量减到最少,尺寸减 到最小,不仅可以减少路径电感,而且还可以 减少主接地上的虚焊点,并可减少RF能量泄漏 到层叠板内其它区域的机会。 射频IQ线,时钟线,尽量包地,避免干扰 微带线和带状线线宽是否达到阻抗匹配, 射频电源是否跟BB电源分开,RF电源线宽不 能太细 射频线是否有参考地

PCB

项目 设计者:

LAYOUT CHECK LIST

检查 者:

(OK) OR (NG)

备注

整体 检查PCB与原理图是否同步 检查 利用在Design Rules中设置的规则对PCB进行整体的连通性(Connective)以 及间距(Clearance)的检查,并检查并排除所有的 检查元器件摆放是否符合设计规范要求 元器件摆放是否重叠(允许零件的丝印重叠,但不允许跨入) 元件 元器件的摆放是否影响其他元件的插拔和焊接 布局 元器件摆放符合限高要求,不影响其他元件的贴焊和安装 元器件离板边的距离是否符合工艺要求 检查所用元件库机械尺寸以及PIN脚顺序是否正确(新增加的元件) 有极性器件的摆放方向尽可能一致

检查元器件摆位是否和结构的冲突 检查屏蔽罩,固定孔,耳机,麦克以及按键,摄像头位置,SIM,CF与SD 卡座是否与结构所给的位置一致 检查去耦电容是否靠近相对应的器件的电源引脚 检查零件与屏蔽罩之间间距是否符合设计规范要求(>=0.4mm) 各插件孔,安装孔,过孔以及为增加电源和地的 导电面积而加的过孔的层定义是否正确,孔是 否沉铜的设置是否正确 板的四周电源和地层要有一定的挖空区, 避免 毛刺短路,降低EMI 检查耦合电容是否起到耦合的作用,走线顺序 是否恰当 线路 检查 BB 检查ESD器件是否起到作用 检查单点接地点是否放在焊盘上(最好不要放 在焊盘上) 检查器件管脚是否设置为热焊盘 信号线离板边的间距是否符合要求(>=0.3mm) 晶振,时钟芯片及网口变压器下尽量避免信号 通过

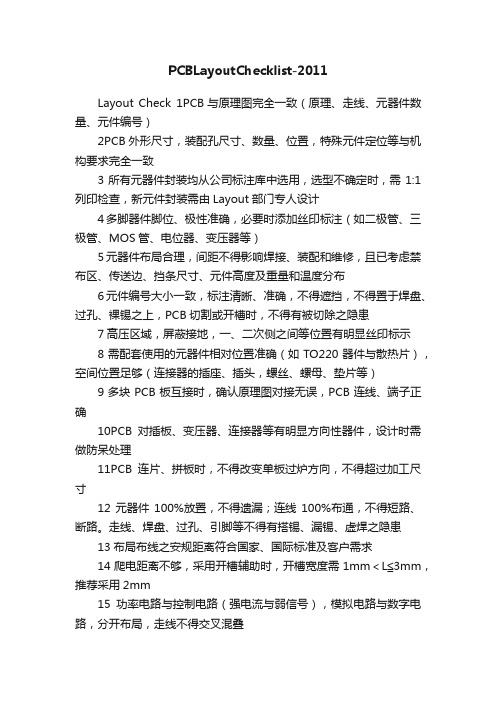

PCBLayoutChecklist-2011

PCBLayoutChecklist-2011Layout Check 1PCB与原理图完全一致(原理、走线、元器件数量、元件编号)2PCB外形尺寸,装配孔尺寸、数量、位置,特殊元件定位等与机构要求完全一致3所有元器件封装均从公司标注库中选用,选型不确定时,需1:1列印检查,新元件封装需由Layout部门专人设计4多脚器件脚位、极性准确,必要时添加丝印标注(如二极管、三极管、MOS管、电位器、变压器等)5元器件布局合理,间距不得影响焊接、装配和维修,且已考虑禁布区、传送边、挡条尺寸、元件高度及重量和温度分布6元件编号大小一致,标注清晰、准确,不得遮挡,不得置于焊盘、过孔、裸锡之上,PCB切割或开槽时,不得有被切除之隐患7高压区域,屏蔽接地,一、二次侧之间等位置有明显丝印标示8需配套使用的元器件相对位置准确(如TO220器件与散热片),空间位置足够(连接器的插座、插头,螺丝、螺母、垫片等)9多块PCB板互接时,确认原理图对接无误,PCB连线、端子正确10PCB对插板、变压器、连接器等有明显方向性器件,设计时需做防呆处理11PCB连片、拼板时,不得改变单板过炉方向,不得超过加工尺寸12元器件100%放置,不得遗漏;连线100%布通,不得短路、断路。

走线、焊盘、过孔、引脚等不得有搭锡、漏锡、虚焊之隐患13布局布线之安规距离符合国家、国际标准及客户需求14爬电距离不够,采用开槽辅助时,开槽宽度需1mm<L≦3mm,推荐采用2mm15功率电路与控制电路(强电流与弱信号),模拟电路与数字电路,分开布局,走线不得交叉混叠16高、中、低频电路分区布设;高频信号回路尽量小,走线尽量短;与其他信号线远离,满足3W原则17电源线、地线尽量加粗,走线合理,滤波电容位置准确18多层板内电层满足20H原则,各层上标明层序号19功率地、工作地、保护地、静电防护与屏蔽地等设计合理,单点连接点位置合适20EMI防护合理,安规电容、压敏电阻、TVS等布局布线正确,符合电流流向21保险丝前后距离合适,爆炸碎片不得外泄,熔断后不得放电打火22电源输入输出部分明显分开,滤波整流后的走线不得再绕回原输入端,防止二次干扰23金属壳体器件,周围需预留足够空间,不可与其他器件相碰;贴板安装时,本体下方不得布线、打孔(同电位的除外)24SMD本体下方谨慎走线,不得有裸线,过孔需涂绿油覆盖,0805以下封装内部不推荐走线25走线宽度符合要求(需考虑载流能力、温升、压降等因素)26轴向高度过高,改为卧式安装的器件,PCB上需预留足够空间,并考虑固定方式,防止震动磨损、掉落和造成短路27结合加工工艺、元件选型,器件放置需合理选择PCB正反面28根据原理及焊接工艺,合理设计SMD放置方向,布局时考虑锡流阴影效应检查结果(Y/N)检查内容序号原因说明Layout Check 检查结果(Y/N)检查内容序号原因说明29因焊接工艺(波峰焊、回流焊)不同,同一SMD元件,需制做两个封装,布局时根据预设的焊接工艺合理选择元件封装30走线、铜箔距板边0.75mm以上,焊盘、过孔内壁距板边1mm 以上,一般元器件距板边1mm以上,金属体、SMD距板边2mm以上31PCB上无孤岛,大面积空白区域需做铺铜接地处理32单面板焊盘属性设计正确,接地固定孔选择准确33背板正确标示槽位号、槽位名、端口名、护套方向34工艺边设计合理,与原PCB之间或拼板、连片之间需做V割处理,必要位置做CUT-OUT或邮票孔处理35贴片机所需光绘点、定位孔放置合理,数量适当36工装测试所需定位孔尺寸合适、位置合理、数量适当37测试点数量足够,位置分布合理,两相邻测试点间距需大于5mm 38PCB上标明机种号、版本号、完成时间等必要信息39有无铅化要求的PCB,板上需有无铅标识40PCB板材、板厚、铜箔厚度、表面处理方式、防火等级等要求需在板外说明清楚,或用文件另行通知加工厂 Layout: Check:。

PCB Layout布局布线 Checklist检查表

35

PCB布线与布局

向,以减少不必要的层间窜扰;当由于板结构限制(如某些背板)难以避 免出现该情况,特别是信号速率较高时,应考虑用地平面隔离各布线层,

用地信号线隔离各信号线;

36

PCB布线与布局

不允许出现一端浮空的布线,为避免“天线效应”。

阻抗匹配检查规则:同一网格的布线宽度应保持一致,线宽的变化会造成

30

PCB布线与布局

单层PCB:地线至少保持1.5mm宽,跳线和地线宽度的改变应保持最低

31

PCB布线与布局

双层PCB:优先使用地格栅/点阵布线,宽度保持1.5mm以上。或者把地放 在一边,信号电源放在另一边

32

PCB布线与布局

保护环:用地线围成一个环形,将保护逻辑围起来进行隔离

PCB电容:多层板上由于电源面和地面绝缘薄层产生了PCB电容。其优点

时钟布线经连接器输出时,连接器上的插针要在时钟线插针周围布满接地

插让针模拟和数字电路分别拥有自己的电源和地线通路,在可能的情况下,应

5

PCB布线与布局

尽量加宽这两部分电路的电源与地线或采用分开的电源层与接地层,以便

减小电源与地线回路的阻抗,减小任何可能在电源与地线回路中的干扰电

压单独工作的PCB的模拟地和数字地可在系统接地点附近单点汇接,如电源

应(改善瞬态响应时间)。

22

PCB布线与布局

旁路电容靠近电源输入处放置

23

PCB布线与布局

去耦电容置于电源输入处。尽可能靠近每个IC

PCB基本特性 阻抗:由铜和横切面面积的质量决定。具体为:1盎司0.49 毫欧/单位面积

电容:C=EoErA/h,Eo:自由空间介电常数,Er:PCB基体介电常数,

PCB 原理图 Checklist检查表

类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P 和N 与网络命令的P 和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol 。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU 点灭的指示灯,便于故障时直观判断电源问题还是MCU 问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE 按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD 门芯片的OD 门或者OC 门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO 、IIC 、PCI 、Local bus 仿真电路中使用电感、电容使用合适Q 值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

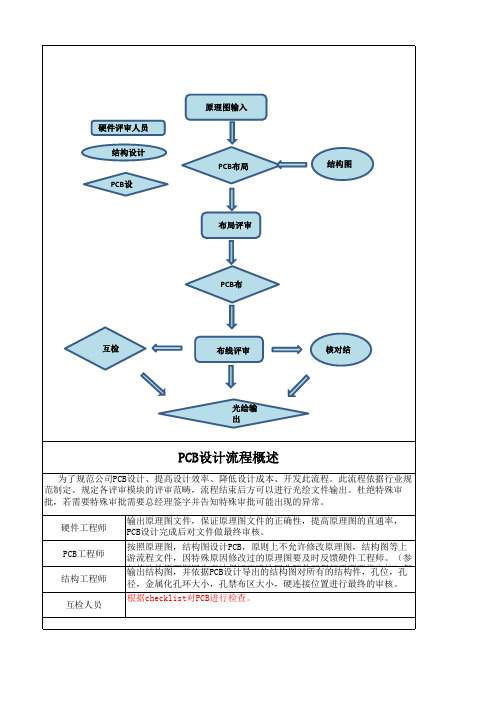

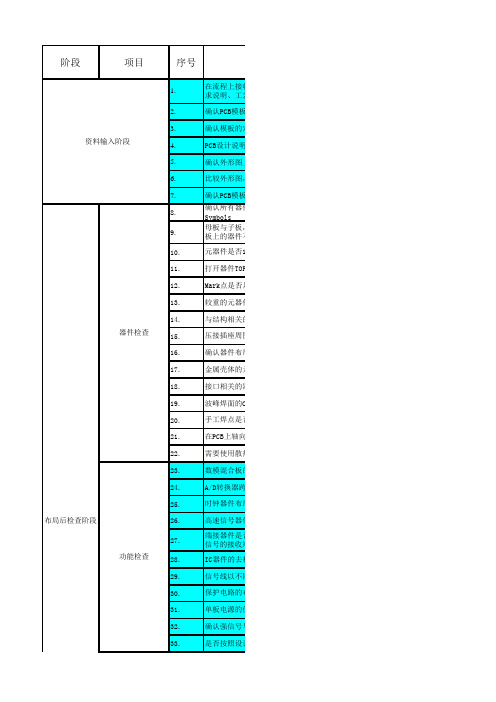

PCB设计checklist

原理图输入 硬件评审人员 结构设计 互检

布线评审

核对结

光绘输 出

PCB设计流程概述

为了规范公司PCB设计、提高设计效率、降低设计成本、开发此流程。此流程依据行业规 范制定。规定各评审模块的评审范畴,流程结束后方可以进行光绘文件输出。杜绝特殊审 批,若需要特殊审批需要总经理签字并告知特殊审批可能出现的异常。 硬件工程师 PCB工程师 结构工程师 互检人员 输出原理图文件,保证原理图文件的正确性,提高原理图的直通率, PCB设计完成后对文件做最终审核。 按照原理图,结构图设计PCB,原则上不允许修改原理图,结构图等上 游流程文件,因特殊原因修改过的原理图要及时反馈硬件工程师。(参 与修改的原理图因为无法保证正确性因此硬件工程师需要严格审核)保 输出结构图,并依据PCB设计导出的结构图对所有的结构件,孔位,孔 径,金属化孔环大小,孔禁布区大小,硬连接位置进行最终的审核。 根据checklist对PCB进行检查。

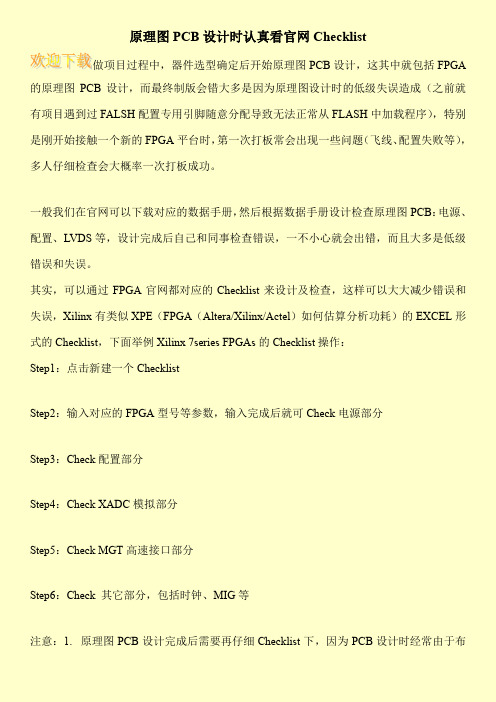

原理图PCB设计时认真看官网Checklist

原理图PCB设计时认真看官网Checklist

做项目过程中,器件选型确定后开始原理图PCB设计,这其中就包括FPGA 的原理图PCB设计,而最终制版会错大多是因为原理图设计时的低级失误造成(之前就有项目遇到过FALSH配置专用引脚随意分配导致无法正常从FLASH中加载程序),特别是刚开始接触一个新的FPGA平台时,第一次打板常会出现一些问题(飞线、配置失败等),多人仔细检查会大概率一次打板成功。

一般我们在官网可以下载对应的数据手册,然后根据数据手册设计检查原理图PCB:电源、配置、LVDS等,设计完成后自己和同事检查错误,一不小心就会出错,而且大多是低级错误和失误。

其实,可以通过FPGA官网都对应的Checklist来设计及检查,这样可以大大减少错误和失误,Xilinx有类似XPE(FPGA(Altera/Xilinx/Actel)如何估算分析功耗)的EXCEL形式的Checklist,下面举例Xilinx 7series FPGAs的Checklist操作:

Step1:点击新建一个Checklist

Step2:输入对应的FPGA型号等参数,输入完成后就可Check电源部分

Step3:Check配置部分

Step4:Check XADC模拟部分

Step5:Check MGT高速接口部分

Step6:Check 其它部分,包括时钟、MIG等

注意:1. 原理图PCB设计完成后需要再仔细Checklist下,因为PCB设计时经常由于布。

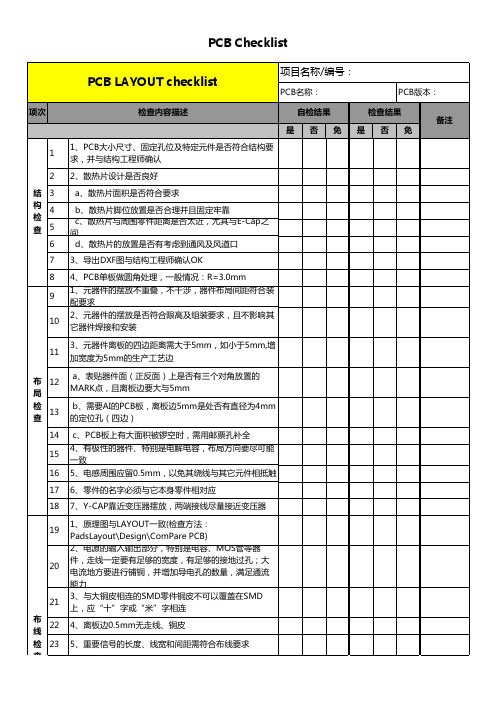

PCB LAYOUT自查 标准

项目名称/编号:

PCB名称: 自检结果 否 免 是 PCB版本: 检查结果 否 免 备注

20

21 布 22 线 检 23 查

线 检 查 24 25 26 27 28 29 30 31 距 32 离 检 33 查 34 35 36 37 38

6、SMT器件焊盘上无过孔,且同网络过孔孔到焊盘的间 距要保证最小安全间距 7、走线无直角、锐角、多余线头,没有孤立的铜皮和无 属性铜皮 8、走线进出插件零件焊盘处需加“泪滴”,特别是经常拔 插的器件 9、增加ICT测试点 1、高低压距离 电位差 50 100 200 300 400 600 1000 距离(mm) 0.3 0.6 1.0 1.2 1.5 2.0 5.0 LAYO

42

43

44 45 46

自检人/日期 :

1、本表单适用于PCB投板前的最后检查;

复检人/日期 :

2、该表经CAD工程师自检及复检人员(复检人为项目负责人)签字确认后将表单统一管理;

2、安全距离---参考安规资料,初级与次级:高压 6.4MM,低压3.5MM,距离不够,可开槽,槽宽最小为 0.8mm 1、单板名称、料号、版本号、设计日期及是否留有 S/N(尺寸规格33*8mm)位置,我们自己的LOGO符。 2、元器件位号字体、大小合适,摆放整齐、美观、形象 法,最多两个方向,且无丝印压焊盘现象,电源座,跳 线、连接器件等连接头的标识说明不被其它器件覆盖, 第一PIN标示明确 3、重要或经常拔插的器件和连接头的丝印要适当放大或 另加相关文字,方便查找 4、表示FUSE过流、过压值(XA,XV)及警告提示:“ CAUTION:FOR CONTINUED PROTECTION AGAINST RISK OF FIRE,REPLACE ONLY WITH SAME TYPE AND RATING OF FUSE." 5、所有太贴近的焊盘之间加白油,设定SMD与SMD、 SMD与PAD、PAD与PAD之间距离为40mil,如有问题 加白油(双面板加双面白油,单面板将白油放于29层) 6、板尺寸、板厚公差、层叠、阴焊油、基材类型、工艺 说明、金手指工艺要求、V-CUT工艺要求、异形孔公差 、波峰焊方向及其它物殊工艺要求需注明 7、拼板的设计是否符合生产工艺,并与工艺工程师确认 8、拼板大小尺寸为: 最大(L460 W290) 最小(L50 W50) 8、接插件标明,丝印

PCB Layout Review Check List-V0.3

說明:1).Tooling hole 完成孔直径为160 +2/-2 mil.2).增加“PCB 背面SMD 过DIP 制程零件PAD LAYOUT 建议规范”3).BGA 及QFP 旁毋需Lay 光学点.4).“PCB LAYOUT 基本规范”:为R&D Layout 时必须遵守的事项, 否则SMT,DIP,裁板时无法生产.5).“锡偷LAYOUT RULE 建议规范”: 加适合的锡偷可降低短路及锡球.6).“PCB LAYOUT 建议规范”:为制造单位为提高量产良率,建议R&D 在design 阶段即加入PCB Layout.7).“PCB 背面SMD过DIP 制程零件PAD LAYOUT 建议规范”:SMD 过DIP 特殊制程PAD 尺寸及摆设方位.8).“零件选用建议规范”: Connector 零件在未来应用逐渐广泛,又是SMT 生产时是偏移及置件不良的主因,故制造希望9).R&D 及采购在购买异形零件时能顾虑制造的需求, 提高自动置件的比例.10).“零件包装建议规范”:,零件taping 包装时, taping 的公差尺寸规范,以降低抛料率.No. 問題描述圖片說明判定結果備註說明合格不合格01 一般PCB 过板方向定义:PCB 在SMT 生产方向为短边过回焊炉(Reflow), PCB 长边为SMT 输送带夹持边.PCB 在DIP 生产方向为I/O Port 朝前过波焊炉(Wave Solder), PCB 与I/O 垂直的两边为DIP 输送带夹持边.02 金手指过板方向定义:SMT: 金手指边与SMT 输送带夹持边垂直. DIP: 金手指边与DIP 输送带夹持边一致.03 SMD 零件文字框外缘距SMT 输送带夹持边L1 需≧150 mil.SMD 及DIP 零件(I/O 零件除外)文字框外缘距板边L2 需≧100 mil.04 PCB 板边至PCB 板边的螺丝孔(精灵孔)PAD 的中心, 直径3mm的范围内不得有SMD 或DIP 零件(如右图虚线所示)05 V-Cut 或邮票孔须距正上方平行板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧80 mil.06 V-Cut 或邮票孔须距正上方垂直板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧200 mil.07 V-Cut 或邮票孔须距左右方平行板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧140 mil.08 V-Cut 或邮票孔须距左右方垂直板边的积层堆栈的Chip C, Chip L 零件文字框外缘L≧180 mil.09 邮票孔与周围突出板边零件的文字框须距离L≧40 mil.10 本体厚度跨越PCB 的零件,其跨越部份的V-CUT 必须挖空.11 如有邮票孔或V-cut 时, trace 距邮票孔或V-cut 的距离L1 边须≧50 mil;其余TRACE 的距离L2 须距板边≧25 mil. (此项规范顾虑到外包厂在手折版时会将trace 拉断, 请LAYOUT 务必配合)12 URM 及BGA Heat Sink 的定位孔(Non-PTH 孔)旁的trace 须与定位孔缘相隔L≧40 mil, 以避免组装时将trace 压坏.13 所有PCB 厂邮票孔及V-CUT 的机构图必须一致.14 PCB 之某一长边上需有两个TOOLING HOLES, 其中心距PCB 板边需等于(X,Y)=(200, 200) mil﹐Tooling hole 完成孔直径为160 +2/-2 mil.15 (1) Pitch = 50 mil 的BGA PAD LAYOUT:✓BGA PAD 直径= 20 mil✓BGA PAD 的绿漆直径= 26 mil (2) Pitch = 39.37 mil 的BGA PAD LAYOUT:✓BGA PAD 直径= 16 mil✓BGA PAD 的绿漆直径= 22 mil16 各类金手指长度及附近之Via Hole Layout Rule:✓Cards 底部需距金手指顶部距离为Y; 金手指顶部绿漆可覆盖宽度=W; Via✓Hole 落在金手指顶部L 内必须盖绿漆, 并不能有锡珠残留在此区域的ViaHole 内.✓AGP / NLX / SLOT 1 转接卡的零件面: L=600, W=20, Y=284 ✓AGP / NLX / SLOT 1 转接卡的锡面: L=200, W=20, Y=284✓PCI 的零件面: L=600, W=20, Y=260✓PCI 的锡面: L=200, W=20, Y=260✓Via Hole 锡面与零件面皆要盖绿漆17 多联板标示白点:(1) 联板为双面板, 在V-cut 正面及背面各标示一个φ100mil 的白点.(2) 联板为单面板, 在V-cut 零件面标示一个φ100mil 的白点.(3) 所有PCB 厂白点标示的位置皆一致.18 若PCB 短边(非SMT 输送带挟持边)L 需≧4800 mil (≒120 mm); 若无法满足, 请以联板方式排版,使L≧4800 mil,以提高SMT 生产效率.19 ICT 测试点基本规范:✓测试点不可覆盖防焊漆.✓测试点为正方形, 其边长L = 30 mil. (图一)✓相邻测试点中心距D 须≧75 mil. (图二)✓测试点不可置于零件文字框内.✓DIMM, RIMM Connector 的Latch 搬开后须与AGP 文字框距离≧40 mil.20 电解电容三孔共享layout,负极两孔需采漏锡方式,使其相通21 所有零件皆须有文字框, 其文字框外缘不可互相接触、重迭及共享.22 线圈孔径layout 尺寸:✓三线缠绕线圈的孔径为91 mil✓单线线圈的孔径为60 mil✓零件三线缠绕立式线圈脚距为9.0± 1.0 mm ✓零件三线缠绕卧式线圈脚距为16.0± 1.5 mm23 若PCB 零件面及锡面皆须过SMT, 且DIP 零件皆集中在零件面: ✓锡面: SMD 零件最好集中在某些区域, 且与DIP 零件集中区域有所区隔.✓锡面: 改版时, 变动的SMD 零件最好只是在SMD 零件集中区挪动; 变动的DIP 零件最好只是在DIP 零件集中区挪动.✓Through Hole 零件在过DIP 制程时须做治具, 治具会保护住锡面SMD 零件以防止其过锡波时沾锡; 治具会露出DIP 零件脚让锡波沾锡:(图一)✧若锡面SMD 最高的零件高度max(H)为Hmax, 则选用的治具厚度T 须比Hmax 大2 mm 以上.✧DIP可选用的治具厚度T与Through Hole Ring 边缘必须距离D以上, 方可使DIP 零件脚吃锡.✧治具成型时, 其导脚θ=45°.✧治具成型后, 其厚度L须≧1.5 mm, 以增加治具寿命.✧根据以上原则, 锡面SMD PAD 边缘须与Through Hole Ring 边缘相距X 的简易原则: (图二)24 Short Body 型的VGA 15 Pin 的最后一排零件脚在LAYOUT 时须在锡面LAY 锡偷.Ps: DIP 过板方向为I/O Port 朝前.25 Socket 7 及Socket 370 的角落朝后的位置在LAYOUT 时须在锡面LAY 锡偷.26 其余零件在台北工厂SAMPLE RUN 或ENG RUN 时会标出易短路的Pin 位置,R&D 改版时请加入锡偷.27 若零件长方向与过板方向垂直, 则锡偷的位置及尺寸如右图:28 X=1.3~1.8, Y=1.3~1.7 皆可有助于提升良率.X=1.8 且Y=1.5 为最佳组合.板长1/4 长度的中央区域,且P1 或P2 有一个≦48mil, 为最须LAY 锡偷的位置.(如图a)若无法LAY 连续长条的锡偷,则Pin 与Pin 的中心点必须LAY 满锡偷. (如图b)29 单排排针长边Layout 方向与PCI 长边平行.30 单排排针Drill/Pad 孔径Layout:大孔ψdrill / ψpad = 48 / 64 mil;31 锡面测试点的边缘距过板前方的大铜箔距离d 须≧60 mil.3233 若此零件各种sources 间尺寸差异太大,大小PADs 之间以绿漆分开(较佳选择),绿漆宽度W 须≧10 mil. 或Layout 成本垒板型式.34 未覆盖SOLDER MASK 的PTH 孔或VIA HOLE 边缘须与SMD PAD 边缘距离L ≧12 mil.Via Hole 不能落在PAD 内部.35 若此零件有多种sources, 则W,H , L max 选用所用sources 最大的值max(W,H , L max )代入(Equation 1)的X ,Y,R .363738若此零件有多种sources,则W , Z 选用所用sources 最大的值max(W , Z )代入(Equation 2)的X ,Y ,S .39 线圈的PAD 及零件文字框LAYOUT 尺寸如右图:40 ZIF 的游戏杆长方向与PCI 平行.41 ZIF 的摆设位置请勿摆在PCB 中央1/4 板长的区域.42 Through Hole 零件的与接大铜箔时, 须:✓锡面:PTH 可与邻近大铜箔相接.✓零件面及内层线路:法一:Thermal Relief 型式, PTH 与其余大铜箔不可完全相接, 需用PCB 基材隔开.法二:过锡炉前方(PTH 中心点的前180 度)的大铜箔可与PTH 直接相接; 过锡炉后方(PTH 中心点的后180 度)的大铜箔则不可与PTH 直接相接, 需间隔W ≧60 mil.43 若同一片板子有两种机种名称, 但其LAYOUT 皆相同, 为避免SMT 生产时混板, 须在某一角落的光学点, 用不同的喷锡样式辨别. 例如:✓OEM 客户: 用圆形喷锡(直径= 40 mil)光学点.✓用正方形喷锡(长*宽= 25*25 mil)光学点.Ps: 由于R&D在LAYOUT时不知道哪些机种会有不同名称, 故制造单位在生产时帮忙check, 反应时填写技术中心制订的”修改建议”表格, pass 给技术中心, 由技术中心跟LAYOUT 沟通修改. OEM 机种光学点修改必须经过业务同意.44 多联板CAD 文件排列顺序:✓单版排列编号采取逆时针方向, 并将第零片放置在左下角(由左而右, 由下而上).✓白点标示固在离第零片较远的板边上.45 大颗BGA(长*宽=35*35 mm)加Heat Sink 后, 附耳文字框宽W=274 mil, 附耳文字框长度L=2606 mil, 附耳底部零件限高H 须≦50 mil.46 所有零件文字框内缘须距”零件最大本体的最外缘或PAD 最外缘”≧10 mil; 亦即双边≧20 mil.零件公差:L +a/-b Lmax=L+a, Lmin=L-bW +c/-d Wmax=W+c, Wmin=W-d∴文字框Layout: 长≧Lmax+20, 宽≧Wmax+2047 若”零件最大本体的最外缘与PAD 最外缘”外形比例不符合,则零件文字框依两者最大值而变化.48 文字框线宽≧6 mil.49 SMD 零件极性标示:(1) QFP: 以第一pin 缺角表示.(图a)(2) SOIC: 以三角框表示. (图b)(3) 钽质电容: 以粗线标示在文字框的极性端. (图c)50 零件标示极性后文字框外缘不可互相接触、重迭.51 用来标示极性的文字框线宽≧12 mil.52 螺丝孔规格:✓Through Hole 为Non-PTH 孔.✓Non-PTH 孔Ring 周围均匀分布精灵孔.✓防焊漆在Component Side 全不覆盖.✓防焊漆在Solder Side 仅露出精灵孔吃锡, 其余覆盖防焊漆.53 当机种变更版本时, 其对角线之一个或二个光学点位置必须挪动, 其间距(a i ’,b I’)与前一版本(a i , b i)必须| a i-a i’ | ≧200 mil 或| b i-b i’ | ≧200 mil; 但若改版幅度不大时, 可在对角线光学点的其中一个旁标示直径100mil 的白点, 白点位置随版本变化而改变, 以利辨别.Ps. ai, ai’, bi, bi’ 定义请参阅附件一.54 ICT 测试点建议规范:✓尽量将所有测试点置于Solder Side.✓测试点应平均分布, 以防测试时板翘.✓测试点中心应距板边或V-CUT 折断边≧100 mil.✓Slot1, AGP 长边与邻近的电解电容垂直摆放.✓Slot1, AGP, Socket 7, Socket 370, IC 的文字框与邻近的电解电容须距L≧100 mil, 以防测试时Test Jet 及金手指撞击电解电容.55 BGA LAYOUT 如”PCB 基本规范”项次13 完成后, 除BGA PAD 外, 皆须加印白文字漆于绿漆上, 以防止绿漆覆盖VIA HOLES 不佳时而造成BGA 空焊, 并在BGA 本体外缘W = 30 mil 标示三角形极性.56 PCB 零件面上须印刷白色文字框, 此白框可摆在任何位置, 但不可被零件置件后压住, 其白框长L*宽W = 1654 *276 mil; 此文字框乃为Shop Flow 贴条形码,以利计算机化管理.57 PCB 背面上SMD 零件过DIP 制程,其制程吃锡较不易, 需有特殊PAD Layout,各类零件(Chip、IC、SOT、MELF) PAD 尺寸大小建议如下:零件摆设位置与过板方向关系如右图所示.58 过SMT 的零件, 其塑料材质的热变形温度(Td)须≧240℃, 或其塑料能承受Resistance to Soldering Heat 在240℃, 10 秒钟而不变形, 塑料材质如全部LCP、PPS, 及部份PCT、PA6T.但Nylon46 及Nylon66 含水率太高,不适合SMT reflow.59 零件的Shielding Plate 不可选用镀全锡.60 SMD 零件的包装须为(1)TAPE & REEL (2)硬TRAY 盘包装(3) Tube 包装,TAPE & REEL 为最佳选择, 包装规范请参阅”零件包装建议规范”.61 过DIP 零件的包装须为硬TRAY 盘包装, 或Tube 包装为最佳选择, 包装尺寸则无硬性规范. 其中DIMM, RIMM 及各式Slots 如有Board Lock 设计则必须以硬TRAY 盘包装.62 SMD TYPE 的Connectors,其零件塑料顶部正中央须有一平坦区域(贴上一平坦胶片)W*L 以利置件机吸取.,其面积建议如下(单位mm):(1) Y<5 且X<20:平坦区域面积W*L≧1.8*1.8.(2) Y<5 且X≧20:平坦区域面积W*L≧3*3.(3) 5≦Y<10:平坦区域面积W*L≧3*3.(4) Y≧10:平坦区域面积W*L≧6*6.(5) 贴胶片面积不可大于零件本体.63 PCB无防呆孔但Connector 却有极性要求, 其插入的DIP Connectors 须有一个定位防呆Post, 以防插件极反.64 若SMD Connector 有极性, 则在Connector 本体顶部标示极性.65 因SMT 机器高度限制,选用的SMD 零件其PCB 底部至零件顶部的最大高度H须≦13.5mm.66 于零件本体或Housing 打上厂商Logo.67 DIP Connector 其Board Lock 与PCB Through Hole 干涉量以8~10 mil 为最佳,且组装时须平稳顺畅,避免PCB 上其它零件跳脱.68 Through Hole 一般零件:1. StandOff Hc: Through Hole 零件其StandOff 高度Hc 须≧0.2 mm.2. StandOff 须置于Housing 周围,以便检查浮件问题.(图(b))3. Solder Tail 脚长Tc(图(c)):(1) 若min(Pr, Pc)<1mm 时, 则Tc= 2.3 +0.15/–0.10 mm.(2) 若min(Pr, Pc)=1mm 时, 则Tc= 2.6±0.2 mm.(3) 若min(Pr, Pc)>1mm 时, 则Tc= 2.9±0.3 mm.4. Kink 脚长Yc 须: Tc ≦Yc ≦3.6 mm. (图(a))Through Hole 特殊零件Solder Tail 脚长:✓Short Boby D-SUB 零件, Tc= 2.35 +0.15/–0.10 mm.✓Phone Jack, Tc= 3.0±0.2 mm.✓Game/Audio, Tc= 2.6±0.2mm5. 脚间距定义以减少Solder Bridge:(1) 3.2mm<Pr<4.2mm(2) 3.5mm<Pc<4.5mm如Pr Pc 不在此范围内需Layout 锡偷。

PCB设计CHECK LIST--修改版3

PCB CHECK LIST(讨论稿)一.布局方面:Check Approval□□ 1.产品外形尺寸,接口位置,安装孔的尺寸和位置符合要求(定位孔或非接地的安装孔需设置为非金属化孔)。

导线、功能焊盘应为圆角矩形,建议尺寸为2mm×3mm,在允许的情况下应采用双面焊盘,并用过孔(15mil)固定,且到板边的距离保持1mm以上。

□□ 2.元器件的摆放不重叠。

□□ 3.元器件的摆放不影响其他元器件的插拔和贴焊。

□□ 4.元器件的摆放应符合限高的要求,不会影响其他器件的贴焊和安装。

如电池盒下方,电池下方,背光板液晶下方等。

□□ 5.MARK点的位置摆放应符合要求:1、MARK点离板边及周围器件3mm 以上。

2、MARK点需放在PCB板对角位置。

3、单板上至少设置两个MARK点,若单板上无法放置MARK点,可在拼板或单板工艺边对角设置2个以上MARK点。

□□ 6.元器件离板边的距离应符合工艺要求:元器件焊盘到传送边的距离大于3mm,到非传送边的距离大于2mm。

□□ 7.体积大,间距小的元器件尽量放在元件面。

如果必须放在焊接面,其离板边的距离要大于等于7mm。

□□ 8.BGA和大于120PIN的QFP器件不能放在焊接面,BGA周围6mm以内不要有体积大插件或贴片器件,以免造成BGA返修困难□□ 9.有极性器件的摆放方向要尽可能一致。

□□ 10.相邻贴片器件的焊盘最少相距30mil。

BGA内部或背面密度大的地方可以放宽到25mil。

□□ 11.对于插拔时受力比较大的元器件,比如变压器引脚,热敏,压敏电阻的焊盘等,器件引脚直径与PCB 焊盘孔径及焊盘直径的对应□□插座)焊盘保持2mm以上,同时保持液晶(多PIN插座)引脚平行方向无器件阻挡,以利于焊接。

□□ 13.靠板边的热敏电阻或其他易倒伏器件,尽量放置于引线外围,以免造成加工不良□□ 14.与新结构配合的PCB要打印出1:1的图纸与结构比对,或者将PCB 转化为CAD支持的格式,请结构人员协助比对。

PCB layout_checklist

基板的安装孔、槽、边角区域等高应力区域,器件布置时应避免距离其过 近。 贴片的器件外形离定位边上定位孔的最小距离是否符合要求 贴片的器件外形或贴片焊盘间的最小距离(取两者中的最小者)是否满足 装配要求:普通装配,CHIP件间距≥0.5mm,CHIP与IC间距≥0.8mm;高密 装配,CHIP件间距≥0.3mm,CHIP与IC间距≥0.5mm 原件尺寸:高度≤6.5mm,特殊情况下允许≤9mm;原件封装:元件封装宽 度≤20mm,排阵及排母需有吸取盖(零件高度≤9mm); 贴片焊盘与贴片焊盘间或与插件焊盘间是否重叠设计,是否符合重叠设计 的要求 PCB焊盘上不可有过孔,焊盘须与原件匹配,不可存在焊盘与原件大小不 匹配的情况 BGA周围器件不可距BGA过近,不能布置较高高度的器件及吸热量过大的热 原件,且有利于贴装和返修。 确认卧插件的插入跨距合理,最小可插入跨距5mm,最大不超过20mm 确认竖插件的插入跨距是否为2.5mm或5.0mm,2.5mm跨距的插件是否有通 气孔 卧插件的插入孔之间的距离是否满足要求 竖插件的插入孔之间的距离是否满足要求 自插件的插入孔离两传送边的最小距离是否满足要求,距离定位边上的定 位孔的最小距离是否满足要求 自插件器件外形间及自插件与贴片元件的器件外形间至少保证0.5mm的距 离 自插件在波峰焊接面上的弯脚禁止区域是否重叠、干涉,波峰焊接面的贴 片焊盘不能进入弯脚禁止区域(特别是对插件三极管的检查)

预先考虑拼板方式拼板含工艺边最终尺寸在330长250宽范围内沿实装生产流向在pcb的正反面留5mm的传送边区域沿波峰焊方向在pcb的正反面是否留5mm的传送边区域非波峰焊接面允许保留4mm的传送边区域即可在非波峰焊接面pcb沿dip方向前端是否留有3mm的布局禁止区域在波峰焊接面是否预留4mm推荐5mm的波峰焊中线区域所有零件要离板边1

射频电路设计PCB审查checklist

【值得收藏】射频电路设计PCB审查checklist 2016-05-18硬件十万个为什么大小编下图所示为PCB 设计完成后的结构轮廓图:我们将布局成“U”形。

布局成U 形并不是不可以,但需要在中间加隔腔将其左右进行隔离,做好屏蔽。

还有一种在横向也需要添加隔腔。

即,用隔腔把一字形左右进行隔离。

这主要是因为需要隔离部分非常敏感或易干扰其它电路;另外,还有一种可能就是一字形输入端到输出端这段电路的增益过大,也需要用隔腔将其分开(若增益过大,腔体太大,可能会引起自激。

)。

B 芯片外围电路布局射频器件外围电路布局严格参照datasheet 上面的要求进行布局,受空间限制可以进行调整;数字芯片外围电路布局就不多讲了。

二、布线注意事项根据50 欧姆阻抗线宽进行布线,尽量从焊盘中心出线,线成直线,尽量走在表层。

在需要拐弯的地方做成45 度角或圆弧走线,推荐在电容或电阻两边进行拐弯。

如果遇到器件走线匹配要求的,请严格按照datasheet 上面的参考值长度走线。

比如,一个放大管与电容之间的走线长度(或电感之间的走线长度)要求等等。

在进行PCB 设计时,为了使高频电路板的设计更合理,抗干扰性能更好,应从以下几方面考虑(通用做法):(1)合理选择层数在PCB 设计中对高频电路板布线时,利用中间内层平面作为电源和地线层,可以起到屏蔽的作用,有效降低寄生电感、缩短信号线长度、降低信号间的交叉干扰。

(2)走线方式走线必须按照45°角拐弯或圆弧拐弯,这样可以减小高频信号的发射和相互之间的耦合。

(3)走线长度走线长度越短越好,两根线并行距离越短越好。

(4)过孔数量过孔数量越少越好。

(5)层间布线方向层间布线方向应该取垂直方向,就是顶层为水平方向,底层为垂直方向,这样可以减小信号间的干扰。

(6)敷铜增加接地的敷铜可以减小信号间的干扰。

(7)包地对重要的信号线进行包地处理,可以显著提高该信号的抗干扰能力,当然还可以对干扰源进行包地处理,使其不能干扰其他信号。

很全面的PCB_checklist_表格

85. 86. 87. 88. 89. 90. 91. 92. 93. 94. 95. 96. 97. 98. 99.

100.

101.

如果电源/地平面有分割,尽量避免分割开的参考平面上有高速信号的跨越。 确认电源、地能承载足够的电流。过孔数量是否满足承载要求,(估算方法:外层铜厚1o 线宽,短线电流加倍) 对于有特殊要求的电源,是否满足了压降的要求 为降低平面的边缘辐射效应,在电源层与地层间要尽量满足20H原则。(条件允许的话,电 如果存在地分割,分割的地是否不构成环路? 相邻层不同的电源平面是否避免了交叠放置? 保护地、-48V地及GND的隔离是否大于2mm? -48V地是否只是-48V的信号回流,没有汇接到其他地?如果做不到请在备注栏说明原因。 靠近带连接器面板处是否布10~20mm的保护地,并用双排交错孔将各层相连? 电源线与其他信号线间距是否距离满足安规要求? 金属壳体器件和散热器件下,不应有可能引起短路的走线、铜皮和过孔 安装螺钉或垫圈的周围不应有可能引起短路的走线、铜皮和过孔 设计要求中预留位置是否有走线 非金属化孔内层离线路及铜箔间距应大于0.5mm(20mil),外层0.3mm(12mil),单板起 间距应大于2mm(80mil) 铜皮和线到板边 推荐为大于2mm 最小为0.5mm 内层地层铜皮到板边 1 ~ 2 mm, 最小为0.5mm 对于两个焊盘安装的CHIP元件(0805及其以下封装),如电阻、电容,与其焊盘连接的印 称引出,且与焊盘连接的印制线必须具有一样的宽度,对于线宽小于0.3mm(12mil)的引出 与较宽印制线连接的焊盘,中间最好通过一段窄的印制线过渡?(0805及其以下封装) 线路应尽量从SOIC、PLCC、QFP、SOT等器件的焊盘的两端引出 器件位号是否遗漏,位置是否能正确标识器件 器件位号是否符合公司标准要求 确认器件的管脚排列顺序, 第1脚标志,器件的极性标志,连接器的方向标识的正确性 母板与子板的插板方向标识是否对应 背板是否正确标识了槽位名、槽位号、端口名称、护套方向 确认设计要求的丝印添加是否正确 确认已经放置有防静电和射频板标识(射频板使用) 确认PCB编码正确且符合公司规范 确认单板的PCB编码位置和层面正确(应该在A面左上方,丝印层) 确认背板的PCB编码位置和层面正确(应该在B右上方,外层铜箔面) 确认有条码激光打印白色丝印标示区 确认条码框下面没有连线和大于0.5mm导通孔 确认条码白色丝印区外20mm范围内不能有高度超过25mm的元器件 在回流焊面,过孔不能设计在焊盘上。(正常开窗的过孔与焊盘的间距应大于0.5mm (2 盘的间距应大于0.1 mm (4mil),方法:将Same Net DRC打开,查DRC,然后关闭Same N 过孔的排列不宜太密,避免引起电源、地平面大范围断裂

PCB布局,布线工艺审查Check List

3 7.9 细密间距引脚,0402贴片器件与传送边所在的板边距离要求大于10m.10 相邻插件元件本体之间的最小距离为0.5mm,焊盘之间的最小距离为1mm。

是[ ] 否[ ] 无[ ] 免[ ]

7.11

插装元器件以焊盘排列方向平行于波峰焊方向布局,连接器等多个引脚在一条直线 上的器件的轴线要求和波峰焊方向平行。

≤0.300g/mm2;J 形引脚器件:A≤0.200g/mm2;面阵列器件:A≤0.100g /mm2)

7.5 除结构有特殊要求之外,插件器件是否布局在PCB板的同一面,避免双面布局插件器 是[ ] 否[ ] 无[ ] 免[ ] 件。

7.6 不同属性的金属件或金属壳体的器件不能相碰。确保最小1.0mm的距离满足安装要求。是[ ] 否[ ] 无[ ] 免[ ]

是[ ] 否[ ] 无[ ] 免[ ]

1.3 PCB走线时,应做到横平竖直,斜线按45度角走线,拐弯,连接处避免产生尖角。 是[ ] 否[ ] 无[ ] 免[ ]

1.4

走线不能覆盖焊盘,应从焊盘末端引线;密间距的SMT焊盘(间距小于0.65mm)引脚 需要连接时,应从焊盘外部连接,不容许在焊脚中间直接连接。

是[ ] 否[ ] 无[ ] 免[ ]

1.5

片式元件走线和焊盘连接要避免不对称走线,IC元器件引脚的出线应从焊盘端面中心 位置引出。

是[ ] 否[ ] 无[ ] 免[ ]

1

布线设计

1.6

1OZ铜厚的PCB:线宽要求≥4mil,外层线间距≥5mil,内层线间距≥4mil;2OZ铜厚 的PCB:线宽≥6mil,线间距≥6mil。

是[ ] 否[ ] 无[ ] 免[ ]

1.7 对于防腐蚀要求高的PCB,细密线路要求设计到PCB板底面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.4.12

4.4.13

4.4.ห้องสมุดไป่ตู้4

Critical TRACE(连接CLK的TRACE)以最短原则设计 Critical TRACE(连接CLK的TRACE)间距离是否尽可能远(最小为线 边到线边距离的三倍) Critical TRACE(连接CLK的TRACE)如为ANALOG TRACE ,要加上 GUARD LINE(屏蔽线) 先设计Critical TRACE(时钟信号线),再布其它线 在ANALOG PAD处是否有引线(不应有引线,否则会把ANALOG PAD的 GROUND RING 割破) ANALOG PAD在TESTER SIDE时,是否把线布在DEVICE SIDE。(应该布 在DEVICE SIDE ) TRANSISTORS(三极管),不要把BASE(基极)的连线走在EMITTER和 COLLECT之间 OP AMP(放大器)输入线必须很短,一对输入线等长 所有反馈(OUTPUT TO INPUT)元件,必须放近OP AMP(放大器), 连线越短越好 OP AMP 的输入线路要远离输出线路 线尽可能不要走入孔的Clearance范围以内(如很难避免时,设计前 一定要通知主管) 其他 DRC检查 最小间距检查 PAD与线的SPACING:最小要5mil(最好把线与SPACING平分三等份 PAD与PAD的SPACING:最小要8mil 线共GND PLANE的距离为15mil(此种情况只会发生于COMPOSITE GND,走线与GND在同一层) 线到孔的距离≥20mil Minimum Spacing: Surface Layers: 7mil Inner Laywes: 4Layer Board: 11mil 6/8 Layer Board: 13mil 10/12 Layer Board: 14mil 与电原理图网络匹配检查 元件焊盘过孔尺寸检查 板厚度≤125mil时,VIA孔(过孔)为25mil 板厚度>125mil时,VIA孔(过孔)为32mil 对于长方形的PAD ,长的每边15mil ,短的每边有4mil Via Hole 尺寸为20mil POWER 及 GROUND ACCESS 为32mil GRID HOLE及其他ACCESS为45mil GUIDE PIN HOLE(非镀通孔) 如图纸有提供HOLE SIZE ,按图纸做 如图纸提供是PIN SIZE ,HOLE SIZE 等于PIN SIZE(对角线或直 径)加4mil 螺丝及COUNTERSINK 请参考螺丝与孔对照表,表上列出为孔的大小 VIA 孔的ANNULAR RING 每边为5mil 螺丝孔的ANNULAR RING,PAD的大小为孔的两倍 BGA SOCKET(POGO PAD TYPE) VIA HOLE :0.25mm(10mil ,当板的厚度小于或等于0.125”时) 0.30mm(12mil,当板的厚度大于0.125”时) BGA SOCKET(POGO PAD TYPE) Annular Ring:最小要3mil(最好做5mil) PAD与线的SPACING:最小要5mil(最好把线与SPACING平分成三等 份) PAD与PAD的SPACING:最小要8mil BGA SOCKET(Through Hole TYPE) Hole size:1.27mm pitch 用0.5mm(20mil) 1.00mm pitch 用0.35mm(14mil) BGA SOCKET(Through Hole TYPE) Annular Ring:先做长圆PAD,长的两边做0.008”,短的两边做 0.005” 做不到两边就做一边长PAD,再不成就做圆PAD,但最小要做5mil PAD与线的SPACING:最小要0.005mil(最好把线与SPACNG平分成三等 份)

2.45 3 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 3.10 3.11 3.12 3.13 3.14 3.15 3.16 3.17 3.18 3.19 3.20 3.21 3.22 3.23 3.24 3.25 3.26 3.27 3.28 3.29 3.30 3.31 3.32 3.33 3.34 3.35 3.36 3.37 3.38 3.39 3.40 3.41 3.42 3.43 3.44 3.45 3.46 3.47 3.48 3.49 3.50 3.51 3.52

PCBA Checklist

序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 编号 1 1.1 1.2 1.3 1.4 1.5 2 2.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 2.9 2.10 2.11 2.12 2.13 2.14 2.15 2.16 2.17 2.18 2.19 2.20 2.21 2.22 2.23 2.24 2.25 2.26 2.27 2.28 2.29 2.30 2.31 2.32 2.33 2.34 2.35 2.36 2.37 2.38 2.39 2.40 2.41 2.42 2.43 2.44 检查项目说明 硬件设计要求 独立功能模块是否用框线和名称标示 IC等器件退耦电容归属是否明确 单板功能方框图已提供 重要信号已单独标示 PCB设计的特殊要求已单独说明 封装与布局 所有器件封装已是最新版本,并与实物保持一致(硬件设计者与实物 核对封装) 所有器件已经放置到板面 整体布局参照原理功能框图,兼顾美观及电源、地的分割 高、中、低频电路分开 数字电路与模拟电路分开放置 高温、发热器件远离其他器件放置 退耦电容靠近相关器件放置 晶体、晶振靠近相关器件放置,多负载时应平衡放置 打印1:1的布局图,器件封装、布局经过硬件工程师确认 普通板有大于3mm工艺边 器件布局间距,IC大于2mm、BGA大于5mm;特殊情况可适当调整。但 保证IC大于1mm,BGA大于3mm 压接件距其他器件大于5mm,焊接面压接件贯通区域无任何器件 有极性插装器件第一脚为方焊盘 坐标原点为板框左、下延伸线交点 板外框平滑弧度5mm,或者按结构尺寸图设计 高度≥10mm器件周围3mm内不能放置贴片器件(矮、小器件) 双列封装数字集成电路有1个或以上滤波电容 QFP、BGA、PLCC、模拟IC等器件有2个或以上滤波电容 含贴片器件的PCB,贴片器件所在面的板任选2角各放置一个定位光标 MOUNTING孔(安装孔)是否镀铜(要镀铜) GUIDE PIN孔(定位孔)是否没镀铜(除另有说明,不要镀铜) 元器件的1脚是否为方PAD POWER PLANE 分割时是否出现瓶颈 BGA SOCKET 相同的POWER PIN 是否连接起来 BGA SOCKET相同的GND PIN 是否连接起来 BGA SOCKET的四圈及四角,是否加上DECOUBLING CAP 的PATTERN 是否在板上形成了一圈POWER RING(永不要在板上形成了一圈POWER RING,否则会产生电磁噪音,可把POWER RING 割成两个半圈 ) 在SMA区内,是否有POWER PLANE(不应有) GROUND PLANE上是否走线(不可以走线) 在GROUND PLANE 上是否出现island(不可以) 在POWER PLANE 上是否出现island(不可以) 在SOCKET中央是否提供FLOATING METAL RING(电源圈和GND圈)或 STIP条(电源条和GND条) ANALOG PAD是否有GROUND RING 去耦电容是否距离对应POWER PIN 够近(越近越好) 板上Analog区与Digital区是否隔开 每一层的ANALOG区与DIGITAL区的大小、形状是否完全一样 ANALOG TRACE 下层的GROUND PLANE为ANALOG GROUND DIGITAL TRACE 下层的GROUND PLANE为DIGITAL GROUND ANALOG POWER PIN的去耦电容必须接ANALOG GROUND DIGITAL POWER PIN 的去耦电容必须接DIGITAL GROUND 继电器为尾对尾相对或互相垂直(绝对不可平行放) 线圈式电容最外的圈接地 LEAD式电容,不要把2个电容的POWER脚放在一起 所有反馈(OUTPUT TO INPUT)元件,必须放近OP AMP(放大器), 连线越短越好 检查结果 是 否 NA 备注 (不符合项需要说 明)

106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156

52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105

3.53 3.54 3.55 3.56 3.57 3.58 3.59 3.60 3.61 3.62 3.63 4 4.1 4.2 4.2.1 4.2.2 4.2.3

4.2.4

4.3 4.4 4.4.1 4.4.2 4.4.3 4.4.4 4.4.5 4.4.6 4.4.7

4.4.8 4.4.9 4.4.10 4.4.11

去耦电容必须非常接近OP AMP 的POWER PIN(例如线路有电阻,电容 必须优先于电阻放近POWER PIN) 布线 相邻层布线方向定义互为垂直;如不可避免平行,则两层的走线不可 完全重叠 非差分信号平行布线长度≤2000mil 线间距≥6mil,线宽≥5mil 电压大于5V的分割区分割线宽为50mil,5V及以下的分割线宽≥25mil 普通板板边沿禁止布线区3mm 没有锐角和90布线 高速信号线、时钟信号线遵循回路面积最小原则 总体布线均匀,布线尽可能短,且少过孔 布线线宽保持一致,没有跳变 差分信号平行布线、等长 接插件管脚间的布线≤500mil 高频、高速、时钟等重要信号与地平面相邻 没有开路线 布线在空间没有形成闭环 布线长度最短 电源和高热器件,安装面没有其他布线穿越 卧装TO220封装三极管下,铺铜箔、开阻焊窗 屏蔽盒、屏蔽线连接到对应的地网络 所有网络已完成布线 定位光标设置正确 色码电阻、电感下没有过孔 焊接面贴片电阻、电容、电感焊盘间区域没有过孔 没有孤立铜箔区 保证分割区的连续性 开窗有明确标注 没有封闭尺寸 标注单位一致,与缺省单位不一致时自带单位 安装孔位置有标注 尺寸标注误差≤3mil 板框倒角有标注 过孔设置正确 母板过孔为VIA40、VIA24、VIA16、VIA12,单板过孔为VIA24、VIA20 、VIA16、VIA12、VIA8、 VIA16 没有过孔上焊盘 过孔间距≥8mil 过孔与焊盘间距≥10mil 铺铜箔区域,铜箔与过孔间距≥15mil 多排连接器内部没有过孔 板上有独立的地测试孔 丝印未上焊盘 母板正反两面都有丝印标示(板名、单板插座名称) 丝印方向为从左到右、或者从下到上 板名、板本号已有 丝印归属明确,无歧义 主要供电电源,根据电流大小加粗走线,保证供电 外部电源供电的电源插座位置靠近外部电源放置 单板上已经放置了条形码丝印和防静电标识 线连到大PAD时,大PAD做成TEAR DROP形 元器件下不要走线(包括SOLDSIDE和COMP SIDE)(1.空间很小时, 继电器下可走线 ;2. CLK线、ANALOG线不要从元器件下走线 ;3. 尽可能避免从电容下走线) 线与元件PIN距离是否≥100 mil 线距小于10mil时,平行长度是否超过1寸(不可以超过1寸) 两个PAD或孔中间的线是否放中央 当一线连接A、B、C、D点时,连接方法为DAISY CHAIN(串联)例如A —B—C—D……