超标量流水线

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PPT第二张

超标量流水线思想:多条流水线并行工作,提高指令级并行度。

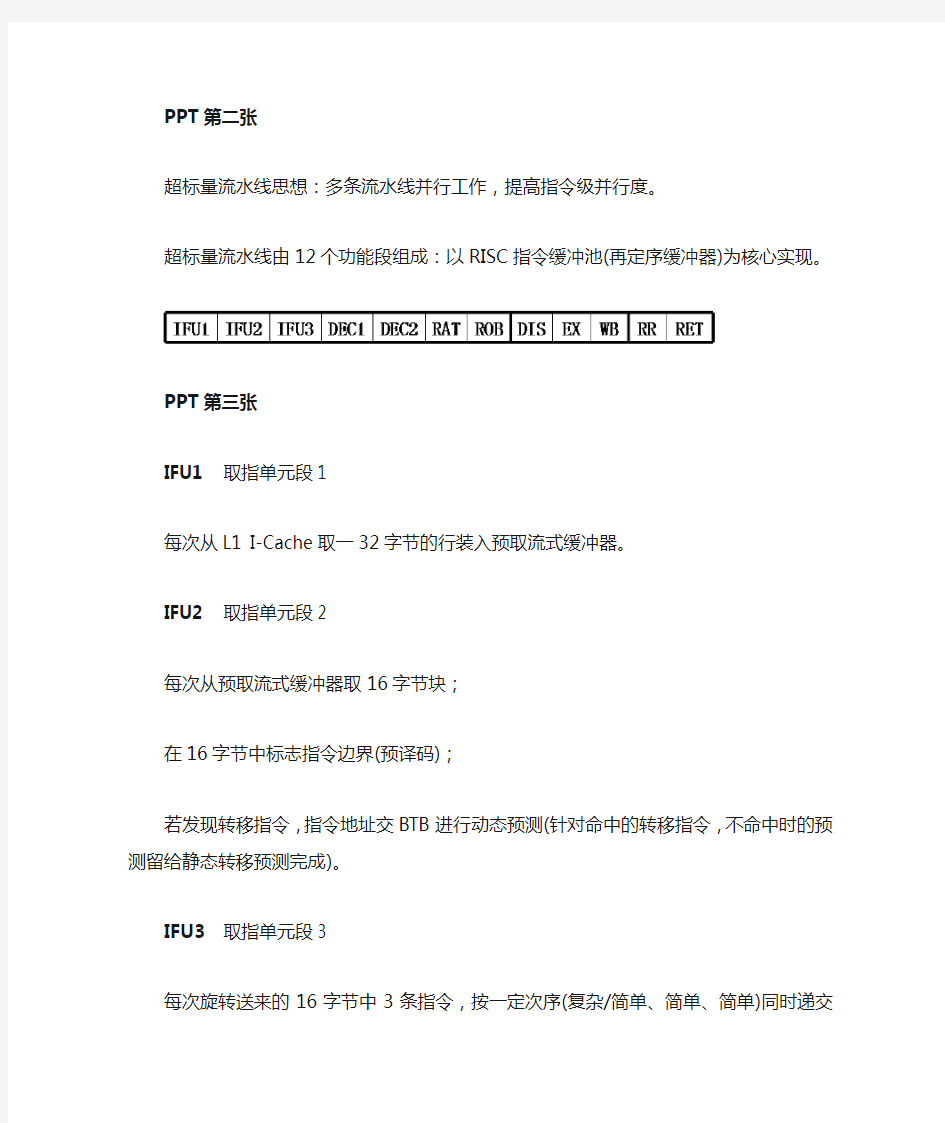

超标量流水线由12个功能段组成:以RISC指令缓冲池(再定序缓冲器)为核心实现。

PPT第三张

IFU1 取指单元段1

每次从L1 I-Cache取一32字节的行装入预取流式缓冲器。

IFU2 取指单元段2

每次从预取流式缓冲器取16字节块;

在16字节中标志指令边界(预译码);

若发现转移指令,指令地址交BTB进行动态预测(针对命中的转移指令,不命中时的预测留给静态转移预测完成)。

IFU3取指单元段3

每次旋转送来的16字节中3条指令,按一定次序(复杂/简单、简单、简单)同时递交给DEC1。

取指段特征:各段不按时钟动作,而是需要时产生动作;指令按序流动。

DEC1 译码段1

每次3个译码器同时可将3条IA指令译码成最多6个RISC的微操作(μop);微操作翻造由MIS实现。

DEC2 译码段2

每次最多接收6个μop,并按原始程序顺序排成队列;

若μop为转移型且BTB未命中(BTB未处理),则交静态转移预测机构(替换/生成BTB 项、预测转移方向)。

静态预测转移规则:

对转移地址非相对PC方式,属返回/调用指令的预测转移,否则不转移;

对转移地址是相对PC,地址增加的预测不转移,否则转移。

RAT 寄存器重命名和分配段(按序发射)

每时钟取3个μop,检查是否使用IA寄存器,若有则转为内部寄存器(ROB项的值域段,又称别名寄存器),然后将3个μop送ROB。

此段消除了绝大多数RAW、W AW、W AR数据相关。

ROB再定序缓冲器段

ROB(有40个项的环形缓冲器)接收μop;

负责管理每项的各种标志位(如是否已到保存站等)。

译码段特征:CISC→RISC,指令按序流动,

需要时动作→按时钟发射。

DIS派遣段(保存站RS实现)

RS能以任意顺序从ROB拷贝μop到相应端口;

RS从端口调度到ALU的原则是操作数已就绪(已排除RAW相关)且执行单元可用(指令执行完时);

对MEM的读、写的动态MEM地址判别在DIS段实现。

EX 执行段(各功能部件实现)

执行μop,结果经CDB返回ROB;

MEM写将产生两个μop,写地址μop即建立SDB项;

若μop是转移指令,则结果同时返回BTB(更新/猜错)和ROB。

WB 写回段

μop执行结果写回或L1 D-Cache数据读入ROB,并进行错误检查和修正,同时将结果或数据送到RS。

执行段特征:乱序流动、并行执行,EX部件可不同时长。

RR 回收就绪段(确认段)

每时钟回收3个μop;

按程序顺序以IA指令为单位,对μop进行确认,可消除W AW、W AR相关;

对分支和异常的确认处理可能需清除部分或全部ROB。

RET 回收段

按程序顺序以IA指令为单位,将回收就绪的IA指令对应结果写回IA寄存器及设置EFLAGS标志;通知MOB将相应结果写入L1的D-Cache,ROB中清除IA指令对应的μop。

回收段特征:RISC→CISC,按序回收。

PPT第四张

软硬件实现:

超标量机要求相同操作的指令能够相对均匀地分布在程序中,避免发生资源冲突,硬件方面通过内置多条流水线来同时执行多个处理器,其实质是以空间换取时间。主要是以避免、消除相关为主

PPT第五张

优点:与一般的流水机器相比,超标量处理器的特点主要表现在:

(1)配置有多个性能不同的处理部件,采用多条流水线并行处理。

(2)能同时对若干条指令进行译码,将可并行执行的指令送往不同的执行部件,从而达到在每个时钟周期启动多条指令的目的。

(3)在程序运行期间由硬件(通常是状态记录部件和调度部件)完成指令调度。

PPT第六张

缺点:相应的硬件较为复杂

相同操作的指令序列连续出现时,会发生资源冲突

指令级并行性自身存在很大限制

PPT第七张

第一个超标量的设计是在1965年Seymour Cray开发的CDC 6600。1988 年的Intel i960CA 与1990 的AMD 29050处理器是第一个量产的单晶粒超标量处理器。这些RISC系统的CPU 使用超标量架构,是由于当时RISC的设计的核心较简单,能够直接发送指令与调度多种功能性的单位(像是ALU)。这也是在八、九十年代RISC处理器比CISC处理器的运算速度更快的主要原因。

除了那些低功率CPU、嵌入式CPU、以及使用电池电源的CPU,1998年以后开发的CPU设计都已经是超标量体系结构。第一种采用了超标量技术的X86处理器是Pentium。第一批采用了把CISC指令异步解码为微指令序列技术的处理器是Nx586, P6体系结构的Pentium Pro 以及AMD K5。这使得被缓存的微指令可以动态调度(dynamic scheduling)执行,使得P6架构的并行性更优于P5架构的Pentium; 这也使得预测执行(speculative execution)更易实现,CPU的时钟频率也可以更高。