可逆计数器设计报告

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、题目(二)2、加/减可逆计数器

二、要求:.设计一个4位二进制加/减可逆计数器。控制信号为1时,加计数;0时,减计数。要求写出Verilog代码,给出仿真波形(能反映出所有工作状态)。

三、思路方法:

题目要求的计数器是一个带有低电平负载和清零输入端的同步4位二进制计数器。内部应该像‘163一样采用D触发器而非T触发器,这样便于实现载入和清零功能。每个D触发器的输入由一个2输入多路复用器驱动,这个复用器由1个或门和2个与门构成。如果输入信号CLR_L有效,多路复用器的输出就为0。反之,如果输入信号LD_L有效,上面那个与门就把输入数据传送到输出端。如果CLR_L和LD_L都无效,下面的与门就把”异-或-非”门(XNOR)的输出传送到多路复用器的输出端。

它的二进制计数顺序既可以按升序进行也可以按降序进行,由输入信号UP/DN的值来控制。当UP/DN为1时,按升序计数;当UP/DN为0时,按降序计数。

四、仿真结果及分析

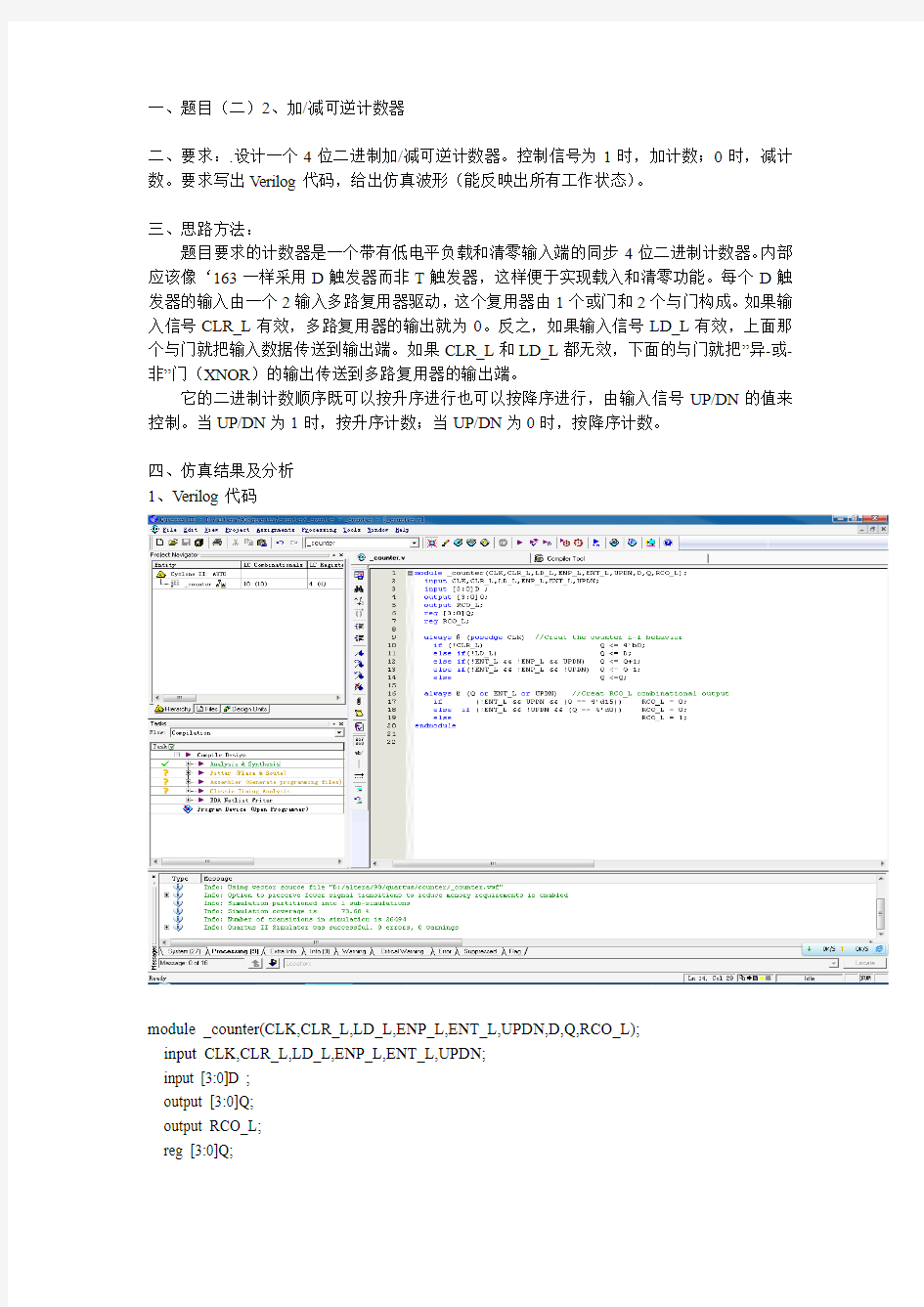

1、Verilog代码

module _counter(CLK,CLR_L,LD_L,ENP_L,ENT_L,UPDN,D,Q,RCO_L);

input CLK,CLR_L,LD_L,ENP_L,ENT_L,UPDN;

input [3:0]D ;

output [3:0]Q;

output RCO_L;

reg [3:0]Q;

reg RCO_L;

always @ (posedge CLK) //Creat the counter f-f behavior

if (!CLR_L) Q <= 4'b0;

else if(!LD_L) Q <= D;

else if(!ENT_L && !ENP_L && UPDN) Q <= Q+1;

else if(!ENT_L && !ENP_L && !UPDN) Q <= Q-1;

else Q <=Q;

always @ (Q or ENT_L or UPDN) //Creat RCO_L combinational output

if (!ENT_L && UPDN && (Q == 4'd15)) RCO_L = 0;

else if (!ENT_L && !UPDN && (Q == 4'd0)) RCO_L = 0;

else RCO_L = 1;

endmodule

2、所有功能的仿真结果

(1)加计数:计数器工作再自由计数模式且UPDN=1,计数器从0000加计数到1111时,RCO_L输出一个周期的低电平,然后计数器跳回0000重新开始计数。

结果分析:从仿真图中可以看到,Q从0000计数到1111然后跳回0000重新开始计数,满足计数要求。

(2)减计数:计数器工作再自由计数模式且UPDN=0,计数器从1111减计数到0000时,RCO_L输出一个周期的低电平,然后计数器跳回1111重新开始计数。

结果分析:从仿真图中可以看到,Q从1111计数到0000然后跳回1111重新开始计数,满足计数要求。

(3)清零:当CLR_L=0,计数器清零,输出为Q=0000。

结果分析:从仿真图可以看到,当CLR_L=0时,Q=0000,满足设计要求。

(4)置数:当LD_L=0时,计数器置数,Q=D。

结果分析:从仿真图可以看到,输出端D=0111,输出Q=0111,满足设计要求。

五、实验总结

通过Verilog硬件描述语言,设计了4位二进制加/减计数器,计数器有加计数、减计数、清零和置数的功能,且所有的这些设计功能都通过了仿真分析,符合设计要求。通过本次实验,学会了Quartus设计数字电路的一般方法和仿真方法,并且在实验中加深了对理论知识的理解。