基于FPGA的QPSK调制解调器的设计

基于FPGA的QPSK OFDM调制解调器设计与实现

基于FPGA的QPSK OFDM调制解调器设计与实现OFDM(正交频分多路复用)是一种高效的调制解调技术,常用于无线通信系统中。

本文将介绍基于FPGA的QPSK(四相移键控)OFDM调制解调器的设计与实现。

一、引言OFDM技术在无线通信领域有着广泛的应用,其通过将高速数据流分成多个低速子载波进行传输,有效提高了系统的传输效率和频谱利用率。

而QPSK调制方式在OFDM系统中常被使用,能够传输两个比特的信息。

二、系统设计1. 系统框架基于FPGA的QPSK OFDM调制解调器主要包括信号生成、调制、多载波复用、通道传输、接收、解调等模块。

其中,信号生成模块负责产生待发送的信息信号;调制模块将信息信号进行QPSK调制;多载波复用模块将调制后的信号进行串行-并行转换;通道传输模块将并行数据通过多个子载波进行传输;接收模块接收并处理接收到的信号;解调模块将接收到的信号进行QPSK解调,得到原始信息信号。

2. 信号生成在信号生成模块中,我们可以使用伪随机序列发生器生成随机的数字信号作为待发送的信息源。

这里我们选择使用16位的二进制数字信号。

3. QPSK调制QPSK调制模块将二进制信号映射到复平面上的四个相位,即正弦信号与余弦信号共同构成的星座图。

通过将两个比特的输入分别映射到正弦信号与余弦信号的相位上,得到QPSK调制信号。

4. 多载波复用多载波复用模块将QPSK调制信号进行串行-并行转换,将多个并行的调制信号通过并行数据总线发送到通道传输模块。

5. 通道传输通道传输模块将并行的调制信号通过多个子载波进行传输。

在传输过程中,可能会出现信道衰落、噪声等问题,需要引入信道估计和均衡技术进行处理。

6. 接收与解调接收模块接收到经过信道传输后的信号,并进行信道估计和均衡处理,将接收到的信号进行QPSK解调,得到原始的二进制信息。

三、系统实现本文使用基于FPGA的开发板进行系统的实现。

通过使用硬件描述语言进行电路的设计,将各个模块进行逻辑连接,实现QPSK OFDM 调制解调器的功能。

基于FPGA的QPSK系统设计

目录摘要:本文 (1)关键字: (2)1设计分析 (2)1.1设计目的 (2)1.2 设计任务与要求 (2)1.3 设计原理分析 (3)2系统控制器模块分析 (3)2.1 VHDL简介 (3)2.1.1VHDL具有以下特点: (3)2.1.1.1功能强大、设计灵活 (3)2.1.1.2支持广泛、易于修改 (4)2.1.1 .3强大的系统硬件描述能力 (4)2.1.1.4独立于器件的设计、与工艺无关 (4)2.1.1.5很强的移植能力 (4)2.1.1.6编辑本段优势 (4)2.2 FPGA简介 (5)2.2.1FPGA工作原理 (5)2.2.2FPGA芯片结构 (6)2.2.3基本特点 (7)2.3 QPSK简介 (8)2.3.1QPSK正交调制器原理图 (8)2.3.2QPSK相干解调原理图 (9)2.4 QPSK调制电路的FPGA实现及仿真 (9)2.4.1 基于FPGA的QPSK调制电路方框图 (9)24.2 调制电路VHDL程序及仿真结果 (10)2.5 QPSK解调电路的FPGA实现及仿真 (12)2.5.1 基于FPGA的QPSK解调电路方框图 (12)2.5.2解调电路VHDL程序及仿真结果 (12)3结论 (15)4参考文献 (16)摘要:本文采用FPGA设计芯片技术对多进制数字通信技术的QPSK调制器实现进行了研究与分析,将调制器中原有多种专用芯片的功能集成在一片大规模可编程逻辑器件FPGA芯片上,实现了高度集成化、小型化、实际研究仿真表明,该方案具有突出的灵活性和高效性,为设计者提供了多种可自由选择的设计方法和工具。

关键字:FPGA、QPSK、数字通信随着电子技术的不断发展与进步,电子设计系统设计方法发生了很大的变化,传统的设计方法正在退出历史的舞台,而基于EDA技术的芯片设计正在成为电子系统设计的主流。

随着现代信息技术的发展,模拟调制技术越来越不能满足日益发展的移动通信、视频信号传输以及卫星通信的要求,数字调制技术日益得到重视。

如何实现一种基于FPGA全数字高码率QPSK调制设计?

如何实现一种基于FPGA全数字高码率QPSK调制设计?1 ** 全数字高码率QPSK调制解调软件设计**1.1 QPSK调制1.1.1 QPSK调制原理1.1.2 QPSK并行调制实现调制(信号)的符号速率达到500Mbps,根据奈奎斯特采样定理,DA的采样频率采用2Gbps。

由于数据速率比较的高,对(FPGA)运算要求太高,因此在设计过程中,采用并行处理的方式,来减轻对FPGA运算的压力。

图1-1为高码率500M QPSK调制实现框图。

其实现的原理为将二进制数据流经过QPSK映射后形成I、Q两路基带信号,在经过8倍成型(滤波器)后,分别与两路正交的数字本振混频后相加输出至(DAC)即可。

图1-1 并行QPSK调制实现框图1.1.2.1 QPSK符号映射QPSK信号的每个码元包含两个比特(信息),可用ab表示。

ab 序列有四种排列,即00,01,10,11。

每种排列对应4种不同的调制相位。

通常各种排列的相位关系按照格雷码进行编码,其符号映射关系如图1-2所示。

图1-2 QPSK映射星座图在实现过程中,将每个符号所包含的两比特二进制信息,分别对应为I、Q两路,先到的信息比特映射为I路,后到的信息比特映射为Q路。

其中二进制0对应正值(逻辑高+1),二进制1对应负值(逻辑低-1)。

图1-3为500Mbps QPSK调制(MATLAB)(仿真)映射星座图,从图中可以看出基带数据严格聚集在[-1,-1],[-1,1],[1,-1],[1,1]四个相位点上。

图1-3 500MbpsQPSK调制MATLAB仿真映射星座图1.1.2.2数字基带成型滤波由于现代无线电(通信)及卫星通信中,频带和功率一般均受限。

一方面,为了有效利用信道,节约频谱资源,需要对发射信号进行带限;另一方面,当矩形脉冲通过带限信道时,脉冲会在时间上扩展,每个符号的脉冲将扩展到相邻符号的码元内,这会造成码间串扰(ISI),并导致接收机在(检测)码元时发生错误的概率增大。

基于FPGA的QPSK解调技术的设计与实现的开题报告

基于FPGA的QPSK解调技术的设计与实现的开题报告一、选题背景及意义随着现代通信技术的发展,频谱资源越来越紧张,为提高频谱利用效率,射频通信系统中使用数字调制技术是一种可有效降低带宽能量占用和提高信道容量的方式。

其中一种常用的数字调制技术是QPSK调制,它可以将两路单极性NRZ数据分别调制在正弦波和余弦波载波上,实现带宽利用率的提高。

在接收端,解调器需要对QPSK调制信号进行还原,提取出原始的信息数据。

因此,本课题选取了基于FPGA的QPSK解调技术的设计与实现作为研究方向,旨在探索一种高效实现数字信号解调的方法,为提高现代通信技术的发展水平做出贡献。

二、研究内容1. 系统总体设计本课题设计的QPSK解调系统包括射频前端的载频同步、时序同步、均衡、解调等模块,还包括数字信号处理相关的滤波器、采样率变换等模块。

通过这些模块的协同作用,将接收到的QPSK调制信号解调还原成原始的数字信号数据流。

2. 载频同步模块该模块负责完成载频的同步,用于去除接收端的时移影响和相位偏差。

常用的载频同步算法有Costas算法、DDS算法、ZT算法等。

3. 时序同步模块该模块用于解决接收数据中时序抖动的问题,采用软判决算法实现。

4. 均衡模块该模块用于抑制信道传输时产生的干扰,提高系统的抗干扰性能。

常用的均衡算法有线性均衡算法、决策反馈均衡算法等。

5. 解调模块该模块用于将QPSK调制信号还原成原始数字信号。

该模块通常包括滤波器、采样率变换器等子模块。

三、研究计划第一年:我们将完成系统的总体设计,并完成载频同步模块和时序同步模块的算法研究和验证。

同时进行硬件平台的搭建和仿真测试。

第二年:我们计划完成均衡模块和解调模块的算法研究和验证,并将这些模块集成到硬件平台上。

在验证完成后,完善系统的功能和性能,并进行实际场景测试。

第三年:在系统的测试和实际应用中不断完善和优化,提高系统的性能和稳定性,并探索将该技术应用到更广泛领域的可能性,为现代通信技术的发展做出更大的贡献。

基于FPGA的QPSK高速数字调制系统的研究与实现

基于FPGA的QPSK高速数字调制系统的研究与实现摘要:介绍了一种基于FPGA的QPSK的高速数字调制系统的实现方案。

先从调制系统的基本框图入手,简要介绍其实现原理及流程;然后着重介绍FPGA功能模块的软件编程、优化及整个系统的性能。

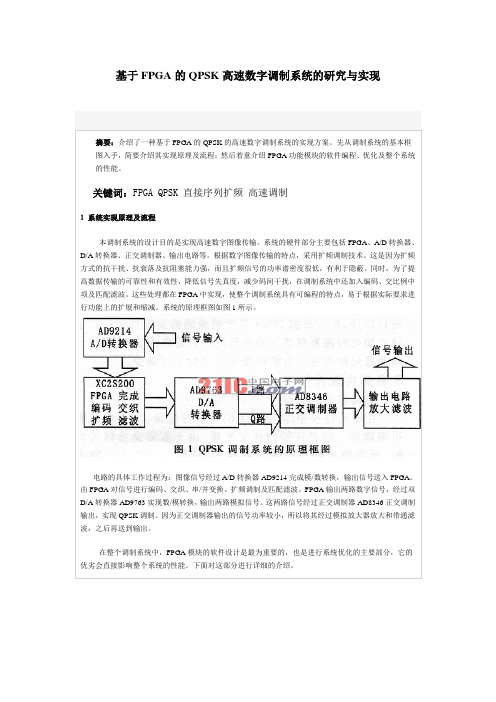

关键词:FPGA QPSK 直接序列扩频高速调制1 系统实现原理及流程本调制系统的设计目的是实现高速数字图像传输。

系统的硬件部分主要包括FPGA、A/D转换器、D/A转换器、正交调制器、输出电路等。

根据数字图像传输的特点,采用扩频调制技术。

这是因为扩频方式的抗干扰、抗衰落及抗阻塞能力强,而且扩频信号的功率谱密度很低,有利于隐蔽。

同时,为了提高数据传输的可靠性和有效性,降低信号失真度,减少码间干扰,在调制系统中还加入编码、交比例中项及匹配滤波。

这些处理都在FPGA中实现,使整个调制系统具有可编程的特点,易于根据实际要求进行功能上的扩展和缩减。

系统的原理框图如图1所示。

电路的具体工作过程为:图像信号经过A/D转换器AD9214完成模/数转换,输出信号送入FPGA。

由FPGA对信号进行编码、交织、串/并变换、扩频调制及匹配滤波。

FPGA输出两路数字信号,经过双D/A转换器AD9763实现数/模转换,输出两路模拟信号。

这两路信号经过正交调制器AD8346正交调制输出,实现QPSK调制。

因为正交调制器输出的信号功率较小,所以将其经过模拟放大器放大和带通滤波,之后再送到输出。

在整个调制系统中,FPGA模块的软件设计是最为重要的,也是进行系统优化的主要部分,它的优劣会直接影响整个系统的性能。

下面对这部分进行详细的介绍。

2 软件部分实现原理FPGA模块的软件设计部分包括以下几个方面:编码、交织、串并变换、扩频、匹配滤波以及复位和时钟。

2.1 编码和交织数字通信中经常使用信道编码加交织模块来提高数据传输的可靠性和有效性。

为了达到一定的增益要求,选择卷积码中纯编码增益为3.01的(1,1,6)码(在大信噪比下),并对其进行增信删余。

QPSK调制解调技术的设计与仿真

摘要本文主要阐述的是QPSK调制与解调电路的设计。

数字调制解调技术在数字通信中占有非常重要的地位。

为了使数字信号在带通信道中传输,必须用数字信号对载波进行调制。

根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制)。

多进制数字调制与二进制相比,其频谱利用率更高,在有限的信道频带内,能够传输高速数据。

数字通信技术与FPGA的结合是现代通信系统发展的一个必然趋势。

多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。

文中介绍了QPSK调制解调的原理,并基于FPGA实现了QPSK调制解调电路。

MUXPLUSⅡ环境下进行编译、综合仿真,验证了设计的正确性。

此外,本方案采用了相位选择法,与常用的调相解调法相比,设计更简单,更适合于FPGA实现,系统的可靠性也更高。

通过对仿真波形的分析可知,该方案很好的实现了QPSK调制与解调功能。

关键词:PSK FPGA QPSK调制解调AbstractThis article mainly deals with the design of QPSK modulation and demodulation circuit. Technology of digital modulation and demodulation plays an important role in digital communication system.In order to transmit digital signal in band-pass channel,digital signal must be used on the carrier modulation..According to the different bands of digital signal that is handled,there are binary and multi-band pared with binary modulation ,multi-band modulation has higher specrum utilization rate,and it could transmit high-speed data in limited-band channel.The combination of digital communication technology and FPGA is a certainly trend of the development of modern communication system.The combination of multi-band modulation and FPGA makes the performance of communication system a rapid increase.The paper introduces the principle of QPSK modulation and demodulation, the circuits are also be realized based on FPGA. The complier and simulation under MAX+PLUSII environment provides the correction of the design..In addition, this design employs phase selection ,compared with the PM demodulation method,phase selection is simpler,more suitable for FPGA implementation,the reliability of the system is higher.The analysis of simulation waveform indicates that the programme achieves QPSK modulation and demodulation functions well.Keywords:PSK FPGA QPSK modulation demodulation目录摘要 (I)ABSTRACT.................................................... I I 前言 (1)1.绪论 (2)1.1QPSK的简介 (2)1.2FPGA和CPLD简介 (2)1.3VHDL简介 (3)1.4MAX+PLUS II简介 (3)2.调制与解调电路的基本设计原理 (4)2.1QPSK调制的电路原理图 (5)2.2QPSK解调的电路原理图 (5)3.QPSK调制与解调电路的设计 (6)3.1调制电路的设计 (6)3.1.1 设计思路 (6)3.1.2 调制电路的程序 (7)3.1.3 调制电路仿真结果 (8)3.2解调电路的设计 (9)3.2.1 设计思路 (9)3.2.2 解调电路的程序 (10)3.2.3 解调电路的仿真结果 (10)3.3仿真分析 (11)3.3.1 BPSK调制解调的实现及其仿真波形 (11)3.3.2 BPSK和QPSK的区别 (16)3.3.3 QPSK仿真波形的分析 (18)4.总结 (20)参考文献 (21)附录 (22)前言现代通信系统要求通信距离远、通信容量大、传输质量好。

基于FPGA的QPSK调制解调的系统仿真

基于FPGA的QPSK调制解调的系统仿真摘要:本文针对传统的四相移键控(QPSK)的调制解调方式提出一种基于高速硬件描述语言(VHDL)的数字式QPSK调制解调模型。

这种新模型便于在目标芯片FPGA/CPLD上实现QPSK调制解调功能。

文中介绍了QPSK调制解调的原理,并基于FPGA实现了QPSK 调制解调电路。

并给出了可编程逻辑器件FPGA的最新一代集成设计环境QuartusⅡ进行系统仿真的仿真结果。

关键词:QPSK FPGA 调制解调仿真无线通信在现代社会中起着举足轻重的作用。

作为数字通信技术中重要组成部分的调制解调技术一直是通信领域的热点课题。

在众多调制方式中,四相相移键控(QPSK)信号由于抗干扰能力强而得到了广泛的应用,具有较高的频谱利用率和较好的误码性能,并且实现复杂度小,解调理论成熟。

现场可编程门阵列(FPGA)具有功能强大,开发过程投资小、周期短,可反复编程修改,保密性能好,开发工具智能化等特点,用FPGA实现调制解调电路,不仅降低了产品成本,减小了设备体积,满足了系统的需要,而且比专用芯片具有更大的灵活性和可控性。

本课题主要研究了基于FPGA的QPSK调制解调的系统仿真,并给出了QuartusII环境下的仿真结果[1]。

1 QPSK调制的原理四相绝对移相键控QPSK是MPSK的一种特殊情况,它利用载波的四种不同相位来表征数字信息。

由于每一种载波相位代表两个比特信息,故每个四进制码元又被称为双比特码元。

我们把组成双比特码元的前一信息比特用a表示,后一比特信息用b表示。

双比特码元中两个信息比特ab通常是按格雷码(即反射码)排列的,当ab为00时,载波相位为0°,当ab为01时,载波相位为90°,当ab为11时,载波相位为180°,当ab为10时,载波相位为270°。

2 QPSK信号的产生与解调2.1 QPSK信号的产生QPSK信号的产生分为调相法和相位选择法。

基于FPGA的QPSK调制器的设计与实现

20 0 8年 l 2月

湖南 冶金 职 业技 术 学院 学 报

Ju a fHu a tl ria rfsin l e h oo yC U g o r lo n nMeal gc l oe s a c n lg o ee n u P o T

V0. No4 1 8 .

率 、 强 的抗干 扰性 、 电路 上 实现也 较 为简单 , 较 在 本 文研 究 了基 于 F G P A的 Q S P K调制 电路 的实现

【a)^万 i相 系统 c

图 1QP SK信 号Q atsI 境 下 的仿 真 结 ur l环 u

内部 的 P L直 接产 生 Ck L l0和 Ck ll两 路 频 率 相

l F G 0 l / : PA I -l 2 3 xl

一 | 4 "/ r4 r

种 : 幅 键 控 (S ) 频 移 键 控 (s )相 移 键 控 振 A K、 FK、 (S ) P K 。根据 所处 理 的基 带信 号 的进 制不 同 , 它们

可 分 为二进 制 和多进 制 调制( 进制 ) M 。多进制 数

O

1

一r 12 /

中图 分 类号 : M7 文 献标 识 码 : 文章 编号 :62 7 1 ( 0)4 0 9 0 T 6 A 17 — 422 8 — 9— 3 0 0

0 引 言

于a b通常是按格 雷码 的规 则排 列的 , 它与 载波 故 相位的对应关 系如表 1 示 ,相 应的 向量关 系如 所

种不 同相位的载波 。按串饼 变换 器的双 比特码元 的不 同 , 逻辑选相 电路输 出相 应相位 的载波 , 虚线

11 四相 绝对移 相键控 ( P K . QS )

基于FPGA的QPSK调制解调电路设计与实现

基于FPGA的QPSK调制解调电路设计与实现数字调制信号又称为键控信号,调制过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制,最基本的方法有3种:正交幅度调制(QAM)、频移键控(FSK)、相移键控(PSK).根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制).多进制数字调制与二进制相比,其频谱利用率更高.其中QPSK(即4PSK)是MPSK(多进制相移键控)中应用最广泛的一种调制方式。

1 QPSK简介QPSK信号有00、01、10、11四种状态.所以,对输入的二进制序列,首先必须分组,每两位码元一组。

然后根据组合情况,用载波的四种相位表征它们。

QPSK信号实际上是两路正交双边带信号, 可由图1所示方法产生。

QPSK信号是两个正交的2PSK信号的合成,所以可仿照2PSK信号的相平解调法,用两个正交的相干载波分别检测A和B两个分量,然后还原成串行二进制数字信号,即可完成QPSK信号的解调,解调过程如图2所示。

图1 QPSK信号调制原理图图2 QPSK 信号解调原理图2 QPSK 调制电路的FPGA 实现及仿真 2。

1基于FPGA 的QPSK 调制电路方框图基带信号通过串/并转换器得到2位并行信号,,四选一开关根据该数据,选择载波对应的相位进行输出,即得到调制信号,调制框图如图3所示。

基带信号clkstart串/并转换四选一开关分 频0°90°180°270°调制信号FPGA3 QPSK 调制电路框图系统顶层框图如下图中输入信号clk为调制模块时钟,start为调制模块的使能信号,x为基带信号,y是qpsk调制信号的输出端,carrier【3。

0】为4种不同相位的载波,其相位非别为0、90、180、270度,锁相环模块用来进行相位调节,用来模拟通信系统中发送时钟与接收时钟的不同步start1为解调模块的使能信号。

y2为解调信号的输出端。

基于FPGA的QPSK系统设计

基于FPGA的QPSK系统设计QPSK一、实验目的1、利用FPGA实现QPSK调制解调电路设计与实现,加深对QPSK的理性认识,通过实践提高动手能力以及理论联系实际的能力 2、通过对电路模块的组合使用构成通信系统,加深对通信系统的认识和理解,进一步体会《通信原理》课程中的理论知识 3、通过本次试验进一步掌握对Quartus II软件以及VHDL编程语言的使用4、通过本次课程设计的实践提高我们的实践操作能力、提高分析问题和解决问题的能力二、设计任务及要求利用FPGA实现QPSK调制解调电路设计与实现,用FPGA进行数据处理。

实验中给定FPGA模块,D/A转换、A/D转换以及乘法器模块三、实验原理1、FPGA简介目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完1QPSK整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。

一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。

但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。

厂商也可能会提供便宜的但是编辑能力差的FPGA。

因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。

另外一种方法是用CPLD(复杂可编程逻辑器件备)。

基于fpga的qpsk调制器的设计与实现

图1QPSK 调制的原理架构低比特位a高比特位b载波相位θ00011111概述在无线通信与卫星通信中,针对数字信号处理,QPSK 是一种调制方法[1],它的频谱利用率高、抗干扰性强,是一种非常重要的调制解调方式。

近几年来,随着集成电路技术工艺革新,尤其是数字芯片越来越小型化与高速化,数字信号处理技术在通信系统中发挥的作用越发重要,越来越引起人们的重视。

介绍了QPSK 调制原理,运用硬件描述语言实现QPSK 调制,验证了数字调制系统的实现可行性。

2基本原理一个多进制数字相位调制(MPSK)信号码元[2]可以用以下公式(1)表示:(1)M =2k ,其中k 为正整数。

(2)其中A 为振幅,w 为角速度,两者都为常数,t 为调制时间。

θk 为间隔均匀的调试相位,它的值映射了基带码元的取值情况;公式(2)表示相位情况个数,当M =4时,调制方式即为QPSK 调制,它规定了4种载波相位:45°、135°、225°和315°。

QPSK 调制的输入数据是二进制数字序列,考虑到要和四进制的载波相位对应起来,要进行二进制转四进制,即把输入的二进制数据两两比特分组,共有4种组合情况:00、01、10、11,每一组称为双比特码元,它们表示四进制4个符号中的一个符号。

QPSK 调制每次可传输一个双比特码元[3],映射到4种相位的载波。

表1表示了双比特码元和载波相位θ之间映射关系,由表1可见,双比特码元采用格雷码的编码,好处在于相邻相位的双比特码元只有一位不同,假若发生相位误差至相邻相位上的情况,那么这样编码只会造成仅一个比特的误差。

目前,相位调制法与相位选择法[4]为QPSK 调制的主要实现方法,选取了相位选择法,编码调试在FPGA 环境下完成。

原理架构如图1所示,有源晶振50MHz 作为系统时钟,信号源模块使用伪随机序列PRBS,然后把序列输入串并转换模块,输出双比特流数据。

4种相位的载波从四相载波发生器产生。

论文 基于FPGA的QPSK解调器的设计与实现

基于FPGA 的QPSK 解调器的设计与实现Design and Realization of QPSK DemodulationBased on FPGA Technique赵海潮(Zhao ,Haichao ) 周荣花(Zhou ,Ronghua ) 沈业兵(Shen ,Yebing ) 北京理工大学 (北京 100081)摘要:根据软件无线电的思想,用可编程器件FPGA 实现了QPSK 解调,采用带通采样技术对中频为70MHz 的调制信号采样,通过对采样后的频谱进行分析,用相干解调方案实现了全数字解调。

整个设计基于XILINX 公司的ISE 开发平台,并用Virtex-II 系列FPGA 实现。

用FPGA 实现调制解调器具有体积小、功耗低、集成度高、可软件升级、扰干扰能力强的特点,符合未来通信技术发展的方向。

关键词:QPSK ;FPGA ;软件无线电;带通采样中图分类号:TN91 文献标识码:AAbstract : This paper describes the design of QPSK demodulator based on the Xilinx's FPGA device. It is in accord with software radio, bandpass sampling and coherent demodulation techniques are used in the demodulation, and also make analysis with the spectrum.key words : QPSK ;FPGA ;software radio ;bandpass sampling1、引言四相相移键控信号简称“QPSK ”。

它分为绝对相移和相对相移两种。

由于绝对移相方式存在相位模糊问题,所以在实际中主要采用相对移相方式QDPSK 。

它具有一系列独特的优点,目前已经广泛应用于无线通信中,成为现代通信中一种十分重要的调制解调方式。

基于FPGA的QPSK解调器的设计与实现

基于FPGA的QPSK解调器的设计与实现

赵海潮; 周荣花; 沈业兵

【期刊名称】《《微计算机信息》》

【年(卷),期】2004(20)7

【摘要】根据软件无线电的思想,用可编程器件FPGA实现了QPSK解调,采用带通采样技术对中频为70MHz的调制信号采样,通过对采样后的频谱进行分析,用相干解调方案实现了全数字解调。

整个设计基于XILINX公司的ISE开发平台,并用Virtex-II系列FPGA实现。

用FPGA实现调制解调器具有体积小、功耗低、集成度高、可软件升级、扰干扰能力强的特点,符合未来通信技术发展的方向。

【总页数】2页(P76-77)

【作者】赵海潮; 周荣花; 沈业兵

【作者单位】100081 北京市海淀区中关村南大街5号北京理工大学电子工程系2001硕

【正文语种】中文

【中图分类】TN91

【相关文献】

1.基于FPGA的QPSK高速解调器的设计与实现 [J], 宋广怡;彭继强

2.基于FPGA的全数字QPSK调制解调器的设计 [J], 李理

3.基于FPGA的自适应QPSK解调器的设计实现 [J], 刘鹏

4.基于FPGA的自适应QPSK解调器的设计实现 [J], 刘鹏

5.基于FPGA的QPSK调制解调器 [J], 牛学芬; 管莹; 李佳音

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的QPSK调制器的设计

2 基于 F P G A的 QP S K调 制器 的设计 2 . 1 数 字调 制方式的基本原理

2 k

k

Ⅳ+ ………………………・ 一( 式4 )

本文主要 以 M=4来讨 论 ,4 P S K即 四相移 相键 控 ,常

的方 法 。 2 . 2 四相 移 相 键 控 Q P S K 的调 制 原 理

1 2 0 .

厂 1 \ \ .

11

。

1 O

( a )初始 相位 为0

( b)初始相 位为 , 4

在2 P S K信号的表达式 中 ,一个码元 的载波初 始相 位 0 可 以等 于 0或 ,将其 推广 到 多进 制 时 ,0 可 以 取多 个值 。

参量进行控 制 ,使 载波 的这些 参量 随基 带信 号 的变化 而变 化 ,即进 行调制。从原理上来说 ,只要已调信号适 合于信道

q k= ( k一1 ) k= 1 , 2 , L, M … … … … 一( 式3 ) 通常 ,M取 2的整数次幂 :

:

传输,受调载波的波形可以是任意的。因为正弦信号形式简

摘

要 :本 文主要 阐述 了数 字调制 系统 的基本原理 ,针 对 四相 移相键控 ( QP S K)调制 方式进行 了分

析 ,并用 F P G A设计 出了一个采 用相 位选择 法的 QP S K调 制器 。经过 测试验证 ,用 S y n p l i f y

P r o 软 件 综 合 后 得 出该 调 制 器 的 电路 原 理 图 , 比较 并得 出 了设 计 Q P S K 的 一般 方 法 。 关 键 词 :调 制 ;Q P S K;载 波 ;F P G A

qpsk调制解调——基于fpga

一实验概述本实验包括:分频器设计、计数器设计、串行移位输出器设计、伪码发生器设计、QPSK I/Q调制器设计、QPSK I/Q解调器设计,基于选项法中频调制器设计并将其综合起来组成一个系统。

二实验仪器计算机ALTER公司的Quartus8.0 EDA试验箱。

三EDA及实验工具简介EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

从应用领域来看,EDA技术已经渗透到各行各业,如上文所说,包括在机械、电子、通信、航空航航天、化工、矿产、生物、医学、军事等各个领域,都有EDA应用。

quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

Altera quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

四 实验步骤及实验模块参数(一)设计一个分频器,要求29 分频。

(二)设计计数器,计数值16。

(三)设计串行移位输出器,移位级数14。

(四)设计伪码发生器,伪码产生的数据数率要8Kb/s ,特征方程1359+++x x x 。

(五)设计QPSK I/Q 调制器,调制载波288KHZ ,基带速率576KHZ ,系统时钟4068KHZ 。

QPSK调制解调器的设计及FPGA实现

QPSK调制解调器的设计及FPGA实现一、本文概述随着无线通信技术的飞速发展,调制解调器作为信息传输的关键部分,其性能对整个通信系统的稳定性和可靠性有着至关重要的影响。

四相相移键控(Quadrature Phase Shift Keying,QPSK)作为一种高效且稳定的调制方式,在无线通信中得到了广泛应用。

本文旨在深入研究QPSK调制解调器的设计,并探讨其在现场可编程门阵列(Field Programmable Gate Array,FPGA)上的实现方法。

本文首先将对QPSK调制解调的基本原理进行详细阐述,包括其信号处理方式、调制解调流程以及关键性能指标。

在此基础上,我们将探讨QPSK调制解调器的设计方法,包括调制器与解调器的结构选择、参数优化等。

同时,我们还将分析影响QPSK调制解调器性能的关键因素,如噪声、失真等,并提出相应的优化策略。

为了实现QPSK调制解调器的硬件化,本文将重点研究其在FPGA 上的实现方法。

我们将首先分析FPGA在数字信号处理方面的优势,然后详细介绍如何在FPGA上设计并实现QPSK调制解调器,包括硬件架构的选择、关键模块的设计与实现、以及资源优化等方面的内容。

我们还将讨论如何在实际应用中测试和优化FPGA实现的QPSK调制解调器,以确保其性能达到最佳状态。

本文旨在深入研究QPSK调制解调器的设计及其在FPGA上的实现方法,为无线通信系统的优化和升级提供理论支持和技术指导。

通过本文的研究,我们期望能够为相关领域的工程师和研究人员提供有益的参考和启示,推动QPSK调制解调技术的发展和应用。

二、QPSK调制原理QPSK,即四相相移键控(Quadrature Phase Shift Keying),是一种数字调制方式,它在每一符号周期内通过改变载波信号的相位来传递信息。

QPSK调制利用四个不同的相位状态来表示两个不同的比特组合,从而实现了更高的数据传输效率。

在QPSK调制中,每个符号通常代表两个比特的信息。

基于fpga的qpsk调制解调原理及实现方法

基于fpga的qpsk调制解调原理及实现方法QPSK(Quadrature Phase Shift Keying)是一种常见的调制解调技术,在许多无线通信系统中广泛应用。

本文将介绍基于FPGA的QPSK调制解调的原理,并给出实现方法。

一、QPSK调制原理QPSK调制是一种相位调制技术,通过调整信号的相位来实现多个比特的传输。

在QPSK调制中,将数字比特流分为两组,每组两位比特,分别称为I和Q。

QPSK调制原理如下:1. 将两位比特I和Q转换为相应的相位值:- 00:相位0°- 01:相位90°- 10:相位180°- 11:相位270°2. 将相位调制的信号进行合并,得到QPSK调制信号。

具体操作是将两路调制信号分别乘以正弦函数和余弦函数,然后相加。

二、QPSK解调原理QPSK解调是将接收到的QPSK调制信号还原为原始的数字比特流。

解调的过程可以分为两步:信号的采样和相位恢复。

1. 信号的采样:使用FPGA时钟信号对收到的QPSK调制信号进行采样,采样频率应与信号的带宽相匹配。

2. 相位恢复:通过采样得到的信号,利用相位锁定环(PLL,Phase-Locked Loop)等技术,恢复原始信号的相位。

三、基于FPGA的QPSK调制解调实现方法基于FPGA的QPSK调制解调可以通过硬件描述语言(如Verilog 或VHDL)实现。

下面给出一种基本的实现方法。

1. QPSK调制实现:a. 采用FPGA的GPIO(通用输入输出)接口输入数字比特流。

b. 将输入的比特流转换为相应的相位值,可以使用查找表(Look-Up Table)实现。

c. 将相位值转换为正弦和余弦函数的乘积,并相加得到调制信号。

d. 输出调制后的信号。

2. QPSK解调实现:a. 使用FPGA的ADC(模数转换器)接口采样接收到的QPSK 调制信号。

b. 对采样信号进行滤波,去除噪声和多径干扰。

基于FPGA的PSK调制解调器设计与实现

基于FPGA的PSK调制解调器设计与实现PSK调制解调器是一种常用的数字通信调制技术,有着广泛的应用。

本文将介绍基于FPGA的PSK调制解调器的设计和实现方法,包括硬件设计和软件编程。

通过本文的阐述,读者将能够了解到PSK调制解调器的工作原理及其在数字通信中的重要性,同时也能够掌握使用FPGA实现PSK调制解调器的具体步骤。

一、PSK调制解调器的工作原理PSK调制解调器是一种通过改变载波相位来传输数字信息的调制解调技术。

它的工作原理是利用不同相位表示不同的数字码元,将数字信息转化为相位变化。

二、FPGA在数字通信中的应用FPGA(可编程逻辑门阵列)是一种可编程的集成电路芯片,其灵活性和并行处理能力使得它成为了数字通信领域中的重要工具。

FPGA可以通过编程实现不同的功能模块,适应不同的应用需求,因此在数字通信中有着广泛的应用。

三、基于FPGA的PSK调制解调器设计流程1. 硬件设计在硬件设计中,需要考虑到PSK调制解调器所涉及的各个部分,包括载波生成模块、相位调制模块、解调模块、信号恢复模块等。

通过使用FPGA的可编程逻辑单元和触发器等组件,可以实现这些模块,并将其连接起来形成完整的调制解调器。

2. 软件编程在软件编程中,需要根据硬件设计的要求,提供相应的控制信号和数据处理算法。

使用FPGA开发工具和编程语言,可以编写适应PSK 调制解调器需要的代码,实现信号的调制解调和数据的处理。

四、基于FPGA的PSK调制解调器实现步骤1. 硬件配置首先,需要将FPGA与其他外设进行连接,如计算机、模拟信号发生器等。

确保硬件连接正确,以便进行后续的实验和测试。

2. 硬件设计根据PSK调制解调器的工作原理和需求,设计硬件电路,并使用FPGA开发工具进行电路的逻辑设计和仿真。

确保硬件设计符合预期的要求并能够正常工作。

3. 软件编程在硬件设计完成后,根据硬件电路的需要,编写相应的软件程序。

使用FPGA开发工具中的编程语言和库函数,实现PSK调制解调器的控制和数据处理功能。