DFS MTDS CALIPER

5G考试基础试题(含答案)

(A )5G 考试基础试题(含答案)一、单项选择题1、 5G NR 帧结构的基本时间单位是 (C )A) subframeB) slotC) TcD) symbol2、 5G 无线帧长是多少ms ( B )A) 5B) 10C) 20D) 403、 EN-DC 中,MCG 进行NR 邻区测量使用的参考信号A) SSB RSB) CSI-RSC) C-RSD) DM-RS4、 EN-DC 中,下面哪种测量目前协议未定义( C )A) MCG 下进行2/3G 邻区测量B) MCG 下进行LTE 邻区测量C) SCG 下进行LTE 邻区测量D) SCG 下进行NR 邻区测量5、划分SUL频段的意义是(C)A)增大上行数据传输速率B)增大下行数据传输速率C)与3.5GHz搭配使用,补充上行覆盖范围D)与5GHz搭配使用,补充下行覆盖范围6、5G中sub-6GHz频段能支持的最大带宽为(B)A)200MHzB)100MHzC)80MHzD)60MHz7、在5G技术中,用于提升接入用户数的技术是(A)A)Massive MIMOB)SOMAC)Massive CAD)1mcTTI8、5G NR的信道带宽利用率最高可达(A)A)98.28%B)90.28%C)92.55%D)97.32%9、5G每平方公里至少支持多少台设备(D)(B ) B) 1万C) 10 万D) 100 万10、基站带宽为80MHz时,UE信道带宽不可能为( A)A) 120MHzB) 40MHzC) 20MHzD) 50MHz11、SCG的主小区被称作(D )A) Primary cellB) MCG Seco ndary cellC) SCG Seco ndary cellD) PSCell12、下面哪种子载波间隔是中国移动白皮书中规定必选A) 15KHzB) 30KHzC) 60KHzD) 120KHz13、5G参数集包含哪些参数(A )A) SCS+CPC) BandwidthD) Slot format14、对于1个服务小区,基站可以通过专用RRC信令给UE配置多个DL BWP和多个ULBWP最多各配多少个( B)A) 2B) 4C) 8D) 1215、5G帧结构描述中,下面哪一项是错误的(C )A) 帧结构配置可以由SIB静态帧结构配置B) 上下行资源比例可在1:4到2:3之间调整C) R15的协议中,RRC高层配置的tdd-UL-DL-Co nfiguratio nDedicated 定义了周期大小D) DCI format2-0 用于动态指示帧结构16、一个BWP最少占用多少个RB ( C )A) 16B) 22C) 24D) 3217、下列选项中关于beam report 描述有误的是( B)A) 网络配置CSI-RS资源和上报方式B) UE通过RRC信令上报beam测量结果C) 可以将beam分组,以组的形式上报D) UE可以通过SSB进行beam测量上报18、LTE测量NR的RS类型是(A)A) SSBB) CSI-RSC) Mix of SSB and CSI-RSD) CRS19、LTE测量NR,测量的基本单位是( B)A) 小区B) BeamC) 载波D) PLMN20、目前,NR FR1和LTE共同确定的Gap, Gap pattern 有几种(D)A) 1B) 2C) 3D) 421、SCG失败时,下面哪项正确(D)A) UE悬挂所有的SCG无线承载的SCG传输并向MN上报SCG失败信息,触发RRC连接重建B) UE不维持当前MN和SN的测量配置C) UE不执行MN和SN配置的测量D) SN配置的测量通过MN路由时,在SCG失败时,UE继续上报SN配置测量形成的测量报告22、基于SSB的NR同频测量在measconfig 里最多可以配置几个SMTC窗口( B)A) 1B) 2C) 3D) 423、Release 14 之后有几种PHR Type ( C )A) 1B) 2C) 3D) 424、以下哪个是用于SRS传输的PHR ( C)A) TypelB) Type2C) Type3D) Type425、5GNR下,一个SS/PBCH block 包含(D)个OFDM symbolsA) 1B) 226、5GNR下,DL Layer mapping 的时候当layer 数大于(C), codeword才是双流A) 2B) 3C) 4D) 527、下列选项中哪个是5G NR下PUCCH配置特点(D)A)系统带宽两端B)固定14个符号C)跳频D)灵活长度28、下列关于5GNR slot format 说法正确的是(C)A)对DL/UL分配的修改以slot为单位B) SCS=60KHz 时,支持配置Periodic=0.625msC)Cell-specific 的单周期配置中,单个配置周期内只支持一个转换点D)在R15,UE-specific 配置的周期和cell-specific 配置的周期可以不一致29、gNB可以通过哪种方式给UE发送Timing AdvanceCommandA) RRC专用信令B) MAC CEC) 系统消息D) DCI30、下列关于SR的说法错误的是(B)A) SR流程的目的是为UL-SCH上的新传数据(不是重传数据)申请资源B) 处于任何状态的UE都可以发送SRC) 每个SR的配置可以关联一个或者多个逻辑信道,每个逻辑信道又可以映射多个零个或者一个RRC配置的SR的配置。

AT28HC64B高性能电擦可编程只读存储器(EEPROM)说明书

Features Array•Fast Read Access Time – 70 ns•Automatic Page Write Operation–Internal Address and Data Latches for 64 Bytes•Fast Write Cycle Times–Page Write Cycle Time: 10 ms Maximum (Standard)2 ms Maximum (Option – Ref. AT28HC64BF Datasheet)–1 to 64-byte Page Write Operation•Low Power Dissipation–40 mA Active Current–100µA CMOS Standby Current•Hardware and Software Data Protection•DATA Polling and Toggle Bit for End of Write Detection•High Reliability CMOS Technology–Endurance: 100,000 Cycles–Data Retention: 10 Years•Single 5 V ±10% Supply•CMOS and TTL Compatible Inputs and Outputs•JEDEC Approved Byte-wide Pinout•Industrial Temperature Ranges•Green (Pb/Halide-free) Packaging Option Only1.DescriptionThe AT28HC64B is a high-performance electrically-erasable and programmable read-only memory (EEPROM). Its 64K of memory is organized as 8,192 words by 8 bits. Manufactured with Atmel’s advanced nonvolatile CMOS technology, the device offers access times to 55 ns with power dissipation of just 220 mW. When the device is deselected, the CMOS standby current is less than 100µA.The AT28HC64B is accessed like a Static RAM for the read or write cycle without the need for external components. The device contains a 64-byte page register to allow writing of up to 64 bytes simultaneously. During a write cycle, the addresses and 1 to 64 bytes of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the device will automatically write the latched data using an internal control timer. The end of a write cycle can be detected by DATA polling of I/O7. Once the end of a write cycle has been detected, a new access for a read or write can begin.Atmel’s AT28HC64B has additional features to ensure high quality and manufactura-bility. The device utilizes internal error correction for extended endurance and improved data retention characteristics. An optional software data protection mecha-nism is available to guard against inadvertent writes. The device also includes anextra 64 bytes of EEPROM for device identification or tracking.20274L–PEEPR–2/3/09AT28HC64B2.Pin Configurations2.128-lead SOIC Top ViewPin Name Function A0 - A12Addresses CE Chip Enable OE Output Enable WE Write Enable I/O0 - I/O7Data Inputs/Outputs NC No Connect DCDon’t Connect2.232-lead PLCC Top ViewNote:PLCC package pins 1 and 17 are Don’t Connect.2.328-lead TSOP Top View30274L–PEEPR–2/3/09AT28HC64B3.Block Diagram4.Device Operation4.1ReadThe AT28HC64B is accessed like a Static RAM. When CE and OE are low and WE is high, the data stored at the memory location determined by the address pins is asserted on the out-puts. The outputs are put in the high-impedance state when either CE or OE is high. This dual line control gives designers flexibility in preventing bus contention in their systems.4.2Byte WriteA low pulse on the WE or CE input with CE or WE low (respectively) and OE high initiates a write cycle. The address is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the first rising edge of CE or WE. Once a byte write has been started, it will automatically time itself to completion. Once a programming operation has been initiated and for the duration of t WC , a read operation will effectively be a polling operation.4.3Page WriteThe page write operation of the AT28HC64B allows 1 to 64 bytes of data to be written into the device during a single internal programming period. A page write operation is initiated in the same manner as a byte write; after the first byte is written, it can then be followed by 1 to 63 additional bytes. Each successive byte must be loaded within 150 µs (t BLC ) of the previous byte. If the t BLC limit is exceeded, the AT28HC64B will cease accepting data and commence the internal programming operation. All bytes during a page write operation must reside on the same page as defined by the state of the A6 to A12 inputs. For each WE high-to-low transition during the page write operation, A6 to A12 must be the same.The A0 to A5 inputs specify which bytes within the page are to be written. The bytes may be loaded in any order and may be altered within the same load period. Only bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not occur.4.4DATA PollingThe AT28HC64B features DATA Polling to indicate the end of a write cycle. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data to be presented on I/O7. Once the write cycle has been completed, true data is valid on all outputs, and the next write cycle may begin. DATA Polling may begin at any time during the write cycle.40274L–PEEPR–2/3/09AT28HC64B4.5Toggle BitIn addition to DATA Polling, the AT28HC64B provides another method for determining the end of a write cycle. During the write operation, successive attempts to read data from the device will result in I/O6 toggling between one and zero. Once the write has completed, I/O6 will stop toggling, and valid data will be read. Toggle bit reading may begin at any time during the write cycle.4.6Data ProtectionIf precautions are not taken, inadvertent writes may occur during transitions of the host system power supply. Atmel ® has incorporated both hardware and software features that will protect the memory against inadvertent writes.4.6.1Hardware ProtectionHardware features protect against inadvertent writes to the AT28HC64B in the following ways: (a) V CC sense – if V CC is below 3.8 V (typical), the write function is inhibited; (b) V CC power-on delay – once V CC has reached 3.8 V, the device will automatically time out 5 ms (typical) before allowing a write; (c) write inhibit – holding any one of OE low, CE high or WE high inhib-its write cycles; and (d) noise filter – pulses of less than 15 ns (typical) on the WE or CE inputs will not initiate a write cycle.4.6.2Software Data ProtectionA software-controlled data protection feature has been implemented on the AT28HC64B. When enabled, the software data protection (SDP), will prevent inadvertent writes. The SDP feature may be enabled or disabled by the user; the AT28HC64B is shipped from Atmel with SDP disabled.SDP is enabled by the user issuing a series of three write commands in which three specific bytes of data are written to three specific addresses (refer to the “Software Data Protection Algorithm” diagram on page 10). After writing the 3-byte command sequence and waiting t WC , the entire AT28HC64B will be protected against inadvertent writes. It should be noted that even after SDP is enabled, the user may still perform a byte or page write to the AT28HC64B. This is done by preceding the data to be written by the same 3-byte command sequence used to enable SDP.Once set, SDP remains active unless the disable command sequence is issued. Power transi-tions do not disable SDP, and SDP protects the AT28HC64B during power-up and power-down conditions. All command sequences must conform to the page write timing specifica-tions. The data in the enable and disable command sequences is not actually written into the device; their addresses may still be written with user data in either a byte or page write operation.After setting SDP, any attempt to write to the device without the 3-byte command sequence will start the internal write timers. No data will be written to the device, however. For the dura-tion of t WC , read operations will effectively be polling operations.4.7Device IdentificationAn extra 64 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12 V ±0.5 V and using address locations 1FC0H to 1FFFH, the additional bytes may be written to or read from in the same manner as the regular memory array.50274L–PEEPR–2/3/09AT28HC64BNotes:1.X can be VIL or VIH.2.See “AC Write Waveforms” on page 8.3.VH = 12.0 V ±0.5 V.Note:1.I SB1 and I SB2 for the 55 ns part is 40 mA maximum.5.DC and AC Operating RangeAT28HC64B-70AT28HC64B-90AT28HC64B-120Operating Temperature (Case)-40°C - 85°C -40°C - 85°C -40°C - 85°C V CC Power Supply5 V ±10%5 V ±10%5 V ±10%6.Operating ModesMode CE OE WE I/O Read V IL V IL V IH D OUT Write (2)V IL V IH V IL D IN Standby/Write Inhibit V IH X (1)X High ZWrite Inhibit X X V IH Write Inhibit X V IL X Output Disable X V IH XHigh ZChip Erase V ILV H (3)V IL High Z7.Absolute Maximum Ratings*Temperature Under Bias................................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityStorage Temperature.....................................-65°C to +150°C All Input Voltages(including NC Pins)with Respect to Ground.................................-0.6 V to +6.25 V All Output Voltageswith Respect to Ground...........................-0.6 V to V CC + 0.6 V Voltage on OE and A9with Respect to Ground..................................-0.6 V to +13.5V8.DC CharacteristicsSymbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0 V to V CC + 1 V 10µA I LO Output Leakage Current V I/O = 0 V to V CC10µA I SB1V CC Standby Current CMOS CE = V CC - 0.3 V to V CC + 1 V 100(1)µA I SB2V CC Standby Current TTL CE = 2.0 V to V CC + 1 V 2(1)mA I CC V CC Active Current f = 5 MHz; I OUT = 0 mA40mA V IL Input Low Voltage 0.8V V IH Input High Voltage 2.0V V OL Output Low Voltage I OL = 2.1 mA 0.40V V OH Output High VoltageI OH = -400 µA2.4V60274L–PEEPR–2/3/09AT28HC64B10.AC Read Waveforms (1)(2)(3)(4)Notes:1.CE may be delayed up to t ACC - t CE after the address transition without impact on t ACC .2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE or by t ACC - t OE after an address changewithout impact on t ACC .3.t DF is specified from OE or CE whichever occurs first (C L = 5 pF).4.This parameter is characterized and is not 100% tested.9.AC Read CharacteristicsSymbol ParameterAT28HC64B-70AT28HC64B-90AT28HC64B-120Units MinMax MinMax MinMax t ACC Address to Output Delay 7090120ns t CE (1)CE to Output Delay 7090120ns t OE (2)OE to Output Delay 035040050ns t DF (3)(4)OE to Output Float 035040050ns t OHOutput Hold00ns70274L–PEEPR–2/3/09AT28HC64B11.Input Test Waveforms and Measurement Level12.Output Test LoadNote:1.This parameter is characterized and is not 100% tested.R F 13.Pin Capacitancef = 1 MHz, T = 25°C (1)Symbol Typ Max Units Conditions C IN 46pF V IN = 0 V C OUT 812pFV OUT = 0 V815.AC Write Waveforms15.1WE Controlled15.2CE Controlled14.AC Write CharacteristicsSymbol ParameterMin MaxUnits t AS , t OES Address, OE Setup Time 0ns t AH Address Hold Time 50ns t CS Chip Select Setup Time 0ns t CH Chip Select Hold Time 0ns t WP Write Pulse Width (WE or CE)100ns t DS Data Setup Time 50ns t DH , t OEHData, OE Hold Timens90274L–PEEPR–2/3/09AT28HC64B17.Page Mode Write Waveforms (1)(2)Notes: 1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE).2.OE must be high only when WE and CE are both low.18.Chip Erase Waveformst S = t H = 5 µs (min.)t W = 10 ms (min.)V H = 12.0 V ±0.5 V16.Page Mode CharacteristicsSymbol Parameter MinMax Units t WC Write Cycle Time10ms t WC Write Cycle Time (Use AT28HC64BF))2ms t AS Address Setup Time 0ns t AH Address Hold Time 50ns t DS Data Setup Time 50ns t DH Data Hold Time 0ns t WP Write Pulse Width 100ns t BLC Byte Load Cycle Time 150µs t WPHWrite Pulse Width High50ns100274L–PEEPR–2/3/09AT28HC64B19.Software Data Protection EnableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4.1 to 64 bytes of data are loaded.20.Software Data Protection DisableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4. 1 to 64 bytes of data are loaded.21.Software Protected Write Cycle Waveforms (1)(2)Notes:1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE) after the softwarecode has been entered.2.OE must be high only when WE and CE are both low.11AT28HC64BNote:1.These parameters are characterized and not 100% tested. See “AC Read Characteristics” on page 6.23.Data Polling WaveformsNotes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 6.25.Toggle Bit Waveforms (1)(2)(3)Notes: 1.Toggling either OE or CE or both OE and CE will operate toggle bit.2.Beginning and ending state of I/O6 will vary.3.Any address location may be used, but the address should not vary.22.Data Polling Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 0ns t OEH OE Hold Time 0ns t OE OE to Output Delay (1)ns t WR Write Recovery Timens24.Toggle Bit Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 10ns t OEH OE Hold Time 10ns t OE OE to Output Delay (2)ns t OEHP OE High Pulse 150ns t WR Write Recovery Timens12AT28HC64B26.Normalized I CCGraphs13AT28HC64B27.Ordering Information27.1Green Package Option (Pb/Halide-free)t ACC (ns)I CC (mA)Ordering Code Package Operation RangeActive Standby 70400.1AT28HC64B-70TU 28T Industrial (-40°C to 85°C)AT28HC64B-70JU 32J AT28HC64B-70SU 28S 90400.1AT28HC64B-90JU 32J AT28HC64B-90SU 28S AT28HC64B-90TU 28T 120400.1AT28HC64B-12JU 32J AT28HC64B-12SU28SPackage Type32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)28T28-lead, Plastic Thin Small Outline Package (TSOP)27.2Die ProductsContact Atmel Sales for die sales options.28.Packaging Information 28.132J – PLCC14AT28HC64BAT28HC64B 28.228S – SOIC1528.328T – TSOP16AT28HC64BHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2009 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

最佳多普勒处理机

哈尔滨工业大学电子工程系

6

距离门多普勒滤波器

把距离(时间)量化成小间隔可以消除距离信息损失和距离崩溃损失,

这种处理叫做是距离门处理。通常距离门的宽度与脉冲宽度在同一个数量 级。距离分辨力是由波门确定的,一旦将雷达回波A/D量化成距离间隔,

每个门(对应不同采样点)的输出可送入一组窄带滤波器进行杂波抑制,因

脉冲雷达的距离崩溃

脉冲工作且fd<1/τ时,由于窄带滤波器的带宽Δf<fd<1/τ,则1/Δf>τ,即单

个目标的一串回波脉冲经过窄带滤波后输出的每个脉冲在时域上均被展宽。

考虑多不同距离的多个目标回波同时输入情形,输出脉冲展宽导致距离分 辨力降低,严重地将导致距离崩溃。

直接窄带滤波输出

2018/12/3

MTI、MTD/PD的核心

MTI——衰减与任何固定杂波对应的多普勒频率区域

由于与地面杂波对应的频谱区域趋向集中在PRF谱线附近,所以周 期性的MTI滤波器(延时线对消器)响应呈现梳子形状,故称之为梳状滤 波器。

MTD/PD——与目标的多普勒频谱响应匹配

由于相对于雷达的目标多普勒频移的幅度可能出现在对应于最大 雷达平台速度和目标速度之和多普勒频率的任何区域内,所以目标频 谱区域必须用覆盖所有可能的预期目标多普勒频移的一组多普勒滤波 器填满。因此,PD滤波器响应通常由多普勒频率滤波器组构成,这些 滤波器组填充了发射波形PRF谱线之间区域的大部分。

W H M s W V H U H M s UV U H M nUI V H (U H M s U)V If H H H W M n W V U M n UV VH V

2018/12/3 哈尔滨工业大学电子工程系 11

云计算第三版Amazon云计算AWS

3.1 基础存储架构Dynamo

《云计算》第三版配套PPT课件

成员资格及错误检测

为了避免新加入的节点之间不能及时发现其他节点的存在,Dynamo中设置了一些 种子节点(Seed Node)。种子节点和所有的节点都有联系。当新节点加入时, 它扮演一个中介的角色,使新加入节点之间互相感知。

新节点 1

新节点 2

直到N个节点全部传遍

结论:

Dynamo中的节点数不能太多 Amazon采用了分层Dynamo结构 来解决该问题

25 of 52

容错机制 《云计算》第三版配套PPT课件

由于成本方面的原因,Dynamo中很多服务器采用的是普通 PC主机; 其硬盘性能和专业服务器硬盘相差很远,出错很难避免; Dynamo中容错机制非常重要

11 of 52

《云计算》第三版配套PPT课件

数据均衡《云分计算布》第的三版问配套P题PT课件

➢一致性哈希算法

平衡性 单调性 分散性 负载

两步进行:

求出设备节点的哈希值,并

配置到环上的一个点;接着

计算数据的哈希值,按顺时

针方向将其存放到环上第一

个大于或等于数据哈希值的

节点上; 添加新节点时,按

照上述规则,调整相关数据

问题 数据均衡分布

数据备份 数据冲突处理 成员资格及错误检测 临时故障处理 永久故障处理

采取的相关技术 改进的一致性哈希算法 参数可调的弱quorum机制 向量时钟(Vector Clock) 基于Gossip协议的成员资格和错误检测 Hinted handoff(数据回传机制),

Merkle哈希树

种子节点

A B

C

24 of 52

3.1 基础存储架构Dynamo

HSMS-2800中文资料

In a quad, the diagonal capacitance is the capacitance between points A and B as shown in the figure below. The diagonal capacitance is calculated using the following formula

3

12 #4

CROSS-OVER QUAD 34

12 #9

Байду номын сангаас

Description/Applications

These Schottky diodes are specifically designed for both analog and digital applications. This series offers a wide range of specifications and package configurations to give the designer wide flexibility. Typical applications of these Schottky diodes are mixing, detecting, switching, sampling, clamping, and wave shaping. The HSMS-2800 series of diodes is optimized for high voltage applications. The HSMS-2810 series of diodes features very low flicker (1/f) noise. The

temperature.

Quad Capacitance

中国移动通信光传送网维护管理规程

中国移动通信光传送网维护管理规程中国移动通信集团公司二○○二年十月目录第一章总则 (5)第二章维护和管理组织 (7)第一节维护和管理机构的职责 (7)第二节各级维护和管理职能部门的关系 (11)第三节维护责任的划分 (12)第三章维护和管理工作制度 (13)第一节岗位责任制 (13)第二节值班和交接班制 (15)第三节技术档案和资料管理 (16)第四节装备、设备、备盘、备件、仪表和工具管理制度 (16)第五节随工和验收制度 (16)第六节重大阻断报告制 (17)第四章传输线路的维护 (18)第一节通则 (18)第二节线路维护的职责 (18)第三节线路维护内容 (19)第四节长途线路主要技术维护指标及要求 (21)第五节障碍处理和程序 (23)第五章SDH传送网的维护 (26)第一节通则 (26)第二节SDH再生段和复用段 (27)第三节通道 (29)第四节传送网同步与定时 (32)第五节障碍处理 (33)第六节定期测试 (36)第七节光接口 (37)第八节辅助系统 (38)第六章WDM传输系统的维护 (39)第一节通则 (39)第二节光放大器站 (39)第三节WDM系统终端站 (40)第四节光通道、级联的光通道 (41)第五节OADM站 (42)第六节系统性能测试 (42)第七节故障处理 (46)第七章传送网资源管理 (48)第一节通则 (48)第二节通道管理 (49)第八章网管系统的维护 (52)第一节通则52第二节网管系统的设置 (52)第三节网管硬件维护 (52)第四节网管软件和数据维护 (53)第五节网管系统维护网络的要求 (54)第九章障碍处理流程 (56)第十章传送网其它设备的维护 (57)第十一章质量管理 (58)第一节通则 (58)第二节质量监督检查 (58)第三节质量统计分析和考核评定 (59)第十二章机房管理和安全保密 (60)附录A 中国移动光传送网组织结构职能描述 (62)附录B VC-N投入业务性能指标 (63)附录C WDM系统光接口指标 (65)第一章总则第1条移动通信光传送网是由长途、本地光缆及传输设备等组成,是移动通信网基础设施的主要组成部分。

TD信息元素详解

信息元素功能性定义作者:李欣目录目录 (1)信息元素功能性定义 (11)1 核心网信息元素 (11)1.1 CN Information elements (11)1.2 CN Domain System Information (11)1.3 CN Information info (11)1.4 IMEI (11)1.5 IMSI (GSM-MAP) (11)1.6 Intra Domain NAS Node Selector (11)1.7 Location Area Identification (12)1.8 NAS message (12)1.9 NAS system information (GSM-MAP) (12)1.10 Paging record type identifier (12)1.11 PLMN identity (12)1.12 PLMN Type (12)1.13 P-TMSI (GSM-MAP) (12)1.14 RAB identity (12)1.15 Routing Area Code (12)1.16 Routing Area Identification (13)1.17 TMSI (GSM-MAP) (13)2 UTRAN 移动信息元素 (13)2.1 Cell Access Restriction (13)2.2 Cell identity (13)2.3 Cell selection and re-selection info for SIB3/4 (13)2.4 Cell selection and re-selection info for SIB11/12 (13)2.5 Mapping Info (14)2.6 URA identity (14)3 UE 信息元素 (14)3.1 Activation time (14)3.2 Capability Update Requirement (14)3.3 Cell update cause (15)3.4 Ciphering Algorithm (15)3.5 Ciphering mode info (15)3.6 CN domain specific DRX cycle length coefficient (15)3.7 CPCH Parameters (15)3.8 C-RNTI (15)3.9 DRAC system information (15)3.10 Void (16)3.11 Establishment cause (16)3.12 Expiration Time Factor (16)3.13 Failure cause (16)3.14 Failure cause and error information (16)3.15 Initial UE identity (16)3.16 Integrity check info (16)3.17 Integrity protection activation info (17)3.18 Integrity protection Algorithm (17)3.19 Integrity protection mode info (17)3.20 Maximum bit rate (17)3.21 Measurement capability (17)3.22 Paging cause (17)3.23 Paging record (17)3.24 PDCP capability (17)3.25 Physical channel capability (18)3.26 Protocol error cause (18)3.27 Protocol error indicator (18)3.28 RB timer indicator (18)3.29 Redirection info (18)3.30 Re-establishment timer (18)3.31 Rejection cause (18)3.32 Release cause (18)3.33 RF capability FDD (19)3.34 RLC capability (19)3.35 RLC re-establish indicator (19)3.36 RRC transaction identifier (19)3.37 Security capability (19)3.38 START (19)3.39 Transmission probability (19)3.40 Transport channel capability (20)3.41 UE multi-mode/multi-RAT capability (20)3.42 UE radio access capability (20)3.43 UE Timers and Constants in connected mode (21)3.44 UE Timers and Constants in idle mode (21)3.45 UE positioning capability (21)3.46 URA update cause (21)3.47 U-RNTI (21)3.48 U-RNTI Short (21)3.49 UTRAN DRX cycle length coefficient (21)3.50 Wait time (21)3.51 UE Specific Behavior Information 1 idle (21)3.52 UE Specific Behavior Information 1 interRAT (22)4 无线承载信息元素 (22)4.0 Default configuration identity (22)4.1 Downlink RLC STATUS info (22)4.2 PDCP info (22)4.3 PDCP SN info (22)4.4 Polling info (22)4.5 Predefined configuration identity (23)4.6 Predefined configuration value tag (23)4.7 Predefined RB configuration (23)4.8 RAB info (23)4.9 RAB info Post (23)4.10 RAB information for setup (23)4.11 RAB information to reconfigure (24)4.12 NAS Synchronization indicator (24)4.13 RB activation time info (24)4.14 RB COUNT-C MSB information (24)4.15 RB COUNT-C information (24)4.16 RB identity (24)4.17 RB information to be affected (24)4.18 RB information to reconfigure (25)4.19 RB information to release (25)4.20 RB information to setup (25)4.21 RB mapping info (25)4.22 RB with PDCP information (25)4.23 RLC info (25)4.24 Signaling RB information to setup (26)4.25 Transmission RLC Discard (26)5 传输信道信息元素 (26)5.1 Added or Reconfigured DL TrCH information (26)5.2 Added or Reconfigured UL TrCH information (27)5.3 CPCH set ID (27)5.4 Deleted DL TrCH information (27)5.5 Deleted UL TrCH information (27)5.6 DL Transport channel information common for all transport channels (27)5.7 DRAC Static Information (27)5.8 Power Offset Information (28)5.9 Predefined TrCH configuration (28)5.10 Quality Target (28)5.11 Semi-static Transport Format Information (28)5.12 TFCI Field 2 Information (28)5.13 TFCS Explicit Configuration (28)5.14 TFCS Information for DSCH (TFCI range method) (29)5.15 TFCS Reconfiguration/Addition Information (29)5.16 TFCS Removal Information (29)5.17 Void (29)5.18 Transport channel identity (29)5.19 Transport Format Combination (TFC) (29)5.20 Transport Format Combination Set (29)5.21 Transport Format Combination Set Identity (29)5.22 Transport Format Combination Subset (29)5.23 Transport Format Set (29)5.24 UL Transport channel information common for all transport channels (30)6 物理信道信息元素 (30)6.1 AC-to-ASC mapping (30)6.2 AICH Info (30)6.3 AICH Power offset (30)6.4 Allocation period info (30)6.5 Alpha (30)6.6 ASC Setting (30)6.7 Void (31)6.8 CCTrCH power control info (31)6.9 Cell parameters Id (31)6.10 Common timeslot info (31)6.11 Constant value (31)6.12 CPCH persistence levels (31)6.13 CPCH set info (31)6.14 CPCH Status Indication mode (31)6.15 CSICH Power offset (32)6.16 Default DPCH Offset Value (32)6.17 Downlink channelisation codes (32)6.18 Downlink DPCH info common for all RL (32)6.19 Downlink DPCH info common for all RL Post (32)6.20 Downlink DPCH info common for all RL Pre (32)6.21 Downlink DPCH info for each RL (32)6.22 Downlink DPCH info for each RL Post (33)6.23 Downlink DPCH power control information (33)6.24 Downlink information common for all radio links (33)6.25 Downlink information common for all radio links Post (33)6.26 Downlink information common for all radio links Pre (33)6.27 Downlink information for each radio link (33)6.28 Downlink information for each radio link Post (33)6.29 Void (33)6.30 Downlink PDSCH information (33)6.31 Downlink rate matching restriction information (34)6.32 Downlink Timeslots and Codes (34)6.33 DPCH compressed mode info (34)6.34 DPCH Compressed Mode Status Info (34)6.35 Dynamic persistence level (34)6.36 Frequency info (34)6.37 Individual timeslot info (35)6.38 Individual Timeslot interference (35)6.39 Maximum allowed UL TX power (35)6.40 Void (35)6.41 Midamble shift and burst type (35)6.42 PDSCH Capacity Allocation info (35)6.43 PDSCH code mapping (36)6.44 PDSCH info (36)6.45 PDSCH Power Control info (36)6.46 PDSCH system information (36)6.47 PDSCH with SHO DCH Info (36)6.48 Persistence scaling factors (36)6.49 PICH Info (36)6.50 PICH Power offset (37)6.51 PRACH Channelisation Code List (37)6.52 PRACH info (for RACH) (37)6.53 PRACH partitioning (37)6.54 PRACH power offset (37)6.55 PRACH system information list (37)6.56 Predefined PhyCH configuration (38)6.57 Primary CCPCH info (38)6.58 Primary CCPCH info post (38)6.59 Primary CCPCH TX Power (38)6.60 Primary CPICH info (38)6.61 Primary CPICH Tx power (38)6.62 Primary CPICH usage for channel estimation (38)6.63 PUSCH info (38)6.64 PUSCH Capacity Allocation info (38)6.65 PUSCH power control info (39)6.66 PUSCH system information (39)6.67 RACH transmission parameters (39)6.68 Radio link addition information (39)6.69 Radio link removal information (39)6.70 SCCPCH Information for FACH (39)6.71 Secondary CCPCH info (39)6.72 Secondary CCPCH system information (40)6.73 Secondary CPICH info (40)6.74 Secondary scrambling code (40)6.75 SFN Time info (40)6.76 SSDT cell identity (40)6.77 SSDT information (40)6.78 STTD indicator (40)6.79 TDD open loop power control (41)6.80 TFC Control duration (41)6.81 TFCI Combining Indicator (41)6.82 TGPSI (41)6.83 Time info (41)6.84 Timeslot number (41)6.85 TPC combination index (41)6.86 TSTD indicator (41)6.87 TX Diversity Mode (41)6.88 Uplink DPCH info (41)6.89 Uplink DPCH info Post (42)6.90 Uplink DPCH info Pre (42)6.91 Uplink DPCH power control info (42)6.92 Uplink DPCH power control info Post (42)6.93 Uplink DPCH power control info Pre (42)6.94 Uplink Timeslots and Codes (42)6.95 Uplink Timing Advance (42)6.96 Uplink Timing Advance Control (43)7 测量信息元素 (43)7.1 Additional measurements list (43)7.2 Cell info (43)7.3 Cell measured results (43)7.4 Cell measurement event results (44)7.5 Cell reporting quantities (44)7.6 Cell synchronization information (44)7.7 Event results (44)7.8 FACH measurement occasion info (45)7.9 Filter coefficient (45)7.10 HCS Cell re-selection information (45)7.11 HCS neighboring cell information (45)7.12 HCS Serving cell information (45)7.13 Inter-frequency cell info list (46)7.14 Inter-frequency event identity (46)7.15 Inter-frequency measured results list (46)7.16 Inter-frequency measurement (46)7.17 Inter-frequency measurement event results (47)7.18 Inter-frequency measurement quantity (47)7.19 Inter-frequency measurement reporting criteria (47)7.20 Inter-frequency measurement system information (47)7.21 Inter-frequency reporting quantity (47)7.22 Inter-frequency SET UPDATE (48)7.23 Inter-RAT cell info list (48)7.24 Inter-RAT event identity (48)7.25 Inter-RAT info (48)7.26 Inter-RAT measured results list (48)7.27 Inter-RAT measurement (49)7.28 Inter-RAT measurement event results (49)7.29 Inter-RAT measurement quantity (49)7.30 Inter-RAT measurement reporting criteria (49)7.31 Inter-RAT measurement system information (50)7.32 Inter-RAT reporting quantity (50)7.33 Intra-frequency cell info list (50)7.34 Intra-frequency event identity (50)7.35 Intra-frequency measured results list (50)7.36 Intra-frequency measurement (50)7.37 Intra-frequency measurement event results (51)7.38 Intra-frequency measurement quantity (51)7.39 Intra-frequency measurement reporting criteria (51)7.40 Intra-frequency measurement system information (51)7.41 Intra-frequency reporting quantity (52)7.42 Intra-frequency reporting quantity for RACH reporting (52)7.43 Maximum number of reported cells on RACH (52)7.44 Measured results (52)7.45 Measured results on RACH (52)7.46 Measurement Command (52)7.47 Measurement control system information (53)7.48 Measurement Identity (53)7.49 Measurement reporting mode (53)7.50 Measurement Type (53)7.51 Measurement validity (53)7.52 Observed time difference to GSM cell (53)7.53 Periodical reporting criteria (53)7.54 Primary CCPCH RSCP info (54)7.55 Quality measured results list (54)7.56 Quality measurement (54)7.57 Quality measurement event results (54)7.58 Quality measurement reporting criteria (54)7.59 Quality reporting quantity (54)7.60 Reference time difference to cell (54)7.61 Reporting Cell Status (55)7.62 Reporting information for state CELL_DCH (55)7.63 SFN-SFN observed time difference (55)7.64 Time to trigger (55)7.65 Timeslot ISCP info (55)7.66 Traffic volume event identity (55)7.67 Traffic volume measured results list (55)7.68 Traffic volume measurement (55)7.69 Traffic volume measurement event results (56)7.70 Traffic volume measurement object (56)7.71 Traffic volume measurement quantity (56)7.72 Traffic volume measurement reporting criteria (56)7.73 Traffic volume measurement system information (56)7.74 Traffic volume reporting quantity (56)7.75 UE internal event identity (56)7.76 UE internal measured results (57)7.77 UE internal measurement (57)7.78 UE internal measurement event results (57)7.79 UE internal measurement quantity (57)7.80 UE internal measurement reporting criteria (57)7.81 Void (58)7.82 UE Internal reporting quantity (58)7.83 UE Rx-Tx time difference type 1 (58)7.84 UE Rx-Tx time difference type 2 (58)7.85 UE Transmitted Power info (58)7.86 UE positioning Ciphering info (58)7.87 UE positioning Error (58)7.88 UE positioning GPS acquisition assistance (59)7.89 UE positioning GPS almanac (59)7.90 UE positioning GPS assistance data (59)7.91 UE positioning GPS DGPS corrections (59)7.92 UE positioning GPS ionospheric model (59)7.93 UE positioning GPS measured results (59)7.94 UE positioning GPS navigation model (60)7.95 UE positioning GPS real-time integrity (60)7.96 UE positioning GPS reference time (60)7.97 UE positioning GPS UTC model (61)7.98 UE positioning IPDL parameters (61)7.99 UE positioning measured results (61)7.100 UE positioning measurement (61)7.101 UE positioning measurement event results (61)7.102 Void (62)7.103 UE positioning OTDOA assistance data for UE-assisted (62)7.104 Void (62)7.105 UE positioning OTDOA measured results (62)7.106 UE positioning OTDOA neighbor cell info (62)7.107 UE positioning OTDOA quality (63)7.108 UE positioning OTDOA reference cell info (63)7.109 UE positioning position estimate info (64)7.110 UE positioning reporting criteria (64)7.111 UE positioning reporting quantity (64)7.112 T ADV info (65)8 其它信息元素 (65)8.1 BCCH modification info (65)8.2 BSIC (65)8.3 CBS DRX Level 1 information (65)8.4 Cell Value tag (65)8.5 Inter-RAT change failure (65)8.6 Inter-RAT handover failure (66)8.7 Inter-RAT UE radio access capability (66)8.8 Void (66)8.9 MIB Value tag (66)8.10 PLMN Value tag (66)8.11 Predefined configuration identity and value tag (66)8.12 Protocol error information (66)8.13 References to other system information blocks (66)8.14 References to other system information blocks and scheduling blocks (67)8.15 Rplmn information (67)8.16 Scheduling information (67)8.17 SEG COUNT (67)8.18 Segment index (67)8.19 SIB data fixed (67)8.20 SIB data variable (67)8.21 SIB type (67)8.22 SIB type SIBs only (67)9 ANSI-41 Information elements (68)10 Multiplicity values and type constraint values (68)信息元素功能性定义消息是由多个信息元素组合而成,信息元素根据其功能的不同划分为:核心网域信息元素、UTRAN 移动信息元素、UE 信息元素、无线承载信息元素、传输信道信息元素、物理信道信息元素和测量信息元素。

最小加权熵支撑树图像边缘提取方法

最小加权熵支撑树图像边缘提取方法

杨方方;陈秀宏

【期刊名称】《计算机工程与应用》

【年(卷),期】2009(045)010

【摘要】提出了一种新的彩色图像边界提取的方法,以色彩图像直方图中搜索到的峰值作为聚类中心,根据彩色图像像素结构的特点,首先计算区域内相邻像素点之间对应的向量的欧式距离,然后构造该区域内的最小支撑树,计算相应的加权熵值确定分割阈值,最后结合向量排序统计,将排序的结果按照灰度值进行分类进行输出,实验证明了这种方法的有效性.

【总页数】3页(P182-183,198)

【作者】杨方方;陈秀宏

【作者单位】江南大学,信息工程学院,江苏,无锡,214122;江南大学,信息工程学院,江苏,无锡,214122

【正文语种】中文

【中图分类】TP391.41

【相关文献】

1.一种加权最小熵的ISAR自聚焦算法 [J], 徐刚;杨磊;张磊;李亚超;邢孟道

2.基于最小熵的自适应加权包络对齐算法 [J], 管志强;陈庆元

3.基于决策熵的决策树规则提取方法 [J], 孙林;徐久成;马媛媛

4.基于加权最小二乘的变流器杂散电感提取方法 [J], 朱艺锋;田野;郑景乐

5.多先验加权最小交叉熵图象重建算法 [J], 朱杨明;庄天戈

因版权原因,仅展示原文概要,查看原文内容请购买。

生物统计识别方法,用于获取生物统计数据以实施此生物统计识别方

专利名称:生物统计识别方法,用于获取生物统计数据以实施此生物统计识别方法的便携式电子设备和电子设备专利类型:发明专利

发明人:D·普拉卡

申请号:CN01809258.6

申请日:20010306

公开号:CN1427983A

公开日:

20030702

专利内容由知识产权出版社提供

摘要:本发明涉及一种生物统计识别方法,包括步骤:采集生物统计数据;分析产生当前签名的所述数据;将所述当前签名与基准签名比较。

本发明的特征在于:所述方法还包括步骤:验证该当前签名的起源;确定该签名是否确实是在采集阶段所获得的生物统计数据的分析结果。

本发明还涉及一种便携式电子设备和用于获得实施该方法的生物统计数据的设备。

申请人:格姆普拉斯公司

地址:法国热姆诺

国籍:FR

代理机构:中国专利代理(香港)有限公司

更多信息请下载全文后查看。

【精品】转录组RNAseq术语解释

【关键字】精品RNA-Seq名词解释1.index测序的标签,用于测定混合样本,通过每个样本添加的不同标签进行数据区分,鉴别测序样品。

2.碱基质量值(Quality Score或Q-score)是碱基识别(Base Calling)出错的概率的整数映射。

碱基质量值越高表明碱基识别越可靠,碱基测错的可能性越小。

3.Q30碱基质量值为Q30代表碱基的精确度在99.9%。

4.FPKM(Fragments Per Kilobase of transcript per Million fragments mapped)每1百万个map上的reads中map到外显子的每1K个碱基上的fragment个数。

计算公式为公式中,cDNA Fragments 表示比对到某一转录本上的片段数目,即双端Reads数目;Mapped Reads(Millions)表示Mapped Reads总数,以10为单位;Transcript Length(kb):转录本长度,以kb个碱基为单位。

5.FC(Fold Change)即差异表达倍数。

6.FDR(False Discovery Rate)即错误发现率,定义为在多重假设检验过程中,错误拒绝(拒绝真的原(零)假设)的个数占所有被拒绝的原假设个数的比例的期望值。

通过控制FDR来决定P值的阈值。

7.P值(P-value)即概率,反映某一事件发生的可能性大小。

统计学根据显著性检验方法所得到的P 值,一般以P<0.05为显著,P<0.01为非常显著,其含义是样本间的差异由抽样误差所致的概率小于0.05或0.01。

8.可变剪接(Alternative splicing)有些基因的一个mRNA前体通过不同的剪接方式(选择不同的剪接位点)产生不同的mRNA剪接异构体,这一过程称为可变剪接(或选择性剪接,alternative splicing)。

可变剪接是调节基因表达和产生蛋白质组多样性的重要机制,是导致真核生物基因和蛋白质数量较大差异的重要原因。

FOSAN富信电子 三级管 2N5401-产品规格书

安徽富信半导体科技有限公司ANHUI FOSAN SEMICONDUCTOR TECHNOLOGY CO.,LTD.2N5401 TO-92Bipolar Transistor双极型三极管▉Features特点PNP High Voltage高压▉Absolute Maximum Ratings最大额定值Characteristic特性参数Symbol符号Rat额定值Unit单位Collector-Base Voltage集电极基极电压V CBO-160V Collector-Emitter Voltage集电极发射极电压V CEO-150V Emitter-Base Voltage发射极基极电压V EBO-5V Collector Current集电极电流I C-600mA Power dissipation耗散功率P C(T a=25℃)625mW Thermal Resistance Junction-Ambient热阻RΘJA200℃/WJunction and Storage TemperatureT J,T stg-55to+150℃结温和储藏温度■Device Rank产品分档Rank档位A BH FE(2)Range100-200200-300ANHUI FOSAN SEMICONDUCTOR TECHNOLOGY CO.,LTD.2N5401■ElectricalCharacteristics 电特性(T A =25℃unless otherwise noted 如无特殊说明,温度为25℃)Characteristic 特性参数Symbol 符号Min 最小值Type 典型值Max 最大值Unit 单位Collector-Base Breakdown V oltage集电极基极击穿电压(I C =-100µA ,I E =0)BV CBO -160——V Collector-Emitter Breakdown Voltage集电极发射极击穿电压(I C =-1mA ,I B =0)BV CEO -150——V Emitter-Base Breakdown V oltage发射极基极击穿电压(I E =-10µA ,I C =0)BV EBO -5——V Collector-Base Leakage Current集电极基极漏电流(V CB =-160V ,I E =0)I CBO ——-100nA Collector-Emitter Leakage Current集电极发射极漏电流(V CE =-120V ,I B =0)I CEO ——-100nA Emitter-Base Leakage Current发射极基极漏电流(V EB =-5V ,I C =0)I EBO ——-100nADC Current Gain直流电流增益(V CE =-5V ,I C =-1mA)H FE (1)80——DC Current Gain直流电流增益(V CE =-5V ,I C =-10mA)H FE (2)100—300DC Current Gain直流电流增益(V CE =-5V ,I C =-100mA)H FE (3)50——Collector-Emitter Saturation Voltage集电极发射极饱和压降(I C =-10mA ,I B =-1mA)(I C =-50mA ,I B =-5mA)V CE(sat)——-0.2-0.5VBase-Emitter Saturation V oltage基极发射极饱和压降(I C =-10mA ,I B =-1mA)(I C =-50mA ,I B =-5mA)V BE(sat)——-1-1V Transition Frequency特征频率(V CE =-5V ,I C =-10mA)f T 100——MH Z Output Capacitance输出电容(V CB =-5V ,I E =0,f=1MH Z )C ob—6—pFANHUI FOSAN SEMICONDUCTOR TECHNOLOGY CO.,LTD.2N5401■Typical Characteristic Curve典型特性曲线ANHUI FOSAN SEMICONDUCTOR TECHNOLOGY CO.,LTD.2N5401■Dimension外形封装尺寸。

MCC电路保护器说明书

FeaturesMaximum Ratings8.0 AmpSchottky Rectifier 20 to 100 VoltsElectrical Characteristics @ 25°C Unless Otherwise Specified•Operating Junction Temperature Range: -55⁰C to +150⁰C •Storage Temperature Range: -55⁰C to +150⁰C•High Current Capability •Low Forward Voltage•For Surface Mount Application•Lead Free Finish/RoHS Compliant(Note 1) ("P" Suffix D esignates Compliant. See O rdering I nformation)•Epoxy Meets UL 94 V-0 Flammability Rating •Moisture Sensitivity Level 1•Halogen Free. “Green” Device (Note 2)SK845L SK84545V 31.5V 45V SK835L SK83535V 24.5V 35V SK84L SK8440V 28V 40V SK82L SK8220V 14V 20V SK83L SK8330V 21V 30V MCC Part Number Device Marking MaximumRecurrent Peak Reverse VoltageMaximumRMS VoltageMaximum DCBlockingVoltageTypical Junction CapacitanceC J400pFMeasured at 1.0MHz,V R =4.0VMaximum DC Reverse Current a t Rated DC Blocking Voltage I R0.1m A 10m A T J =25⁰C ;T J =100⁰CPeak Forward Surge CurrentI FSM200A8.3ms,H alf S ineV F0.65V I F M =8.0A;Average Forward CurrentI F(AV)8.0A T L =95⁰C Maximum Instantaneous Forward Voltage0.80V Note:1.High Temperature Solder Exemptions Applied, S ee EU Directive Annex 7a .2.Halogen free "Green” products are defined as those which contain <900ppm bromine,<900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.3.Mounted on P.C.B. With 0.6" x 0.6" (16 mm x 16 mm) Copper Pad AreasSK82L-86L SK88L-810L T J =25⁰C SK86L SK88L SK810LSK86SK88SK81060V 60V 80V 80V 100V100V42V 56V 70V•Typical Thermal Resistance (Note 3) : 50o C/W Junction to Ambient •Typical Thermal Resistance (Note 3) : 18o C/W Junction to LeadCurve Characteristics25125150012345678910A v e r a g e F o r w a r d C u r r e n t (A)Fig. 1 - Forward Current Derating Curve5075100Lead Temperature (°C)1100255075100125150175200225P e a k F o r w a r d S u r g e C u r r e n t (A)Fig. 2 - Maximum Non-Repetitive Peak Forward Surge10Number of Cycles at 60 Hz0.020.050.20.525200.010.11100.00.10.20.30.40.50.60.70.80.91.0Instantaneous Forward Voltage (V)I n s t a n t a n e o u s F o r w a r d C u r r e n t (A )Fig. 3 - Typical Instantaneous Forward Characteristics0.020.050.20.525200.010.1110Instantaneous Forward Voltage (V)I n s t a n t a n e o u s F o r w a r d C u r r e n t (A )Fig. 4 - Typical Instantaneous Forward Characteristics110100100010000I n s t a n t a n e o u s R e v e r s e L e a k a g e C u r r e n t (μA )Fig. 5 - Typical Reverse Leakage CharacteristicsPercent of Rated Peak Reverse Voltage (%)0.1110100100010000I n s t a n t a n e o u s R e v e r s e L e a k a g e C u r r e n t (μA )Fig. 6 - Typical Reverse Leakage CharacteristicsPercent of Rated Peak Reverse Voltage (%)Ordering InformationDevice PackingPart Number-TP Tape&Reel: 3Kpcs/Reel。

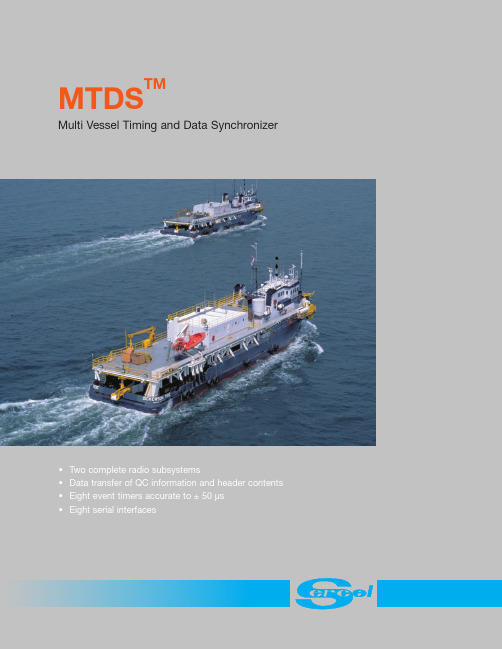

MTDS介绍

MTDS TMMulti Vessel Timing and Data Synchronizer•Two complete radio subsystems•Data transfer of QC information and header contents •Eight event timers accurate to ±50 µs•Eight serial interfacesThe MTDS has eight event timers as well as eight serial interfaces that allow bi-directional information transfer between vessels. Data can contain GCS90 QC information, headerinformation from the navigation system,and acoustic source position data. Once the vessels are synchronized, there are eight event timers running on each MTDS in synchronization to control system start, fire commands, and timebreak.The MTDS contains two complete radio subsystems with synthesized receiver/transmitters that can be programmed from the operator’sconsole. One radio operates in the 216 -220 MHz band, while the other operates in the 478 - 482 MHz band. Sixteen contiguous frequencies are assigned based at 25 kHz spacing to allow some flexibility of operating frequency.MTDSTMThe MTDS provides autonomous timing synchronization for the seismic source and the recorder accurate to ±50 µs in multi-vessel operation. It transmits an analog signal,typically gun signature data, in real time from the source vessel to the recording rmation goes to the recording vessel to be processed as an auxiliary channelthrough the SYNTRAK aux box and is recorded along with the seismic data.SpecificationsTypical Range Line of sight Transmitter Power Output 10 watts, nominalOperating Frequencies 216, 478 MHz standard150 MHz available optionsEvent Synchronization Tolerance ± 50 µsRecommended OperatingTemperature Range 0°C (32°F) to 55° C (131°F)Maximum Humidity95% at 40°C, non condensingTimersEight independentDuration, each timer1 - 32,767 ms in 1-ms incrementsModelTMI 3600Backplane 9 ISA, 3 PCI and 2 CPU slots for 16-bit plug-in cards RAM32 Mbytes Hard Drive 1 GbyteDiskette Drive 1.44 Mbytes (3.5 in.)CD ROM Drive IDE 32XPower Supply250 Watts with auto-switching115/230 Vac (95-130 Vac or 180-264 Vac),47-63 Hz inputOperating SystemMicrosoft DOS 6.22CPUPentium processor (200 MHz), 32 Mbytes RAM, 128 Kbytes Static RAM, 25 MHz ClockBus speed,enhanced IDE hard drive 3.5-inch diskette drive, CD ROM.Serial Ports COM 1 (for mouse)COM2 (unassigned)Parallel Ports LPT1, bidirectional Video Card VGA-compatibleIO CardSIIG ®I/O Professional TM, two high-speed (16550 device) serial ports,one DB-9 serial connector on card edge, one 10-pin connector on card,compatible ECP-compliant enhanced parallel Port (EPP), DB-25 parallel connector on card edgeSerial Extender Card92-109124 DigiBoard, eight serial ports, DB-25 connectors, Data Terminal Equipment.Sercel-France16 rue de Bel-AirB.P.439. 44474 CARQUEFOU CedexTelephone:(33) 2 40 30 11 81Fax:(33) 2 40 30 19 48E-mail:sales@sercel.frS.A. au capital de 2 000000€Siège Social: 16 rue de Bel Air 44470 Carquefou. R.C.S. Nantes B.378.040.497. Code APE 332 B Sercel Incorporated-USA17200 Park RowHOUSTON Texas 77084-5935Telephone:(1) 281492 6688 Fax:(1) 281579 7505 E-mail:sales.hou@Printed in France. © Sercel 07/01 - Photos :courtesy of SchlumbergerInformation subject to change without notice。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Estabilizador de Arcillas

CALIPER Descripción del Producto

Cáliper es un compuesto asfáltico especialmente diseñado para el efectivo control de lutitas.

Especificaciones Técnicas

Forma: Sólido

Apariencia: Polvo fino

Color: Marrón oscuro a negro

Densidad: 1,05 ± 0,05 gr/cc

Solubilidad en agua: Dispersable

Aplicación del Producto

Cáliper es dispersable tanto en agua dulce como en agua de mar. Se recomienda adicionar emulsificantes para una mejor dispersibilidad en el agua. Combate la desintegración de las arcillas tanto física como químicamente.

Por el carácter electronegativo de sus partículas, éstas se adhieren químicamente a los bordes rotos de las microfacturas en el cuerpo de la arcilla donde macro aniones previenen la entrada de fluido, reduciendo de esta manera la probabilidad del desmoronamiento de arcillas.

Estabilizador de Arcilla Cáliper - Página 2/2

Otros beneficios resultantes del uso de Cáliper son:

•Reduce el esfuerzo de torsión y la fricción.

•Mejora el control de filtrado API y HTHP.

•Mejora la calidad del revoque.

•Inhibe la dispersión de sólidos de perforación.

Tratamiento Recomendado

Como tratamiento preventivo de arcillas desmoronables 10 a 14 kg/m3 Cuando el desmoronamiento de arcillas ha comenzado 11 a 20 kg/m3 Para reducir la torsión y la fricción 6 a 15 kg/m3 Para mejorar el filtrado 6 a 15 kg/m3

Presentación

Bolsas de 25 kilos。