HFRFID实验手册

实验6 HF高频RFID通信协议实验-V20170317

实验6 HF高频RFID通信协议实验-V201703171.实验目的掌握高频读卡器的通讯协议;掌握高频模块工作原理;掌握本平台高频模块的操作过程;2.实验设备硬件:RFID实验箱套件,电脑等;软件:Keil,串口调试助手;STC_ISP软件:配套光盘\第三方应用软件\STC_ISP异或计算小软件:配套光盘\第三方应用软件\异或计算小软件源码路径:配套光盘\源代码\RFID基础实验\实验 6 HF高频RFID通信协议实验-V20170317Hex路径:配套光盘\源代码\RFID基础实验\实验6 HF高频RFID通信协议实验-V20170317\out3.实验原理3.1 高频RFID系统典型的高频HF(13.56MHz)RFID系统包括阅读器(Reader)和电子标签(Tag,也称应答器Responder)。

电子标签通常选用非接触式IC卡,又称智能卡,可读写,容量大,有加密功能,数据记录可靠。

IC卡相比ID卡而言,使用更方便,目前已经大量使用在校园一卡通系统、消费系统、考勤系统、公交消费系统等。

目前市场上使用最多的是PHILIPS的Mifare系列IC卡。

读写器(也称为“阅读器”)包含有高频模块(发送器和接收器)、控制单元以及与卡连接的耦合元件。

由高频模块和耦合元件发送电磁场,以提供非接触式IC 卡所需要的工作能量以及发送数据给卡,同时接收来自卡的数据。

此外,大多数非接触式IC卡读写器都配有上传接口,以便将所获取的数据上传给另外的系统(个人计算机、机器人控制装置等)。

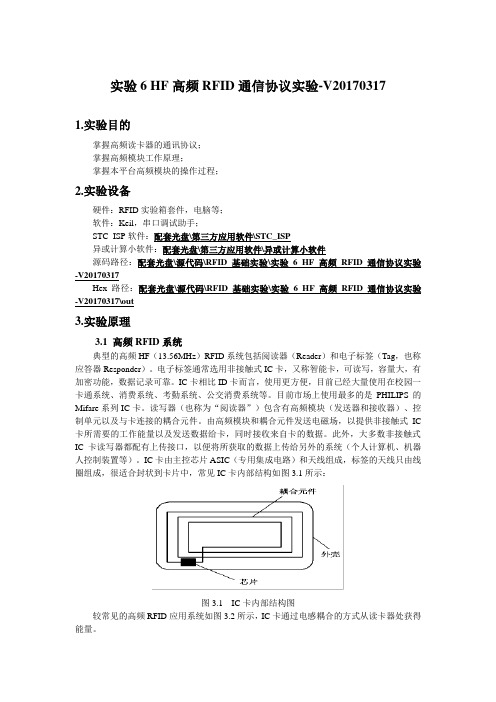

IC卡由主控芯片ASIC(专用集成电路)和天线组成,标签的天线只由线圈组成,很适合封状到卡片中,常见IC卡内部结构如图3.1所示:图3.1 IC卡内部结构图较常见的高频RFID应用系统如图3.2所示,IC卡通过电感耦合的方式从读卡器处获得能量。

图3.2 常见高频RFID应用系统组成下面以典型的IC卡MIARE 1为例,说明电子标签获得能量的整个过程。

RFID原理与应用-HF中ISO15693协议命令的验证和操作(word文档良心出品)

通过这次实验,熟悉了ISO15693协议命令的三种操作模式和标签六种巡查模式,学会了如何在射频场范围内的电子标签,截取标签的制造商、UID、DSFID等信息,顺利完成了实验。

实验报告书

课程名:《RFID原理与应用》

题目:实验四HF ISO15693协议命令

实验类别【验证和测试】

班级:

学号:

姓名:

一、实验内容或题目

HF ISO15693协议命令

二、实验目的与要求

(1)熟悉ISO15693协议命令的三种操作模式;

(2)熟悉标签六种巡查模式

(3)标签数据块操作;

(4)检测射频场范围内的电子标签,截取标签的制造商、UID、DSFID等信息。

(3)读取卡中存储的数据。

(4)向指定块写入数据。

(5)读取的多个数据块的内容,验证最多可以读取几个块。

5,分别改变标签所处的状态,如进入“静默状态”(Quite)、“进入选定状态”(Selected)、“返回准备状态”(Ready)。

6,检测射频场范围内的电子标签,截取标签的制造商、UID、DSFID等信息。

三、实验步骤与截图

实验项目:

1,连接读写器(打开端口)。

2,读写器自定义命令。

(1)获取读写器信息

(2)打开射频

(3)修改读写器地址

(4)设置读写器模式

(5)设置蜂鸣器、LED

3,对标签六种巡查模式进行检测

(1)单张询查

(2)询查命令带AFI(单张)

(3)多张询查

(4)继续询查(多张)

(5)新的询查带AFI(多张)

(6)多张继续询查带AFI

4,标签数据块操作

执行询查命令后,对ቤተ መጻሕፍቲ ባይዱ取了UID的标签存储的数据进行修改。

RFID教学实验箱实验内容初稿(实验一添加实验步骤说明)(精)

13.56MHZ HF多协议读写器实验一、基于符合ISO/IEC 14443 A、B及 ISO/IEC 15693 标准协议的寻卡(查询)及读取UID号操作实验二、基于符合ISO/IEC 14443A 标准协议的_Request、Anticoll、Select、Halt、Authentication 操作实验三、基于符合ISO/IEC 14443A标准协议的M1卡认证及读写数据操作实验四、基于符合ISO/IEC 14443B 标准协议的Request、Halt、Deselect操作实验五、基于符合ISO/IEC 14443B 标准协议的AT88RF020卡认证及读写数据操作实验六、基于符合ISO/IEC 14443B 标准协议的SR176卡认证及读写数据操作实验七、基于符合ISO/IEC 14443A 协议的Verayo卡的256/512位读卡器认证标签、读写块、internal、获取随机数、写口令到标签等双向认证操作实验八、基于符合ISO/IEC 14443A 标准协议的verayo卡带认证的读写标签数据操作实验九、基于符合ISO 15693 标准协议的Inventory16、Inventory、Stay_Quiet、Select指令操作实验十、基于符合ISO 15693 标准协议的Reset_To_Ready、Read、Write、Lock、Write_AFI、Lock_AFI、Write_DSFID、Lock_DSFID、Get_System_Information、Get_Multiple_Block_Security指令操作实验十一、基于符合ISO/IEC 7816 标准协议的CPU卡RATS指令操作实验十二、CPU卡操作系统FMCOS的发卡指令操作(1):选择文件、取响应数、取随机数、外部认证实验十三、CPU卡操作系统FMCOS的发卡指令操作(2):擦除DF、建立文件、增加或修改密钥实验十四、CPU卡操作系统FMCOS的发卡指令操作(3):内部认证、读二进制文件、写二进制文件、写记录文件实验十五、CPU卡操作系统FMCOS的消费指令操作(1):验证PIN、初初化交易、读余额、圈存实验十六、CPU卡操作系统FMCOS的消费指令操作(2):消费/取现/圈提、取交易认证、重装/修改PIN2、综合性实验(1)实验项目实验一、基于符合ISO/IEC 14443 A、B及 ISO/IEC 15693 标准协议的寻卡(查询)及读取UID号操作实验二、基于符合ISO/IEC 14443A 标准协议的_Request、Anticoll、Select、Halt、Authentication操作实验三、基于符合ISO/IEC 14443A标准协议的M1卡认证及读写数据操作实验四、基于符合ISO/IEC 14443B 标准协议的Request、Halt、Deselect 操作实验五、基于符合ISO/IEC 14443B 标准协议的AT88RF020卡认证及读写数据操作实验六、基于符合ISO/IEC 14443B 标准协议的SR176卡认证及读写数据操作实验七、基于符合ISO/IEC 14443A 协议的Verayo卡的256/512位读卡器认证标签、读写块、internal、获取随机数、写口令到标签等双向认证操作实验八、基于符合ISO/IEC 14443A 标准协议的verayo卡带认证的读写标签数据操作实验九、基于符合ISO 15693 标准协议的Inventory16、Inventory、Stay_Quiet、Select指令操作实验十、基于符合ISO 15693 标准协议的Reset_To_Ready、Read、Write、Lock、Write_AFI、Lock_AFI、Write_DSFID、Lock_DSFID、Get_System_Information、Get_Multiple_Block_Security指令操作(2)实验方案实验一、基于符合ISO/IEC 14443 A、B及 ISO/IEC 15693 标准协议的寻卡(查询)及读取UID号操作实验目的1、学习和了解13.56MHZ 非接触IC技术。

RFID原理与应用-HF中ISO15693协议命令的验证和操作(word文档良心出品)

课程名:《RFID原理与应用》

题目:实验四HF ISO15693协议命令

实验类别【验证和测试】

班级:

学号:

姓名:

一、实验内容或题目

HF ISO15693协议命令

二、实验目的与要求

(1)熟悉ISO15693协议命令的三种操作模式;

(2)熟悉标签六种巡查模式

(3)标签数据块操作;

(4)检测射频场范围内的电子标签,截取标签的制造商、UID、DSFID等信息。

四、实验遇到的问题和体会

通过这次实验,熟悉了ISO15693协议命令的三种操作模式和标签六种巡查模式,学会了如何在射频场范围内的电子标签,截取标签的制造商、UID、DSFID等信息,顺利完成了实验。

三、实验步骤与截图

实验项目:

1,连接读写器(打开端口)。

2,读写器自定义命令。

(1)获取读写器信息

(2)打开射频

(3)修改读写器地址

(4)设置读写器模式

(5)设置蜂鸣器、LED

3,对标签六种巡查模式进行检测

(1)单张询查

(2)询查命令带AFI(单张)

(3)多张询查

(4)继续询查(多张)Fra bibliotek(5)新的询查带AFI(多张)

(6)多张继续询查带AFI

4,标签数据块操作

执行询查命令后,对获取了UID的标签存储的数据进行修改。

(1)获取标签生产厂商、单个数据块包含的字节个数和标签的存储容量以及标签的写类型。

(2)查看标签的写类型,如果该电子标签可以操作,兼容A、B类写类型的标签尝试修改“数据块操作”框中的“标签写类型”、“最大块号”、“数据块大小”等信息。

(3)读取卡中存储的数据。

(4)向指定块写入数据。

RFID实验箱实验指导书整合版解析

广州飞瑞敖电子科技有限公司RFID实验箱实验指导书广州飞瑞敖电子科技有限公司注意:以*号开头实验为选作实验,如课时紧张,可跳过该实验它对综合实验的开展不会产生影响。

STM32F103VE单片机实验 (3)实验一开发环境的搭建及硬件测试实验 (4)实验二STM32工程建立 (8)实验三串口通讯实验 (28)实验四时钟中断 (33)实验五外部中断 (41)*实验六ADC采集 (45)*实验七SPI-Flash读写 (52)实验八LCD显示 (59)实验九触摸屏 (68)实验十UC/OSII LED 闪烁 (74)实验十一 UC/OSII任务挂起、恢复、删除 (81)实验十二 UCGUI 演示 (86)实验十三基于UCGUI的LED闪烁 (94)实验十四数码管 (99)RFID实验 (103)实验一 LF低频RFID实验 (103)实验二 HF高频RFID通信协议 (113)实验三 UHF特高频RFID实验 (126)实验四 2.4G有源RFID低功耗实验 (144)实验五 HF高频RFID应用 (153)实验六 2.4G 人员定位实验 (159)实验七Wi-Fi模块的使用 (163)STM32F103VE单片机实验写在最前面-为什么要学习STM32单片机?当老师和学生拿到该实验指导书的时候,难免会有这样的疑问,这个实验箱是RFID实验箱,我应该学习RFID的知识才对,为什么学习STM32单片机呢?对于这个问题的回答首先要从该款实验箱的设计初衷说起。

飞瑞敖电子科技有限公司的IOT-L02-03型RFID实验箱的设计初衷和教学重点是放在RFID技术的应用而非工作原理上。

STM32单片机做为实验箱的核心MCU,通过UART接口同时与四种RFID模块相连(当然了,同一时间内只会和一个模块形成通路,具体和哪个模块形成通路则是通过由三个二位选择开关来控制的),与此同时,STM32通过GPIO接口连接了丰富的外围设备如LED流水灯、数码管、液晶显示屏、蜂鸣器等。

实验7HF ISO15693协议操作

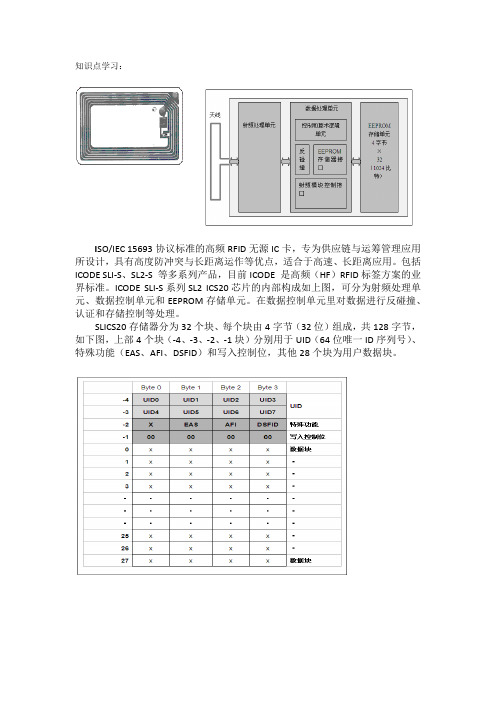

知识点学习:I SO/IEC 15693协议标准的高频RFID无源IC卡,专为供应链与运筹管理应用所设计,具有高度防冲突与长距离运作等优点,适合于高速、长距离应用。

包括ICODE SLI-S、SL2-S 等多系列产品,目前ICODE 是高频(HF)RFID标签方案的业界标准。

ICODE SLI-S系列SL2 ICS20芯片的内部构成如上图,可分为射频处理单元、数据控制单元和EEPROM存储单元。

在数据控制单元里对数据进行反碰撞、认证和存储控制等处理。

SLICS20存储器分为32个块、每个块由4字节(32位)组成,共128字节,如下图,上部4个块(-4、-3、-2、-1块)分别用于UID(64位唯一ID序列号)、特殊功能(EAS、AFI、DSFID)和写入控制位,其他28个块为用户数据块。

UID占用块-4和块-3共8个字节(64位),是厂商写入的世界唯一标签识别序列号,用户不可更改,在UID中包含厂商代码、产品分类代码和标签芯片生产序列代码,UID的代码构成如上图。

块-1是写入控制位,具体控制分配见上图,它可以控制每个数据块的写入和块-2(特殊功能块)每个字节的写入。

写入位1代表写入保护,且不可再修改控制位。

特殊功能EAS(Electronic Article Surveillance,电子防盗系统)主要用来防止物品被盗,标签管理者可以设置(EAS=1)和清除(EAS=0)EAS标识,当设置有EAS标识的标签通过读写器的作用范围时,读写器会识别EAS标识,发出警报。

EAS的数据结构如下图,EAS的LSB的第一位(e位)写1代表EAS标示有效,写0代表清除EAS标示,其他位无效。

特殊功能AFI(Application Family Idenfifier,应用族标识符),可事先规定应用族代码并写入AFI字节,在处理多个标签的时候进行分类处理。

例如在物流中心处理大量货物时,可根据标签上的AFI应用族标识符来区分是出口货物还是内销货物。

实验7 基于WiFi的HF高频RFID实验-V201700317

实验7 基于WiFi的HF高频RFID实验-V201703171.实验目的掌握WiFi模块的配置和使用方法;掌握基于WiFi的阅读器操作过程;2.实验设备硬件:实验箱,电脑等;软件:HLK-RM04_串口配置工具,TCP&UDP测试工具软件;HLK-RM04用户手册V1.1.pdf路径:配套光盘\第三方应用软件\WiFi配置工具TCP&UDP测试工具安装与使用说明文档路径:配套光盘\第三方应用软件\TCP&UDP 测试工具雷凌USB无线网卡安装说明路径:配套光盘\第三方应用软件\雷凌usb无线网卡光盘源码路径:配套光盘\源代码\RFID基础实验\实验7 基于WiFi的HF高频RFID实验-V20170317Hex路径:配套光盘\源代码\RFID基础实验\实验7 基于WiFi的HF高频RFID实验-V20170317\out3.实验原理本实验通过WiFi模块实现PC与阅读器的通信,原理如图3.1所示:图3.1 实验原理图将高频阅读器的串口连接到WiFi模块的串口。

WiFi模块工作模式设为串口转WiFi,并配置成无线AP模式。

实验中WiFi模块为TCP(也可以设成UDP)服务器,PC连接到AP点后再通过使用TCP&UDP测试工具软件建立一个TCP的客户端,去主动连接WiFi模块的本地IP地址。

这样PC与WiFi模块之间的通信数据会通过WiFi模块的串口传给阅读器,阅读器与WiFi模块之间通信数据也会通过WiFi模块传给PC,从而实现PC与阅读器的无线网络通信。

高频RFID协议、指令请参考之前的HF高频RFID实验,这里不再做阐述。

4.实验步骤4.1 高频RFID阅读器固件烧录第一步:打开配套光盘\源代码\RFID基础实验\实验7 基于WiFi的HF高频RFID实验-V20170317下的RC632开发.uvproj工程,打开main.c文件,查看系统初始化波特率设置,实验默认为9600,如不是,请更改,如图4.1所示:图4.1 更改波特率第二步:使用串口线连接PC和高频阅读器的DB9接头。

RFID相关实验实验指导书整合版(DOC)

RFID相关实验实验指导书整合版(DOC)⼴州飞瑞敖电⼦科技有限公司IOT-L01-05型物联⽹综合实验箱RFID相关实验指导书⼴州飞瑞敖电⼦科技有限公司IOT-L01-05型 (1)实验⼀ LF低频RFID实验 (2)⼀、实验⽬的 (2)⼆、实验设备 (2)三、实验原理 (2)四、实验过程 (5)实验⼆、HF⾼频RFID通信协议 (7)⼀、实验⽬的 (7)⼆、实验设备 (7)三、实验原理 (7)四、实验步骤 (15)实验三 UHF特⾼频RFID实验 (20)⼀、实验⽬的 (20)⼆、实验设备 (20)三、实验原理 (20)四、实验步骤 (26)实验四 2.4G有源RFID低功耗实验 (31)⼀、实验⽬的 (31)⼆、实验设备 (31)三、实验原理 (31)四、实验步骤 (34)实验⼀ LF低频RFID实验⼀、实验⽬的1.1了解ID卡内部存储结构1.2掌握符合ISO 18000-2标准的⽆源ID卡识别系统的⼯作原理1.3掌握符合ISO 18000-2标准的⽆源ID卡识别系统的⼯作流程1.4 掌握本平台ID模块的操作过程⼆、实验设备硬件:RFID实验箱套件,电脑等。

软件:Keil,串⼝调试助⼿。

三、实验原理3.1 低频RFID系统与ID卡低频RFID系统读卡器的⼯作频率范围⼀般从120KHz到134KHz。

该频段的波长⼤约为2500m,除了⾦属材料影响外,⼀般低频能够穿过任意材料的物品⽽不降低它的读取距离。

低频RFID系统使⽤ID卡,全称为⾝份识别卡(Identification Card),作为其电⼦标签。

ID卡是⼀种不可写⼊的感应卡,其内部唯⼀存储的数据是⼀个固定的ID卡编号,其记录内容(卡号)是由芯⽚⽣产⼚商封卡出⼚前⼀次性写⼊,封卡后不能更改,开发商只可读出卡号加以利⽤。

ID卡与我们通常使⽤磁卡⼀样,仅仅使⽤了“卡的号码”⽽已,卡内除了卡号外,⽆任何保密功能,其“卡号”是公开、裸露的。

⽬前市场上主要有台湾SYRIS的EM、美国HID、TI、MOTOROLA等各类ID卡。

RFID实验5 HF13.56MHz ISO 14443模块认证

(5)拖出一个 GroupBox,将 Text 属性改为“认证”,拖出一个 Label,将其 Text 属性改 为“地址块”,拖出两个 Button,分别将 Text 属性设置为“认证密钥 A”、“认证密钥 B”, 将对应 Name 属性设置为“AuthABtn”、“AuthBBtn”,拖出 3 个 TextBox 分别将其 Name 属 性设置为“txt_Address”、“txt_KeyA”、“txt_KeyB”

4.3.2 操作步骤

通过使用上位机软件与 RFID 高频 14443 模块下位机进行通信,完成对高频 14443 标签 的认证操作。

(1)打开上位机软件,启动 RFID 原理机的电源,用串口线建立通信连接。 (2)参照 4.1 节的步骤,读取卡片的 UID。将卡片放到识别区(如果连接了外接天 线,将卡片放置在天线旁边),在执行寻卡操作之前需要将串口(默认波特率为“ 115200”, 若改成其他值,可能造成无法正确接收到数据)打开并发送“请求所有”操作请求,最 后将卡号识别出来。 (3)选择操作的卡片,选择成功返回如图 4-11 所示的信息。

完成后的功能界面如图 4-16 所示。

图 4-16 认证密钥界面设计

第三步:编写代码实现功能(此处只附部分主要代码及解析)。 程序执行流程图如图 4-17 所示。

部分主要代码解析如下:

图 4-17 程序执行流程图

//认证操作 A 按钮事件(认证操作 B 按钮事件类似)

private void AuthABtn_Click(object sender, EventArgs e) {

RFID原理与应用-HF中ISO14443A协议命令的验证和操作

首先,读写器“以读写器中密钥存储区扇区号”为地址,读取存储在密钥存储区内的密钥,然后用该密钥证实待验证的电子标签扇区,如果该密钥与标签扇区上的密钥匹配,则证实成功,状态栏显示“Authentication2:执行成功”。否则显示验证失败。

9、对标签认证后对数据区的数据进行读写。

10、修改标签密码。

11、钱包操作。

实验报告书

课程名:《RFID原理与应用》

题目:实验五HF中ISO14443A协议命令的验证和操作

实验类别【验证和测试】

班级:

学号:

姓名:

一、实验内容或题目

熟悉满足ISO14443A协议命令的标签在读写器中的设置。

二、实验目的与要求

(1)了解ISO14443签进行休眠;

四、实验遇到的问题和体会

通过这次实验,了解ISO14443A的协议命令,熟悉标签的防冲突设置,能对电子标签进行休眠和对电子标签进行钱包操作

1.非接触式智能卡ISO15693与ISO14443区别。

答:ISO14443标准中的非接触式智能卡的类型可以分为Type A和Type B(Type C—G目前已经暂时被列入ISO14443标准之外,等到5年之后再行复议)。通信速率为106kbit/s,它们的不同主要在于载波的调制深度及位的编码方式。TYPE A采用开关键控(On-Off keying)的Manchester编码,TYPE B采用NRZ-L(NRZ-L=Non-Return-to-Zero, for level不归零)的BPSK编码。TYPE B与TYPE A相比,具有传输能量不中断、速率更高、抗干扰能力列强的优点。RFID的核心是防冲撞技术,这也是和接触式IC卡的主要区别。ISO 14443-3规定了TYPE A和TYPE B的防冲撞机制。二者防冲撞机制的原理不同,前者是基于位冲撞检测协议,而TYPE B通信系列命令序列完成防冲撞。ISO 15693采用轮寻机制、分时查询的方式完成防冲撞机制。防冲撞机制使得同时处于读写区内的多张卡的正确操作成为可能,既方便了操作,也提高了操作的速度。

RFID实验指导书

RFID实验指导书适用所有对无线射频传感器感兴趣的学生xxx编写概述一、课程目的《RFID无线射频实验》是一门实践性很强的实验课程,为了学好这门课,每个学生须完成一定的实验实践作业。

通过本实验的实践操作训练,可以更好的了解RFID的基本功能和基本的使用方法,为以后深入的研究学习打下良好的基础。

本课程实验的目的是旨在使学生进一步扩展对无线射频方向理论知识的了解;培养学生的学习新技术的能力以及提高学生对该方向的兴趣与动手能力。

二、实验名称与学时分配三、实验要求1.问题分析充分地分析和理解问题本身,弄清要求做什么,包括功能要求、性能要求、设计要求和约束。

2.原理理解在按照教程执行过程当中,需要弄清楚每一个步骤为什么这样做,原理是什么。

3.实践测试按照要求执行每一步命令,仔细观察返回值,了解每项返回值表达什么意思,为什么有的卡片可以破解有的不可以。

三、实验考核实验报告应包括如下内容:1、实验原理描述:简述进行实验的原理是什么。

2、实验的操作过程:包括实验器材、实验流程的描述。

3、分析报告:实验过程中遇到的问题以及问题是否有解决方案。

如果有,请写明如何解决的;如果没有,请说明已经做过什么尝试,依旧没有结果导致失败。

最后简述产生问题的原因。

4、实验的体会以及可以讲该功能可以如何在其他地方发挥更强大的功能。

注:最后实验结果须附命令行回显截图四、实验时间总学时:6学时。

实验一高低频卡鉴别一、实验目的1、掌握RFID驱动等环境安装设置。

2、掌握如何通过读取电压高低来区分高低频。

二、实验要求1、认真阅读和掌握本实验的程序。

2、实际操作命令程序。

3、保存回显结果,并结合原理进行分析。

4、按照原理最后得出结果。

三、注意事项:命令在实行时,如果想停止,不能用平时的Ctrl+C或者ESC等常规结束按键(可能会造成未知损坏),只需要按下Promxmark3上的黑色按钮。

方形的为高频天线(Proxmark3HFAntenna13.56MHZ);圆形的为低频天线(Proxmark3LFAntenna125KHz/134KHz)四、实验内容1.安装驱动打开我的电脑》右键--属性—设备管理器》人体学输入设备这个“HID-compliantdevice”就是我们的proxmark3设备,选择“USB 人体学输入设备”一般是最下面那个,注意:不是“HID-compliantdevice”,更新驱动程序。

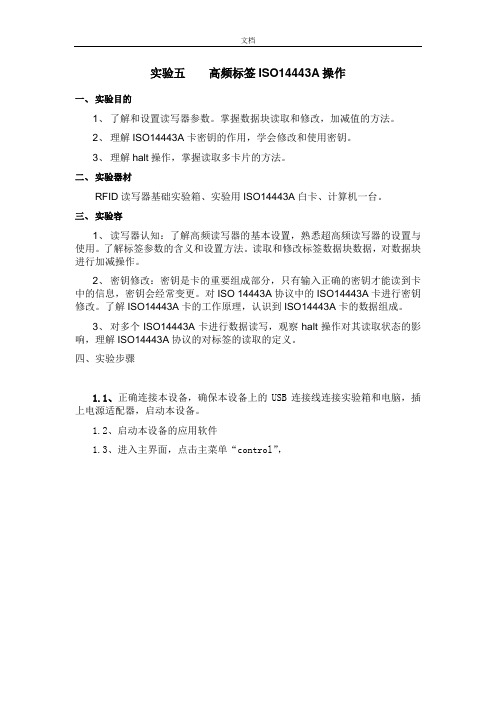

实验5HFISO14443A操作

实验五高频标签ISO14443A操作一、实验目的1、了解和设置读写器参数。

掌握数据块读取和修改,加减值的方法。

2、理解ISO14443A卡密钥的作用,学会修改和使用密钥。

3、理解halt操作,掌握读取多卡片的方法。

二、实验器材RFID读写器基础实验箱、实验用ISO14443A白卡、计算机一台。

三、实验容1、读写器认知:了解高频读写器的基本设置,熟悉超高频读写器的设置与使用。

了解标签参数的含义和设置方法。

读取和修改标签数据块数据,对数据块进行加减操作。

2、密钥修改:密钥是卡的重要组成部分,只有输入正确的密钥才能读到卡中的信息,密钥会经常变更。

对ISO 14443A协议中的ISO14443A卡进行密钥修改。

了解ISO14443A卡的工作原理,认识到ISO14443A卡的数据组成。

3、对多个ISO14443A卡进行数据读写,观察halt操作对其读取状态的影响,理解ISO14443A协议的对标签的读取的定义。

四、实验步骤1.1、正确连接本设备,确保本设备上的USB连接线连接实验箱和电脑,插上电源适配器,启动本设备。

1.2、启动本设备的应用软件1.3、进入主界面,点击主菜单“control”,1.4、选择下拉菜单中“Add HF Reader”,或右键点击主界面空白处,选择菜单中“add HF Reader”,1.5、选择串口(弹出的显示值即对应串口),点击ok,加载HF高频读写器模块1.6、如模块加载成功,则主界面会生成一个HF高频读写器模块1.7、选中HF 高频读写器模块,右键点击,获得右键菜单,菜单功能说明如下1.8、选中“Reader Settings and Diagnostics ”,进入HF 高频读写器参数设置界面,按图设置后关闭窗口。

知识学习A、高频HF的射频识别设备(高频读写器)工作于13.56MHz频段,系统通过天线线圈电感耦合来传输能量,通过电感耦合的方式磁场能量下降较快。

磁场信号具有明显的读取区域边界。

实验5HF ISO14443A操作

实验五高频标签ISO14443A操作一、实验目的1、了解和设置读写器参数。

掌握数据块读取和修改,加减值的方法。

2、理解ISO14443A卡密钥的作用,学会修改和使用密钥。

3、理解halt操作,掌握读取多张卡片的方法。

二、实验器材RFID读写器基础实验箱、实验用ISO14443A白卡、计算机一台。

三、实验内容1、读写器认知:了解高频读写器的基本设置,熟悉超高频读写器的设置与使用。

了解标签参数的含义和设置方法。

读取和修改标签数据块数据,对数据块进行加减操作。

2、密钥修改:密钥是卡的重要组成部分,只有输入正确的密钥才能读到卡中的信息,密钥会经常变更。

对ISO 14443A协议中的ISO14443A卡进行密钥修改。

了解ISO14443A卡的工作原理,认识到ISO14443A卡的数据组成。

3、对多个ISO14443A卡进行数据读写,观察halt操作对其读取状态的影响,理解ISO14443A协议的对标签的读取的定义。

四、实验步骤1.1、正确连接本设备,确保本设备上的USB连接线连接实验箱和电脑,插上电源适配器,启动本设备。

1.2、启动本设备的应用软件1.3、进入主界面,点击主菜单“control”,1.4、选择下拉菜单中“Add HF Reader”,或右键点击主界面空白处,选择菜单中“add HF Reader”,1.5、选择串口(弹出的显示值即对应串口),点击ok,加载HF高频读写器模块1.6、如模块加载成功,则主界面会生成一个HF高频读写器模块1.7、选中HF高频读写器模块,右键点击,获得右键菜单,菜单功能说明如下Array1.8知识学习A、高频HF的射频识别设备(高频读写器)工作于13.56MHz频段,系统通过天线线圈电感耦合来传输能量,通过电感耦合的方式磁场能量下降较快。

磁场信号具有明显的读取区域边界。

主要应用于1米以内的人员或物品的识别。

主要遵循两种协议:ISO/IEC14443(A、B)协议,ISO/IEC15693协议。

实验6HF高频RFID通信协议实验V20170317.doc

实验6 HF高频RFID通信协议实验-V201703171.实验目的掌握高频读卡器的通讯协议;掌握高频模块工作原理;掌握本平台高频模块的操作过程;2.实验设备硬件:RFID实验箱套件,电脑等;软件:Keil,串口调试助手;STC_ISP软件:配套光盘\第三方应用软件\STC_ISP异或计算小软件:配套光盘\第三方应用软件\异或计算小软件源码路径:配套光盘\源代码\RFID基础实验\实验 6 HF高频RFID通信协议实验-V20170317Hex路径:配套光盘\源代码\RFID基础实验\实验6 HF高频RFID通信协议实验-V20170317\out3.实验原理3.1 高频RFID系统典型的高频HF(13.56MHz)RFID系统包括阅读器(Reader)和电子标签(Tag,也称应答器Responder)。

电子标签通常选用非接触式IC卡,又称智能卡,可读写,容量大,有加密功能,数据记录可靠。

IC卡相比ID卡而言,使用更方便,目前已经大量使用在校园一卡通系统、消费系统、考勤系统、公交消费系统等。

目前市场上使用最多的是PHILIPS的Mifare系列IC卡。

读写器(也称为“阅读器”)包含有高频模块(发送器和接收器)、控制单元以及与卡连接的耦合元件。

由高频模块和耦合元件发送电磁场,以提供非接触式IC 卡所需要的工作能量以及发送数据给卡,同时接收来自卡的数据。

此外,大多数非接触式IC卡读写器都配有上传接口,以便将所获取的数据上传给另外的系统(个人计算机、机器人控制装置等)。

IC卡由主控芯片ASIC(专用集成电路)和天线组成,标签的天线只由线圈组成,很适合封状到卡片中,常见IC卡内部结构如图3.1所示:图3.1 IC卡内部结构图较常见的高频RFID应用系统如图3.2所示,IC卡通过电感耦合的方式从读卡器处获得能量。

图3.2 常见高频RFID应用系统组成下面以典型的IC卡MIARE 1为例,说明电子标签获得能量的整个过程。

实验5 HF高频RFID认知实验-V20170317

实验5 HF高频RFID认知实验-V201703171.实验目的学习通过上位机软件操作高频RFID读写器;了解标签的基本操作,体会标签的操作的原理;2.实验设备硬件:实验箱套件,电脑等;软件:串口调试助手,射频卡读写器演示软件;Hex路径:配套光盘\源代码\RFID基础实验\实验 5 HF高频RFID认知实验-V20170317\out射频卡读写器演示软件:配套光盘\第三方应用软件\基于CLRC632的多协议卡上位机测试软件3.实验原理本实验结合上位机,与高频RFID读写器通信实现对标签操作。

上位机实验的功能本质是与高频RFID读写器的串口通信,从而实现对标签的读卡号、读/写数据等一系列的功能。

实验过程并不涉及射频识别原理、通讯协议、标签内部结构和编程实现,仅在上位机上进行操作,目的是让大家对RFID读写器、标签的操作有个感性的认识,以便后续更加深入的实验。

4.实验步骤第一步:认识高频RFID读写器,实物图如图4.1所示:图4.1 高频模块实物图第二步:使用串口线连接PC和3号节点高频读卡器的DB9接头,S1开关拨打到左边:STC串口与DB9连接。

第三步:根据配套光盘\第三方应用软件\STC_ISP\STC-ISP软件使用说明书,使用STC-ISP软件将配套光盘\源代码\RFID基础实验\实验 5 HF高频RFID认知实验-V20170317\out下的SL601F.hex文件通过STC_ISP串口下载软件下载到3号高频节点的单片机中。

第四步:将高频标签放置在天线上方,如图4.2所示:图4.2 放置高频标签第五步:打开射频卡读写器演示软件(路径:配套光盘\第三方应用软件\基于CLRC632的多协议卡上位机测试软件),选择正确的COM端口,配置成功后显示“连接操作成功”,如图4.3所示:图4.3 配置上位机第六步:设置高频卡类型:这里实验用的是Mifare_Std S50卡,点击“选择操作卡”进行选择,如图4.4所示:图4.4 选择卡类型第七步:读卡号:点击“寻卡ALL”,将返回卡的ID号,同时在提示栏返回“操作成功”,这里读取到的卡ID号是“5A017903”,如图4.5所示:图4.5 读卡号第八步:读数据:高频卡有16个扇区,每个扇区有4块,共有64个块。

实验7HF-ISO15693协议操作

实验7HF-ISO15693协议操作知识点学习:ISO/IEC 15693协议标准的高频RFID无源IC卡,专为供应链与运筹管理应用所设计,具有高度防冲突与长距离运作等优点,适合于高速、长距离应用。

包括ICODE SLI-S、SL2-S 等多系列产品,目前ICODE 是高频(HF)RFID标签方案的业界标准。

ICODE SLI-S系列SL2 ICS20芯片的内部构成如上图,可分为射频处理单元、数据控制单元和EEPROM存储单元。

在数据控制单元里对数据进行反碰撞、认证和存储控制等处理。

SLICS20存储器分为32个块、每个块由4字节(32位)组成,共128字节,如下图,上部4个块(-4、-3、-2、-1块)分别用于UID(64位唯一ID序列号)、特殊功能(EAS、AFI、DSFID)和写入控制位,其他28个块为用户数据块。

UID占用块-4和块-3共8个字节(64位),是厂商写入的世界唯一标签识别序列号,用户不可更改,在UID中包含厂商代码、产品分类代码和标签芯片生产序列代码,UID的代码构成如上图。

块-1是写入控制位,具体控制分配见上图,它可以控制每个数据块的写入和块-2(特殊功能块)每个字节的写入。

写入位1代表写入保护,且不可再修改控制位。

特殊功能EAS(Electronic Article Surveillance,电子防盗系统)主要用来防止物品被盗,标签管理者可以设置(EAS=1)和清除(EAS=0)EAS标识,当设置有EAS标识的标签通过读写器的作用范围时,读写器会识别EAS标识,发出警报。

EAS的数据结构如下图,EAS的LSB的第一位(e位)写1代表EAS 标示有效,写0代表清除EAS标示,其他位无效。

特殊功能AFI(Application Family Idenfifier,应用族标识符),可事先规定应用族代码并写入AFI字节,在处理多个标签的时候进行分类处理。

例如在物流中心处理大量货物时,可根据标签上的AFI应用族标识符来区分是出口货物还是内销货物。

【精编】智能家居物联网实训台RFID实验手册

智能家居物联网实训台RFID实验手册目录第1章RFID基础知识11.1RFID简介11.2RFID工作原理11.3RFID应用2第2章HF RFID32.1高频(HF)读卡模块简介32.1.1MFRC500简介32.1.2MFRC500特点72.1.3MIFARE卡介绍72.2实训1 MIFARE 1卡读写测试实训142.2.1实训目的142.2.2实训设备142.2.3实训内容142.2.4实训原理142.2.5实训步骤172.3实训2 MIFARE 1卡通讯测试实训252.3.1实训目的252.3.2实训设备252.3.3实训内容252.3.4实训原理252.3.5实训步骤29第3章UHF RFID323.1超高频(UHF)读卡模块简介323.1.1JT-2860模组特点323.1.2JT-2860模组参数333.1.3JT-2860模组接口定义343.2实训3 标签读写测试实训363.2.1实训目的363.2.2实训设备363.2.3实训内容363.2.4实训原理363.2.5实训步骤37第4章IC卡收费系统开发实训464.1实训目的464.2实训设备464.3实训内容464.4实训原理464.4.1IC卡收费系统简介464.4.2IC卡收费系统运行方式474.4.3IC卡收费系统组成48 4.5实训步骤504.5.1新建一个Qt工程504.5.2与读卡器建立通讯514.5.3实现开户功能654.5.4实现查询功能73第1章RFID基础知识1.1RFID简介RFID(射频识别:radiofrequencyidentification)是一种非接触式的自动识别技术,它通过射频信号自动识别目标对象并获取相关数据,识别工作无须人工干预,作为条形码的无线版本,RFID技术具有条形码所不具备的防水、防磁、耐高温、使用寿命长、读取距离大、标签上数据可以加密、存储数据容量更大、存储信息更改自如等优点,其应用将给零售、物流等产业带来革命性变化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、HF RFID基础实验1.1、读ISO15693标签UID号、读/写/锁定数据块命令实验目的通过本实验使学生了解 RFID 的基本原理,熟悉 ISO15693标签的基本特征以及协议规范,理解并掌握实验过程中所用到的基本概念。

通过使用开发系统的TI-TRF7960开发系统理解本节所用的的命令操作以及通讯机制。

实验设备TI TRF7960读卡器一个、USB 连接线一条、电脑一台、HF RFID实验上位机软件、ISO156963 标签若干张实验知识预备及原理缩略语AFI(application family identifier)应用族识别符,应用的卡预选准则CRC(cyclic redundancy check)循环冗余校验DSFID(data storage format identifier)数据储存格式标识符EOF (end of frame)帧结束LSB(least significant bit)最低有效位MSB(most significant bit)最高有效位RFU(reserved for future use0)留作将来ISO/IEC 使用SOF (start of frame)帧的起始UID (unique identifier)唯一标识符VCD(vicinity coupling device)附近式耦合设备VICC(vicinity integrated circuit card)附近式卡理解Ti_RF7960 硬件连接原理框图将迷你USB线缆直接连入读卡器和电脑即可。

HF RFID读卡器MiniUSB电脑USB口数据速率和数据编码数据编码采用脉冲位置调制,VICC应能够支持两种数据编码模式。

VCD决定选择哪一种模式,并在帧起始(SOF)时给与VICC指示。

(1)数据编码模式:256取1一个单字节的值可以由一个暂停的位置表示。

在256/fC(约18.88μs)的连续时间内256 取 1 的暂停决定了字节的值。

传输一个字节需要 4.833 ms,数据速率是1.54 kbits/s(fC/8192)。

最后一帧字节应在VCD发出EOF前被完整传送,如图2-1所示。

图1-1 256 取1编码模式在图 1-1中数据´E1´ = (11100001)b = (225) 是由 VCD 发送给 VICC 的。

暂停产生在已决定值的时间周期的后一半,如图 1-2所示。

图1-2 1 个时间周期的延迟(2)数据编码模式:4 取1使用 4取 1脉冲位置调制模式,这种位置一次决定 2个位。

4个连续的位对构成 1个字节,首先传送最低的位对。

数据速率为26.48 kbits/s (fC/512)。

如图 1-3示出了 4取 1脉冲位置技术和编码。

图1-3 4 取1编码模式例如:图1-4示出了 VCD 传送´E1´ = (11100001)b = 225。

图1-4 4 取1编码示例VICC到VCD通信信号接口对于一些参数定义了多种模式,以满足不同的噪声环境和不同的应用需求。

1.负载调制VICC 应能经电感耦合区域与 VCD 通信,在该区域中,所加载的载波频率能产生频率为 fs 的副载波。

该副载波应能通过切换 VICC 中的负载来产生。

2.副载波由VCD通讯协议报头的第一位选择使用一种或两种副载波,在GB/T XXXXX.3中定义。

VICC应支持两种模式。

当使用一种副载波,副载波负载调制频率fS1应为fC/32(约423.75 kHz)。

当使用两种副载波,频率fS1应为fC/32(约423.75 kHz),频率fS2应为fC/28(约484.28 kHz)。

若两种副载波都出现,它们之间应有连续的相位关系。

3.数据速率使用低或高数据速率。

由VCD通讯协议报头的第二位选择使用何种速率,在GB/TXXXXX.3中有定义。

VICC应支持表1.1示出的数据速率。

表1.1数据速率数据速率单副载波双副载波低 6.62 kbits/s (f C/2048) 6.67 kbits (f C/2032)高26.48 kbits/s (f C/512) 26.69 kbits (f C/508) 4.位表示和编码根据以下方案,数据应使用曼彻斯特编码方式进行编码。

所有时间参考了VICC到VCD的高数据速率。

对低数据速率,使用同样的副载波频率或频率,因此,脉冲数和时间应乘以4。

(1)使用一个副载波时的位编码逻辑0以频率为f C/32(约423.75 kHz)的8个脉冲开始,接着是非调制时间256/f C(约18.88μs),见图1-5。

图1-5 逻辑0逻辑1以非调制时间256/fC(约 18.88μs)开始,接着是频率为fC/32(约423.75 kHz)的8个脉冲,见图1-6。

图1-6 逻辑1(2)使用两个副载波时的位编码逻辑0以频率为fC/32(约423.75 kHz)的8个脉冲开始,接着是频率为fC/28(约484.28 kHz)的9个脉冲,见图1-7。

图1-7 逻辑0逻辑 1 以频率为fC/28(约 484.28 kHz)的 9 个脉冲开始,接着是频率为fC/32(约 423.75 kHz)的8个脉冲,见图1-8图1-8 逻辑1VICC到VCD帧选择帧为了容易同步和不依赖协议。

帧由帧起始(SOF)和帧结束(EOF)来分隔,使用编码违例来实现此功能。

ISO/IEC保留未使用项以备将来使用。

所有时间参考了VICC到VCD的高数据速率。

对低数据速率,使用同样的副载波频率或频率,因此,脉冲数和时间应乘以4。

在发送一帧数据给VCD后,VICC应准备在300μs内接收来自VCD的一帧数据。

1.使用一个副载波时的S OFSOF包含三个部分:—个非调制时间 768/f C (56.64μs)。

—频率为f C /32 (423.75 kHz)的24个脉冲。

—逻辑1以非调制时间256/f C(18.88μs)开始,接着是频率为f C/32(423.75 kHz)的8个脉冲。

单副载波SOF见图1-9。

图1-9 使用1个负载波时的开始帧2.使用两种副载波时的S OFSOF包含三个部分:—频率为f C/28(约 484.28 kHz)的脉冲。

—频率为f C/32(约 423.75 kHz)的24个脉冲—逻辑1以频率为f C/28(约 484.28 kHz)的9个脉冲开始,接着是频率为f C/32(约 423.75 kHz)的8个脉冲。

双副载波时的SOF见图1-10。

图1-10 使用双副载波时的S OF3.使用两个副载波时的E OFEOF包含三个部分:—逻辑0以频率为fC/32(约 423.75 kHz)的8个脉冲开始,接着是频率为fC/28(约 484.28 kHz)的9个脉冲。

—频率为fC /32(约 423.75 kHz)的24个脉冲。

—频率为fC /28(约 484.28 kHz)的27个脉冲。

双副载波时的EOF见图1-11图1-11 使用双副载波的E OF4.使用一个副载波时的E OFEOF包含三个部分:—逻辑0以频率为fC/32(约 423.75 kHz)的8个脉冲开始,接着是非调制时间256/fC(约 18.88 μs)。

—频率为fC /32(约 423.75 kHz)的24个脉冲。

—一个非调制时间 768/fC (约 56.64μs)。

单副载波时的EOF见图1-12。

图1-12 使用单副载波时E OF注:详细请参阅《高频RFID技术高级教程》实验准备本节介绍的内容为如何连接目标板通过PC的串口(本系统为USB转串口)与上位机软件连接演示不同协议标签的读写。

1.下载程序注:出厂时程序已下载无须重复下载。

如需要独自完成开发或修改源代码可从我公司,或市面上购买普通MSP430仿真器,连接硬件接口即可完成程序,烧写。

即修改程序需配合MSP430仿真器在IAR编译环境下进行。

对应版本的IAR安装目录:RFID技术实验\工具软件\IAR(MSP430程序读写软件)接上MSP430仿真器系统会自动更新驱动,如下图:图1-13 设备管理器仿真器与TI TRF7960目标板接好。

打开目录: \新感知RF2-V210\RFID技术实验\2-HF RFID实验\TRF7960_Parallel_SPI_Firmware_Ver3-2_EXP_MIFARE下的工程文件。

下载程序如下图:图1-14 工程界面2.安装USB驱动程序注:须将TI TRF7960读卡器右下角的拨码开放拨向usb端驱动安装目录::\新感知RF2-V210\RFID技术实验\工具软件\USB串口驱动,安装方案参看该目录下的“安装简要说明”。

安装成功在设备描述中有一个串口端口,安装完成后在设备管理器中查看COMxx端口,(例如COM8)如下图所示:图1-16 查看系统分配的端口号2、上位机软件介绍确保TI TRF7960RFID 与电脑连接正常,打开上位机软件(路径:\RFID 技术实验\2-HF RFID 实验\PC 软件\TRF7960EVM GUI Software )无线龙RFID 。

选择可用COMxx 端口连机,如下图所示:图1-17标签类型:(ISO/IEC) 15693(ISO/IEC) 14443A(ISO/IEC) 14443BTag-it ™ – TI 公司的协议卡标签类型 功能选项RSSI 窗口数据窗口GUI 控制选择协议命令 LOG 窗口特殊功能芯片状态功能选项:Find Tags-该功能可以读各种协议的标签Registers-允许用户手动设置TRF7960的寄存器Test- 测试LOG 窗口:主机请求请求回应MSP430回应卡片回应RSSI 窗口:插槽(slot)UID号RSSI主通道(AM)RSSI副通道(PM)实验过程1、将TI TRF7960读卡器右下角的拨码开放拨向 usb端,然后使用 mini USB 线将TI TRF7960目标板与电脑连接起来,并查看相应端口号。

2、确保TI TRF7960RFID与电脑连接正常,打开上位机软件无线龙RFID选择可用COMxx端口连机,如下图所示:3、标签类型选择15693,并设置协议。

点击设置协议命令时会发送3条命令)(写寄存器、设置AGC、设置接收器模式(AM/PM)设置AGC命令:010*******F0000000设置接收器模式命令:010*******F1FF00004、询卡[Inventory(0x01)],当标签接收到inventory的命令,芯片将执行防冲撞序列。

操作如下:(a)选择询卡命令(b)选择设置协议(c)选择执行选择命令图1-20设置协议图1-21图1-22询卡请求命令:010B1000000卡片在16个时间槽中的一个时间段返回UID 值,如下所示:[408C4503000104E0,7F] (408C4503000104E0为标签号,7F 为RSSI 寄存器 值)[,40][,40][,40][,40][,40][,40][,40][,40][,40][,40][,40][,40][,40][,40][,40] 5、 设置标签标志位:双幅载波、搞数据率,选择数据编码模式 1 out of 4 或者1 out 256。